## THE UNIVERSITY OF MICHIGAN

## COLLEGE OF ENGINEERING

Department of Electrical Engineering Space Physics Research Laboratory

Scientific Report No. JS-4

# DEVELOPMENT OF A DIGITIZED VOLTAGE GENERATOR FOR IONOSPHERIC PROBE MEASUREMENTS

Prepared on behalf of the project by: George D. Breen

ORA Project 03599

under contract with:

NATIONAL AERONAUTICS AND SPACE ADMINISTRATION CONTRACT NO. NASw-139 WASHINGTON, D.C.

administered through:

OFFICE OF RESEARCH ADMINISTRATION ANN ARBOR

October 1961

MMRQ622

This report has also been submitted as a thesis in partial fulfillment of the requirements for the degree of Electrical Engineer in The University of Michigan, 1961.

# TABLE OF CONTENTS

|                                                                      | Page |

|----------------------------------------------------------------------|------|

| ABSTRACT                                                             | v    |

| LIST OF TABLES                                                       | vii  |

| LIST OF FIGURES                                                      | viii |

| LIST OF SYMBOLS                                                      | xi   |

| I. INTRODUCTION                                                      | 1    |

| II. SYSTEM DESIGN                                                    | 7    |

| A. Duality                                                           | 8    |

| 1. Dual Source—Identical, Isolated, and Synchronized Step Generators | 8    |

| 2. Single Source—Dual Output Systems                                 | 9    |

| a. Dual Secondary Transformer                                        | 9    |

| b. Switching Techniques                                              | 11   |

| B. Stairstep Voltage Generator                                       | 13   |

| 1. A Train of Unit Voltage Steps, Delayed, Added, and Stored         | 14   |

| 2. Triggered Steps                                                   | 15   |

| 3. Gated Linear Sweep                                                | 18   |

| 4. "Q-Transporter"                                                   | 21   |

| III. CIRCUIT DESIGN                                                  | 24   |

| A. "Q-Transporter"                                                   | 24   |

| B. Trigger Circuit                                                   | 29   |

| C. Multivibrator Driver Circuit                                      | 1414 |

|       |        |                                                                                     | Page |

|-------|--------|-------------------------------------------------------------------------------------|------|

|       | D.     | Voltage-Operated Reset Switch                                                       | 47   |

|       | E.     | Output Amplifier                                                                    | 56   |

|       | F.     | Zero Reference                                                                      | 62   |

|       | G.     | Power Supplies                                                                      | 69   |

| IV.   | DUAL   | OUTPUT CIRCUIT                                                                      | 77   |

|       | Α.     | Diode Switches                                                                      | 77   |

|       | В.     | Synchronization of Reset Levels                                                     | 79   |

| ٧.    | ERROR  | ANALYSIS                                                                            | 83   |

|       | Α.     | Step Droop                                                                          | 83   |

|       | В.     | Environmental Effects                                                               | 86   |

|       |        | 1. Voltage Stability                                                                | 87   |

|       |        | 2. Temperature Stability                                                            | 88   |

|       |        | 3. In-Flight Calibration                                                            | 88   |

| VI.   | PRACI  | TCAL CONSTRUCTIONAL DETAILS                                                         | 90   |

|       | Α.     | Transistor Selection                                                                | 90   |

|       | В.     | Circuit Adjustment                                                                  | 91   |

|       |        | APPENDICES                                                                          |      |

| ı.    | STOR   | AGE-COUNTER STAIRSTEP-WAVEFORM GENERATOR                                            | 97   |

| II.   | TRAN   | SISTOR PARAMETERS                                                                   | 102  |

| III.  |        | RIMENTAL DETERMINATION OF THE TEMPERATURE COEFFICIENTS ARGE ELECTROLYTIC CAPACITORS | 103  |

| .सप्त | FERENC | ES                                                                                  | 110  |

#### ABSTRACT

The program of ionospheric research conducted by The University of Michigan's Department of Electrical Engineering makes extensive use of rocket-borne probes. Data are collected by means of an electrostatic sensor in the probe, and analyzed by means of a large, ground-based, general-purpose digital computer. To exploit the vast potential of the latter more fully, a development project was undertaken to modify, or redesign as necessary, present analog-type sensors. Means of generating an accurate series of discrete voltage levels, corresponding to a stairstep waveform, are investigated and an efficient method is described. The resulting compact, transistorized circuitry has been compensated for variations in supply voltages and ambient temperature to insure voltage level accuracies of better than 99% with less than 0.05% droop per step. In addition, means have been developed to provide two identical output waveforms with a high degree of electrical isolation.

## LIST OF TABLES

| No.    |                                                                      | Page |

|--------|----------------------------------------------------------------------|------|

| I.     | Summary of Q-Transporter and Trigger Stage Design<br>Considerations  | 40   |

| II.    | Q-Transporter and Trigger Circuit Component Values                   | 40   |

| III.   | Q-Transporter Step-Generation Sequence                               | 41   |

| IV.    | Multivibrator Component Values                                       | 1414 |

| ٧.     | Properties of 2N338 Transistor                                       | 58   |

| VI.    | Stairstep-Generator Component Values                                 | 75   |

| VII.   | $P_{\mathbf{V}}$ , Percentage Droop of Output Steps with Temperature | 85   |

| III-1. | Capacitor Test-Circuit Component Values                              | 108  |

## LIST OF FIGURES

| No. |                                                                         | Page      |

|-----|-------------------------------------------------------------------------|-----------|

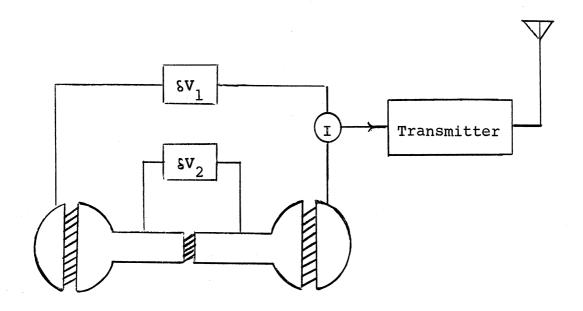

| 1   | Functional Block Diagram of "Dumbbell" Probe.                           | 2         |

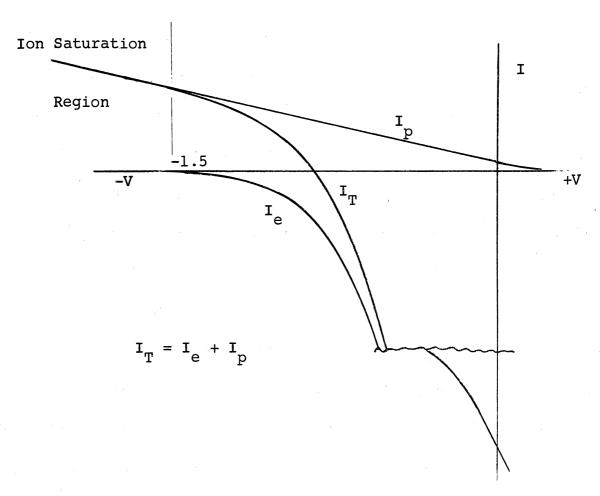

| 2   | Single Spherical Electrode Volt-Ampere Characteristic.                  | 2         |

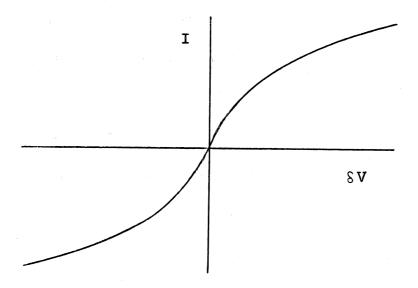

| 3   | Volt-Ampere Characteristic of Equal Area Bipolar Probe.                 | 4         |

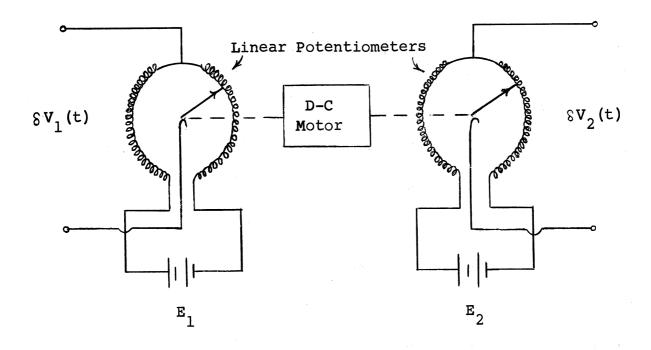

| 4   | Motor-driven &V Generator.                                              | 4         |

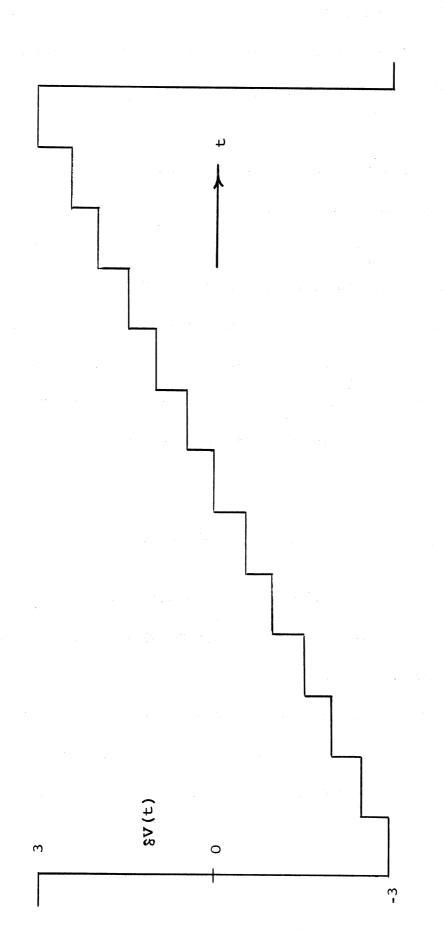

| 5   | Ideal "Stairstep" Waveform.                                             | 6         |

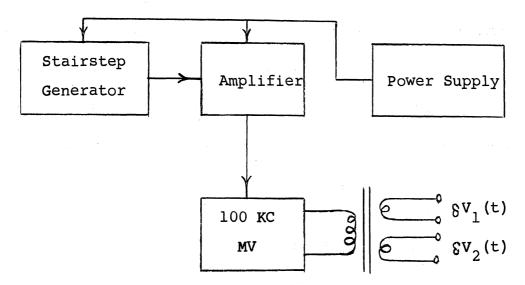

| 6   | Stairstep Generator with Transformer Coupled Dual Output.               | 10        |

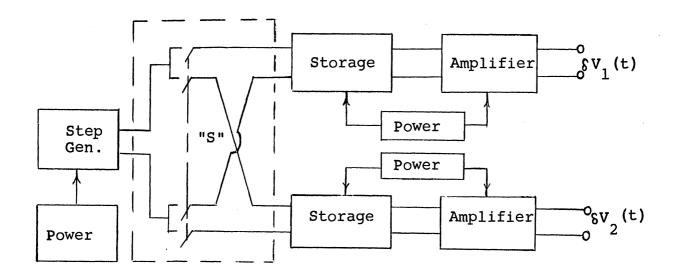

| 7   | Block Diagram of Stairstep Generator with Switched Dual Output          | s. 11     |

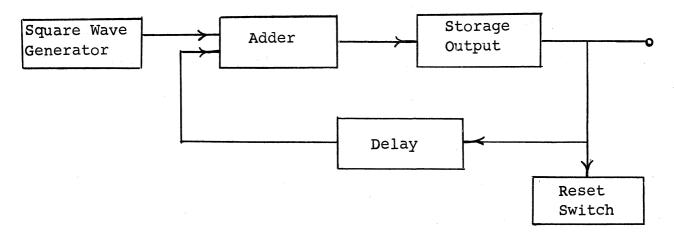

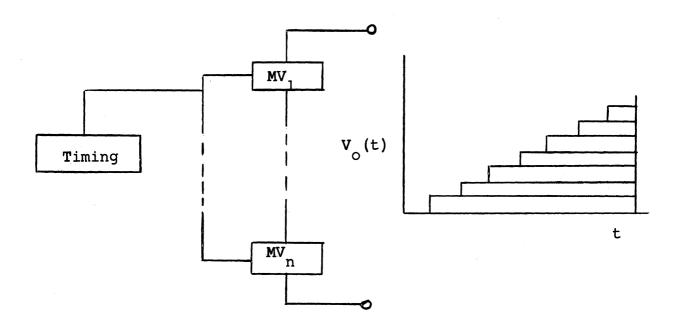

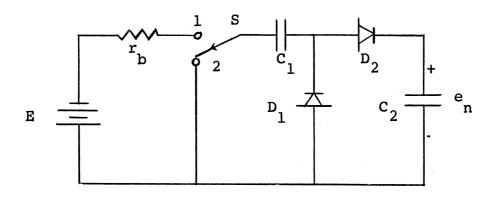

| 8   | Unit Step Implementation of Stairstep Generator.                        | 14        |

| 9   | Implementation of Stairstep Waveform Considered as Sum of Square Waves. | 15        |

| 10  | Storage-Counter Circuit with Output Waveform.                           | 17        |

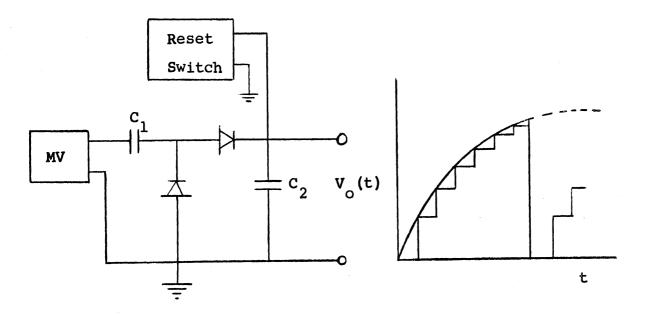

| 11  | Storage-Counter Circuit Linearized by Feedback with Output Waveform.    | 17        |

| 12  | Stairstep Waveform Considered as Limiting Case of a Gated Linear Sweep. | 18        |

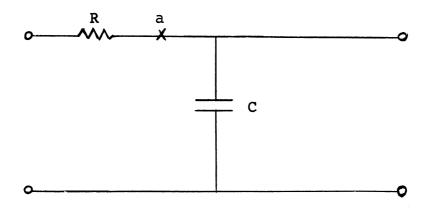

| 13  | RC Integrator Circuit.                                                  | 19        |

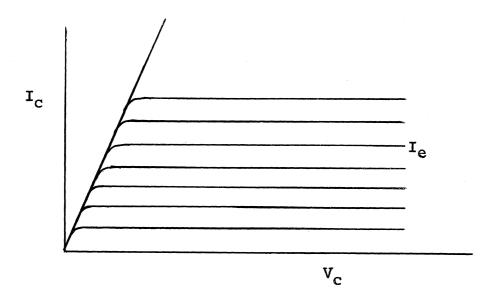

| 14  | Typical Junction Transistor Collector Characteristics.                  | 20        |

| 15  | Gated Linear Sweep Circuit.                                             | 20        |

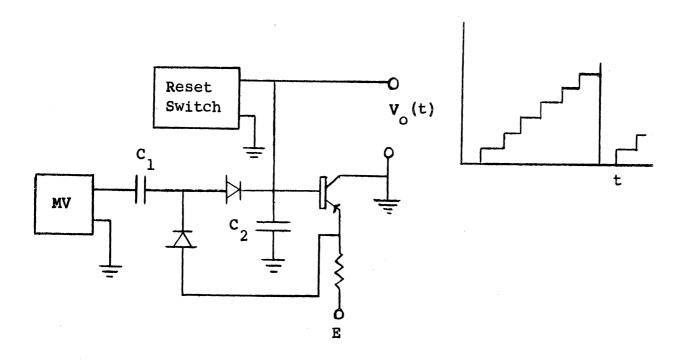

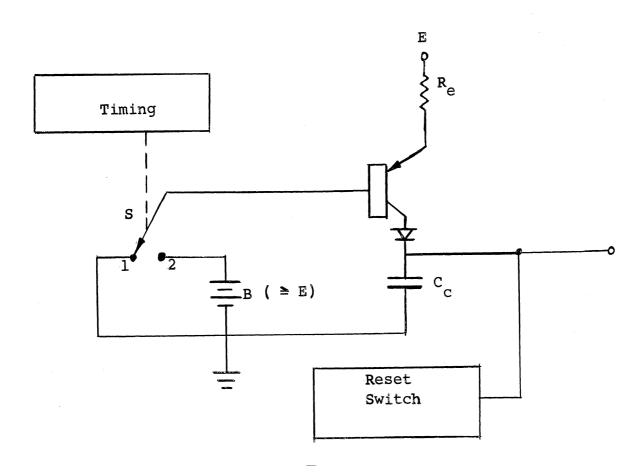

| 16  | Modified Gated Linear Sweep Circuit                                     | 22        |

| 17  | Q-Transporter Equivalent Circuit.                                       | 27        |

| 18  | Q-Transporter Trigger Circuit.                                          | 29        |

| 19  | Modified Q-Transporter Trigger Circuit.                                 | 31        |

| 20  | Complete Q-Transporter Trigger Circuit.                                 | 33        |

| 21  | Q-Transporter Base Waveforms.                                           | 35 and 36 |

# LIST OF FIGURES (Continued)

| No. |                                                                    | Page |

|-----|--------------------------------------------------------------------|------|

| 22  | Q-Transporter Response to Trigger Pulse.                           | 42   |

| 23  | Q-Transporter Output Waveform.                                     | 43   |

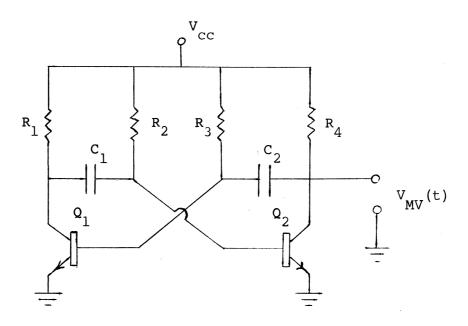

| 24  | Multivibrator Circuit.                                             | 45   |

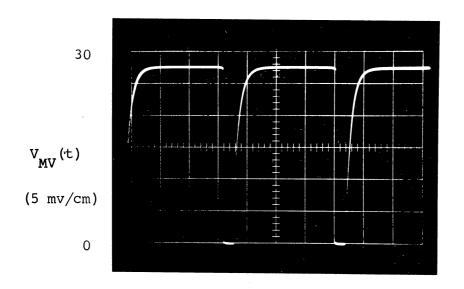

| 25  | Multivibrator Output Waveform.                                     | 45   |

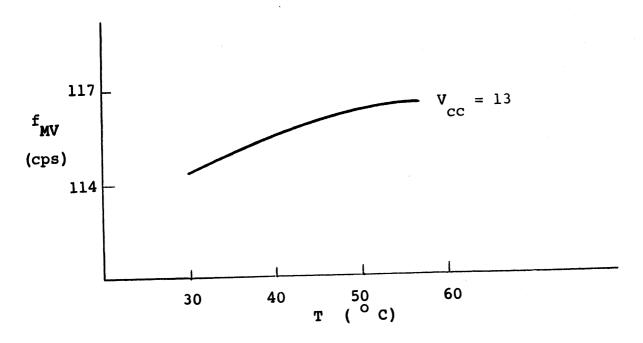

| 26  | Multivibrator Temperature Characteristic.                          | 46   |

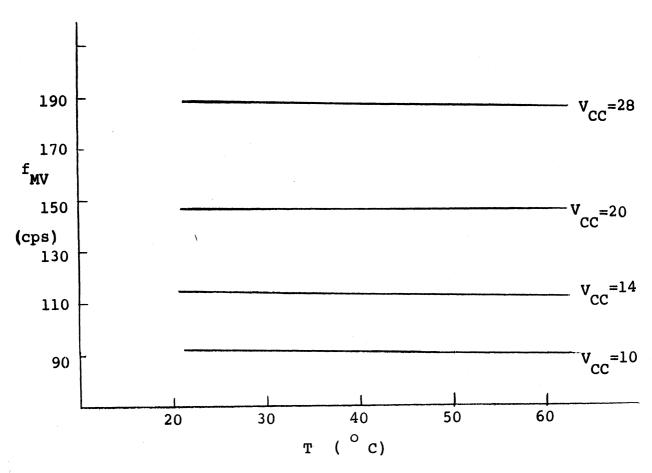

| 27  | Temperature Compensated Multivibrator Characteristic.              | 46   |

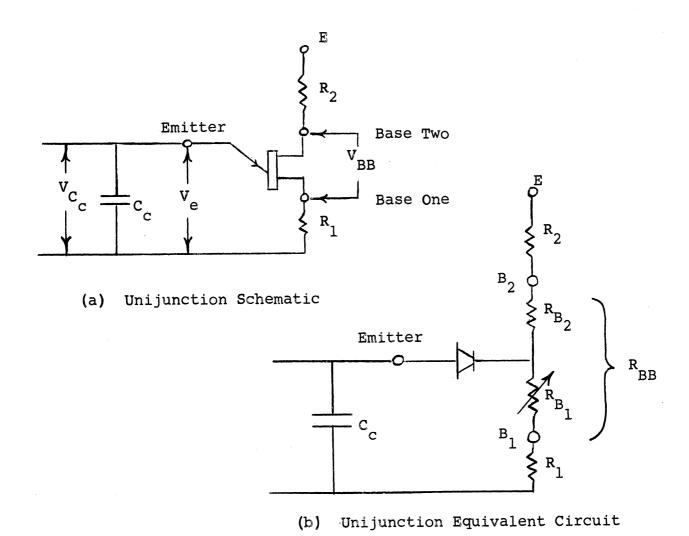

| 28  | Unijunction Transistor Schematic and Equivalent Circuit.           | 47   |

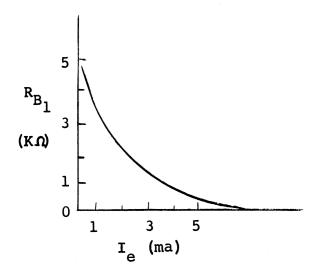

| 29  | Variation of Unijunction Base-One Resistance with Emitter Current. | 49   |

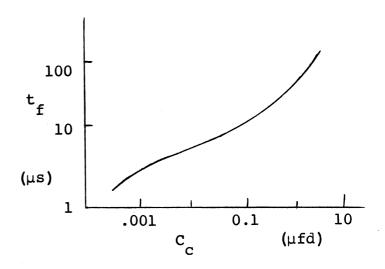

| 30  | Unijunction Discharge Time versus Emitter Circuit Capacitance.     | 49   |

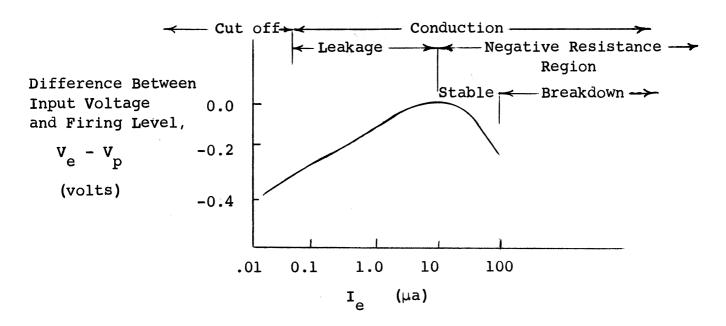

| 31  | Typical Unijunction Input Characteristic Near Peak Point.          | 49   |

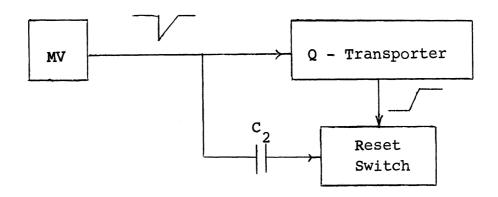

| 32  | Block Diagram of Unijunction Triggering Method.                    | 52   |

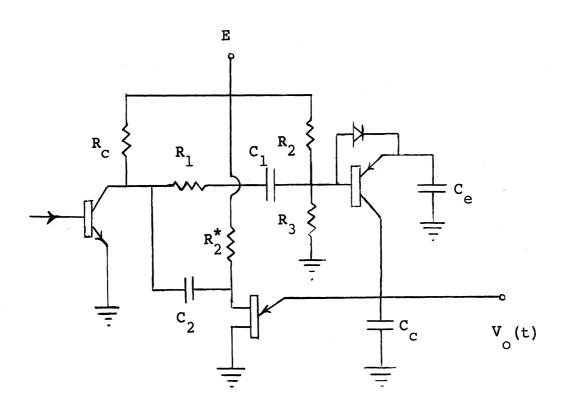

| 33  | Unijunction Triggering Circuit.                                    | 52   |

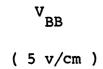

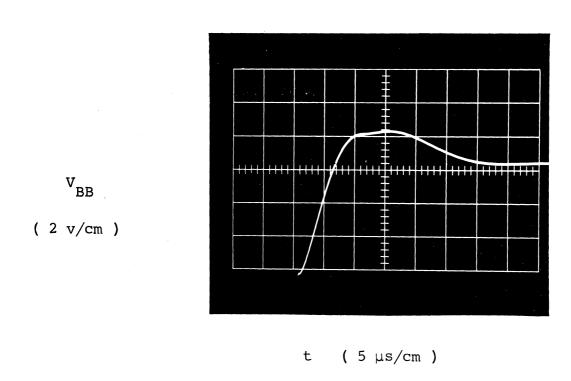

| 34  | Oscillogram of Unijunction Interbase Voltage, $V_{\mathrm{BB}}$ .  | 54   |

| 35  | Oscillogram of Unijunction Discharge Spike in Interbase Voltage.   | 54   |

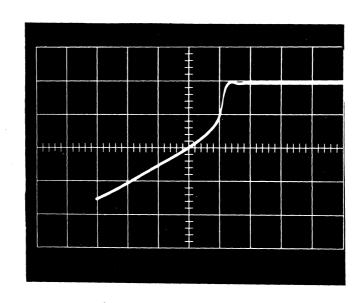

| 36  | Emitter Follower Equivalent Circuit.                               | 57   |

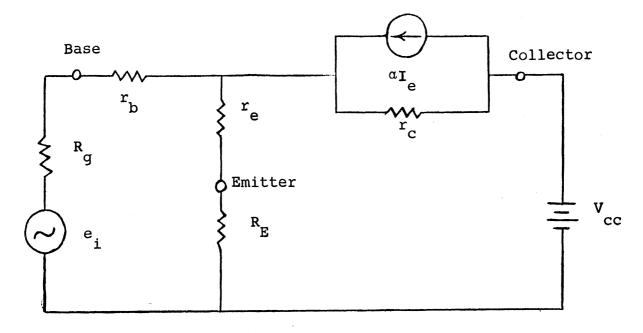

| 37  | Emitter Follower Amplifier Circuit.                                | 58   |

| 38  | Emitter Follower Stage Voltage Gain.                               | 60   |

| 39  | Diode Zero Reference Circuit.                                      | 62   |

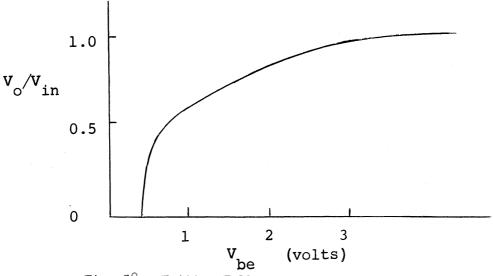

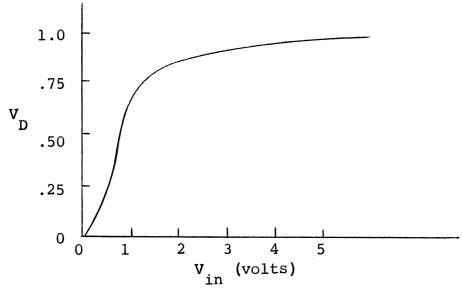

| 40  | Silicon Diode Forward Transfer Characteristics.                    | 63   |

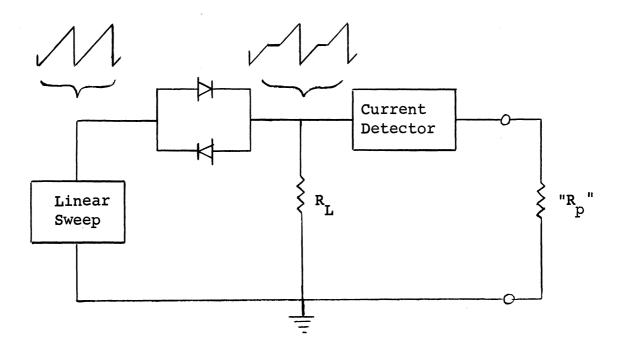

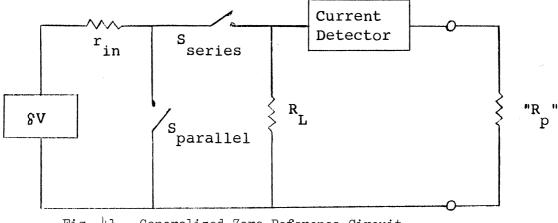

| 41  | Generalized Zero Reference Circuit.                                | 63   |

| 42  | Emitter Follower Zero Reference Circuit.                           | 66   |

| 43  | Zero Reference Circuit Input Waveform.                             | 66   |

# LIST OF FIGURES (Concluded)

| No.          |                                                             | Page |

|--------------|-------------------------------------------------------------|------|

| 44           | Zero Reference Circuit Output Waveform.                     | 67   |

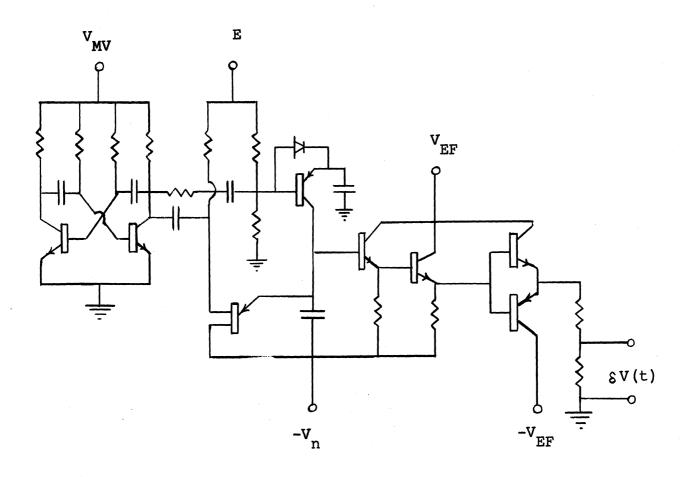

| 45           | δV Schematic Indicating Required Supply Voltages.           | 68   |

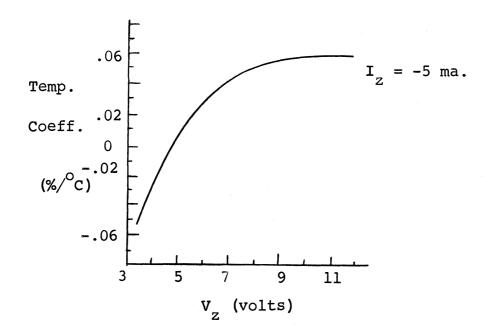

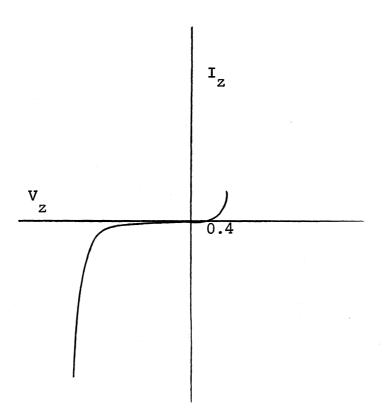

| 46           | Typical Temperature Coefficients of Zener Reference Diodes  | 70   |

| 47           | Typical Zener Diode Reverse Characteristic.                 | 70   |

| 48           | Variation of Zener Diode Dynamic Impedance.                 | 73   |

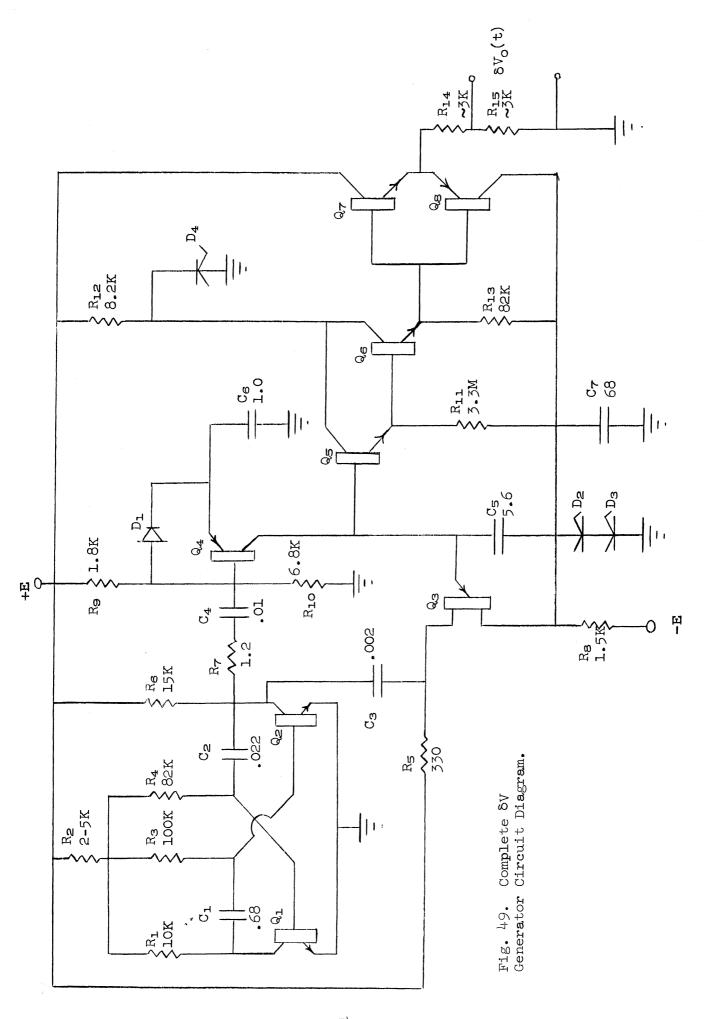

| 49           | Complete &V Circuit Diagram.                                | 74   |

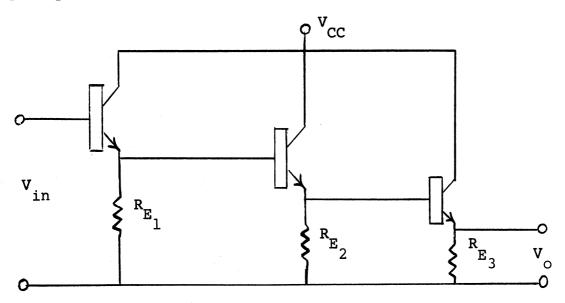

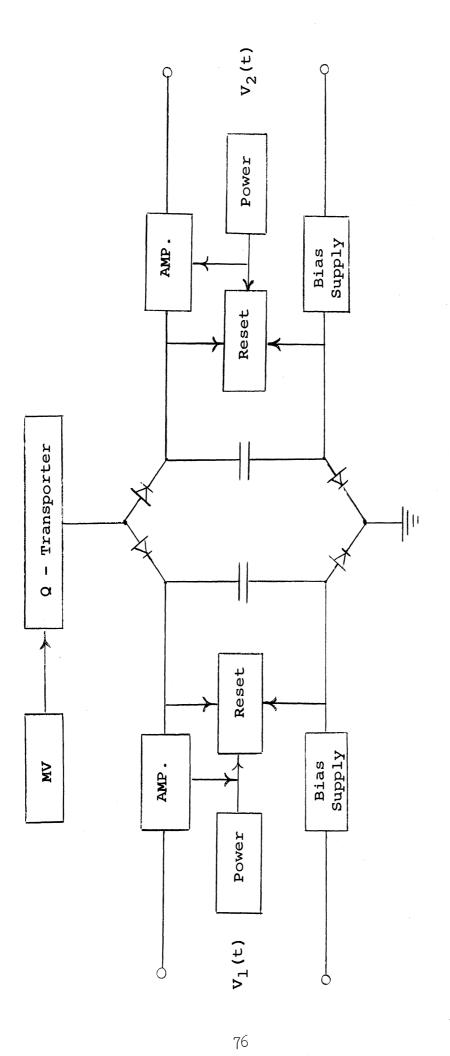

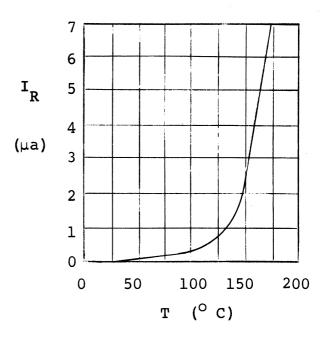

| 50           | Dual Output Circuit.                                        | 76   |

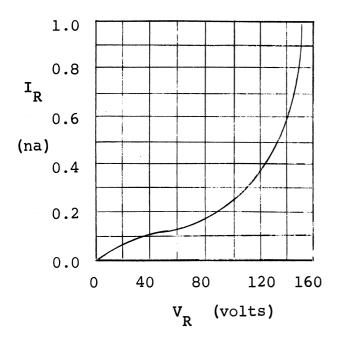

| 51           | Bridge Diode Reverse Characteristics (at 25°C).             | 78   |

| 52           | Bridge Diode Reverse Characteristics versus Temperature.    | 78   |

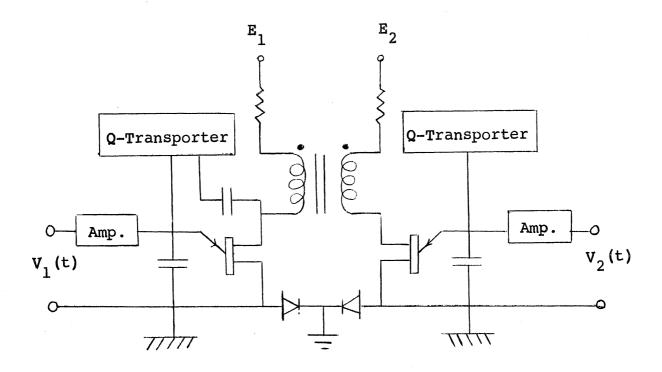

| 53           | Transformer Synchronization of Reset Levels.                | 79   |

| 54           | Dual System Synchronization Test Circuit.                   | 80   |

| 55           | Transformer Coupled Synchronizing Pulse.                    | 81   |

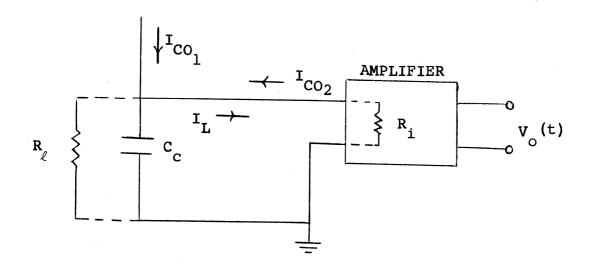

| 56           | Output Capacitor Currents.                                  | 83   |

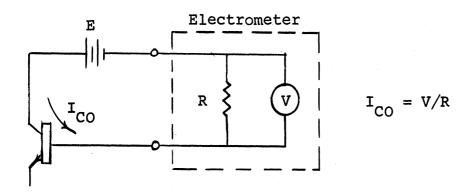

| 57           | Transistor Leakage Current Measurement Circuit.             | 91   |

| 58           | Negative Voltage Reference Circuit.                         | 94   |

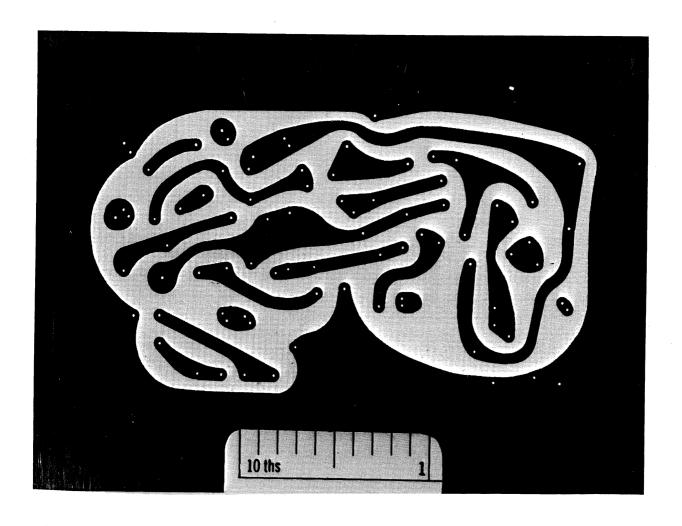

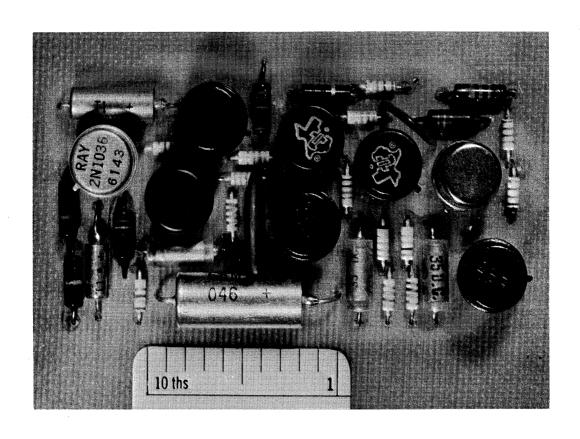

| 59           | Wiring Connections on Printed Circuit Board.                | 95   |

| 60           | Component Arrangement on Printed Circuit Board.             | 96   |

|              |                                                             |      |

| I-l          | Diode Counter Circuit.                                      | 97   |

| I <b>-</b> 2 | Linearized Storage Counter Circuit.                         | 99   |

| III-l        | Capacitor Temperature Coefficient Test Circuit.             | 105  |

| III-2        | Temperature Characteristic of Texas Instruments' SCM Series | 109  |

# LIST OF FIGURES (Continued)

| No. |                                                                                | Page |

|-----|--------------------------------------------------------------------------------|------|

| 22  | Q-Transporter Response to Trigger Pulse.                                       | 42   |

| 23  | Q-Transporter Output Waveform.                                                 | 43   |

| 24  | Multivibrator Circuit.                                                         | 45   |

| 25  | Multivibrator Output Waveform.                                                 | 45   |

| 26  | Multivibrator Temperature Characteristic.                                      | 46   |

| 27  | Temperature Compensated Multivibrator Characteristic.                          | 46   |

| 28  | Unijunction Transistor Schematic and Equivalent Circuit.                       | 47   |

| 29  | Variation of Unijunction Base-One Resistance with Emitter Current.             | 49   |

| 30  | Unijunction Discharge Time versus Emitter Circuit Capacitance.                 | 49   |

| 31  | Typical Unijunction Input Characteristic Near Peak Point.                      | 49   |

| 32  | Block Diagram of Unijunction Triggering Method.                                | 52   |

| 33  | Unijunction Triggering Circuit.                                                | 52   |

| 34  | Oscillogram of Unijunction Interbase Voltage, $V_{\mbox{\footnotesize{BB}}}$ . | 54   |

| 35  | Oscillogram of Unijunction Discharge Spike in Interbase Voltage.               | 54   |

| 36  | Emitter Follower Equivalent Circuit.                                           | 57   |

| 37  | Emitter Follower Amplifier Circuit.                                            | 58   |

| 38  | Emitter Follower Stage Voltage Gain.                                           | 60   |

| 39  | Diode Zero Reference Circuit.                                                  | 62   |

| 40  | Silicon Diode Forward Transfer Characteristics.                                | 63   |

| 41  | Generalized Zero Reference Circuit.                                            | 63   |

| 42  | Emitter Follower Zero Reference Circuit.                                       | 66   |

| 43  | Zero Reference Circuit Input Waveform.                                         | 66   |

### LIST OF SYMBOLS

amperes C capacitor  $C_{c}, C_{e}$ Q-Transporter stage collector and emitter capacitors, respectively D diode Ε supply voltage  $e_{o}(t)$ output voltage Storage counter circuit output voltage  $e_n$ Storage counter feedback (error) voltage  $e_{\mathbf{r}}$ f frequency transistor hybrid parameters;  $h_{fe}$ ,  $h_{ob}$ ,  $h_{ib}$ ,  $h_{rb}$ h I,i current  $I_{c}, I_{e}$ transistor collector and emitter currents, respectively  $I_e, I_p$ electron and positive ion probe currents, respectively  $\mathbf{I}_{\mathrm{CO}},\mathbf{I}_{\mathrm{EO}}$ transistor leakage currents; collector to base and base to emitter, respectively Unijunction transistor peak emitter current  $I_p$ total probe current  $I_{\rm TP}$  $I_z$ Zener diode reverse current multiplier (=  $1 \times 10^3$ ) K  $K_{0}, K_{1}$ fixed scale factors k Boltzmann's constant multiplier (= 1 x 10<sup>6</sup>) M

multivibrator

ΜV

multiplier (=  $1 \times 10^{-3}$ ) positive ion density in the ionosphere  $q^{II}$ number of steps in stairstep voltage sweep  $P_q, P_v$ percentage change in charge and voltage, respectively Qn Transistor no. n Q,q charge q unit of electric charge unit electric charge/Boltzmann's constant = 1/11,600 q/k R resistor, resistance Unijunction Transistor Interbase resistance  $R_{BB}$  $R_{B_{l}}$ Unijunction Transistor Base-One resistance  $R_{B_2}$ Unijunction Transistor Base-Two resistance Emitter Follower Amplifier emitter resistor  $R_{\rm E}$ effective series resistance of signal generator  $R_{g}$ input resistance  $R_i$  $R_{T.}$ load resistance multivibrator high-level output resistance  $R_{MV}$ output resistance  $R_{\odot}$ "plasma resistance"  $R_{o}$  $R_{SAT}$ transistor collector to emitter saturation resistance transistor equivalent circuit resistances  $r_h, r_c, r_e$ switch no. n  $S_n$ s, sec. seconds T,t time

temperature

$T_e$ electron temperature in the ionosphere arbitrary reference time  $T_{o}$ U(t) Unit Step Function V,v voltage, volts Unijunction Transistor Interbase voltage  $V_{\mathrm{BB}}$  $V_{be}$ transistor base-emitter voltage  $V_{c}, V_{e}$ transistor collector and emitter voltages, respectively  $\Lambda^{\text{CBO}}$ maximum rated transistor collector to base voltage  $\Lambda^{D}$ diode voltage  $V_{in}$ input voltage  $V_{n}$ negative supply voltage V<sub>O</sub> output voltage  $g^{V}$ Unijunction Transistor peak emitter voltage  $V_{R}$ Zener diode reverse voltage  $V_{z}$ Zener diode reverse reference voltage α normal transistor current gain current averaged transistor current gain  $\alpha_{N}$ normal transistor current gain  $\alpha_{\mathsf{T}}$ inverted transistor current gain (collector and emitter terminals interchanged)  $\Delta V$ ,  $\Delta q$ change in voltage and charge on output capacitor, C, resulting from single operation of Q-Transporter stage, respectively δV Probe electrode voltage  $\epsilon$ small voltage change Unijunction Transistor Intrinsic Standoff Ratio η

$\mu$  multiplier (= 1 x 10<sup>-6</sup>)

RC or RL circuit time constant

$\phi_{\mathrm{c}},\phi_{\mathrm{e}}$  Transistor collector and emitter junction voltages, respectively

$\Omega$  ohms

#### I. INTRODUCTION

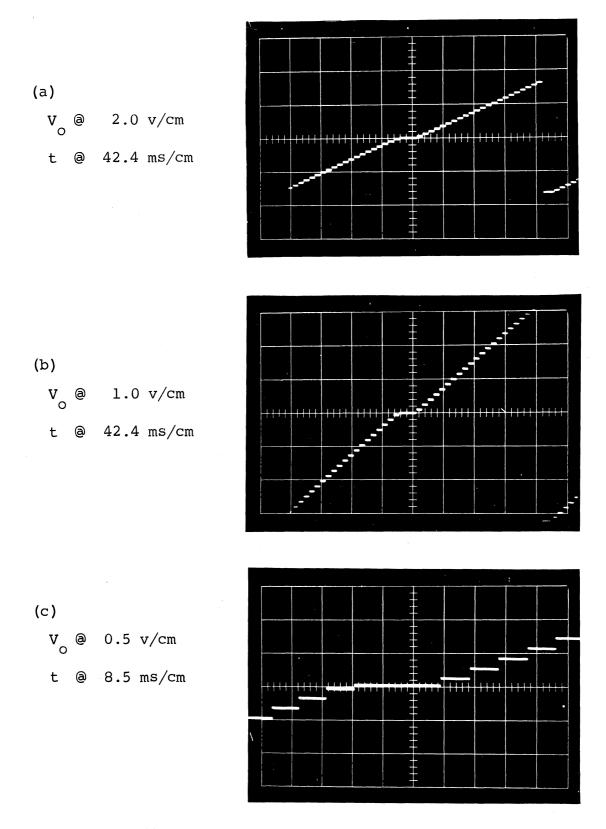

This report describes the development of a transistorized stepped voltage source to be used to implement electrostatic ionospheric probe experiments conducted by the Space Physics Research Laboratory of The University of Michigan, Department of Electrical Engineering.

A description of the experiment and the theoretical considerations pertaining thereto can be found in Scientific Report No. JS-1 of The University of Michigan's Office of Research Administration, dated August, 1961. Summarized briefly, the report describes how electron temperatures  $(T_e)$  and ion densities  $(N_p)$  in the ionosphere are deduced from measurements made by a rocket-launched instrumentation package, the sensor of which operates as a Langmuir probe. Part of the theoretical problem is establishing a region in which the electric fields are such that the desired quantities ( $N_D$  and  $T_e$ ) can be most directly related to the voltage,  $\delta V(t)$ , applied across a set of electrodes and the resulting plasma current, I(t). This includes the formidable problem of adequately describing the perturbation of the field due to the presence of the instrumentation hardware, and/or mitigating this effect by appropriate compensation techniques, often done with guard electrodes. When this is done, separate and synchronized voltage sources must be provided for the two electrode pairs. These sources must be isolated because circuitous current paths would otherwise result, since all external terminals of the probe are interconnected through the plasma. The arrangement of the electrodes and their voltage sources is shown in Fig. 1 for a "Dumbbell"-shaped probe. detector measures the current to the outer hemispherical collectors.

Fig. 1. Functional Block Diagram of "Dumbbell" Probe.

Fig. 2. Single Spherical Electrode Volt-Ampere Characteristic.

and current data are then telemetered to the ground for analysis.

Each voltage source, commonly referred to as a  $\delta V$  generator, establishes a potential across its pair of electrodes in the plasma. As an electrode is driven negative, with respect to the plasma, low-energy electrons are repelled and positive ions are attracted. The electron current falls to zero at a potential that is a function of the average energy (temperature) of these particles, as in Fig. 2. In the temperature range encountered (500-3000° K), this occurs between -0.3 and -1.5 vdc. Further excursions, to about -3 vdc, serve to define the positive ion saturation region of the V-I curve. The complete characteristic of the bipolar probe, shown in Fig. 3, is obtained by alternately reversing the polarities of the electrode pairs. Thus the dynamic range required of the  $\delta V$ 's is -3 to +3 vdc.

In early experiments these requirements were fulfilled by two ganged, motor-driven potentiometers, each connected to a separate, regulated battery source, as shown in Fig. 4. This arrangement adequately fulfilled the requirements from the system point of view. The potentiometers provided linearity and duality; the motor shaft provided synchronization and adequate electrical isolation, and the batteries provided accurate reference voltages.

However, since the applied voltages vary linearly, the graphic record of the dynamic volt-ampere characteristic of the probe is a continuous curve. This feature necessitates tedious point-by-point graph reading to provide digitized data for computer solution of the pertinent variables, i.e., ionospheric electron temperatures and ion densities as a function of altitude.

Fig. 3. Volt-Ampere Characteristic of Equal Area Bipolar Probe.

Fig. 4. Motor - Driven &V Generator.

Experience with these rocket probes has shown that five minutes of flight data require some 6 man-months of data reduction time, mainly as a result of the analog to digital conversion problem implicit in the graph-reading process mentioned above.

The improvements desired in equipment or techniques obviously must not compromise present accuracy for the sake of short-term economy. Yet, from the magnitude of the time intervals cited, it can be seen that the potential economic benefits to be reaped in this area are substantial. Hence it was thought expedient to reduce this excessive time lag by programming the  $\delta V$  generators to apply a series of discrete, digitized voltages across the probe electrodes, resulting in data in a form more conveniently read from the telemetered record. The ideal waveform can be described mathematically in terms of the Unit Step Function, U(t), i.e.:

$$V_{O}(t) = K_{O} + K_{I} \left[ U(t) + U(t - t_{O}) + ...U(t - nt_{O}) \right]$$

(1)

where  $K_{\rm O}$  can be an arbitrary d-c level,  $K_{\rm l}$  is an adjustable scale factor,  $t_{\rm O}$  is the step length and n is the number of steps per cycle. Figure 5 describes this "stairstep" waveform graphically.

The following sections will discuss methods of generating this waveform, with provision for the two isolated outputs required by the experiment. Subsequently, the engineering details of the design of a circuit suitable for flight will be described.

Fig. 5. Ideal "Stairstep" Waveform.

#### II. SYSTEM DESIGN

The System Design aspects of the problem consist in the optimum tradeoff of performance specifications on the one hand, and the functional characteristics of realizable equipment, circuits, components and techniques, on the

other. At this stage, initial solutions will be attempted in terms of symbolic

"Black-Box" devices.

Initially, modifying the motor-driven  $\delta V$  generator to fulfill the new requirements was considered. Such modification would involve replacing that section of the system accounting for the linearity, i.e., the potentiometers, with a device exhibiting a discrete characteristic as a function of shaft position. This suggests a non-shorting, rotary switch. A preliminary design figure of 30 individual voltage levels per cycle  $\begin{bmatrix} n = 30 \text{ in Eq. (1)} \end{bmatrix}$ , dictated switches whose cost and physical size were too great. This, as well as subsequent system modifications reducing the volume allotted to the  $\delta V$  generators to approximately two cubic inches, directed the course of the development toward an all-electronic solid-state system.

Electronically duplicating the desirable features of the electromechanical, motor-driven switch scheme imposes two general system-type problems:

- (1) Generation of the stairstep-waveform subject to the stated volume limitations, and

- (2) Provision for dual outputs synchronized and isolated to the degree afforded by the common motor shaft.

Although an effort will be made to treat each problem individually, their optimum solutions are not independent. As a result, it is advantageous to treat the

second problem first.

### A. DUALITY

Means of satisfying the isolation and synchronization requirements for dual outputs can be divided into two categories. Either two distinct waveform generators are used as the design starting point, so that isolation is assured but synchronization must be provided, or a single waveform source is used, thereby eliminating the synchronization aspect, while complicating the isolation problem. Both approaches will be investigated below.

1. Dual Source-Identical, Isolated, and Synchronized Step Generators

If two separate electronic generators are used to obtain dual outputs, one may reasonably predict that each will be more involved in components, and hence less reliable than the electromechanical version of Fig. 4. The increased complexity suggests that some sort of voltage monitoring would be necessary for comparison of the two outputs. It is apparent from the nature of the experiment that an indication of a discrepancy between the two outputs will only confirm that the data are in error, since the relations between the measured variables,  $\delta V$  and I, are known in a useful way only under the precise guardfield condition that  $\delta V_1(t) = \delta V_2(t)$ . Therefore it is essential to use some sort of automatic feedback control to maintain the equality of step levels whenever separate generators are employed.

It is thus necessary to compare the voltages across the two isolated electrode

pairs, and to provide for feedback voltage control without introducing any mutual current paths. This is not feasible, even with high-input-impedance vacuum-tube circuits, because of the common (ground) connection between input and output in three element active devices. Therefore, without feedback voltage control and the assurance it provides, separate  $\delta V$  generators must be considered too unreliable for use in a dual system.

### 2. Single Source—Dual Output Systems

An alternative to the dual generator system is to generate a single voltage waveform and use it to drive a device that will in turn provide two identical, isolated reproductions. Two possibilities have occurred to the author: one involves the use of a dual-secondary transformer; the second makes use of switching techniques.

a. <u>Dual-Secondary Transformer</u>.—A transformer will provide dual, isolated outputs from a common source, but it is not a d-c operated device, and not directly applicable to the transfer of the 10-msec d-c pulses of Fig. 5. Therefore, modification of the input waveform is necessary to utilize the isolating features of the transformer as an output device. Specifically, it can be shown that the longest possible flat-topped wave that can be passed through a miniature pulse transformer with reasonable droop has a width of the order of 10 µsec. Therefore it would be necessary to chop each of the 30 required voltage levels into 1000 short pulses of 10-µsec duration. A block diagram of a method of implementing this idea is shown as Fig. 6.

Fig. 6. Stairstep Generator with Transformer Coupled Dual Output.

The stairstep voltage generator output would be used as the collector supply for a 100/sec multivibrator oscillator. This arrangement would act as a combined Amplitude and Frequency Modulator. The AM would alter the magnitude of the output according to Eq. (1), while the FM arises from the fact that the charging voltage of the multivibrator RC circuits also varies, thus changing the pulse width. But if the center frequency were chosen so that the minimum frequency output does not result in unduly distorted pulses, this feature could be tolerated.

A more seriously undesirable feature is the shape of the composite envelope formed by the pulses. At best, it represents only an approximation to the desired flat-topped waveform. As the chopping rate is increased to reduce droop and to afford a closer approximation, rise times and switching transients become increasingly significant and detract from the useful data-collection time per cycle. Although an acceptable solution might be

reached using this approach, it is not to be expected without considerable compromise between the quality of the stairstep waveform and the volume of the output transformer.

b. <u>Switching Techniques</u>.—A general approach to the method of switching techniques is shown in block diagram form as Fig. 7.

Fig. 7. Block Diagram of Stairstep Generator with Switched Dual Outputs.

Here a single source charges two storage devices (presumably capacitors) connected in parallel, thereby satisfying the synchronization requirement in addition to providing identical voltage amplitudes. Now d-c isolation can be achieved by activating the switches, which remove the source and separate the two output circuits. To achieve reasonable data-collection efficiency, the charging time must be kept small with respect

to the 10 msec step length.

It is clear, then, that this approach simply transfers the major system problems to the box labeled "S". Specifically, "S" must:

- (1) have an asymmetrical switching cycle of 10:1 or better.

- (2) be synchronized in some fashion with the source,

- (3) have equal and low forward impedance in both paths, and

- (4) have equal and high back impedance in both paths.

Before investigating possible means of fulfilling the above objectives, it is well to point out that the reason given above for rejecting feedback techniques, namely, that simultaneous isolation and feedback control were mutually exclusive, must now be modified in light of the time-shared case of Fig. 7. However, although realizable, neither voltage comparison nor automatic voltage control would now be necessary since both storage circuits would be in parallel while charging.

Returning to the selection of the switching unit "S" of Fig. 7, three devices deserve consideration:

- (1) relays,

- (2) transistors, and

- (3) diodes.

Both relays and transistor switches require an external synchronization connection with the source, making unreliability likely. Furthermore, isolation of 100 megohms or better is desired. This figure is far in excess of the open-circuit impedance of present-day transistor switches. While relays are capable of exceeding this specification, they are not adapted to meeting the severe duty-

cycle requirements of approximately 0.5 msec "on" and 9.5 msec "off".

Diodes, on the other hand, would be ideal from two standpoints: they can be driven to forward resistances approaching 2 ohms and reverse resistances of the order of 1000 megohms. Being passive devices, moreover, synchronization and duty-cycle would be source-controlled without additional synchronization paths.

Requirements for the step generator of Fig. 7 follow directly from the above. In addition to being stable and reliable, it must:

- (1) generate the waveform described by Fig. 5,

- (2) be capable of delivering the output in the form of low-impedance discrete pulses that can forward-bias the diode switches and charge the capacitors rapidly, and

- (3) be capable of maintaining the diodes in a high-resistance portion of their characteristic between pulses.

Having thus reached some conclusions about the duality problem, we can now turn to the other major problem - generation of the stairstep waveform itself.

### B. STAIRSTEP VOLTAGE GENERATOR

Various means of generating a stairstep waveform are suggested by a broad interpretation of the composition of the waveform shown in Fig. 5.

Three different interpretations are given below.

## 1. A Train of Unit Voltage Steps, Delayed, Added, and Stored

The stairstep waveform can be considered to be composed of a series of unit voltage steps sequentially added or accumulated by a storage device. This suggests the generation of a train of unit steps driving an adder circuit modified by a feedback loop as in Fig. 8. The suitability of such an arrangement would be largely determined by the properties of the delay device shown in the feedback loop.

Fig. 8. Unit Step Implementation of Stairstep Generator.

The characteristics of delay devices are markedly dependent on the magnitude of the time delay required, which in this case is approximately 10 msec. This immediately rules out circulating delay devices of the lumped parameter or acoustic line varieties by virtue of their size. What is required, then, is an active delay device of the multivibrator class.

The weak point of this system, however, is the adder, which must be linear over a dynamic range of at least six volts.\* Its inherent non-linearities could be compensated for by appropriate networks in the feedback

<sup>\*</sup>A conservative figure, it will develop later.

loop. Yet, regardless of compensation, the adder would introduce unreliabilities, such as drift, previously avoided by the use of discrete devices such as the square-wave pulse generator and the active delay circuit.

Fortunately, other waveform compositions are available for investigation.

## 2. Triggered Steps

The desired stairstep waveform can also be interpreted as composed of square waves added in series as shown in Fig. 9. Waves of this type could

Fig. 9. Implementation of Stairstep Waveform Considered as Sum of Square Waves

be generated by bistable multivibrators, or other gating arrangements, all of which exhibit two salient characteristics:

- (1) Accurate voltage increments could be assured since each level would be switched "ON" or "OFF" with no intermediate states possible.

- (2) Separate square wave generators and switching arrangements would be required for each voltage level desired.

These characteristics suggest an electronic duplication of a mechanical switch in that each switch position and associated voltage tap correspond to a square-wave oscillator and associated gating or trigger circuit. Therefore, such an implementation has the same limitation as the mechanical switch: excessive size. In a general effort to avoid implementations that involve duplication of circuits and components performing identical operations sequentially, step generators containing storage or delay elements are necessary.

There are single circuits that combine the separate functions of addition and storage. One that uses capacitors for storage, a diode switching network for addition, and the timing circuits of a multivibrator for delay is the storage counter,  $^1$  shown in Fig. 10. The exponential relationship between the sizes of the output steps can be eliminated by charging  $^1$  to a voltage proportional to the output voltage plus the input step. This can be accomplished by a variety of feedback techniques, one of which is shown as Fig. 11.

A derivation of the performance of these circuits is given in Appendix I. The conclusion that adequate step equality can be achieved by using feedback has great significance. For one thing, it means that the need for a linear d-c amplifier of wide dynamic range is eliminated, since this circuit embodies a method of pulse addition whereby the charge accumulated on one capacitor can be transferred to a second capacitor regardless of the latter's state of charge. This, in turn, means that the same components are utilized in generating an arbitrary number of equal steps - a feature not shared by other circuits and a virtual necessity if the volume limitations are to be met.

Fig. 10. Storage Counter Circuit with Output Waveform.

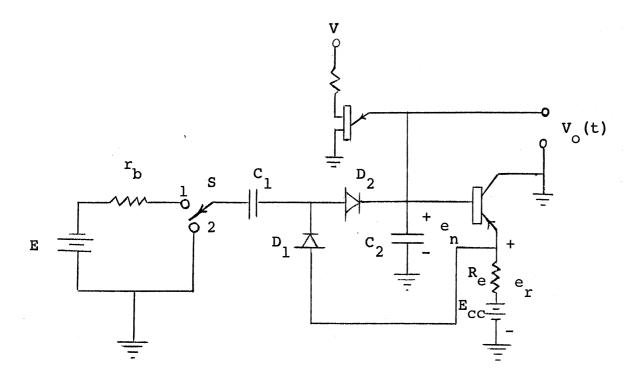

Fig. 11. Storage Counter Circuit Linearized by Feedback with Output Waveform.

However, the mechanism by which this charge transfer takes place, the familiar exponential process, never reaches steady state in any finite time. This is of negligible consequence in applications of pulse counting and frequency division for which the circuit was originally designed, but is a serious limitation in the present application, where an accurate voltage reference source is required. It will be shown below, however, that the same concept of charge transfer, combined with a faster transfer mechanism, will preserve the advantages coincident with the simplicity of this circuit.

## 3. Gated Linear Sweep

There is still another interpretation of the composition of the waveform represented by Fig. 4 that avoids duplication of circuits. This is to

consider the waveform as the limiting case of a gated linear sweep as the

charging time, t<sub>c</sub> in Fig. 12, becomes arbitrarily small.

Fig. 12. Stairstep Waveform Considered as Limiting Case of a Gated Linear Sweep.

Linear sweeps are generated by very common and well-understood circuits.

The simplest is the familiar RC integrator circuit shown in Fig. 13, where

$$e_{O}(t) = E(1 - e^{-t/RC})$$

$$= E\left\{\left[\frac{t}{RC}\right] - \frac{1}{2!} \left[\left(\frac{t}{RC}\right)^{2}\right] + \frac{1}{3!} \left[\left(\frac{t}{RC}\right)^{3}\right] - \dots\right\}(2)$$

Fig. 13. RC Integrator Circuit.

Approximate linearity can be achieved by making RC very much larger than t, so that

$$e_{O}(t) \simeq E(\frac{t}{RC})$$

(3)

To achieve periods of constant output voltage, the charging current to capacitor C must be periodically interrupted by a switch placed at point "a". Either a tube or a transistor would be a suitable gate since both can be readily controlled by an external timing device. An additional requirement on the gate is that the current through it must be independent of the voltage across the capacitor to make the step increments proportional to time. Transistors, being current-operated devices, are ideally suited to this task. Reference to a typical set of transistor output characteristic curves as in Fig. 14 shows that, over a considerable portion of the operating range, the collector current,  $I_c$ , is virtually independent of collector voltage. This property of the transistor allows its use as a gate to achieve the waveform of Fig. 12, by the circuit configuration of Fig. 15.

Ideally, when switch S is in position 1, constant base current flows, resulting in constant collector current and linearly increasing output voltage.

Fig. 14. Typical Junction Transistor Collector Characteristics.

Fig. 15. Gated Linear Sweep Circuit.

In position 2, the transistor is cut off, since B is more positive that E, with the result that the emitter current is reduced to zero and the output voltage is constant. The timing device should be sufficiently asymmetrical to make the charging time negligible. Thus a gated linear sweep approach leads to a feasible step generator and, in addition, one that requires significantly fewer components than the other methods considered. It is clear, however, that if successive step amplitudes are to be identical, the charging times (the time S is in position 1) must be maintained constant.

## 4. Q-Transporter

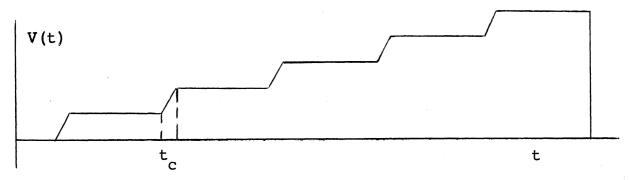

It will be observed that the gated linear sweep circuit can be considered as a modulator, where the square-wave oscillator amplitude modulates the wave-form generated by the sawtooth oscillator formed by R<sub>e</sub>, C<sub>c</sub>, and the voltage-operated reset switch. Not only must the step increments be equal, which has been the primary concern up to now, the level of each individual step must also remain constant from cycle to cycle.\* This precise recurrence of d-c levels will occur only if the square wave and sawtooth oscillators are synchronized and locked in phase. It is, of course, possible to synchronize two oscillators so they become harmonically related. When their frequency ratio becomes large, however (e.g., 30:1, as it is here), pulse-counting synchronization systems require several stages of frequency dividers. This would make the control circuit almost as large as the controlled circuit, which seems extravagant.

<sup>\*</sup>It is helpful to consider a stairstep waveform as a special case (zero velocity) of an "escalator" waveform in which the steps move progressivley up or down from cycle to cycle.

It is possible to eliminate the need for synchronization by making the length of time collector current flows independent (over a suitable range) of the period and duration of the timing pulses, so that, whenever a timing pulse is received, the gate is turned "ON" for a time that is less than, but not determined by, the duration of the timing pulse. This is accomplished by adding a capacitor,  $C_e$ , in the emitter circuit of the gating stage as in Fig. 16. Effectively, if  $R_e$  is large,  $C_e$  becomes the sole power source for

Fig. 16. Modified, Gated, Linear Sweep Circuit.

the transistor. Since the energy stored in  $C_{\rm e}$  is finite and discrete, the gate will remain open (conducting) during a timing pulse only as long as the emitter voltage remains greater than the base-emitter threshold of the transistor. Transistor saturation resistances are typically so low ( $\simeq$ 40 ohms) that RC circuits can be designed to decay during the duration of any reasonable

timing pulse. The discharge of the emitter capacitor,  $C_e$ , results in a pulse of collector current which deposits a discrete quantity of charge in the output capacitor,  $C_c$ , and produces a corresponding step in the output voltage. The depletion of the charge on  $C_e$  results in a quiescent cut-off condition that continues until the termination of the timing pulse. When switch S reverts to position 2, the resulting jump in base voltage unclamps the emitter voltage, which rises as  $C_e$  charges through  $R_e$  toward the supply voltage E. If steady state is achieved long before the next timing pulse, the amount of charge stored in  $C_e$  will be known and discrete. Thus the discrete increments made in the output voltage are independent of both the number of previous charging pulses and a wide range of variation in the frequency of the timing pulses.

This mode of operation of the transistor is based on the same physical principle that makes operation as a constant current source possible - yet the current is by no means constant, or even linear, by virtue of the character of the power source in the emitter circuit  $(C_e)$ . For this reason it is convenient to think in terms of charge rather than current, i.e., when  $C_e$  discharges it gives up a charge,  $q_e$ ,  $\alpha$  of which is deposited on  $C_c$  in the collector circuit during each timing pulse. Hence, I will refer to this circuit as a "Q-Transporter."

By means of the mechanism described above and the switching technique of Part IIB, a satisfactory circuit for the generation of a stairstep waveform may now be designed. Subsequent sections will deal with the engineering design problems concerned with producing an efficient, reliable, voltage- and temperature-stable package.

#### III. CIRCUIT DESIGN

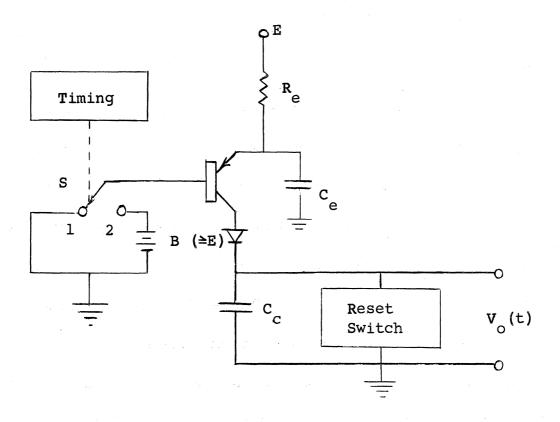

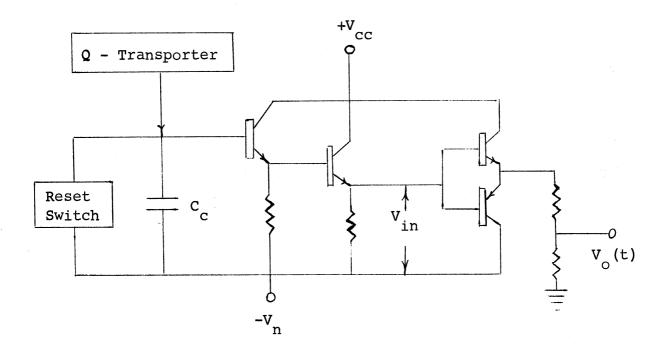

In this section the details of the Q-Transporter circuit will be examined and relations governing its use explained. A trigger circuit that provides a much sharper cutoff mechanism than base-emitter junction clamping shown in Fig. 16 is developed and an asymmetrical multivibrator timing source is given. Output circuits, such as the Unijunction voltage-operated reset switch, a low output impedance emitter follower amplifier and a zero reference circuit, are discussed in detail. Finally, power-supply requirements are treated and provision is made for compensation of random voltage and temperature changes.

## A. Q-Transporter

As noted above, the fundamental property of junction transistors whereby collector current is independent of collector voltage for constant emitter current forms the basis by which equal voltage steps are generated. This property is depicted graphically by the static collector characteristic curves and described analytically by the equations of Ebers and Moll:<sup>2</sup>

$$I_{e} = \frac{\alpha_{I} I_{CO}}{I - \alpha_{N}^{\alpha} I} \exp \left[ \frac{q \emptyset_{C}}{kT} - 1 \right] - \frac{I_{eO}}{1 - \alpha_{N}^{\alpha} I} \exp \left[ \frac{q \emptyset_{e}}{kT} - 1 \right]$$

(4)

$$I_{C} = \frac{\alpha_{N}^{I}_{eo}}{I - \alpha_{N}^{\alpha}_{I}} \exp \left[ \frac{q\emptyset_{e}}{kT} - 1 \right] \frac{I_{CO}}{1 - \alpha_{N}^{\alpha}_{I}} \exp \left[ \frac{q\emptyset_{C}}{kT} - 1 \right]$$

(5)

where  $I_{co}$  and  $I_{eo}$  are the collector and emitter saturation currents, respectively;  $\alpha_N$  and  $\alpha_T$  are the normal inverted current gains, respectively;  $\phi_c$  and  $\phi_e$  are the collector and emitter junction voltages, respectively; T is the temperature in degrees Kelvin and q/k = 1/11,600.

These equations describe the operation of the transistor's pair of "internal diodes" in terms of the external currents. They are valid for large (d-c) input signals in all three operating regions: cutoff, active, and saturation. For current values at which the internal IR drops significantly alter the junction voltages, equivalent circuit analysis techniques, employing linear circuit elements, can be used in conjunction of the above relations.

Solving Eqs. (4) and (5) for  $\mathbf{I}_{\mathbf{c}}$  in terms of  $\mathbf{I}_{\mathbf{e}}$  yields:

$$I_{C} = I_{CO} \left[ 1 - \exp\left(\frac{q\emptyset_{C}}{kT}\right) - \alpha_{N} I_{e} \right]$$

(6)

For the operation contemplated, the collector junction will always be reversed biased, so that  $\phi_c$  will be negative. The exponential term will be less than .005 and hence negligible compared to 1, for  $\phi_c$  less than -0.155 volts at  $T = 65^{\circ}\text{C}$ , the highest operating temperature expected. Thus, if the transistor is operated in regions where the collector junction is reversed biased by more than 0.155 volts, the following simplication can be made:

$$I_{c} = I_{co} - \alpha I_{e} \tag{7}$$

At this point a preliminary calculation is helpful to show the critical approximations and the criteria by which the optimum commercial transistor will be selected. Assume that in Fig. 16 the base-emitter junction is abruptly forward-biased so that collector current flows as given by Eq. (7). From the nature of the emitter source ( $C_e$  charged to voltage  $V_c$ ), it is evident that  $I_e$  will be of the form  $I_1e^{-t/\tau e}$ . ( $I_1$  = maximum permissible emitter current).

Thus:

$$I_{c} = I_{co} - \alpha I_{1} e^{-t/\tau e}$$

(8)

and

$$\mathcal{E}V_{O} = \frac{Q_{C}(t)}{C_{C}} = \frac{1}{C_{C}} \int_{0}^{T} I_{C} dt$$

$$= \frac{1}{C_{C}} \int_{0}^{T} (I_{CO} - \alpha I_{1}e^{-t/\gamma}e) dt$$

$$= \frac{I_{CO}T}{C_{C}} - \frac{\alpha I_{1}}{C_{C}} (1 - e^{-T/\gamma}e)$$

$$(9)$$

where  $\alpha I_1$  is negative for current flow out of the PNP transistor shown and where  $C_c$  will be determined by other considerations to be at least 1.0 $\mu$ fd. T, the duration of the charging period, and  $\tau_e$ , the emitter-base circuit time constant, will subsequently be shown to be approximately 60 and 40  $\mu$ secs respectively. Typically, values of  $I_{co}$  and  $I_1$  for the silicon PNP transistor 2N1036\* are 0.005  $\mu$ a and 20 ma, respectively. At 65°C,  $I_{co}$  will have increased to about 0.4  $\mu$ a, which is still four orders of magnitude less than  $I_1$  thus making the first term of Eq. (9) negligible during the charging phase when  $I_1$  exists.

The question of leakage currents cannot be ignored, however, since  $I_1$  is zero during most of the cycle. The effect of leakage currents during these periods will be treated in Section V on Error Analysis. But since under the most adverse temperature conditions  $I_{co}$  is negligible compared to  $I_1$ , the analyses can be extended by use of the linear equivalent circuit, which is commonly introduced for small signal a-c analysis. However, the assumption of small excursions about a stable operating point, commonly made in an a-c analysis, is by no means justified here. In fact, the operation contemplated will traverse

<sup>\*</sup>Manufacturers' ratings and equivalent circuit parameters for all transistors used are given in Appendix II.

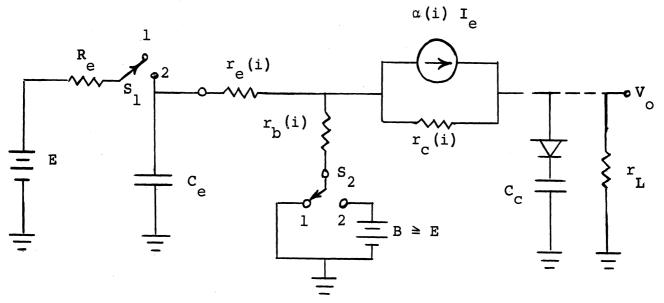

such an expanse of the operating region that substantial changes in the equivalent circuit parameters will result. The equivalent circuit of Fig. 17 is none-theless extremely useful for establishing an important feature of the "Q-Transporter"; changes in the equivalent circuit parameters, resulting from bias current changes that appreciably alter the linearity of operation, will not affect the independence of collector current on collector voltage, provided that the junction-biasing conditions required by the Ebers and Moll equations are satisfied. The parameters of the equivalent circuit are shown to be functions of the bias currents and it is assumed that current-weighted average values exist for any operating path. For the PNP transistor shown, with both switches in position 2,  $I_e = 0$ , if B is greater than E. During this phase,

Fig. 17. Q-Transporter Equivalent Circuit.

$C_e$  charges through  $R_e$  toward the supply voltage E. When both switches are changed to position 1,  $C_e$  discharges into the input impedance,  $h_{ib}(i) = r_e(i) + (1 - \alpha)r_b(i)$ , of the transistor causing  $I_c = \alpha(i)I_e$  to flow in the collector circuit. When the current flow is terminated, either by equilibrium

between the voltages across  $C_e$  and  $C_c$  or by externally activating the switches,  $C_e$  will have lost a charge proportional to its change in voltage, whereas  $\alpha$  of this charge appears across  $C_c$  and  $(1-\alpha)$  is dissipated in the input circuit resistance. Thus:

$$\Delta \mathbf{v}_{o} = \frac{\Delta \mathbf{q}_{o}}{\mathbf{c}_{c}}$$

$$= \frac{\bar{\alpha} \Delta \mathbf{q}_{i}}{\mathbf{c}_{c}}$$

$$= \bar{\alpha} \Delta \mathbf{v}_{\mathbf{C}_{\mathbf{e}}} \frac{\mathbf{c}_{\mathbf{e}}}{\mathbf{c}_{\mathbf{c}}} \tag{10}$$

where

$$\overline{\alpha} = \frac{\int_{i=0}^{I} \alpha(i) i_{e} di}{\int_{i=0}^{I} i_{e} di}$$

(11)

is a current-weighted average which one would expect to be a constant somewhat less than  $\alpha.$

The significant result is with the form of Eq. (10). Anticipating future problems with variations in temperature, one could elect to sacrifice a possible voltage gain at this point in favor of making  $C_{\rm e}$  identical to  $C_{\rm c}$ . Thus, if placed in comparable thermal circumstances, the output would be:

$$V_{o} = \overline{\alpha} \wedge V_{c_{o}}$$

(12)

which is independent of the choice of temperature coefficients of both capacitors. Although this would permit the use of inexpensive capacitors for  $C_{\rm e}$  and  $C_{\rm c}$  as long as a matched pair could be obtained, it is an uneconomical solution from other standpoints. The value of  $C_{\rm c}$  will be dictated by the maximum droop that can be tolerated when load current is drawn from it. The value of  $C_{\rm e}$ , on

the other hand, cannot be selected independently of the circuitry by which its charge is replenished between pulses. It will be shown in the next section that the conflicting requirements of minimum step droop and minimum power consumption can best be resolved by matching the temperature coefficients of the two capacitors so that their ratio remains invarient, but need not necessarily be unity as first assumed.

### B. TRIGGER CIRCUIT

In connection with implementing the base switch, labeled "S" in Fig. 15, it is assumed that a square-wave voltage source is available to provide the "Timing" pulses.

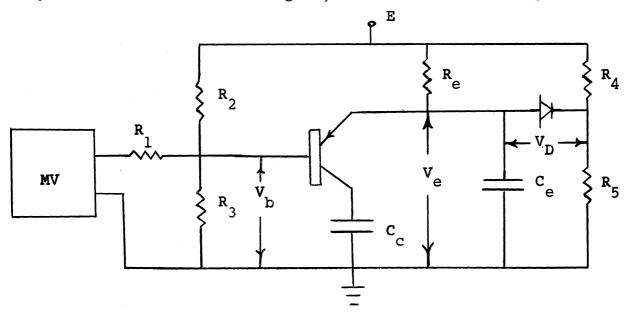

Consider first the circuit of Fig. 18, where an unilateral voltage divider

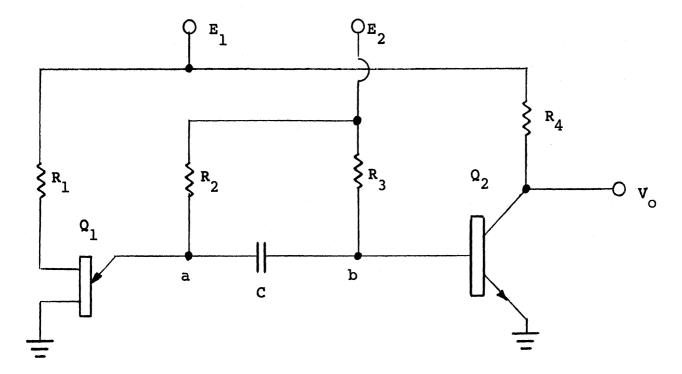

Fig. 18. Q-Transporter Trigger Circuit.

network has been added across  $C_e$  to permit charging to a steady-state voltage other than E. To find a relationship between the quiescent base voltage,  $V_b$ , and the voltage,  $V_e$ , to which the emitter is clamped by the divider,  $R_4$  and  $R_5$ , when the base-emitter junction is reverse-biased and steady-state conditions exist, one can write for the emitter voltage:

$$V_e = V_{C_e} = \frac{R_5}{R_4 + R_5} E + V_D$$

(12)

and for the base voltage:

$$v_{b} = \frac{R_{3}'}{R_{2} + R_{3}'} \cdot E + V_{D}$$

(13)

where:

$$R_3' = \frac{R_3 (R_1 + R_{MV})}{R_1 + R_3 + R_{MV}} \simeq R_3$$

(14)

since  $R_{MV}$ , the multivibrator open circuit resistance, is about 5 megohms, while the other resistances are of the order of several kilohms each. Thus the junction voltage is:

$$v_{be} = v_b - v_e$$

$$= \left(\frac{R_3}{R_2 + R_3} - \frac{R_5}{R_4 + R_5}\right) E + v_D \quad (15)$$

It will be observed that Eq. (15) is linear and that the coefficient of E contains two terms of opposite sign. Thus the partial derivative of  $V_{be}$  with respect to E could be made to vanish by appropriate choice of the resistors. This would make the junction voltage independent of supply voltage variations. Proceeding formally,

$$\frac{g_{\rm E}}{g_{\rm N}} = 0 \tag{16}$$

requires that:

$$\frac{R_3}{R_2 + R_3} = \frac{R_5}{R_4 + R_5} \tag{17}$$

Since both voltage dividers are to have the same ratio, Eq. (17) suggests the possibility of (1) making the corresponding resistors equal, and (2) using the same components for both voltage dividers.

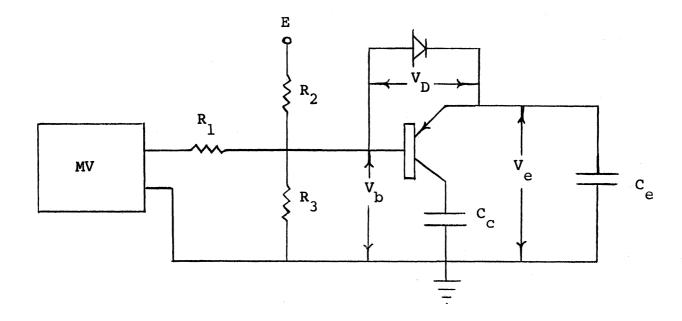

The latter can be achieved by the circuit shown in Fig. 19, which, in addition to consolidating the two voltage dividers, eliminates the separate emitter resistor,  $R_{\rm e}$ . While the nature of the emitter voltage clamp has been

Fig. 19. Modified Q-Transporter Trigger Circuit.

changed from shunt to series to effect the consolidation, the repetitive property of the steady-state emitter voltage is preserved. Moreover, the diode paths connecting the base to the emitter, while bilateral, are mutually exclusive, so that discreteness of the transfered charge is assured.

The dynamic behavior of this circuit will now be investigated. Assuming that steady-state base and emitter voltages have been achieved, consider the instant the multivibrator switches "ON," changing its output impedance from  $R_{mv}$  to  $R_{SAT}$ , the collector to emitter saturation resistance (typically 40 ohms). If the switching is fast enough so that  $R_{SAT}$  can be considered a constant, the new base voltage will be:

$$v_{b}' = \frac{R_{3}''}{R_{2} + R_{3}''} E$$

(18)

where:

$$R_3'' = \frac{(R_1 + R_{SAT}) R_3}{R_1 + R_{SAT} + R_3} \approx \frac{R_1 R_3}{R_1 + R_3}$$

(19)

If  $V_e$  exceeds  $V_b$  plus the threshold voltage of the forward-biased emitter-base junction (approximately 0.4 volts for silicon transistors), emitter current begins to flow:

$$I_e = I_O (1 - e^{-t/RC})$$

(20)

where:

$$R = h_{ib} + R_3$$

(21)

and:

$$I_o = (1-\alpha) \frac{V_e - V_D - V_b}{R + R_{SAT}}$$

(22)

The time constant of the exponential term describes the rate of charge transfer between  $C_e$  and  $C_c$ . It can be seen that realistic values of resistance in Eqs. (19) and (21) indicate that R will not be less than 250 ohms. For  $C_e$  equal to 1.0  $\mu$ fd, the minimum value of charge transfer time constant,  $\tau_{\min}$  will be approximately 250  $\mu$ s. Thus it takes 1 msec (or 12% of the desired step duration) for the output voltage across  $C_c$  to reach 98% of its target value. Some improvement could be realized by reducing  $C_e$ , but this is not feasible for other reasons.\* In any event, the basic problem of asymptotic charging and discharging of capacitors would still not be solved. The reader will recall that this is what led to the decision to reject the storage-counter circuit of Section II.

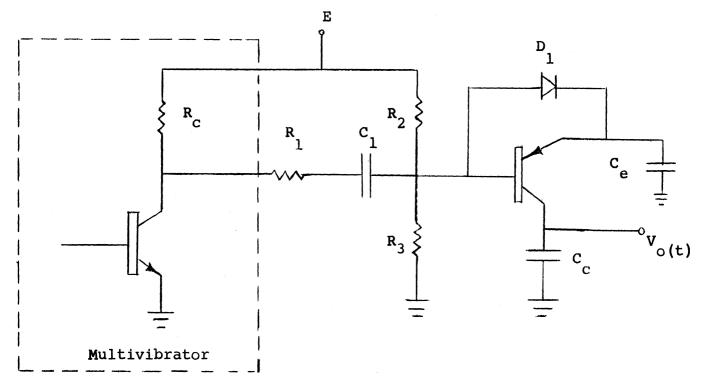

A charge-transfer circuit which reaches its target value in 1.0% of the step duration can be obtained by adding a capacitor in series with  $R_1$ , as in Fig. 20.

<sup>\*</sup>Primarily the need to match the temperature coefficient of Cc.

After a trigger pulse this capacitor,  $C_1$ , would be charged (by the base current but mainly by the supply voltage through  $R_2$  and  $R_{\rm SAT}$ ) so as to return the base voltage exponentially to the quiescent cutoff value,  $V_{\rm b}$ . By proper selection of the time constant associated with the rise in base voltage, the exponential decay of the voltage across the emitter capacitor could be limited to the region of the first time constant, where the rate of charge transfer is

Fig. 20. Complete Q-Transporter Trigger Circuit.

maximum. Moreover, in addition to the high efficiency attained thereby, the sharp cutoff mechanism would exclude operation in the region of low junction voltages, where the temperature-dependence of the exponential term in Eq. (20) is significant.

However, to be effective in controlling the duration of charge transfer period, it is obvious that  $\mathbf{C}_1$  can exert critical influence over the step size, especially with variations in its nominal capacitance with temperature. Hence

it is advantageous to include in the circuit provision for a temperature compensation mechanism. In addition to the choice of temperature coefficient for  $C_1$ , additional flexibility can be achieved by the use of a temperature-sensitive resistor (thermistor or sensistor) for  $R_1$ . This resistance would also serve to limit the peak trigger current (through the multivibrator collector circuit) below the rated maximum of 20 ma. Note in Fig. 20 that between pulses  $C_1$  will charge through  $R_c$ ,  $R_1$ , and  $R_3$  to:

$$V_{C_1} = E - V_b = \frac{R_2}{R_2 + R_3} E$$

(23)

Thus, when the multivibrator switch saturates, the instantaneous maximum charging voltage will be:

$$V_b + V_{C_1} = E$$

(24)

Hence the minimum value of  $\mathbf{R_{l}}$  required to limit  $\mathbf{I_{c}}$  (max) to 20 ma is:

$$R_1 = \frac{E}{0.02} - R_{SAT} - \frac{R_2 R_3}{R_2 + R_3}$$

(25)

which is typically 1.5 kilohms.

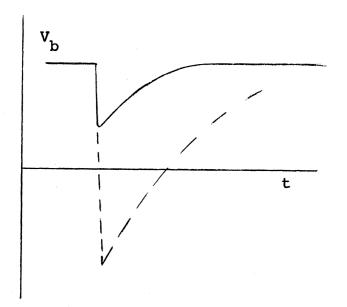

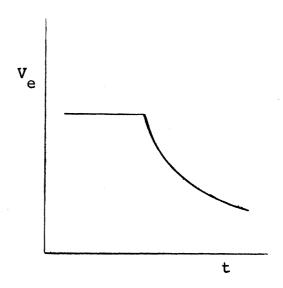

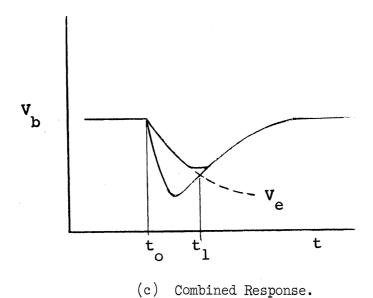

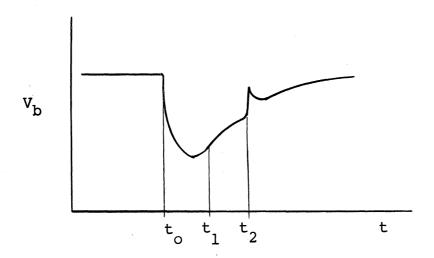

Figure 21(a) shows the effect of a trigger pulse at time  $t_0$  on the base waveform. Since the voltage across  $C_1$  cannot change instantaneously, the base voltage starts to drop toward minus  $V_{C_1}$  in a time determined principally by the transistor fall time. But even as the voltage falls,  $C_1$  begins to charge through the rapidly diminishing multivibrator output impedance. The minimum base voltage attained is shown in Fig. 21(a) as about 4.5 volts below  $V_b$ , the steadystate value. This change takes place in, typically, 10  $\mu$ sec. The base voltage then begins to rise according to the base time constant:

$$T_{b} = (R_{1} + R_{SAT} + \frac{R_{2}R_{3}}{R_{2} + R_{3}}) C_{1} \approx 30 \text{ µsec.}$$

(26)

(a) Base Voltage Response to Negative Trigger Pulse (b) Discharge of Emitter Capacitor Following Trigger Pulse

Fig. 21. Q-Transporter Base Waveforms.

(d) Overshoot Exceeding Quiescent Value.

(e) Overshoot Used to Accelerate Recovery, Without Exceeding Quiescent Value.

Fig. 21 (Concluded)

toward  $V_b$ . As soon as the base voltage has dropped more than 0.4 volts, the emitter-base junction of the Q-Transporter stage begins to conduct, and the emitter voltage,  $V_e$ , decays with time constant:

$\gamma_{e} = \frac{C_{e}C_{c}}{C_{e} + C_{c}} R_{CE} \approx 50 \text{ µsec.}$  (27)

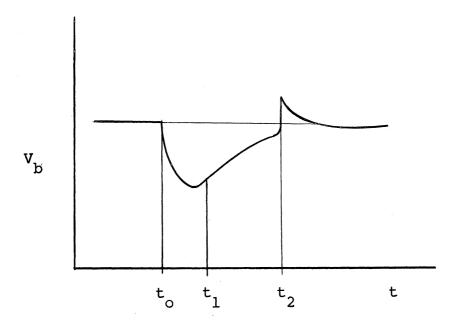

as shown in Fig. 21(b). The emitter decay continues until the base and emitter voltages converge to within the 0.4 volt junction threshold, at which point,  $t_1$ , the Q-Transporter is abruptly reverse-biased and collector current ceases. Sketches of these two voltages are shown superimposed in Fig. 21(c) to exhibit the sharp cutoff mechanism. Once the transistor has been cut off, diode  $\mathbf{D}_{\mathbf{l}}$ is forward-biased and  $C_{\rm e}$  begins to charge, in parallel with  $C_{\rm l}$ , toward  $V_{\rm b}$ . At some point, to, along the exponential rise, the multivibrator reverts to its initial open circuit impedance of  ${\rm R}_{\rm MV}.$  If the switching were instantaneous, the base voltage would immediately overshoot to (1 +  $\frac{2R_3}{R_2$  +  $R_3$ ) E, causing no change in the state of the Q-Transporter stage but altering the voltage to which  $C_{\mathbf{e}}$  is charged, as shown in Fig. 21(d). The amplitude of the overshoot is a function of the magnitude of  $C_{1}$  and hence is temperature-dependent. Furthermore, the variation with temperature is such as to augment rather than mitigate other thermal variations. It is evident that any direct measures taken to suppress this overshoot would also desensitize the circuit to the trigger pulse. However, if the "ON" time of the multivibrator is adjusted so that the overshoot occurs while the base voltage is low enough so that the increase is still less than V<sub>h</sub>, the overshoot will actually accelerate the recharging of C<sub>e</sub>. Figure 21(e) shows the base waveform with the multivibrator "ON" time so adjusted. The multivibrator frequency and asymmetry are determined once the step length and "ON" time are specified. The emitter circuit time constant,  $\tau_e$ , must be much less than the "OFF" time to avoid dependence of step size on multivibrator frequency and to justify the assumption of steady-state conditions prior to the trigger pulse at  $t_0$ .

In addition to establishing the emitter-circuit charging time constant,  $\mathbf{R}_{2}$  and  $\mathbf{R}_{3}$  in series form a voltage divider that sets the quiescent base voltage,  $V_{\rm b}$ , and the steady-state d-c level of  $C_{\rm e}$ . Clearly this level must exceed the maximum voltage to be accumulated on  $\mathbf{C}_{\mathbf{c}}$ , the output capacitor. The maximum output voltage, in turn, is determined by the properties of the voltage-operated reset switch used to discharge  $C_{\mbox{\scriptsize c}}$  at the end of each sweep, as well as the magnitude of the supply voltage, E. The maximum voltage swing is determined in Part D of this section to be approximately 17 volts. Thus  $\mathbf{V}_{\mathbf{b}}$  must exceed this value. While it is advantageous to make both R2 and R3 small to reduce the recharging time of  $C_{\mathrm{e}}$ , this increases the d-c power loss through the series combination to ground. Hence a trade-off is required between power loss on the one hand and charging time on the other. If the recharging of  $C_{\mathrm{e}}$  could be completed in 7 ms after the trigger pulse, an 8-ms step length would allow a 12.5% margin of safety against decreases in multivibrator period. Since such changes are associated with increases in supply (battery) voltage, the margin appears ample. Thus, once the value of  $\mathrm{C}_{\mathrm{e}}$  is determined,  $\mathrm{R}_{\mathrm{2}}$  and  $\mathrm{R}_{\mathrm{3}}$  can be calculated. . The selection of  $C_{\mathrm{e}}$  is related to the choice of  $C_{\mathrm{c}}$  through the temperaturecompensation aspect of Eq. (10), while  $\mathbf{C}_{\mathbf{c}}$  is determined in Section V from a consideration of step droop. The value of  $C_1$  is based on considerations discussed on pages 33 and 34, where it was shown that it is the principal variable in  $\tau_{\text{b}}.$ For a sharp cutoff characteristic, the base and emitter time constant,  $\tau_{\rm e}$  and Tb, should be comparable. If there is an appreciable difference between them, the slope of the longer will approach zero, so that the shorter time constant will be the sole determinant of cutoff. The degree of freedom that does exist,

allows considerable flexibility in the choice of  $\mathrm{C}_1$  on the basis of physical dimensions, step size, and temperature coefficient. Of these, the temperature coefficient is by far the most important consideration, since it permits compensating for the appreciable variation in the voltage drops across  $\mathrm{D}_1$  and the emitter-base junction with temperature. The multivibrator collector-supply voltage can then be used as a fine adjustment of the step size.

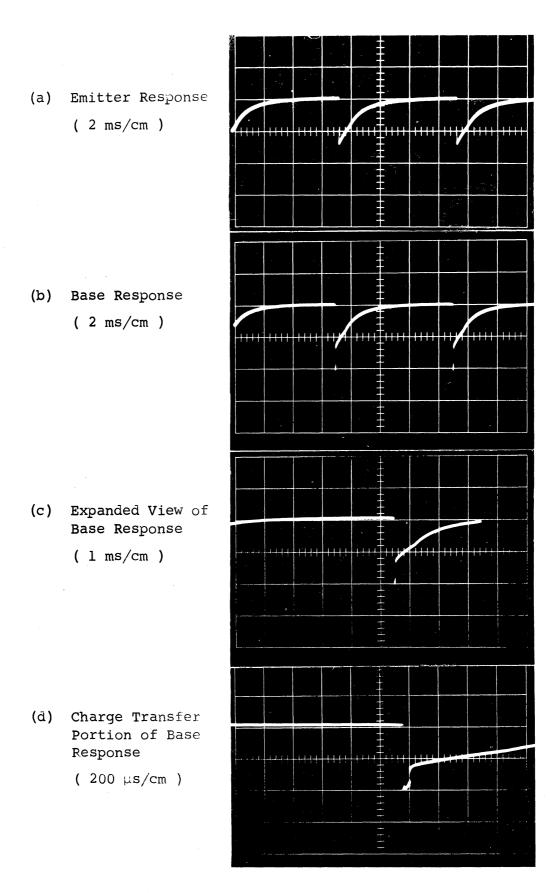

For convenience, a summary of the dependence of the various parameters of this section is given below as Table I; Table II lists typical component values. Details of the step-generation process, depicted graphically in Fig. 21; are given explicitly in Table III and illustrated by means of the oscillograms of Fig. 22, where the sharp cutoff can be seen. The point at which the multivibrator reverts to the high impedance position  $(t_2)$  is visible as a change in the slope of the recharging portion of Fig. 22(c). The partially discharged emitter capacitor,  $C_{\rm e_1}$  exhibits such a low impedance at this time that it suppresses the overshot that would otherwise occur. The duration of the charge-transfer period, the sharp cutoff mechanism, and confirmation of steady-state conditions prior to triggering at  $t_{\rm o}$ , are all apparent in Fig. 22(d). Figure 23 displays the stairstep output voltage obtained from the Q-Transporter circuit.

### TABLE I

SUMMARY OF Q-TRANSPORTER AND TRIGGER STAGE DESIGN CONSIDERATIONS

- (1) Maximum rated multivibrator collector current determines the minimum value of  $\mathbf{R}_{\mathbf{l}}$  .

- (2) Maximum acceptable step droop as well as physical size and temperature coefficient determine value and type of the capacitor used for  $C_c$ .

- (3) Necessity of matching temperature coefficients suggests making  $C_{\rm e}$  identical to  $C_{\rm c}$ , while pressure to reduce recharging time requires use of a smaller value.

- (4) The product of voltage-operated reset switch intrinsic standoff ratio and the supply voltage magnitude ( $\eta E$ ) determines the minimum quiescent base voltage  $\begin{pmatrix} R_3 \\ R_2 + R_3 \end{pmatrix}$ .

- (5) Minimum power loss in  $R_2$  and  $R_3$  on the one hand and minimum recharging time for  $C_{\rm e}$  on the other serve with no. 4 to define  $R_2$  +  $R_3$ .

- (6) Desired step size as well as system-temperature coefficient determine choice of  $C_1$  (coarse) and  $R_1$  (fine).

TABLE II

Q-TRANSPORTER AND TRIGGER CIRCUIT COMPONENT VALUES

TABLE III

Q-TRANSPORTER STEP-GENERATION SEQUENCE (To be used in conjunction with Figs. 21 and 22)

|   | Note                     |               |            |            |             | А         | Д          | ೮         |               |

|---|--------------------------|---------------|------------|------------|-------------|-----------|------------|-----------|---------------|

|   | VD                       | nonconducting | cutoff     | . <b>:</b> | Ε           | saturated | conducting | cutoff    |               |

|   | L LC                     | O.            | rising     | max        | Ξ.          | 0         | 0          | 0         |               |

|   | RCE                      | high          | falling    | min        | <b>E</b> 17 | high      | =          | E         | TIS .         |

| • | Base-Emitter<br>Junction | cutoff        | conducting | saturated  | Ξ           | cutoff    |            | =         | CYCLE REPEATS |

| • | $ m ^{R_{MV}}$           | high          | falling    | min        | =           | E         | rising     | high      |               |

|   | Condition                | quiescent     | MV "ON"    | = .        | Ε           | CUTOFF    | MV "OFF"   | quiescent |               |

|   | Time (µs)                | 0             | 0-15       | 15         | 15-60       | 09        | 800        | 0009      | 8000          |

Q-Transporter stage cuts off.  $C_1$  and  $C_2$  begin recharging in parallel. Note A:

Nonlinear resistance of diode increases, slowing charging of  $\mathbf{C}_{\mathbf{e}}$  . Multivibrator changes state, causing overshoot in base voltage. Note B:

Note C: Charging of Ce completed.

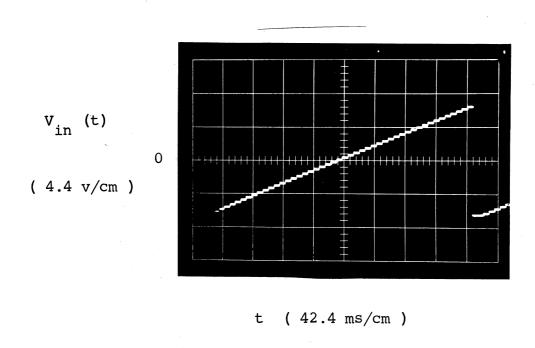

Fig. 22. Q-Transporter Response to Trigger Pulse.

(All vertical scales 2 volts per centimeter)

t (20 ms/cm)

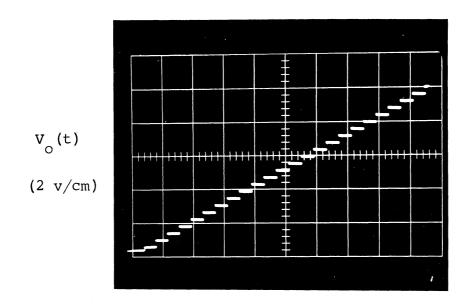

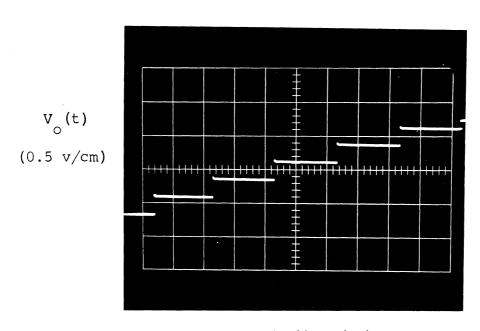

(a) Stairstep Output Waveform

t (4 ms/cm)

(b) Expanded View of Output Waveform

Fig. 23. Q-Transporter Output Waveform.

#### C. MULTIVIBRATOR DRIVER CIRCUIT

The switching times required for efficient step generation with independence of supply voltage variations have been specified in Part B of this section with the aid of Fig. 21. The following is a discussion of the properties of an astable solid-state multivibrator to meet the requirements for the "Timer."

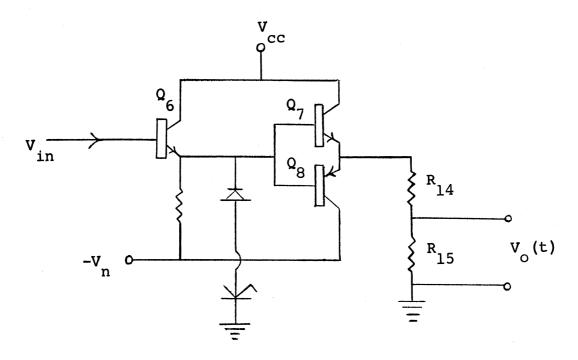

As previously mentioned, it is desirable to use the multivibrator frequency as a means of independent control over the step length and hence the repetition frequency of the stairstep output waveform. The most convenient means of exerting frequency control without affecting the degree of asymmetry is by varying the collector supply voltage. On that basis, a multivibrator of 9:1 asymmetry and base frequency of 70 cps at a nominal collector voltage of 13 vdc was designed using conventional methods. Figures 24 and 25 show the circuit configuration and output waveform, respectively, of this multivibrator.

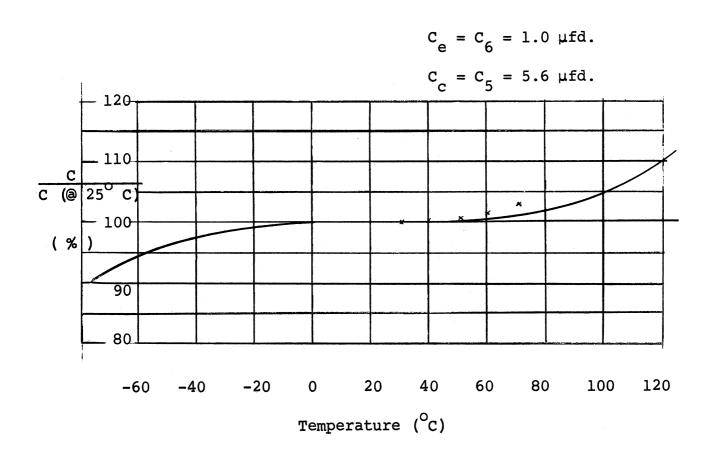

The temperature variation of the circuit, exclusive of capacitors, was then evaluated by placing the entire circuit, except for the capacitors, in an environmental oven. The resulting variation in the output frequency of the circuit is shown in Fig. 26. The variation is due principally to the temperature dependence of  $I_{\rm CO}$  and  $V_{\rm be}$  of both transistors. This variation was then matched by capacitors of opposite coefficients, while the resistors were adjusted for the desired base frequency and asymmetry. Table IV lists the component values used, and Fig. 27 shows the compensated temperature variation over a wide range of collector voltages.

TABLE IV

# MULTIVIBRATOR COMPONENT VALUES

Figure 24: Multivibrator Circuit.

t (2 ms/cm)

Fig. 25. Multivibrator Output Waveform

Fig. 26. Multivibrator Temperature Characteristic.

Fig. 27. Temperature Compensated Multivibrator Characteristic.

## D. VOLTAGE-OPERATED RESET SWITCH

Throughout the preceding, it has been tacitly assumed that a means of rapidly removing the charge accumulated on the output capacitor,  $C_{\rm c}$ , was available. Indeed, blocking oscillator and gas thyrathron circuits are quite commonly employed as voltage-operated switches. A solid-state equivalent of the thyratron is the Unijunction Transistor (formerly called the Double-Based Diode). 4,5 It is small and has a high discharge-current capability.

The applicable schematic and equivalent circuits for this device are shown in Figs. 28(a) and (b), respectively. The internal ohmic path (27K)

Fig. 28. Unijunction Transistor Schematic and Equivalent Circuits.

between the base-two and base-one terminals draws a steady-state direct current from the voltage source E, and establishes an open circuit voltage of

across the emitter and base-one terminals (input) by ordinary voltage divider action. For inputs less than  $V_{BB}$ , the PN emitter junction is reverse-biased and exhibits the high impedance characteristic of such diodes. If the externally applied voltage,  $V_{C_{\mathbf{C}}}$ , is raised, the point will be reached where the emitter junction becomes forward-biased and current begins to flow from the emitter to base-one. Further increases in applied voltage will not raise the emitter voltage,  $V_{\mathbf{e}}$ ; on the contrary,  $V_{\mathbf{e}}$  actually decreases. The emitter current,  $I_{\mathbf{e}}$ , however, increases because  $R_{B_1}$  exhibits a negative resistance characteristic above a peak forward-current value,  $I_{\mathbf{p}}$ . The forward-biased input characteristic of this device is stable until a critical value of emitter current greater than  $I_{\mathbf{p}}$  is reached. Avalanche multiplication of base-one carriers then occurs, decreasing  $R_{B_1}$  according to Fig. 29.

Currently available commercial units are rated to pass peak discharge currents of 2 amperes. Figure 30 depicts the discharge time as a function of emitter capacitance. For  $C_{\rm c}$  greater than 1.0  $\mu{\rm fd}$ , the exponential discharge exhibits an equivalent emitter-to-base-one series resistance of about four ohms, and typically takes approximately 200  $\mu{\rm sec}$ . This is about 3% of a typical step length.

The most seriously undesirable feature of this device is the variation of its input impedance (emitter to base-one) in the vicinity of the firing

Fig. 29. Variation of Unijunction Base-One Resistance with Emitter Current.

Fig. 30. Discharge Time versus Emitter Circuit Capacitance.

Fig. 31. Typical Unijunction Input Characteristic Near Peak Point.

point,  $V_p$ , as depicted in Fig. 31. The current multiplication mechanism by which the rapid discharge takes place is actually a current-operated phenomenon rather than the voltage-controlled mechanism suggested above. Of course this is really just another aspect of the same thing, but the current-biased description is more revealing in this instance—as it is for solid-state devices in general. Initiation of the current multiplication process requires an emitter current of from 2 to 100  $\mu$ a, depending on the value of the interbase voltage,  $V_{BB}$ . Even for fixed values of interbase voltage, the emitter current required for avalanche breakdown exhibits considerable statistical deviation among specific Unijunctions. Thus the input terminals could draw up to 100  $\mu$ a from the input capacitor  $C_c$  without initiating breakdown. For a 5.6- $\mu$ fd input capacitor and an 8.0-ms step length, this results in a 1% droop on the last step before reset occurs. Previous steps would suffer proportionally less droop according to Fig. 31.

Two distinct methods of mitigating this effect are available. One is to increase the step size so that the knee of the input resistance curve, Fig. 31, is traversed in a single step. The second is to apply an external triggering signal either to raise  $V_{\rm e}$  or to lower  $V_{\rm p}$  by lowering  $V_{\rm BB}$ , thereby inducing premature firing.

The first approach requires considerable modification of previous circuits. For a fixed number of steps an increase in step size increases the output swing and hence requires the addition of an output attenuator to realize the required levels. It will be shown subsequently that increasing the step size is desirable to facilitate establishing an unambiguous reference when the output voltage passes through zero. In the next section it will be shown that the principal

limitations in step size are the available supply voltages and the maximum reliable collector breakdown voltage ratings of the transistors. Therefore it is advantageous to consider the method of controlled breakdown by the application of a trigger pulse to one of the Unijunction terminals. Base-two is the terminal best suited to this role; any circuitry attached to the emitter would be additional loading on the output capacitor and would itself contribute to the droop, while application of a trigger signal to base-one would require the addition of a series impedance in that circuit which would increase the discharge time. It can be seen from the equation relating the firing voltage  $V_{\rm p}$  to the interbase voltage  $V_{\rm BB}$ :

$$V_{p} = V_{d} + \eta V_{BB} \tag{29}$$

(where  $V_d$  is the diode drop) that a reduction in  $V_{BB}$  by a factor  $\epsilon$  would reduce  $V_p$  and cause the emitter to fire if  $V_e$  (= $V_c$ ) exceeded  $V_d$  +  $\eta$  ( $V_{BB}$  -  $\epsilon$ ). Due to the storage effects at the junction, the duration of the triggering pulse must exceed 0.6 µsec for pulse amplitudes of about two volts. This signal could be obtained from a separate timing source (multivibrator or sawtooth oscillator), but a more reliable solution is to derive the trigger from existing waveforms. Since  $\epsilon$  is to be negative, it could be obtained from the collector waveform of the multivibrator that triggers the Q-Transporter stage as in Fig. 32. The latter introduces a 180° phase shift that causes a positive signal (the step) of about one-half volt to appear at the emitter terminal of the Unijunction. This, combined with a simultaneously applied two-volt negative trigger signal capacitively coupled to the base-two terminal, would quickly traverse the knee of the firing curve (Fig. 31).

Fig. 32. Block Diagram of Unijunction Triggering Method.

Fig. 33. Unijunction Triggering Circuit.

<sup>\*</sup>R $_2$  of this Section is so designated to permit ready reference to the literature.  $^4,5$