#### ENGINEERING RESEARCH INSTITUTE UNIVERSITY OF MICHIGAN ANN ARBOR

LANGUAGE CONVERSION FOR DIGITAL COMPUTERS

#### General Introduction

and

### Volume I

$\underline{\text{The}}$   $\underline{\text{Logical}}$   $\underline{\text{Realization}}$   $\underline{\text{of}}$   $\underline{\text{Transliterative}}$   $\underline{\text{Functions}}$

bу

ARTHUR W. BURKS

CARL'H. POLLMAR

DON W. WARREN

JESSE B. WRIGHT

Project M828

BURROUGHS ADDING MACHINE COMPANY DETROIT, MICHIGAN

1 June 1952

engn umrog40

#### ABSTRACT

The aim of this report in general is to present some theories concerning code conversion and the design of code conversion equipment for digital computers.

Volume I deals with a restricted type of character-to-character conversion represented by the <u>Transliterative Function</u>. Such conversions do not require remembering previous states nor any time-space transformations. Some theory and a number of effective techniques are given for designing the required equipment—such design being presented at a level of considerable logical abstraction.

The remainder of the report, to be published subsequently, will cover the following topics:

Volume II will discuss the use of various types of equipment—tubes, relays, etc.—as means (1) for carrying out the logical designs of Volume I, and (2) for effecting more general code conversions and format conversions—e.g., those involving serial-parallel transformations, shift codes, etc.

Volume III will present detailed proofs and some relevant discussion of two topics presented in Volume I, concerning (1) minimal networks—in particular, the Balanced MS Net, and (2) the theory behind and validity of the technique for folding trees.

#### TABLE OF CONTENTS

## LANGUAGE CONVERSION FOR DIGITAL COMPUTERS

|                                                                                                                                                      | Page                 |

|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| ABSTRACT                                                                                                                                             | ii                   |

| GENERAL INTRODUCTION                                                                                                                                 | iv                   |

| VOLUME I. THE LOGICAL REALIZATION OF TRANSLITERATIVE FUNCTIONS                                                                                       | . 1                  |

| Section 1. Introduction                                                                                                                              | 1                    |

| Section 2. Definition of Logical Elements and Networks                                                                                               | 3                    |

| Section 3. Logical Design of Networks                                                                                                                | 9                    |

| <ul><li>3.1. Conjunctive Switches: MS (Multiplicative Switches) and MS Nets</li><li>3.2. Alternative Switches Using Other Logical Elements</li></ul> | 9<br>22              |

| Section 4. Techniques for Realizing Transliterative Functions                                                                                        | 25                   |

| 4.1. Decoding Functions 4.2. Encoding Functions 4.3. Arbitrary Transliterative Functions 4.4. Modifications to Provide Pulse Output                  | 27<br>30<br>31<br>36 |

| Section 5. Characteristics of Function Switches                                                                                                      | 39                   |

| 5.1. Element Input Count and General Loading Properties 5.2. The Folded Tree Technique                                                               | 39<br>43             |

| Bibliography                                                                                                                                         | 53                   |

| Index of Terms                                                                                                                                       | 54                   |

# (To be published subsequently)

VOLUME II. THE PHYSICAL REALIZATION OF CODE AND FORMAT CONVERSIONS

VOLUME III. MINIMAL SWITCH THEORY AND THE FOLDED TREE

#### LANGUAGE CONVERSION FOR DIGITAL COMPUTERS

#### General Introduction

It is the purpose of this report to make a general survey of code and format conversion. This will not be a complete survey of the problem, but only a preliminary investigation which is designed to make clear the general nature of the problem, to formulate some of the chief available techniques, and perhaps to serve as a foundation for more detailed studies of such conversions and the design of equipment therefor.

Code conversion is a special case of language translation, and it is useful to consider it in this light. While no sharp lines can be drawn between what is normally called a code conversion and an ordinary linguistic translation (e.g., German to English), the difference can be indicated roughly. Basically, a code conversion is a translation at the character level, while an ordinary linguistic translation takes place at the sentence level. Later in this section the concept of message transliteration will be defined; put in terms of this concept, the difference is that code conversions are primarily message transliterations, while ordinary language translations are not.

In accounting work the initial data and end result are expressed in a natural language whose alphabet (in this part of the world) consists of Latin letters, Arabic numerals, and a few auxiliary characters such as the dollar sign. Since electronic and electro-mechanical circuits generally work most easily in a binary system, most machine languages have two basic characters: represented in this report by '0', '1'. Thus, an adequate machine language is an artificial language with two basic characters (bits), which characteristically represents alphanumeric characters by relatively short sequences of bits so chosen that the translation between the natural language and code (and hence between codes) is essentially a message transliteration.

It should be noted that many machine languages are not quite binary but are <u>almost</u> so. Consider for example a representation of data on a magnetic tape which is six channels wide. On such a tape there is a natural grouping of bits into sequences of six; the edges of the tape constitute, so to speak, parentheses. This grouping provides information in the technical sense of that term, since a machine when turned on in the middle of a message finds, not a continuous sequence of O's and 1's, but

rather a sequence of clearly defined sequences each of which consists of six 0's and/or 1's. The same point holds with regard to the usual organization of characters into "words" inside a machine.

Thus a typical machine language has two primary basic characters ( 0 and 1 or their equivalents) and sometimes secondary basic characters—e.g., ) or its equivalent . As a consequence it is convenient in discussing code conversion to apply a notion of character broader than that of basic character. For example, in discussing the tape language mentioned above it is often convenient to regard the characters not as 1's and 0's but as ordered sextuples of 1's and 0's . For the purposes of this report and from a syntactical point of view, a language L consists of character-type\* class, C , and formation-rule class, F , determining a set of message types  $\{M\}$  , each message being a finite sequence of character-tokens of class C :  $m_1,\,m_2,\,\ldots,\,m_n$  .

Though code conversion is largely a matter of syntax rather than of semantics, it should not be overlooked that a language has a semantic (meaning) dimension, as well as a syntactic (formal) one. The concluding statement of the previous paragraph does not constitute an entirely adequate definition of 'language' because, among other things, it ignores this dimension. Thus the statement in question does not establish the proper identity (or diversity) criteria for codes. For example, there are two teletype codes, each comprised of the same character-type class (thirty-two five-bit sequences) and the same formation-rule class (i.e., the same sequences of characters are allowable messages in both), which nevertheless are different because different five-bit sequences ( 01000 and 00101 ) are employed to represent a '#'.

Not all the syntax of a machine language is represented by the use of basic characters other than  $\,$ 0 and  $\,$ 1  $\,$ 0 often, perhaps usually,

As used herein, the terms 'character-type' and 'character-token' are synonymous with the terms 'character-design' and 'character-event', respectively. Since there is no standard terminology on this point, either set of terms seems permissible although 'type' and 'token' would appear to be preferable to 'design' and 'event' for the following reasons. First, the former terminology is older (cf. The Collected Papers of Charles Sanders Peirce, vol. IV, paragraph 537) and an existing terminology should not be changed without due cause. Second, 'type' and 'token' may be used alone as abbreviations for 'expression-type' and 'token-type', whereas 'event' and 'design' are somewhat misleading. Third, it is often desirable in semantic work to take as a token, not a single event (e.g., a single reading of 'red'), but a substantive or sequence of events (e.g., one occurrence on a given page of a specific token of a book throughout the life of that book).

syntax is represented by sequences of bits in the same way that alphanumeric characters are represented. Thus, spaces, paragraphs, indentations, and various kinds of brackets that occur in a message written in a natural language may be coded in the same way that alphanumeric characters are coded. There is an interesting consequence of this: namely, a coded "message" can contain two or more syntactical structures. Consider as an example a message written in a natural language which is organized into unequal-length words, sentences, paragraphs, and pages. This message can be translated into a machine language which is organized syntactically into equal-length words and blocks in such a way as to preserve the syntactical structure of the original message, in the sense that the original message can be recovered by translating back into the natural language. Thus the coded machine representation of the original message contains both the original syntactical structure and the syntactical structure of the machine language.\*

The concept of translation can now be applied to languages whose characters are finite sequences of two basic characters. Consider two languages, L and L', consisting of character-type classes, C and C', and formation-rule classes, F and F', determining sets of message-types  $\{M\}$  and  $\{M'\}$ . Any function,  $\emptyset$ , which maps  $\{M\}$  into  $\{M'\}$  is called a translation function. Such a function is called reversible if and only if

$$\mathbf{M}_1 \cdot \neq \mathbf{M}_2 \cdot \stackrel{\checkmark}{=} \cdot \phi(\mathbf{M}_1) \neq \phi(\mathbf{M}_2) \cdot$$

If  $\phi$  is a reversible translation function from L to L' , no information is lost in translating by means of it; that is, any message  $\mathrm{M}_1$  may be completely recovered from its translation  $\phi(\mathrm{M}_1)$  .

In this report we are interested only in translation functions which are reversible or almost reversible. Furthermore, we are not interested in all such functions. Thus translation functions such that for long messages M any character of M' requires for its determination simultaneous storage of all characters of M , or even such that the first character  $m_{\hat{1}}$  cannot be produced until all of M is scanned, are not very useful from the point of view of mechanized accounting. However, we know of no sharp lines dividing the translation functions which are useful in mechanized accounting from those that are not. The most that can be said is that the interesting translation functions belong either to the special

See for example the internal language of the Michigan report, The Languages for an Electronic Accounting System, Sec. 2.3.1 and 2.3.2.

<sup>\*\*</sup> For example, the translation discussed in the report previously cited is not completely reversible. E.g., 37.00 and 37 would both translate into the external language as ... 037.000.

class of message transliteration functions (to be defined below) or strongly resemble members of this class.

It is now possible to define the concept of a <u>transliterative function</u>: a single-valued function whose domain and range are sets of finite sequences of O's and I's —each set (domain and range independently) consisting of sequences of equal length. (Later this definition will be restricted to exclude non-information-carrying bits—see section 4.)

Consider now a translation function  $\emptyset$  from L to L' which is explicitly defined as follows:

$$\phi(m_1,m_2,\ldots) = \Psi(m_1), \Psi(m_2),\ldots$$

where  $\Psi$  is a transliterative function and  $m_1, m_2, \ldots$  is an arbitrary message of L (the individual  $m_i$  being character-tokens of class C of L ). Any function,  $\emptyset$  , so defined is a message transliteration function.

So far, the format arrangement of a message has not been discussed. Indeed it will be noted that our concept of translation function has no place for changes in format, since any two messages which differ only in format arrangement will be related to one another by the identity translation function. However, it may be assumed for the present that the messages are transmitted a character at a time, bits of a sequence representing a character—an m; -all being available at one time (compare the definition of a language given earlier). Under these circumstances a message transliteration could be most simply executed as a character-by-character translation. For this purpose the following kinds of equipment would be required: (1) a function switch to realize  $\Psi$  , (2) memory for one character, (3) whatever memory is needed for buffering purposes (i.e., velocity matching), and (4) a few fairly simple control circuits. Since we are interested in code conversions that are message transliterations, or nearly so, it is clear that a function switch is an essential part of all code converters discussed in this report. But function switches have other uses than in code conversion, so it seems desirable to study function switches per se. This will be done in Volume I.

Function switches may be realized (constructed) with various circuit elements: relays, vacuum tubes, mechanical lever arrangements, etc. Not all such elements are equally flexible, however. For example, crystal rectifier "and's" and "or's" cannot be combined as freely as can, say, d-c vacuum-tube "and's" and "or's". On this account it is useful to think of the designing of a function switch as progressing through three stages. The first is the construction of an abstract logical design based on logical operation. The second is the translation of this design into one in terms of elements which are idealized representatives of equipment. The

theory developed by Shannon (6, 3, 4, 12), Aiken (11), and Brown and Rochester (8) is essentially at this second level, for to a large extent they base their work on relays, tubes, and diodes, respectively. The third stage is the construction of the complete circuit design with all details indicated that are needed for actually assembling the physical switch. The last of these three stages is beyond the scope of the present report. The first two stages will be treated in Volumes I and II, respectively.

In code conversions which are not message transliterations, memory circuits often play a more dominant role. For example, if the incoming message is expressed in a shift code, the last shift character to have occurred must be remembered. Again, in converting from unequal-length to equal-length numbers an incoming number must be scanned (and hence remembered) before it can be positioned properly and before dummy characters can be added. It should be noted that while such a converter realizes a non-trivial translation function (one in which it is not the case that  $\phi(M) = M$ ) it requires only a rudimentary function switch, so that the circuit emphasis is upon memory. For this reason it is doubtful that it should be called a "code converter" at all. It is perhaps more properly called a "format converter".

There are other conversions which doubtless should be called format conversions and not code conversions. All merely space-time conversions fall in this class: e.g., a "serial-serial to parallel-parallel conversion". The translation function governing such a conversion is completely trivial, since for all messages, M ,  $\emptyset(M) = M$  (at least if the ordinary concept of character is maintained), and it is for this reason that such conversions are not properly called code conversions. Nevertheless, any study of code conversion should be extended to include these format conversions for two reasons. First, such conversions involve the same kinds of equipment as are required for code conversion. Thus in a "serial-serial, parallel-parallel" conversion, where the instantaneous rate of flow of information out of a converter is not always equal to the input rate of flow, memory for buffering is required as well as distributing circuits for rearrangement of the data. Second, in actual practice such conversions are often combined with bona fide code conversions.\*

For these reasons it is convenient to make a rough-and-ready classification of conversion into three kinds, depending on the characteristics of the equipment required:

<u>Code Conversions</u>—those requiring primarily function switches; e.g., conversions between six-bit codes, four-eight codes, and five-bit shift codes.

<sup>\*</sup> See for example <u>The Design of the Languages for an Electronic Accounting System</u>, Sec. 2.3.2 and 2.3.3; and <u>The Program Translations</u>: <u>Tape Language</u> to Internal Language.

Format Conversions—those requiring primarily memory units and distributing and arranging equipment; e.g., space-time conversions and simple equal-length—unequal-length conversions.

Code-and-format Conversions—those requiring a substantial amount of both function switch equipment and memory and distributing equipment; e.g., a conversion from a serial-parallel, unequal-length-word, five-bit shift code to a parallel-parallel, equal-length-word, four-eight code.

It is desirable to have a single name for all of these conversions. 'Language translation' seems too restrictive, since a mere format conversion hardly involves a translation between two different languages. On the other hand, 'language conversion' seems satisfactory, since 'conversion' is flexible enough to cover all the cases, and we are certainly dealing with languages.\*

Another example of a conversion that is both a code and a format conversion is that between the coded language and the internal language designed by the Michigan Project.\*\* In fact, an appreciable proportion of the translation which will occur in a highly developed automatic accounting system is of a comparable degree of complexity. Under these circumstances one would expect in a report of this character a discussion of the logical design of converters for all three types of conversion. But it must be remembered that general design techniques for such converters are being discussed rather than the design of specific converters. Now the logical components of code-and-format converters are the components of code converters and format converters as well. Hence it seems fairly sufficient at this level of generality to discuss the design of code converters and format converters, omitting any detailed discussion of codeand-format converters as such. An additional reason for this omission is that any example of a code-and-format converter is likely to constitute enough material by itself for a fairly substantial report. In reading this report, however, it should be kept in mind that the individual code converters (Volume I) and format converters (Volume II) are emphasized primarily because this seems a suitable way of discussing the logical components (and their interconnections) for all three kinds of converters.

<sup>\*</sup> The term 'language conversion' was suggested by Don Stevens.

<sup>\*\*</sup> See the references in the penultimate footnote preceding.

#### VOLUME I

#### THE LOGICAL REALIZATION OF TRANSLITERATIVE FUNCTIONS

#### 1. Introduction

Volume I is a study of the design of equipment for realizing Transliterative Functions (essentially, single-valued functions of sequences of 0's and 1's of uniform length to sequences of 0's and 1's of uniform length—see Def. 4, section 4). Such devices will be called Function Switches. They may also be defined in more customary terms as IRE (1)\*\*

function switches\*\*\* modified by requiring (1) that a simultaneous application of signals to the input will cause the simultaneous appearance of the corresponding output signals and (2) that none of the auxiliary circuits for timing, pulse generating, etc., be regarded as part of the Function Switch. These requirements do not prevent the bits of a sequence from coming serially into the mechanism (of which the Function Switch is a part). The circuits for handling such an input, however, would not be part of the Function Switch proper as the term is used here.

The term Realization is formally defined in section 4. This formal meaning, however, is simply an attempt to make precise, in a particular context, the generally understood meaning of the term which is adequate for all but the most 'formal' occurrences of the term throughout the report. In general, technical terms when used in special sense peculiar to this report will be capitalized and will be underlined at the first occurrence. The index will show where the term is introduced or defined.

<sup>\*\*</sup> Such numbers appearing in parentheses after an author or term refer to the bibliography at the end of the volume.

<sup>\*\*\*</sup> The IRE definition states that a function switch is "a network or system having a number of inputs and outputs and so connected that signals representing information expressed in a certain code, when applied to the inputs, cause output signals to appear which are a representation of the input information in a different code". In the terminology of this report the IRE function switch is a "language converter".

As was pointed out in the General Introduction, the design of Function Switches is broken down into three stages: <a href="logical">logical</a>, <a href="idealized">idealized</a> equipment, and <a href="complete circuit design">complete circuit design</a>. The present volume is devoted exclusively to the first of these stages. The principles of the propositional calculus are used freely. "Logical elements" (assumed realizable in equipment) are defined having the properties of conjunction, disjunction, and nagation, and symbolic networks are constructed by "wiring" these elements together to produce switches.

The aim of the volume is achieved by first giving constructive procedures for a few basic component—or "building-block"—switches which may not in themselves constitute a useful realization technique; next, in terms of these components, defining switches for certain special kinds of Transliterative Functions; and finally, giving techniques for combining and modifying these switches to give switches realizing an arbitrary Transliterative Function. In section 2, the basic concepts used in the construction and study of the abstract logical circuits are defined. All the methods for constructing Function Switches are given in sections 3 and 4 with the exception of that for the folded tree, which is discussed in section 5 in connection with minimality and loading properties of switches.

### 2. Definition of Logical Elements and Networks

This section introduces the basic logical elements which will be combined into symbolic circuits (representing physical Function Switches) by techniques to be considered later. It gives rules for the combination of these elements into networks and places some restrictions on the types of circuits to be considered. Finally, it defines and discusses some general properties of these logical networks, which may have some significance for their physical realization and which may be used as a basis for comparison.

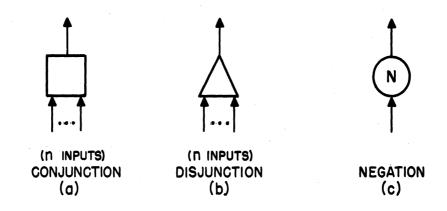

The logical operators: conjunction, disjunction, and negation, are chosen as the basic elements. It is assumed (and will be shown in a later volume) that they can be realized by physical equipment (e.g., pulse control units, relays, tubes, etc.). Each such piece of equipment is represented by a geometric figure or enclosure along with a set, W , of directed line segments associated with it (see Figure 1). The line segments correspond to the Inputs and Outputs of the physical element and will be referred to as Wires. The figure together with its wires is called a Logical Element. Consider a Logical Element, E . Let W represent the set of wires associated with it. Then the inputs of E form the subset,  $W_T$  , composed of all the wires of W directed toward E (i.e., with the arrowheads pointing toward E ). Only the inputs may be 'driven'-i.e., put into one or the other of two electrical states, '0' or '1', by connection to an outside source. Any subset  $W_{\Omega}$  of W may be denoted as the set of outputs of E provided that the union of inputs and outputs is the set W . The output will be the single arrow (wire) directed away from the Element unless otherwise specified.

The Logical Elements are defined as follows: The square in Figure 1(a) represents a piece of equipment with two or more inputs and a single output which is in the 1 state if and only if all of the inputs are in the 1 state. Thus it represents the logical operation, conjunction, and is referred to as a Conjunctive Element. The triangle of Figure 1(b) represents a Disjunctive Element: its single output is in the 1 state if and only if at least one of its inputs is in the 1 state. The circle enclosing an 'N', Figure 1(c), is a Negation Element—a device with a single input and a single output having the property that the state of the output is opposite to the state of the input.

The above three Primitive Elements are sufficient for constructing all of the networks to be considered and all such networks will be assumed,

PRIMITIVE LOGICAL ELEMENTS FIGURE I.

STANDARD NOTATION ABBREVIATED NOTATION RELAY REALIZATION

(a) (b) (c)

AN AUXILIARY LOGICAL ELEMENT

THE "DOUBLE-AND"

FIGURE 2.

in the interests of simplicity, to be compounds of these Primitives even though, in certain applications, another choice of Primitives would seem to serve as well or better.

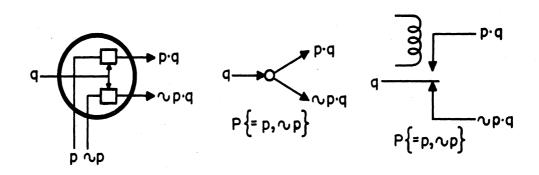

As an example of an auxiliary compound element, the <u>Double-and</u> is introduced in Figure 2. This element is a logical interpretation of the relay (Figure 2c) as it is frequently used in contact networks (cf. section 5). It is represented as a compound of Primitive Elements (Conjunctive) in 2(a) and in convenient abbreviated symbolism in 2(b). The labelling of the input pair (~p, p) represents the standard relay interpretation which is the only mode of operation to be considered.

If tubes are to be used, it is natural to define enclosures (elements) representing the stroke functions. With the proper interpretation of voltage levels, a double triode corresponds to the disjunctive and the pentode to the conjunctive stroke function; these elements are discussed in section 3.3.

Although such compound elements as the two above are of secondary importance to this report, the possibility of such alternatives deserves emphasis because of their usefulness in more specialized applications.

The Function Switches considered in Volume I will be compounded from the Logical Elements exclusively, though not all possible combinations will be considered. The allowable combinations are defined by the following rules whose primary purpose is to ensure that each output will be a function of the inputs. Such a combination is called a Network.

- 1. Any one of the Primitive Logical Elements, or—the "degenerate element"—a single wire with terminals labelled 'input' and 'output', constitutes a Network whose Inputs, Outputs, and Wires are those of the Element.

- 2. If  $F_1$  and  $F_2$  are distinct Networks with designated inputs and outputs, they can be combined to form a compound Network F as follows:

- A.1 All inputs of  $F_1$  are designated inputs of F .

- .2 Each input of  $F_2$  must be designated an input of F or it must be connected to a single output wire of  $F_1$ . (Several inputs of  $F_2$  may be connected to the same output wire of  $F_1$ .)

- .3 No other connections between  $F_1$  and  $F_2$  are permitted.

- B.1 All outputs of  $F_2$  are designated outputs of F .

- .2 Every output of  $F_1$  which is not connected to an input of  $F_2$  must be designated an output of F .

- .3 Any inputs of  $F_1$  or  $F_2$  may also be designated outputs of F .

- C. The <u>Wires</u> of F are defined to be its inputs together with its outputs.

The force of 2C is that the internal connections of a network—unless they are Network outputs—are not called Wires of  $\,F\,$  but must be referred to as Wires of the components,  $\,F_1\,$ ,  $\,F_2\,$ , etc.

The rules B.1 and B.2 (omitting B.3) define a set of outputs which is adequate for all specific Switches\* discussed in this report and will be referred to as the <u>Natural Outputs</u>. Rule B.3 will, of course, be assumed in any general remarks or theorems concerning the class of Networks.

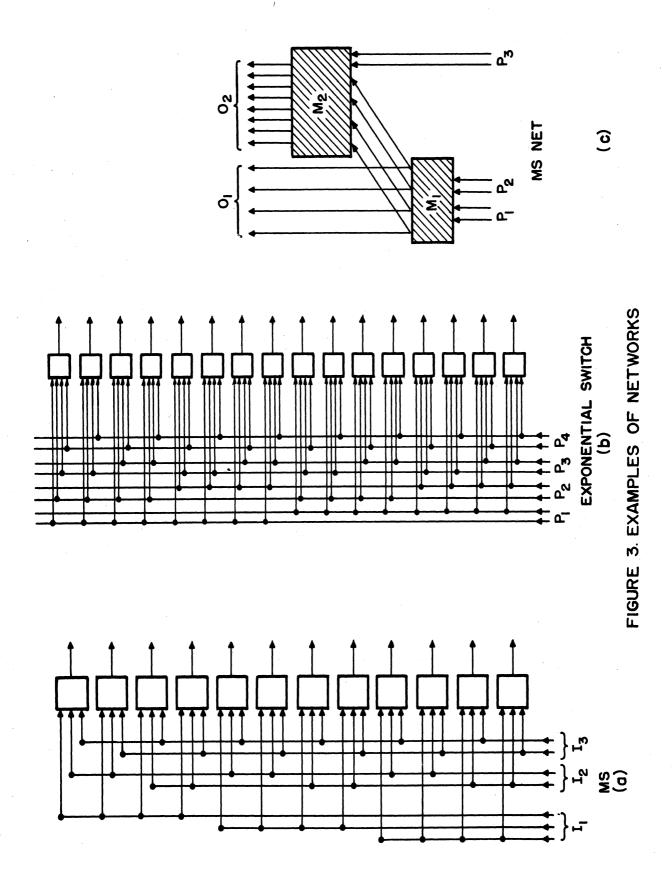

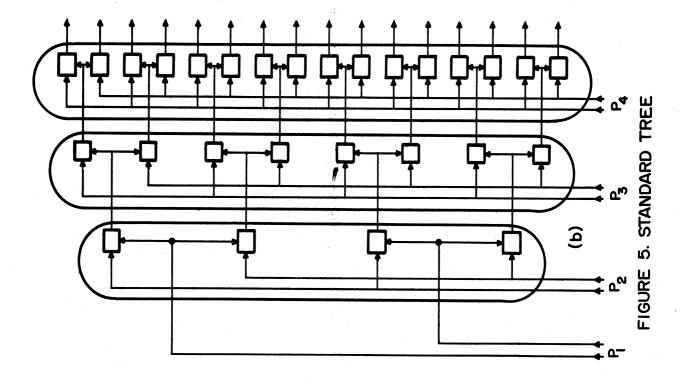

Some typical examples of Networks are shown in Figures 3a, 3b, and 5b. Figure 5c is an application of the Double-and notation to the Network of Figure 5b.

It is the philosophy of this volume to treat Networks as logical entities. Nevertheless, there are frequent allusions to concrete applications and it is to be expected that some readers will carry this translation into physical equipment even further. It should be pointed out, therefore, that the Networks are most easily interpreted in terms of static operation; i.e., the 1 and 0 signals or states of the Wires should be thought of as "high" and "low" d-c levels rather than as pulses. The ramifications of the pulse or dynamic interpretation are taken up in section 4.4.

Although the general question of which of a number of circuits or Networks is "best" for a particular job must remain unanswered (or, perhaps even unformulated), two criteria for comparison which appear to be of some use are presented below.

The first is the <u>Element Input Count</u> denoted by 'C'. It is the total number of inputs for all of the Logical Elements of the Network.

The term 'Switch' will be used frequently in referring to a specific Network.

The network of Figure 3(a) has 12 three-input Conjunctive Elements and so C=36, while the "tree" of Figure 5(b) has 28 two-input Elements and C=56. The Element Input Count is considered a rough index of the complexity of the circuit relative to the type of Element used in its construction. Its significance depends on the particular physical elements used in its realization. Thus in trees (pyramids) designed by Aiken's (1) techniques the number of control grids is a specific interpretation for the Element Input Count of the corresponding abstract circuit.

The second property to be defined is a loading property. Two types of loading are distinguished for each Input of a Network, serial loading and parallel loading. To determine the serial loading of an input q , consider the set of all sequences of Logical Elements of the Network,  $\left\{(E_1,E_2,\ldots,E_m)\right\}$  , where (1) q is an input of  $E_1$  , (2) the output  $q_i$  of  $E_{i-1}$  is connected to an input of  $E_i$  (and possibly to other elements), and (3) the output of  $E_m$  is an output of the Network. Such sequences are called Chains. (A Conjunctive Chain is one composed entirely of Conjunctive Elements.) The length of a Chain is the number of Logical Elements it contains. Pick out any Chain  $\,L$  of this set which has a length equal to or greater than that of any other Chain in the set. Then the length of  $\,L$  is defined to be the Serial Loading Coefficient of  $\,q$  .

Although no use is made of it here, it is interesting to note that the idea of serial loading may be extended by defining the "serial loading coefficient of a logical element, E" in an analogous fashion, the output of E replacing q in the definition given above.

The <u>Parallel Loading Coefficient</u> of a Network input, q, is defined as the number of Logical Elements to which q is directly connected. As in the case of serial loading, this idea may be extended to any Logical Element.

The parallel loading of an input,  $\,q\,$ , does not describe the situation completely. This can be done only by considering the parallel loading coefficients of all the Logical Elements appearing in Chains having as a first term a Logical Element with  $\,q\,$  as an input. These coefficients might be displayed in the form of a matrix to be associated with  $\,q\,$ . For the special cases to which it will be applied in this report (with one exception in section 5), the concept as defined is adequate.

The loading characteristics of a Network will be presented as a set of <u>Loading Couples</u>: number pairs, (S,P), one for each Network input, where S is the Serial and P the Parallel Loading Coefficient. In Figure 3b, the Loading Couples for all Network Inputs are the same, (1,8). In Figure 5b the loading of the two wires of a pair is the same: for a

wire of P<sub>1</sub> or of P<sub>2</sub> , the couple is (3,2); for P<sub>3</sub> , (2,4); and for P<sub>4</sub> , (1,8).

The significance of these numbers varies with the physical equipment considered for the realization. For example, in a relay tree the serial loading and the parallel loading for Logical Elements is of little significance, while the Parallel Loading Coefficient for the switch inputs is of great importance: it is the number of transfer contacts operated by an input relay. It is studied in section 5 and more extensively in Volume III. On the other hand, serial loading is of considerable interest if the circuit is to be realized by crystal rectifiers.

#### 3. Logical Design of Networks

The purpose of sections 3 and 4 is to present techniques for "constructing"—at the abstract level of design—switches which realize Transliterative Functions. It has been found possible to realize all Transliterative Functions by simple combination of a very small number of components (Switches). Since these components may have wider application than it is the purpose of this report to consider, they will be presented separately in the present section, independently of their use in realizing Transliterative Functions. In section 4 this application will be considered in detail. Section 3 will, however, anticipate the subject matter of section 4 to the extent that the components are capable, without modification, of realizing functions.

The present section will be divided into two subsections:

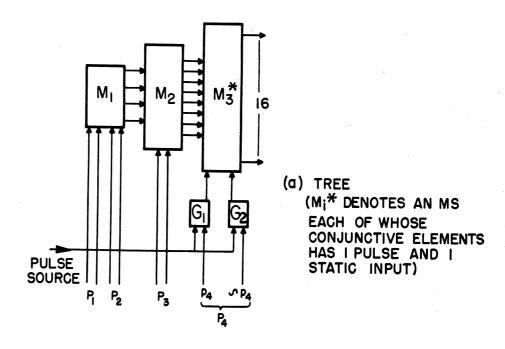

- 3.1. "Conjunctive Switches: MS (Multiplicative Switches) and MS Nets" showing first the construction and operation of these components, and, second, a more detailed discussion of two important specific examples, the "Tree" and the "Balanced MS Net".

- 3.2. "Alternative Switches Using Other Logical Elements" which describes, primarily, the use of stroke function elements.

The definitions of Switches in this section (with one exception) have the form of constructive procedures: i.e., given the proper specification of input sets, use of the rules laid down by a definition will produce a unique Switch. This aspect will be pointed out specifically for each definition as it is presented.

# 3.1. Conjunctive Switches: MS (Multiplicative Switches) and MS Nets

The Multiplicative Switch—hereafter referred to as 'MS'—derives its name from the mathematical concept <u>Cartesian Product</u>.\* The Cartesian Product idea, which is fundamental to this volume, is most frequently applied to sets of wires. To facilitate its application to Networks, a

Given a sequence,  $\mathcal{L}$ , of sets,  $S_1,\ldots,S_n$ , the Cartesian Product of  $\mathcal{L}$  is the set of all possible n-term sequences such that the ith terms of any sequence belong to  $S_i$ . Note for future reference that this operation is associative:  $(S_1 \times S_2) \times S_3 = S_1 \times (S_2 \times S_3)$ .

closely related Concept called the "Cartesian Conjunction" will be defined. Consider a Switch A , a collection,  $\mathcal A$  , of disjoint sets,  $\mathbf I_1,\ldots \mathbf I_n$  , each consisting of two or more input wires of A , and the set, O , of the output wires of A ; then

<u>Def. 1.</u> A subset, S , of O is called a <u>Cartesian Conjunction</u> of  $\mathcal I$ , denoted 'CC( $\mathcal I$ )', if there is a 1-1 correspondence between the Cartesian Product of  $\mathcal I$  and S such that if  $\mathbf w_{\rm e}$  is the wire of S corresponding to e , an element of the Cartesian Product, then all Conjunctive Chains with  $\mathbf w_{\rm e}$  as output originate in e and at least one Chain is connected to each wire of e (e.g., see Figure 3a or 5g).\*

In all the Switches explicitly discussed in this volume  ${\tt CC}(\mathcal{I})$  will be unique and will be referred to as the Cartesian Conjunction of  $\mathcal I$  although in general there may be several distinct sets which are Cartesian Conjunctions of a given  $\mathcal I$ .

The Cartesian Conjunction operation can be iterated: i.e., the  ${\rm I}_{\dot{1}}$  sets may themselves be Cartesian Conjunctions. This leads to:

$$\frac{\text{Corollary}}{(\text{CC}(\mathcal{J}_1) \text{ X}} \frac{\text{to}}{\text{CC}(\mathcal{J}_2)) \text{ X}} \frac{\text{Def. 1}}{\text{CC}(\mathcal{J}_3)} = \text{CC}(\mathcal{J}_1) \text{ X} (\text{CC}(\mathcal{J}_2) \text{ X} \text{CC}(\mathcal{J}_3)) .$$

This follows directly from the relation to Cartesian Products which is associative.

Throughout the report, the number of elements in a set or sequence, S , will be denoted by the expression N(S) . Applying this notation to the present case, clearly

$$\mathbb{N}(\mathbb{CC}(\mathcal{J})) = \prod_{j=1}^{n} \mathbb{N}(\mathbb{I}_{j}) . \tag{1}$$

The following property is also worth noting. Given an input set, I , a grouping into a collection,  $\mathcal J$  , of disjoint subsets  $I_1,\ldots,I_n$  , such that I=U  $I_j$  , and the resultant  $CC(\mathcal J)$  , it is not possible, on the same I , to form a different grouping,  $\mathcal J$ ! (of subsets  $I_j^!$ ,  $I=U^!$ ; such that  $CC(\mathcal J)=CC(\mathcal J)$ ; and, conversely, two unequal output sets

The operating condition being established here is that, to each e corresponds an output wire which is in the l state if and only if every wire of e is in the l state. Note that  $\mathrm{CC}(\mathcal{J})$ , unlike the Cartesian Product, is independent of the order of the sets in  $\mathcal{J}$ .

cannot be the Cartesian Conjunction of the same  $\mathcal Q$  . These statements follow easily from the definition of Cartesian Product.

An MS is a Switch for producing the Cartesian Conjunction—specifically:

Def. 2.\* A Multiplicative Switch (MS) is a network whose set of inputs, I, can be grouped into a collection,  $\mathcal L$ , of disjoint subsets such that  $I = \overset{n}{U} I_j$ ,  $(\mathbb N(I_j) \ge 2)$  in such a way that the set of outputs is  $CC(\mathcal L)$ , each output wire being the output of a single n-input Conjunctive Element whose inputs are the wires of the corresponding element, e, of the Cartesian Product of  $\mathcal L$ .

The constructive force of this definition is that, given an input set I and a partitioning,  $\mathcal Q$  , then one and only one MS can be produced.\*\*

Figure 3a shows an MS with the input set I of 7 wires grouped into subsets,  $I_1$  of 3 wires and  $I_2$  and  $I_3$  of 2 wires each, and with the Cartesian Conjunction represented by the 12 output wires in accordance with formula (1).

For MS's'in general the number of Logical Elements (Conjunctive) required is equal to the number of output wires,  $\prod_{j=1}^n N(I_j)$ , and the Element Input Count is given by the formula

$$C = n \prod_{j=1}^{n} N(I_{j})$$

.

<sup>\*</sup> One of the essential characteristics of a Multiplicative Switch is that every sequence of states appearing on its inputs has the same number, k , of l's . This property might be taken as the basis for defining a broader class of switches which includes the class of MS's as a subclass. Such Switches would realized Transliterative Functions whose domain sequences each have a fixed number, k , of l's , and whose range sequences, as for the MS (cf. Decoding Function, section 4), each have a single l . A switch of this class would consist of a set of k-input Conjunctive Elements, one for each sequence in the domain, the Element inputs being connected to the k switch inputs which register l's corresponding to the associated domain sequence. This type of switch would, for example, decode a 2-out-of-5 code which cannot be handled by the MS.

For this purpose, Switches with inputs or outputs permuted are not considered distinct—the problem is discussed in more detail in connection with MS Nets (last footnote, p. 19).

The Serial Loading Coefficient for any input wire is obviously 1; the parallel loading, however, is dependent on the subset,  $I_j$ , to which the wire belongs and the loading characteristic is expressed, for a wire  $w_{\overline{j}}$  of  $I_{\overline{j}}$ , by the Couple

$$(1, \prod_{j=1}^{n} N(I_{j})) \qquad (j \neq \overline{j}) .$$

E.g., for the MS of Figure 3b, the Loading Couple for any wire of  $I_1$  is (1,4); for any wire of  $I_2$  or  $I_3$ , (1,6).

The MS shown in Figure 3b deserves special mention. It is a familiar piece of decoding apparatus and is characterized by the property of having its set of input wires grouped into pairs (i.e., for all j=l, ...,n ,  $N(I_j) = 2$  ). Henceforth, such input pairs will be referred to as Polar Pairs because of the common mode of operation which uses such a pair to represent a truth value-variable (or a binary digit-position): a signal on one wire meaning 'true' (or l ) and a signal on the other meaning 'false' (or 0 ), which requires that the two wires be in opposite states, i.e., polarized. The Switch itself will be called an Exponential Switch because of the analogy between its relation to the general MS and the mathematical relation of exponentiation to multiplication.\*

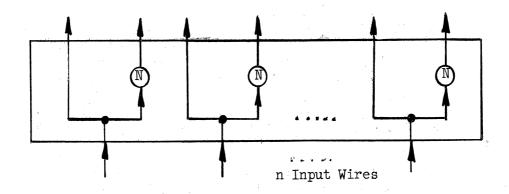

The concept of Polar Pair provides motivation for the introduction of a component which, though not itself a conjunctive switch, is frequently used as an auxiliary to such switches: the <u>Polarizer</u>. The purpose of this Network is to convert a set of inputs representing one variable per wire into the Polar Pair representation. This is done by the obvious device, shown in Figure 4, of introducing a negation element in parallel with each original wire. Clearly, given a set of inputs, the Polarizer is unique. The primary importance of the Polarizer in the development of the present theory is that it allows the existence of Polar Pair inputs to be assumed, without loss of generality, whenever it is convenient to do so.

<sup>\*</sup> The analogy is particularly interesting if the set-theoretic basis for exponentiation (as related to Cartesian Product) is considered where, letting m and n represent the cardinality of two sets,  $S_m$  and  $S_n$ , m^n is interpreted as the number of possible mappings of  $S_n$  into  $S_m$ , which is also the cardinality of the Cartesian Product,  $S_m$  X...n factors ...X  $S_m$ . The analogy can be followed through easily to produce a 1-1 correspondence between the set of mappings and the set of switch outputs. In the present case, n is, as before, the number of subsets of the set of inputs, and m is 2. Note that the definition could apply equally well for any integer, m , other than 2.  $(N(I_1)=N(I_2)=\ldots=N(I_n)=m)$ ; the restriction to m = 2 is merely to effect a slight simplification in the present report.

Figure 4. Polarizer

The final definition of this subsection provides a means for interconnecting MS's to give greater flexibility and at the same time provides limitations which keep the resultant class within reasonable bounds for purposes of analysis.

Def. 3. An MS Net is a Network composed entirely of MS's and (1) having a set of input wires, I , which can be grouped into a collection,  $\mathcal{L}$  , of subsets,  $I = \bigcup_{j=1}^{U} I_j$  , such that  $CC(\mathcal{L})$  is a subset of the set of Network outputs;\* and with the MS's connected as follows: (2) If  $I_j^M$  is a subset of the input set of an MS (as in the definition of MS) and if S is the set of outputs of an MS or one of the  $I_j$  of the MS Net, then any connection between the two sets requires that  $I_j = S$  (i.e., the two sets have the same number of wires and the wires of  $I_j^M$  are connected to those of S in 1-1 fashion). And similarly if a wire of S is designated as a Net output, then the entire set S must be so designated.

This definition is the exception to the <u>constructive procedure</u> policy. The rules of the definition do not lead to a unique switch, given specified input sets. The definition merely defines a broad class of networks to which some of the most useful Switches (e.g., Trees) belong.

<sup>\*</sup> The set of outputs of an MS Net may consist of any outputs allowed by the definition of Network which satisfy (1); however, most of the useful examples explicitly referred to will have as their designated output set the set of Natural Outputs. Similarly with inputs: only the Polar Pair case will be considered in detail.

Some of the conditions of this definition will bear amplification. The explicit requirement that the MS Net be a Network is necessary to rule out feed-back loops which are unnecessary in code transliteration. Condition (2) is of some interest and will be discussed in more detail in Volume III of this report. For the present it may be said that its purpose is to prevent Splitting of MS output sets—some wires connected to one MS sub-input, some connected to another—a situation which has thus far resisted general analysis to a degree altogether out of proportion to any advantages apparent in the procedure. It should be pointed out, however, that condition (2) does permit a phenomenon which shall be referred to as Branching: in the terms of the definition, an S , if taken in its entirety, may be identified, in the prescribed manner, with more than one  $I_{\frac{1}{2}}$  and/or be designated a Net output.

Figure 3c is an MS Net (with Branching), the shaded enclosures representing the MS's,  $O_1 = CC(\boldsymbol{\mathcal{J}}')$ ,  $\boldsymbol{\mathcal{J}}' = \{P_1, P_2\}$  and  $O_2 = CC(\boldsymbol{\mathcal{J}})$ ,  $\boldsymbol{\mathcal{J}} = \{P_1, P_2, P_3\}$ . The output set consists of the union,  $O_1$  u  $O_2$ .

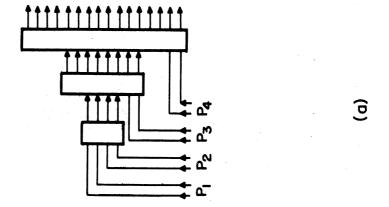

Figures 5 and 6 represent a type of MS Net which is of particular importance and is characterized by having no Branching; i.e., an MS output (or Net input) is directly connected to exactly one MS input subset or is a Net output (not both). Most MS Nets to be dealt with are of this type and will be referred to as <u>Simple MS Nets</u>. In such a Net it is easily seen that the outputs are the Natural Outputs and constitute precisely the Cartesian Conjunction of the input subsets.

The construction of an MS Net can be expressed notationally by a Construction Formula. This formula gives the output of the Net as a function of its inputs. The connective, 'X', denotes Cartesian Conjunction, a parenthesized expression denotes and MS (if an expression occurs more than once it represents a Branching of the output of the MS), and the connective, u, indicates that the Switch output set is the union of the output sets of the MS's so joined—no additional connections being made. (The symbol Pj will be used rather than Ij whenever the input subsets are Polar Pairs.)\*

The MS Net of Figure 6 for n = 4 is expressed by the formula

$$(P_1 \times P_2) \times (P_3 \times P_4)$$

(2)

Although no such cases arise in this report, it should be pointed out that the occurrence of identical MS's (i.e., described by identical Formulas) has not been provided for. The situation can be handled easily by attaching subscripts to the parentheses if distinct MS's are to be formed.

and that of Figure 3c by

$$(P_1 \times P_2) \times ((P_1 \times P_2) \times P_3)$$

(3)

The 'u' in formula (3) indicates that the output is produced by two MS's. Note that (2) represents a Simple MS Net (no Branching), since no expression is repeated, but that (3) has Branching as indicated by the repeated occurrence of ' $(P_1 \times P_2)$ '.

The associative property of Cartesian Conjunction offers a method of constructing a variety of Nets to produce the same output function. For example:

$$(P_1 \times P_2 \times P_3 \times P_4)$$

(2')

$$(((P_1 \times P_2) \times P_3) \times P_4)$$

(2")

represent alternative methods (i.e., alternative MS Nets) for realizing the output given by formula (2). Formula (2') yields the Exponential Switch of Figure 3b, and (2") the Tree of Figure 5.

Having established all of the basic conjunctive components and discussed some of their general properties, two specific MS Nets of particular importance will now be considered.

The Standard Tree. The most succinct characterization of a Standard Tree is by means of its Construction Formula,

$$((...(((P_1 X P_2) X P_3) X P_4) X ...) X P_n)$$

.

From this formula it can be seen that the input set (I) consists of a collection ( $\mathcal{Q}$ ) of n (Polar\*) Pairs, P<sub>1</sub>,...,P<sub>n</sub>; that P<sub>j</sub> is conjoined with the preceding P's by constituting one of two input subsets for an MS whose other input subset is (in effect) P<sub>1</sub> X ... X P<sub>j-1</sub>; and that the Tree output is the output of the "final" MS—the one having P<sub>n</sub> among its Inputs. It is clear, also, that the Standard Tree is a Simple MS Net, since no expression is repeated in its Construction Formula and the Formula expresses precisely CC( $\mathcal{Q}$ ).

The only mode of operation to be considered for the Tree (as well as for most other Switches) is with Polar Pair inputs; therefore it is convenient to use the  $P_j$  notation from this point on. It must be pointed out, however, that, for purposes of constructing the switch it is not intended to impose any restriction on the manner in which the inputs are energized—it is required only that the input set satisfying  $I = U I_j$  has  $N(I_j) = 2$  for all j.

As a constructive procedure, it is clear that, given the input set, I , and its collection of subsets,  $\mathcal{L} = \{P_j\}$  , a "unique" switch is determined—unique, that is, with the usual minor qualifications concerning permutations (see last footnote, p. 19).

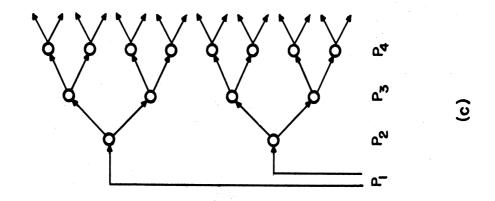

Figure 5 represents a typical Standard Tree. In 5a the basic elements are MS's. In 5b the MS's are isolated by the heavy-line enclosures and their internal Elements shown in detail. Figure 5c shows the abbreviated Double-and notation which derives its simplicity from two important characteristics of the Standard Tree: (1) the Conjunctive Elements always occur in pairs; and (2) all of the Conjunctive Elements (or, equivalently, the Double-ands) of an MS (those constituting a vertical column in the diagrams) are connected directly to one and only one P;—each such column is said to form a Bay. Characteristic (1) is common to the larger class of "Folded Trees" (which is discussed in section 5 and includes the Standard Tree), while (2) is peculiar to the Standard Tree. In Figure 5c all the Double-ands in a column are associated with the P; appearing below it.

The element input count for the Standard Tree (and, in fact, for Trees in general) is given by the formula

$$C = 8(2^{n-1} - 1) *$$

where n is the number of pairs in the input. The number of conjunctive elements is, of course,  $\ensuremath{\text{C}/2}$  .

The loading figures will be given for a  $P_{\tt j}$  , since they are identical for the two wires. Both the serial and parallel loadings vary with the input pair and are given in the usual Couple notation by  $(n\text{-}j\text{+}l,\ 2^{\tt j-l})$  for  $\tt j\geq 2$  . For  $P_{\tt l}$  the value of the Couple for  $\tt j=2$  applies. The second (parallel) Coefficient here is of special interest (particularly in relay networks), since it may become excessively large as  $\tt j$  increases. The folding process, described in section 5, is an effective method for distributing this load over the  $P_{\tt j}$  .

The Balanced MS Net. \*\* The second of the specific Switches to be described is, again, a Simple MS Net. The designation 'Balanced' is

In line with the general policy of this section, this formula is for a "static" tree. The "dynamic" tree, which is more common in the literature and which is discussed extensively in section 5 and in Volume III, has the formula  $C = 4(2^n-1)$ .

<sup>\*\*</sup> The concept of this Switch was derived from Brown and Rochester (8), where a crystal diode version was presented and discussed in somewhat unprecise language.

derived from the fact that each of its MS's has exactly two input subsets\*—  $I = I_1$  u  $I_2$ —and that  $N(I_1)$  is as nearly equal to  $N(I_2)$  as possible. Here, as in the case of the Tree, the definition is in terms of Polar Pair inputs. The switch will be defined recursively by giving rules for its construction starting with the output and proceeding systematically to the input.

The Balanced MS Net with input set  $I = \begin{bmatrix} I \\ J \end{bmatrix}$  is constructed as follows:

- l) Designate a set of  $2^n$  wires as Network outputs. They will constitute the output of a single MS with  $I=I_1$  u  $I_2$  and  $N(I_1)=2^{\lfloor (n+1)/2\rfloor**}$ ,  $N(I_2)=2^{\lfloor n/2\rfloor}$ .

- 2) Let  $\overline{I}$  be an input set of an MS of a partially completed Net such that  $\overline{I}$  has not as yet been connected to any other MS, and  $\overline{N(I)} = 2^X$  for some integer x.\*\*\*

- a) If  $x \ge 2$  then connect in 1-1 fashion to  $\overline{I}$  the output, 0 ,  $(N(0) = N(\overline{I}) = 2^X)$  of an MS with input set  $\overline{I} = \overline{I}_1$  u  $\overline{I}_2$  having  $N(\overline{I}_1) = 2^{\left[(x+1)/2\right]}$  and  $N(\overline{I}_2) = 2^{\left[x/2\right]}$ .

- b) If x = 1 , then designate the wires of  $\overline{I}$  as an input pair of the Net.

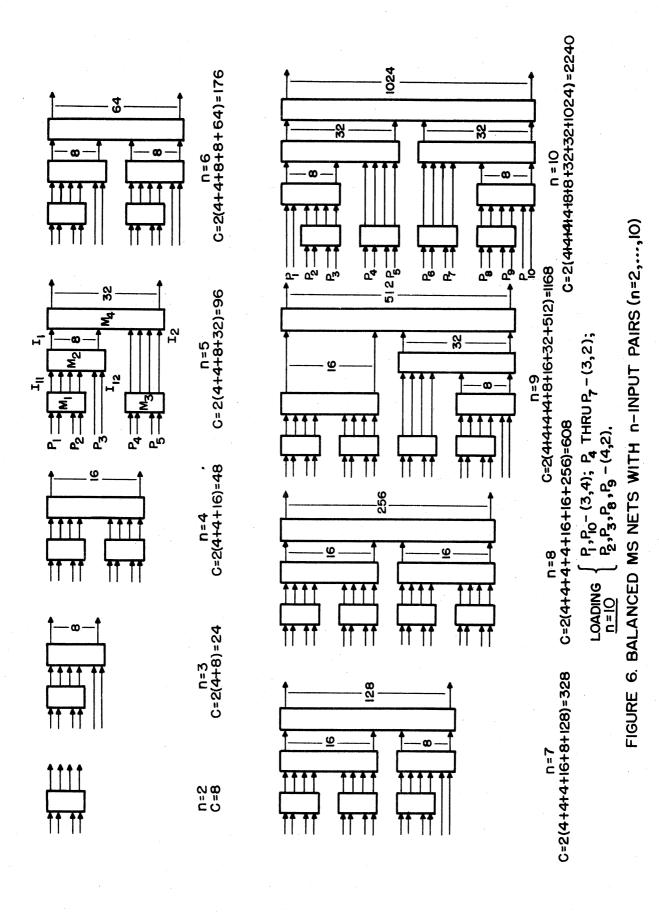

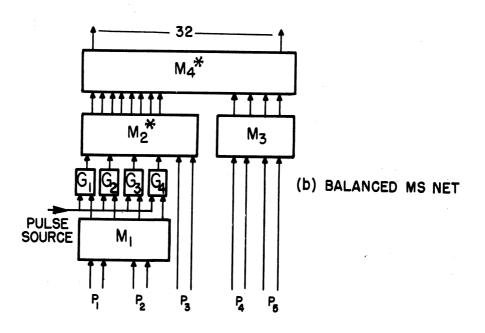

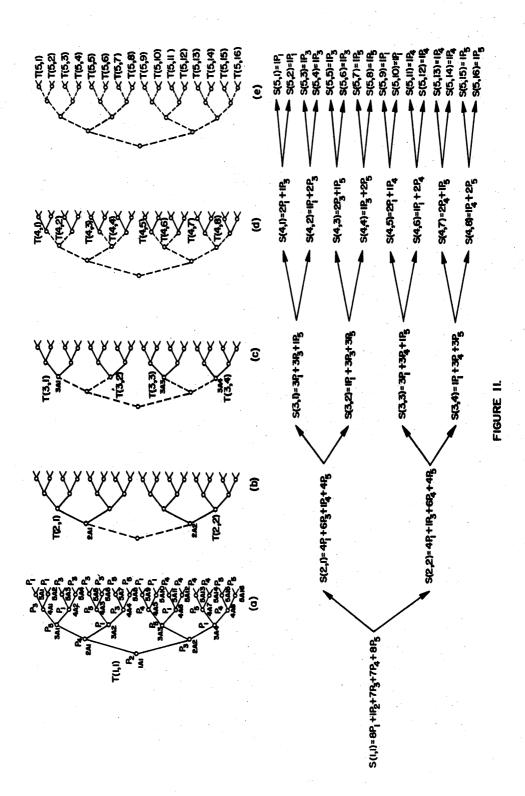

Figure 6 shows a number of Balanced MS Nets. Consider the case of n = 5 , I = P<sub>1</sub> u P<sub>2</sub> u ... u P<sub>5</sub> . There are  $2^5$  = 32 output wires for M<sub>4</sub> . The inputs of M<sub>4</sub> are split as evenly as possible into I<sub>1</sub> , N(I<sub>1</sub>) =  $2^{\lfloor (5+1)/2 \rfloor}$  =  $2^3$  = 8 and I<sub>2</sub> , N(I<sub>2</sub>) =  $2^{\lfloor 5/2 \rfloor}$  =  $2^2$  = 4 . In turn, the inputs of M<sub>2</sub> are split into I<sub>11</sub> , with N(I<sub>11</sub>) =  $2^{\lfloor (3+1)/2 \rfloor}$  = 4 and I<sub>12</sub> , with N(I<sub>12</sub>) =  $2^{\lfloor 3/2 \rfloor}$  = 2 . The Construction Formula for this switch is obviously

$$(((P_1 \times P_2) \times P_3) \times (P_4 \times P_5)) ****$$

<sup>\*</sup> Such MS's may be referred to as 'two-dimensional'.

<sup>\*\* &#</sup>x27;[x]' means 'the integer part of x'; this notation will be used frequently throughout the report.

It can be established inductively that every  $\bar{I}$  will satisfy this condition.

<sup>\*\*\*\*\*</sup>Note that in such a Net as this, the Construction Formula might have been written with any permutations of the subscripts on the P's without in any way changing the form of the Net. For present purposes (and there seems to be no reason in practice for doing otherwise) all such permutations of inputs which have no effect on the outputs (other than permutation) nor on the construction of the switch, will be identified—i.e., a switch for given input conditions specified by the definition will be considered unique.

It is not entirely obvious from the rules of construction that the resultant Net will have the required n input pairs. That this is actually the case can be demonstrated conveniently by means of the Construction Formula. Start with the output set expressed as the 5-term Cartesian Conjunction,  $(P_1 \times P_2 \times P_3 \times P_4 \times P_5)$ , (to use the example of Figure 6). Then the rule for inserting additional parentheses corresponding to the construction rule for adjoining MS's is to 'bifurcate' the smallest parenthetical expression into two such which differ at to number of P's by at most one. The resultant formula obviously denotes the proper number of inputs ( P's ), and the correspondence to the actual rules of construction can be verified readily.

The above definition defines the Balanced MS Net by telling how to built it. An alternative definition which is primarily descriptive rather than constructive and will be used in the discussion of minimality properties in Volume III may be stated as follows:

The Balanced MS Net with input set  $I = P_1 u \dots u P_n$  is an MS Net

- (a) having 2<sup>n</sup> final outputs from a single MS,

- (b) using 2-dimensional MS's throughout, and

- (c) such that each MS has its input sets 'balanced'; i.e., for  $2^x$  outputs the two input sets have  $N(I_1) = 2^{(x+1)/2}$  and  $N(I_2) = 2^{x/2}$ .

The two definitions have been proved equivalent but, in the interests of brevity, the proof is omitted.

The Element Input Count and Loading Couples for the Balanced MS Net cannot be conveniently stated for the general case. For the case  $n=2^k$ , however, the Element Input Count is C=2  $(2^{k-i+1})$ . Figure 6 presents schematic diagrams of the Nets with n input pairs for values of n ranging from 2 to 10 with the Element Input Count, C, computed for each and the Loading Couples given for the case of n=10.

The most important characteristic of this switch is stated formally as follows:

$\overline{\text{Theorem}}$ . The Element Input Count of a Balanced MS Net with n input pairs is less than or equal to the Element Input Count of any n-input-pair MS Net.

The proof of this theorem is rather lengthy and will be reserved for Volume III.

### 3.2. Alternative Switches Using Other Logical Elements

The construction of Networks consisting exclusively of Disjunctive Elements is quite straightforward. Such Nets are important in encoding, but because of their simplicity and because no alternative modes of construction are considered, the treatment of section 4.2 in connection with realization suffices without additional treatment here.

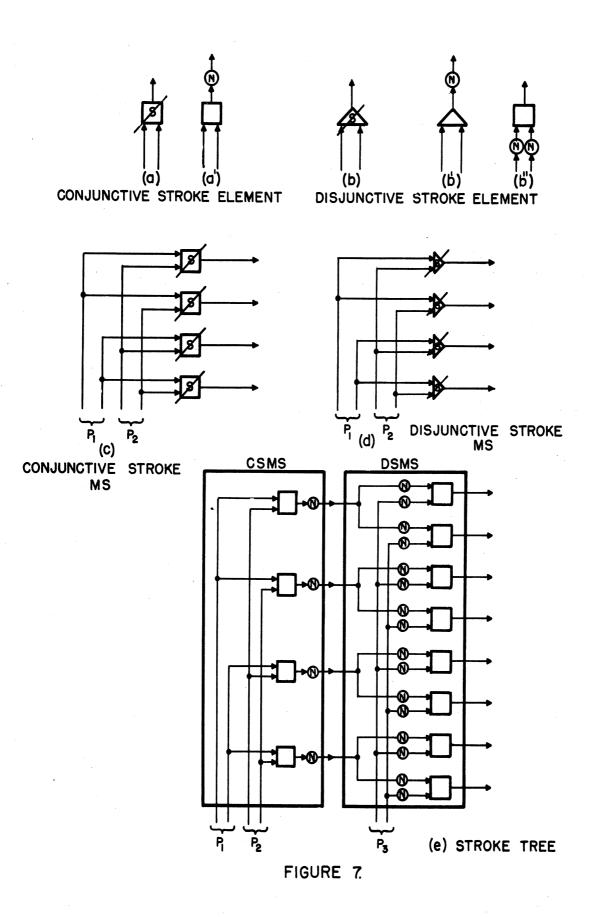

In section 2 the use of logical elements other than conjunction, disjunction, and negation was suggested, although these three were accepted as the "vocabulary" for the report. One slight digression from this policy was made with the introduction of the Double-and in the discussion of Standard Trees. The present section will consider some additional alternatives. All of the elements introduced are definable in terms of the standard vocabulary (e.g., see Figures 7a' and 7b'). While the alternatives could have been tied into the general theory of the report by this means, they have not been so treated and the present section can be considered as an appendix upon which one of the subsequent theory will depend.

The use of vacuum tubes leads naturally to the logical stroke functions; two examples of these functions will be discussed below.\*

The so-called "Sheffer" or Conjunctive Stroke (non-conjunction),  $p/q = def. \sim (p \cdot q)$ , is realized by a plate-loaded pentode without a phase inverter. It is represented diagrammatically as in Figure 7a, whose definition is the same as the definition of the standard network of Figure 7a'.

The Disjunctive Stroke (non-disjunction),  $p \downarrow q = def. \sim (pvq)$ , is realized by a pair of triodes in parallel. This function is diagrammed in Figure 7b, with the corresponding standard network as in Figure 7b' or as in 7b" by the duality,  $\sim (pvq) = \sim p \cdot \sim q$ .

These elements can be combined into Networks, following the rules of section 2. In particular, switches similar to the MS may be constructed: the Conjunctive Stroke MS (CSMS) as in Figure 7c and the Disjunctive Stroke MS (DSMS) as in Figure 7d. These switches give the same result as the standard MS with the qualification that the CSMS produces the <u>negations</u> of the outputs of an MS and the DSMS produces the output which would be produced by an MS with each of its inputs negated—cf. Figure 7b". (In other words, the CSMS with a negation on each of its outputs and the DSMS with a negation

In the two realizations below it is assumed that a high voltage level represents 'true' and a low level 'false'. These conventions could, of course, be reversed with a resultant interchange in the functions realized.

on each of its inputs would produce exactly the result of a standard MS—this is obvious from a consideration of the stroke elements themselves.)

One practical example of the use of these Stroke MS's is in the tree type of Network. Figure 7e shows a Stroke Function of 2 Bays (3 input pairs). The CSMS and DSMS are each enclosed in heavy-line boxes with their internal elements represented as in 7a' and 7b" in order to show how the interconnection effects a cancellation of the negations. In the case of a switch input connected directly to a DSMS the effect is to negate the signal on each wire of the pair, but since these are Polar Pairs, the situation is perfectly symmetric and amounts merely to interchanging the labels of the two wires. A Stroke Tree of any number of Bays may be similarly constructed by using a DSMS for the final (output) Bay and then alternating CSMS and DSMS for the remaining Bays.

### 4. Techniques for Realizing Transliterative Functions

The purpose of the present section is to present effective techniques for constructing, in terms of the components of the preceding sections, switches for realizing all of the transliterative functions. These functions are considered in three categories with one or more realization techniques for each category: "Decoding Functions" in section 4.1, "Encoding Functions" in section 4.2, and the general case, "Arbitrary Transliterative Functions" in section 4.3.\* Up to this point Volume I has been concerned exclusively with the static mode of operation. Pulse operation is discussed separately in section 4.4, "Modifications to Provide Pulse Outputs".

First some terminology will be established. Both "realizations" and "transliterative functions" have been referred to previously, with varying degrees of formality. The formal definitions will now be given.

One might naturally ask at this point why the title of this section is not expressed in a more direct manner in terms of switches (e.g., Design of Transliterative Switches) with the internal organization of the section based on types of switches rather than on functions. This approach was attempted in the initial study of the subject and was discarded for reasons which, if is felt, warrant the present digressive explanation. The difficulty is clearly exemplified by the IRE definition: "Function Switch, One-Many. A function switch in which only one input is excited at a time and each input produces a combination of outputs." (sometimes referred to as an "Encoding Switch"). Note that, in general, this definition describes a "mode of operation" rather than a type of switch-i.e., it merely defines the type of Transliterative Function the switch is to realize. Specifically, it says of the switch itself simply that it has "outputs" whose state is in some way dependent on the state of its "inputs". Under such a definition, any Function Switch (e.g., a "many-one" or "decoding" switch) would be a "one-many" switch if its inputs were properly activated. Since this type of definition offers no means for distinguishing various kinds of switches per se, there appear to be two alternatives: (1) the method of this report, which relies on functions since functions can be distinguished, and does not attempt to classify the switches; and (2) the formulation of definitions which do permit the classification of switches (perhaps from a consideration of their output under all possible input states)—an undertaking which, in the light of a cursory investigation, appears to be somewhat formidable.

Def. 4. A Transliterative Function, T , is a single-valued function (mapping) from a set of sequences of 0's and 1's all of the same length (the domain of definition) onto another set of sequences of 0's and 1's also all of the same length (the range) with the condition that there are no "dummy" digits in either the domain or the range; i.e., for any digit-position, x , of a sequence, the set (range or domain) must contain two sequences, s and s' , such that s has a 1 in position x and s' has a 0 in position x .\*

The domain of T will be denoted by 'D(T)' , its range by 'R(T)' , and an element (sequence) of the domain or range, respectively, by 'd<sub>1</sub>(T)' or simply 'd<sub>1</sub>' and 'r<sub>1</sub>(T)' or simply 'r<sub>1</sub>' —i.e., D(T) =  $\left\{d_1(T)\right\}$  , R(T) =  $\left\{r_1(T)\right\}$  .

Def. 5. A network is said to Realize or to be a Realization of a Transliterative Function,  $\overline{T}$ , if there exists an ordering  $w_1,w_2,\ldots,w_n$  of the set of input wires and a corresponding ordering  $\overline{w}_1,\ldots,\overline{w}_k$  of a subset (perhaps proper) of the output wires having the property that whenever the sequence of states of  $w_1,\ldots,w_n$  is equal to a  $d_i,d_i\epsilon\;D(T)$ , then the sequence of states of  $\overline{w}_1,\ldots,\overline{w}_k$  is equal to  $T(d_i)$ .

This definition postulates the existence of a 1-1 correspondence between the bit positions of the domain sequences and the set of input wires, and a similar one between range sequences and a subset of the output wires. There is another important aspect of domain sequences: they may be thought of as representing information impressed on the inputs from outside. If this information is presented on n Polar Pairs of wires, it is not to be considered an n bit sequence but instead a 2n bit sequence.

The concept of Realization defined here is, admittedly, a narrower concept than the ordinary intuitive one.\*\* It is, however, adequate for the purposes of this report and has the advantage of stating precisely the kind of realization which the given techniques produce.

This condition could be omitted, enlarging the class of Transliterative Functions, but the functions thus admitted would hardly be of sufficient interest to warrant even the slight modifications that would be necessary in the subsequent theory.

A definition closer to the intuitive idea of realization would, for example, admit, under certain circumstances, realizations in which a proper subset of the inputs is activated in accordance with  $d_i(T)$ .

The term 'technique' is used here in a special sense. <u>Techniques</u> are constructive procedures, each associated with a specified class of Transliterative Functions, describing step by step a fully effective method for building a switch to Realize a given Function of the class. Furthermore, it is desirable, and will be a characteristic of all techniques presented, that the relation between inputs and outputs required by the given function be made explicit by means of a labeling of the wires as in the definition of Realization.

The application of these Techniques together with simplifications of the Switch produced may result in "Disjunctive Elements" with but a single input. When this occurs the "Disjunctive Element" is to be eliminated and its input designated a Switch output. It is also possible that a Technique will produce a switch with a "dead-end" input—one which is neither a Switch output nor an input to a Logical Element (e.g., if an Encoding Function—see section 4.2—has the all-zero sequence in its range). Such a switch is not strictly a Network by the formation rules of section 2. However, the status of such a wire is so obvious, and the treatment so simple—merely ignore or eliminate it—that it seemed advisable to admit the discrepancy rather than to complicate the theory further in order to treat this special case with full rigor.

### 4.1. Decoding Functions

$\underline{\text{Def. 6.}}$  A  $\underline{\text{Decoding}}$  Function is a Transliterative Function,  $T_d$  , such that:

- (a) every  $\textbf{r}_{\texttt{i}}(\textbf{T}_{\texttt{d}})$  contains a single l , and

- (b)  $N(D(T_d)) = N(R(T_d))$ .

The effect of condition (b) is to make Decoding Functions 1-1. Functions satisfying condition (a) alone are handled by the techniques for arbitrary functions.

The inputs of the Switches constructed in section 3 were in Polar Pair form. In order to consider such input sets it is useful to define a Polar Sequence as a sequence  $a_1, a_2, \ldots, a_{2k}$  having  $a_{2j-1}, a_{2j}$  either 0,1 or 1,0 for  $j=1,2,\ldots,k$ .

$\underline{\text{Def. 7.}}$  A Complete  $\underline{\text{Decoding Function}},$   $T_c$  , is a Decoding Function satisfying the following:

- (a) every element of  $D(T_c)$  is a Polar Sequence, and

- (b) every Polar Sequence of length  $N(d_1(T_C))$  is an element of  $D(T_C)$  .

It follows clearly from this definition that

$$N(D(T_c)) = 2^{N(d_1(T_c))/2} = N(R(T_c))$$

.

$\begin{array}{lll} \underline{\text{Theorem 1}}. & \text{A Complete Decoding Function,} & T_c & \text{, with} \\ \underline{\text{N(d_i(T_c))}} &= 2n & \text{can be realized by any MS Net with I} &= \\ \underline{\text{n}} & U & P_j & \text{(i.e., with input set consisting of n Polar j=1} \\ Pairs). \end{array}$

Corollary. If  $T_c$  is realized (in accordance with Theorem 1) by a Simple MS Net, then there are no extraneous output wires, i.e., the set of output wires, O(1-1)  $R(T_c)$ .

Proof.  $D(T_c)$  is the Cartesian Product of n sets, each consisting of the two pairs, (0,1), (1,0), i.e.,  $D(T_c) = ((0,1), (1,0))^n$  and is represented by the states of the pairs of wires of  $\mathscr L$ , the set of n P,'s of the Net. The Network output, 0 , by definition contains the Cartesian Conjunction,  $CC(\mathscr L)$ , i.e., a distinct output wire of  $CC(\mathscr L)$  is activated for each sequence of the Cartesian Product,  $D(T_c)$ , represented on the inputs. Each wire of the  $CC(\mathscr L)$  may be assigned an integer, x , as follows: Consider the image sequence,  $T_c(d_1)$ , for  $d_1 \mathcal E D(T_c)$ . It contains a single 1 . Denote the position in which the 1 appears by x , and assign x to the wire of  $CC(\mathscr L)$  which is in the 1 state for  $d_1$ . If this is done for all  $d_1 \mathcal E D(T_c)$ , all wires of  $CC(\mathscr L)$  will be labeled by an x ,  $1 \leq x \leq 2^n$ .

The wires of CC(Q) then, considered in the sequence of the x's , clearly effect a Realization of  $T_c$  . The corollary follows immediately from the fact that for a Simple MS Net O = CC(Q) .

With the result of this theorem, the following specific Realizations are immediately available:

Technique O. A Complete Decoding Function,  $T_c$ , with domain sequence of length 2n ( $N(d_i(T_c)) = 2n$ ) can be Realized by

- (a) an Exponential Switch,

- (b) a Tree, or

- (c) a Balanced MS Net, with input set  $I = U P_j$  j=1

Since explicit Construction Procedures were given in section 3 for each of the switches, (a), (b), and (c), and since the labeling of the wires described in the proof of Theorem 1 gives an ordering of input

and output sequences which establishes the functional correspondence, Technique O is fully effective as required. Note that since the three Switches are simple MS Nets, the Corollary to Theorem 1 indicates that there will be no extraneous output wires.

A Decoding Function, T , may fail to be Complete by violating either of the two conditions characterizing a Complete Decoding Function—i.e.,

- (1) The elements of D(T) are not all Polar Sequences.

- (2) Not every Polar Sequence of length  $N(d_i(T))$  is an element of D(T) .

In the technique given below, step  $\underline{A}$  provides for failures of type (1) and step C for those of type (2).

#### Technique 1.

- A. Examine the sequences of D(T)

- 1. If not all the sequences of D(T) are Polar Sequences, provide a Polarizer with  $N(d_1(T))$  inputs.\* Its outputs are to be connected, in the obvious manner, to the Switch constructed below. Define  $n = N(d_1(T))$ .

- 2. If every  $d_1(T)$  is a Polar Sequence, define  $n = N(d_1(T))/2$  and proceed to  $\underline{B}$ .

- $\underline{B}$ . By Technique O(a), (b), or (c) construct a Switch for the Complete Decoding Function with n Polar Pair inputs.

- $\underline{C}$ . From the Switch produced by  $\underline{A}$  and  $\underline{B}$  remove any Logical Element which is not in a Chain terminating in any one of the N(D(T)) required outputs.

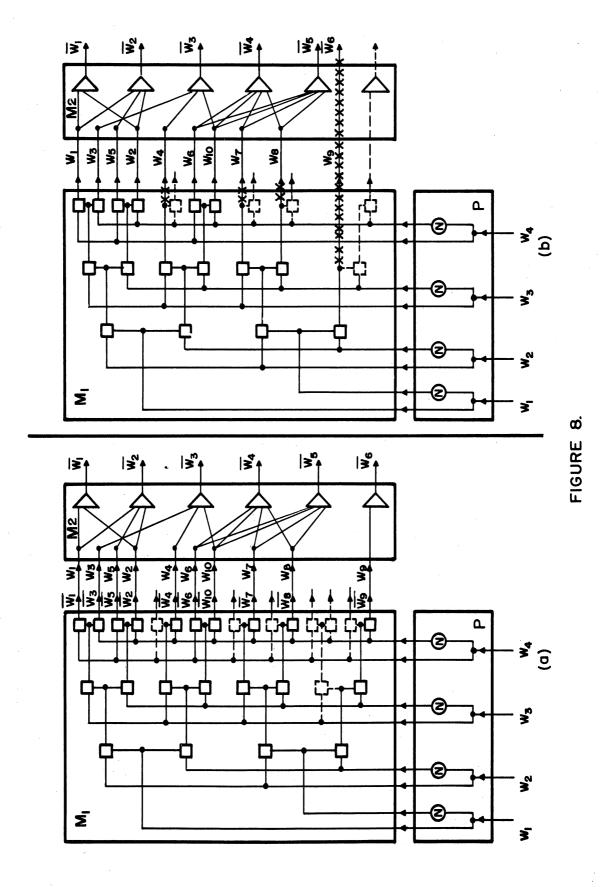

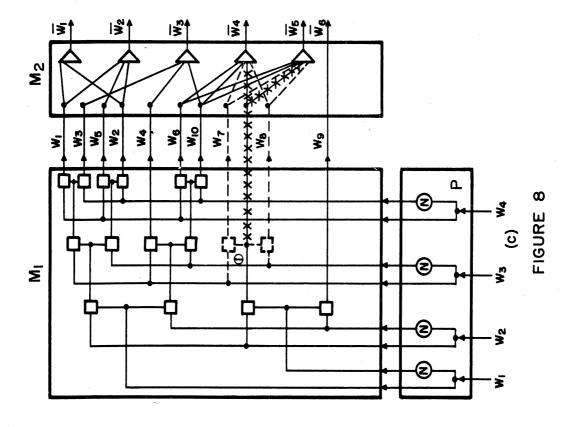

Technique l is illustrated in Figure 8a (disregarding Switch  $M_2$  by applying it to the function  $T_d$  defined in Table II of section 4.3.

It may be the case that some part of every domain sequence—the same part for each—is a Polar Sequence and the remainder not. In practice it would be possible in this case to provide a Polarizer of less than  $N(d_1(T))$  inputs for use with only the "unpolarized" positions, although formally this simplification has been ignored in the interests of presenting a unified general theory.

Clearly the sequences of  $D(T_d)$  are not all Polar Sequences and so according to step A.l a 4-input Polarizer, P , must be provided. Step B requires the construction of a Switch for the Complete Decoding Function with  $N(d_1(T)) = 4$  Polar Pair inputs by Technique O(a), (b), or (c)—i.e., by an Exponential Switch, a Tree, or a Balanced MS Net. In the example a Tree is used—  $M_1$  in the figure. The inputs of P may be labeled in any order and the outputs of P are connected to the inputs of  $M_1$  in the obvious manner. After a particular labeling of the inputs of P has been chosen, the outputs of  $M_1$  are labeled by considering the  $d_1(T_d)$ . Assign the label ' $\overline{w}$ ,' to the output wire which is activated whenever the sequence of states of the input wires,  $w_1, w_2, w_3, w_4$ , is  $d_1$  (the state of  $w_k$  corresponding to the kth bit of  $d_1$ ), where j is the position number of the l in  $T_d(d_1)$ . Finally, proceeding according to step C, the unnecessary Logical Elements are eliminated—in the figure they are drawn with broken lines.

Simplifications may be possible in Switches constructed by this technique. No comprehensive study of simplification procedures has been made, but examples illustrating some of the possibilities are given in section 4.3.

### 4.2. Encoding Functions

Def. 8. An Encoding Function is a Transliterative Function, . Te , such that every  $d_1(T_e)$  contains a single 1 .

The following technique provides a Realization for any given Encoding Function,  $T_{\rm e}$  , where n is the number of domain sequences,  $\bar{n}$  is the number of range sequences, and  $d_{\hat{i}}$  is defined to be the domain sequence whose ith bit is a 1 .

#### Technique 2.

- (1) Provide n input wires and n Disjunctive Elements. Designate the Element outputs as switch outputs; assign the integers from 1 to n to the input wires, and those from 1 to  $\overline{n}$  to the Disjunctive Elements.

- (2) Connect the ith input wire to a distinct input of the jth Disjunctive Element if the jth bit of  $T_{\rm e}(d_{\rm i})$  is a 1 .

Nothing was stated about the number of inputs of the Disjunctive Elements, since this would depend on the nature of  $T_e$ . In general, it is clear (by virtue of the exclusion of "dummy" digits in Def. 4) that no Element will require more than  $N(D(T_e))-1$  inputs. In the "most efficient"

case—a 1-1 function with  $N(D(T_e)) = 2^X$ ,  $N(r_i(T_e)) = x$ —every Element will have  $2^{X-1}$  inputs, since each output must be in the 1 state for exactly half of the  $2^X$  input states.

Technique 2 is illustrated in Figure 8a for the function,  $T_e$ , defined in Table II of section 4.3. The Switch produced is  $M_2$ . The input wires may be numbered  $w_1,\ldots,w_n$  in any order—the order here being chosen merely for convenience in the example of section 4.3. Note that in Figure 8b the single-input Disjunctive Element has been eliminated.

A Switch produced by Technique 2 can often be simplified. Such a Switch will consist of Disjunctive Elements whose inputs are wires of I , the set of input wires for the Switch. Suppose some subset, I , , of I is contained in the input set of several of these Disjunctive Elements, say  $E_1,\dots,E_k$  . Then let I , be the input set for a new Disjunctive Element, E , and replace each  $E_i$   $(i=1,\dots,k)$  by a Disjunctive Element  $E_i$  having the same input set as  $E_i$  except that the output of E replaces the subset I , of inputs of  $E_i$  . This procedure will reduce the Element Input Count, C , by an amount

$$\Delta C = (k-1)(C(E)-1)-1$$

,

from which it is apparent that  $\Delta C>0$  if  $k\geq 2\leq C(E)$  but not k=C(E)=2 —for which  $\Delta C=0$  .

### 4.3. Arbitrary Transliterative Functions