### ENGINEERING RESEARCH INSTITUTE UNIVERSITY OF MICHIGAN ANN ARBOR

# THE LOGICAL DESIGN OF AN IDEALIZED GENERAL-PURPOSE COMPUTER

Project 1828

BURROUGHS CORPORATION RESEARCH CENTER PAOLI, PENNSYLVANIA

30 October 1954

EMEN UMIL V837

## Table of Contents

| Sec                  | Section                                                                                                                              |                                                                                                                           |                      |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------|

| Preface              |                                                                                                                                      |                                                                                                                           | iii                  |

| 1.                   | Introduction                                                                                                                         |                                                                                                                           | 1                    |

| 2.                   | The Computer and its Parts                                                                                                           |                                                                                                                           | 2                    |

| 3.                   | Logical Symbolism and Diagrams                                                                                                       |                                                                                                                           | 5                    |

| 4.                   | STORAGE                                                                                                                              |                                                                                                                           | 9                    |

|                      | 4.2.<br>4.3.                                                                                                                         | Information<br>Cells and Storage Bins<br>Address Decoder<br>Serial Storage                                                | 9<br>10<br>14<br>17  |

| 5.                   | ARITHMETIC UNIT                                                                                                                      |                                                                                                                           | 20                   |

|                      | 5.2.<br>5.3.                                                                                                                         | Machine Arithmetic Operation of the CONTROL The Functions of the ARITHMETIC UNIT Execution of the Arithmetic Instructions | 20<br>25<br>27<br>29 |

| 6.                   | CONTROL                                                                                                                              |                                                                                                                           | 33                   |

|                      | 6.2.<br>6.3.                                                                                                                         | ADDRESS COUNTER CONTROL CLOCK OPERAND DECODER Operation of the CONTROL                                                    | 33<br>37<br>39<br>40 |

| Footnotes            |                                                                                                                                      |                                                                                                                           | 44                   |

| Bibliography         |                                                                                                                                      |                                                                                                                           | 46                   |

| Figures              |                                                                                                                                      |                                                                                                                           | 47                   |

| Appendices           |                                                                                                                                      |                                                                                                                           | 56                   |

| A.<br>B.<br>C.<br>D. | <ul> <li>Machine Solution of a Simple Problem</li> <li>Multiplication</li> <li>Arithmetic Operations on Instruction Words</li> </ul> |                                                                                                                           |                      |

#### Preface

This is the second (and last) report of a series of which "Theory of Logical Nets" [2] was the first. We shall make some comments about the relations of the two reports.

"Theory of Logical Nets" gives a foundational analysis of logical nets (diagrams of digital computing circuits) in general. This second report presents a particular logical net, which represents the structure of an idealized general-purpose digital computer. Thus the first report contains the foundations for this second one, which presents an application of the nets analyzed in the first report.

The logical design of the general-purpose computer presented here was worked out by the first author independently of Project 1828. It was this work that stimulated the research already embodied in the first report. Since this design shows how the nets of the first report may be used, it seemed desirable to present the logical design of the computer as a second report in the series. In doing so we found it necessary to work out a set of logical formulas describing the behavior of the computer, and, since this material is of interest as an application of symbolic logic to computers, we have embodied it in the present report.

# THE LOGICAL DESIGN OF AN IDEALIZED GENERAL-PURPOSE COMPUTER<sup>1</sup>

#### 1. Introduction.

There are many known complete logical designs for general purpose digital computers, but all of them are in terms of specific systems of equipment and most of them are very complex. That complexity is enforced not entirely by logical but also by engineering considerations pertaining to the physical problems involved in the actual construction of a machine. It seems desirable, therefore, to present a design for a complete generalpurpose digital computer which shows its basic logical structure in abstraction from the engineering problem of realizing that structure physically. We give such a design in the present paper, patterned in a general way after the machine described in [1] . Since we use some of the techniques of symbolic logic in its exposition, our logical design is much more "logical" than is usually implied by the use of that term.

The present paper is intended to serve two important purposes. First, as has been said, it is intended to show what is logically required for a general-purpose computer as distinguished from what is required physically, the latter being relative to the present state of the computer

art. Second, it is intended by abstraction from the requirements of equipment to show how a design can be obtained which is much simpler, though admittedly idealized, and hence much easier to understand. Our presentation should have pedagogical value for communicating the basic structure of a general-purpose machine to those acquainted with the rudiments of symbolic logic but lacking in engineering background.

The present paper is a continuation of [2], which gives a foundational analysis of logical nets (diagrams of digital computing circuits) in general. The structure of our idealized general-purpose computer is here represented by a particular kind of net studied in [2], the well-formed net.

#### 2. The Computer and its Parts.

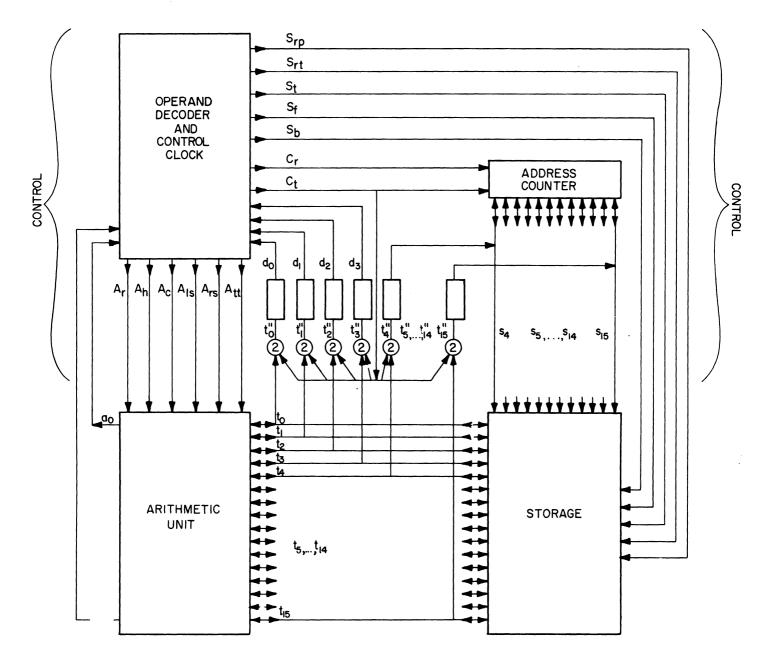

Our automatic computing machine contains three main parts with communication channels between them (Fig. 1). The first part is the ARITHMETIC UNIT, which performs the arithmetic operations of instructions 4, 5, 6, 7, 8, and 9 of Fig. 2, and which "senses" the end digits of a number when that is required for the execution of instructions 13 or 14.

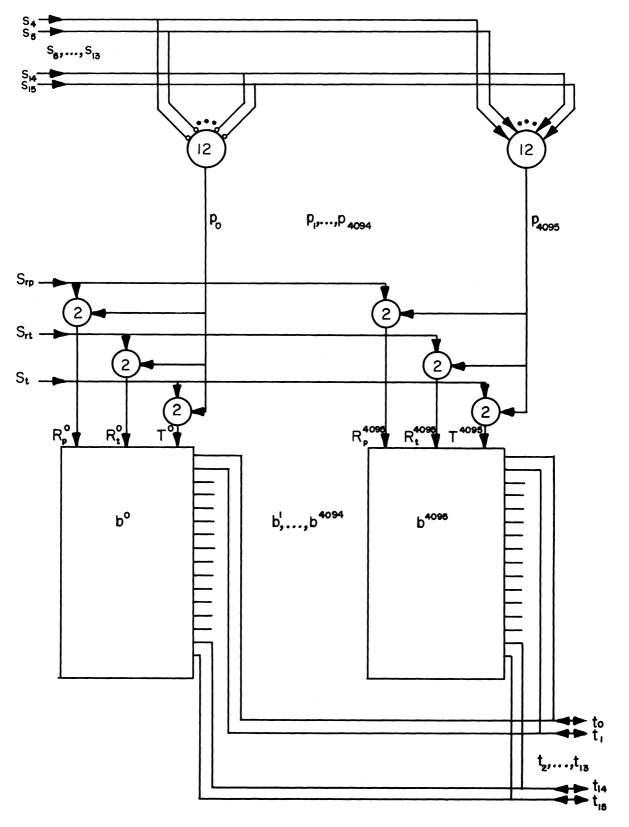

The second part of the computer is its STORAGE, whose

bins contain both numbers to be operated on and instructions to perform specified operations. The STORAGE contains two parts, a serial storage and a parallel storage. The parallel storage contains 4,096 storage bins: bin 0, bin 1, bin 2, ..., bin 4095, whose numbers constitute the addresses of the bins.

The machine must provide a path along which numbers can be transferred between the STORAGE and the ARITHMETIC UNIT when instruction 4, 5, 6, 7, 10, or 11 is executed. In our computer this path is the trunk line  $\underline{t}$ , whose sixteen components  $\underline{t}_0$ ,  $\underline{t}_1$ ,  $\ldots$ ,  $\underline{t}_{15}$  are represented by horizontal lines connecting the ARITHMETIC UNIT and the STORAGE in the lower part of Fig. 1.

For the machine to solve a problem it must be given a list of specific instructions, whose execution will result in the solution to the problem. The execution of these instructions is under the direction of the CONTROL, the third main part of the computer, which consists of all the equipment of Fig. 1 not yet described. Instructions for the machine are stored in order in bins of the parallel storage, and, except when it is instructed to "jump" (see 12, 13, and 14 of Fig. 2), the computer executes these instructions seriatim. To this end count must be kept of the instructions as they are executed; this function is

performed by that part of the CONTROL called the ADDRESS COUNTER, which at any given time will contain the address of the bin storing the next instruction to be executed.

A set of instructions for the machine to execute in solving a problem is a routine, and every routine, however complex, is constructed out of a small number of primitive or basic instructions (the fourteen listed in Fig. 2). As each instruction emerges from the STORAGE it goes to the CONTROL, and that part of the CONTROL called the OPERAND DECODER then stimulates the appropriate control wires to make the other parts of the computer perform whatever functions are required for the execution of that instruction. Eleven control wires lead from the CONTROL to the other parts of the machine: six, bearing the general label  $\underline{A}$ , from the OPERAND DECODER to the ARITHMETIC UNIT; and five, labeled S, from the OPERAND DECODER to the STORAGE. There are also two control wires, labeled C, which connect different parts of the CONTROL, both Cr and  $\underline{C}_{t}$  lead from the OPERAND DECODER and CONTROL CLOCK to the ADDRESS COUNTER, and  $\underline{C}_t$  leads also to the equipment in the center of Fig. 1 labeled  $\underline{t}_{i}^{n}$ . Different basic instructions cause the CONTROL to stimulate different sets of control wires, as indicated in Fig. 2.

How these various parts perform their functions will be explained in detail: the STORAGE in Section 4, the ARITH-METIC UNIT in Section 5, and the CONTROL in Section 6.

# 3. Logical Symbolism and Diagrams.

Since our diagrams are logical nets in the sense of 2, the lines in them represent wires. Each net wire in our diagrams is in one of two states (0,1) at each discrete moment of time  $\tau = 0, 1, 2, \dots$  (Whenever we use  $\tau$ as a time variable, it ranges over discrete moments 0, 1, 2, ... unless otherwise stipulated.) The two states 0 and 1 are complementary; they correspond to the truth values false and true, respectively. In our diagrams control wires are labeled with capital letters, other wires (information wires) are labeled with small letters from the Latin or Greek alphabets. To assert that the wire labeled f is activated or stimulated at time au we write either  $\underline{\mathbf{f}}$ ,  $\underline{\mathbf{f}}(\mathcal{T})$ ,  $\underline{\mathbf{f}} = 1$ , or  $\underline{\mathbf{f}}(\mathcal{T}) = 1$ ; and to assert that it is inactive or not stimulated we write either  $\underline{\mathbf{f}} = 0$  or  $\underline{f}(\mathcal{T}) = 0$ . Thus the symbols used to label wires are systematically ambiguous: any such symbol f is on the one hand a label for the wire beside which it appears, and on the other hand it is a function symbol  $\underline{\mathbf{f}}(\mathcal{T})$  whose argument  $\mathcal{T}$ ranges over successive discrete moments of time and whose values are the wire states 0 and 1.

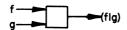

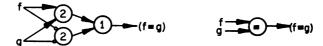

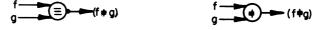

Our primitive logical symbol, the stroke function  $f \mid g$ , means not both  $f \mid and \mid g$ , and the corresponding diagrammatic stroke element appears in Fig. 3a as a square

nucleus with two input wires (f and g) and one output wire  $\underline{f} \mid \underline{g}$  (as in [2]). Other logical symbols we shall use are: negation,  $\overline{f}$  (or alternatively  $\sim f$ ), meaning not  $\underline{f}$ ; (inclusive) disjunction,  $\underbrace{f \lor g}$ , meaning  $\underline{f}$  and  $\underbrace{or}$   $\underline{g}$ ; conjunction, fg (or alternatively  $f \circ g$ ), meaning  $\underline{f}$  and  $\underline{g}$ ; material implication,  $\underline{f} \supset \underline{g}$ , meaning not  $\underline{f}$  or  $\underline{g}$ ; equivalence,  $f \equiv g$ , meaning  $\underline{f}$  and  $\underline{g}$  or not  $\underline{f}$  and not  $\underline{g}$ ; and inequivalence,  $f \neq g$ , meaning f = and not g = or g = andnot f. Just as these six functions can be constructed out of the stroke function (see pp. 255-256 of [4]), so the six corresponding diagram elements can be constructed out of stroke elements, as shown in Figs. 3b, c, d, e, f, and g.2 Each right-hand diagram in Figs. 3b, c, d, f, and g is a definitional abbreviation of the diagram to its left. Having introduced the symbol for negation, we have additional ways to assert that wire  $\underline{\mathbf{f}}$  is inactive at time  $\mathcal{T}$ :  $\overline{\underline{\mathbf{f}}}$ ,  $\overline{\underline{\mathbf{f}}}(\mathcal{T})$ ,  $\overline{\underline{f}}$  = 1, and  $\overline{\underline{f}}(\tau)$  = 1. Similarly we could assert that it is active by writing  $\overline{\underline{f}} = 0$  or  $\overline{\underline{f}}(\mathcal{T}) = 0$ .

The inequivalence element has many properties which make it very useful in computer work. It can be used as a complementer, for if either input is in state 1, the state of the output wire will be the complement of the state of the other input (this application was first pointed out in [7]). We shall later (in Section 5) make use of the following properties of inequivalence: it is both associative

and commutative, and  $\underline{f}_1 \neq \underline{f}_2 \neq \dots \neq \underline{f}_N$  is true just in case an odd number of its arguments are true. That it has these properties is readily proved by induction on the number of arguments. Hence we can have an inequivalence element with any number of inputs (see Fig. 7 for a 3-input inequivalence).

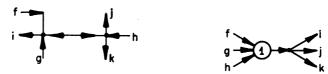

It is convenient also to introduce a generalized threshold element having I positive input wires  $\underline{\mathbf{f}}_1$ ,  $\underline{\mathbf{f}}_2$ , ...,  $\underline{\mathbf{f}}_1$  and  $\underline{\mathbf{J}}$  negative input wires (a negative input wire to an element is one which attaches to that element through a negation element)  $g_1, g_2, \ldots, g_J$ , and a positive integer threshold  $\underline{\mathtt{T}}_{\circ}$  Such an element is diagrammed in Fig. 3h, and its behavior is characterized by the equation  $\underline{h} = \left[ \left( \sum_{i=1}^{\underline{I}} \underline{f}_i + \sum_{i=1}^{\underline{J}} \overline{g}_j \right) \ge \underline{T} \right]$  where  $\Sigma, +$ , and  $\geq$  have their usual mathematical significance.<sup>3</sup> For any  $\underline{I}$ ,  $\underline{J}$ , and  $\underline{T} \ge 0$  the threshold element is easily constructed out of elements already available.  $\underline{T} > \underline{I} + \underline{J}$ ,  $\underline{h} = 0$  and the construction is trivial. equation for the non-trivial case is an inclusive disjunction whose disjuncts are all possible conjunctions of  $\underline{\mathbf{T}}$  arguments from the set of  $\underline{\mathbf{I}}+\underline{\mathbf{J}}$  arguments  $\left\{\underline{\mathbf{f}}_1,\ \underline{\mathbf{f}}_2,\ \cdots,\ \underline{\mathbf{f}}_1,\ \underline{\mathbf{g}}_1,\ \underline{\mathbf{g}}_2,\ \cdots,\ \underline{\mathbf{g}}_J\right\}$  , and hence may be realized by a net containing only negation, conjunction, and disjunction elements (see Theorem 12 of [2]).

should be clear that disjunction and conjunction elements with any number of input wires are special cases of our generalized threshold element.

A second primitive element used in representing digital computing circuits is the <u>delay element</u>, which appears in Fig. 3i as an oblong nucleus with one input wire  $\underline{f}$  and one output wire  $\underline{g}$ . As in the case of the other elements, each of its wires possesses one of the two states (0,1) at each discrete moment of time: the output wire  $\underline{g}$  is in state 0 at  $\mathcal{T}=0$ , and thereafter it possesses the state possessed by the input wire at the prior moment of time. The equations which describe its behavior are:  $\underline{g}(0)=0$  and  $\underline{g}(\mathcal{T}+1)\equiv\underline{f}(\mathcal{T})$  for every time  $\mathcal{T}$ .

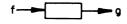

We use two additional primitive elements: an input key whose activation puts the wire attached to it into state 1, and an output light which emits a visible signal if and only if the wire attached to it is in state 1. These are diagrammed as circles with the letters K or L in their interiors, as in Fig. 4. They represent relatively slow ways in which the operator can insert or receive information from the computer.

We use only nets that are well-formed in the sense of [2], but to simplify our diagrams we sometimes omit arrow-heads and wires, as between the small and large circles in Figs. 3e and 3g, and we sometimes show arrowheads going both

ways to avoid duplication of wires. We also allow a multiple junction, that is, a confluence of  $n \ge 2$  output wires, to abbreviate an n-input disjunction element in the manner of Fig. 3j, whose behavior is governed by the equations  $(\underline{f} \vee \underline{g} \vee \underline{h}) = \underline{i} = \underline{j} = \underline{k}$ . And we place a dot at the intersection of two lines to indicate that the wires represented by those lines are connected, as at the left of each right-hand key in Fig. 4. Our final convention is that (except for Fig. 3) wires having the same label are understood to be connected, whether they occur in the same diagram (as the  $\underline{t}_1$ 's in Fig. 7) or in different diagrams (as the  $\underline{t}_1$ 's in Figs. 1, 4, 5, and 7).

#### 4. STORAGE.

## 4.1. Information.

At any one time a single wire can carry one bit of information, 0 in its off state, 1 in its on state. The two digits 0 and 1 suffice for the expression of all real numbers in binary notation, and the term "bit" is a contraction of "binary digit." The machine's vocabulary consists of words, each of which is a sequence of sixteen bits. 4 At any moment exactly one word will be on the trunk line, each of whose sixteen components  $\underline{t_i}$  ( $\underline{i} = 0, 1, 2, ..., 15$ ) carries one of the word's sixteen bits. (Whenever we use

the variable <u>i</u> as subscript of a letter which labels a wire, it ranges over 0, 1, 2, ..., 15 unless otherwise stipulated.) In the machine each word is an ordered set of wire states, and every word is expressed by a number in binary notation. These words can be used to express either numbers or instructions. Their use to express numbers will be explained in Section 5; in the present section we explain their use to express instructions.

A typical instruction, such as ADD X (4 of Fig. 2), is expressed by an instruction word whose first four digits  $\underline{d_0}\underline{d_1}\underline{d_2}\underline{d_3}$  constitute its operand and whose rightmost twelve digits constitute its address  $(\underline{X} = \underline{x_4}\underline{x_5}...\underline{x_{15}})$ , which specifies the location of the storage bin containing the number to be operated on. (In the case of instructions 1, 2, 3, 8, and 9, the address part is unused.)

# 4.2. Cells and Storage Bins.

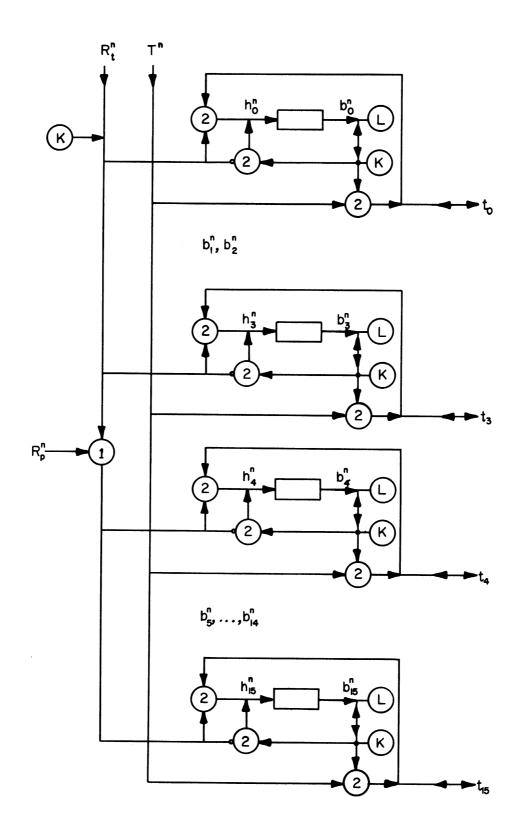

A cell, which is a circuit capable of receiving and storing one bit of information, is easily constructed out of the elements described in Section 3. To see how the cell at the top of Fig. 4 stores information, we first observe that  $\underline{h}_0^n \equiv (\underline{R}_t^n \underline{t}_0 - \overline{R}_t^n \underline{b}_0^n)$ . Now consider what occurs at any time  $\mathcal{T}$  when all of the control wires are in state 0. If  $\underline{b}_0^n(\mathcal{T}) = 1$ , its signal will pass through the conjunction element below  $\underline{h}_0^n$  up to make  $\underline{h}_0^n(\mathcal{T}) = 1$ , whence  $\underline{b}_0^n(\mathcal{T}+1) = 1$ ,

and if all control wires remain inactive, then  $\underline{b}_0^n(\mathcal{T}+1)=1$  will entail  $\underline{h}_0^n(\mathcal{T}+1)=1$  also, whence  $\underline{b}_0^n(\mathcal{T}+2)=1$ . On the other hand, if  $\underline{b}_0^n(\mathcal{T})=0$ , no signal will reach  $\underline{h}_0^n$ , and  $\underline{h}_0^n(\mathcal{T})=0$ , whence  $\underline{b}_0^n(\mathcal{T}+1)=0$ , and, if all control wires remain inactive, then  $\underline{b}_0^n(\mathcal{T}+1)=0$  will entail  $\underline{h}_0^n(\mathcal{T}+1)=0$  also, whence  $\underline{b}_0^n(\mathcal{T}+2)=0$ . Thus, if no control wires are activated during the interval in question, whatever state a cell possesses at time  $\mathcal{T}$  will continue to be possessed by it at times  $\mathcal{T}+\underline{n}$  for  $\underline{n}=1,2,3,\ldots$ .

Note that each symbol  $\underline{b}_{i}^{n}$  of Fig. 4 has a three-fold significance: it labels the output wire of the delay element to its left, it is a function symbol  $\underline{b}_{i}^{n}(\tau)$  as explained at the beginning of Section 3, and it also labels the cell within which it appears. This three-fold significance attaches to the labels of all cells within the machine:  $\beta_{0}^{-1}$  and  $\beta_{0}^{1}$  in Fig. 6,  $\underline{a}_{i}$  in Fig. 7, and  $\alpha_{i}$  in Fig. 8.

Sixteen such cells are combined as in Fig. 4 to make one storage  $\underline{\text{bin}}$ , which can receive and store a word, one bit in each cell. The <u>parallel storage</u> consists of 4,096 such bins  $\underline{b}^0$ ,  $\underline{b}^1$ , ...,  $\underline{b}^{4095}$  connected in parallel as indicated in Fig. 5.

When the machine is idle all components of the trunk are in state 0, and all cells of the bin can be cleared to state 0 manually by activating the key at the upper left corner of Fig. 4. That key's activation at such a time  $\mathcal{T}$

prevents any signal that may be at  $\underline{b}_i^n(\mathcal{T})$  from reaching  $\underline{h}_{1}^{n}$ , whence  $\underline{h}_{1}^{n}(\mathcal{T}) = 0$  and  $\underline{b}_{1}^{n}(\mathcal{T}+1) = 0$  regardless of the value of  $\underline{b}_{i}^{n}(\mathcal{T})$  . Having thus cleared all cells to 0, a 1 may be inserted in any cell by activating the key at that cell's right. For if all control wires are in state 0 and the key at the left is not activated, then activating the right-hand key at time T will cause a signal to pass through the conjunction element below  $\underline{h}_{i}^{n}$  up to make  $\underline{h}_{i}^{n}(\mathcal{T}) = 1$ , whence  $\underline{b}_{i}^{n}(\mathcal{T} + 1) = 1$ , and the cell will continue to store the 1 until caused to change by the activation of the left-hand key or of some control wire. the keys can be used to load each cell with its initial bit of information, and the lights provide a crude way of getting information out of the bin, since each one is visibly on or off according as its cell contains a 1 or a 0. assume that the keys are inactive in the following discussion.

Three control wires lead to each bin, a distinct set to every bin. Fig. 4 shows the <u>n</u>th bin and its control wires  $\frac{R^n}{p}$ ,  $\frac{R^n}{t}$ , and  $\underline{T}^n$ . Its <u>i</u>th cell  $\underline{b}^n$  is connected to the <u>i</u>th component  $\underline{t}_i$  of the trunk.

The control wire  $\underline{T}^n$  is the <u>transmit</u> wire for bin  $\underline{n}$ . When it is activated, the bit in each cell enters the appropriate component of the trunk, passing from  $\underline{b}^n_i$  through

the lower conjunction element onto  $\underline{t}_i$ , whence  $\underline{t}_i = \underline{T}^n \cdot \underline{b}_i^n$ .

It is convenient to be able to alter an instruction by changing its address without modifying the operand. Hence the wiring of the first four cells of each bin is different from that of the last twelve cells, as shown in Fig. 4. The control wire  $\underline{\mathbb{F}}_p^n$  is the partial reception control for bin  $\underline{n}$ . It connects, by way of the disjunction element, to the last twelve cells  $\underline{b}_4^n$ ,  $\underline{b}_5^n$ , ...,  $\underline{b}_{15}^n$ . If it is activated at time  $\mathcal{T}$  (by instruction 11 of Fig. 2), and  $\underline{\mathbb{F}}_t^n$  is not activated, then whatever bit is on trunk component  $\underline{t}_1$  ( $\underline{i} = 4$ , 5, ..., 15) at time  $\mathcal{T}$  will flow through the upper left conjunction element of cell  $\underline{b}_1^n$  onto  $\underline{h}_1$ , from which it will emerge at  $\mathcal{T}+1$  to occupy  $\underline{b}_1^n$ , in which case  $\underline{b}_1^n(\mathcal{T}+1) \equiv \underline{t}_1(\mathcal{T})$  for  $\underline{i} = 4$ , 5, ..., 15, and  $\underline{b}_1^n(\mathcal{T}+1) \equiv \underline{b}_1^n(\mathcal{T})$  for  $\underline{i} = 0$ , 1, 2, 3.

The control wire  $\underline{\mathbb{R}}^n_t$  is the total reception control for bin  $\underline{n}$ . It connects directly to the first four cells and by way of the disjunction element to the last twelve cells also. If it is activated at time  $\mathcal{T}$  (by instruction 10), then whatever bit is on trunk component  $\underline{t}_1$  at time  $\mathcal{T}$  will occupy cell  $\underline{b}^n_1$  at time  $\mathcal{T}+1$ ; in this case  $\underline{b}^n_1(\mathcal{T}+1) \equiv \underline{t}_1(\mathcal{T})$ .

The storage bin's behavior is described more compendiously by the equations  $\underline{b}^n_{\mathbf{i}}(\mathcal{T}+1) \equiv \left[\underline{R}^n_{\mathbf{t}}(\mathcal{T}) \circ \underline{t}_{\mathbf{i}}(\mathcal{T}) \vee \overline{\underline{R}}^n_{\mathbf{t}}(\mathcal{T}) \circ \underline{b}^n_{\mathbf{i}}(\mathcal{T})\right] \quad \text{for} \quad \underline{i} = 0, \dots, 3, \text{ and } \underline{b}^n_{\mathbf{i}}(\mathcal{T}+1) \equiv \left\{\left[\underline{R}^n_{\mathbf{t}}(\mathcal{T}) \vee \underline{R}^n_{\mathbf{p}}(\mathcal{T})\right] \underline{t}_{\mathbf{i}}(\mathcal{T}) \vee \overline{\underline{R}}^n_{\mathbf{t}}(\mathcal{T}) \circ \underline{\underline{E}}^n_{\mathbf{p}}(\mathcal{T}) \circ \underline{b}^n_{\mathbf{i}}(\mathcal{T})\right\} \quad \text{for} \quad \underline{i} = 4, \dots, 15.$

## 4.3. Address Decoder.

For the computer to use the information in its parallel storage, it must have some method of switching to or selecting a specified location there. Twelve binary digits suffice to specify any storage bin uniquely. The Address Decoder is a switching mechanism which activates the proper storage bin when it receives the twelve digit number which is the address of that bin.

The Address Decoder has 4,096 distinct output wires  $\underline{p}_0$ ,  $\underline{p}_1$ , ...,  $\underline{p}_{4095}$ , each connected to a distinct storage bin of the parallel storage. Each distinct  $\underline{p}_i$  is activated by a different set of twelve digits which may be carried by the Address Decoder's twelve input wires  $\underline{s}_4$ ,  $\underline{s}_5$ , ...,  $\underline{s}_{15}$ . The functional connection is accomplished through the use of 4,096 threshold-12 elements, as shown in Fig. 5. The same twelve input wires are connected to each of the 4,096 threshold-12 elements, those connections being described by the equations:  $\underline{p}_0 \equiv (\underline{s}_4 \underline{s}_5 \cdots \underline{s}_{14} \underline{s}_{15})$ ,  $\underline{p}_1 \equiv (\underline{s}_4 \underline{s}_5 \cdots \underline{s}_{14} \underline{s}_{15})$ ,  $\underline{p}_{4095} \equiv (\underline{s}_4 \underline{s}_5 \cdots \underline{s}_{14} \underline{s}_{15})$ .

General directions for the parallel storage are carried by control wires  $\underline{S}_{rp}$ ,  $\underline{S}_{rt}$ , and  $\underline{S}_{t}$  (Figs. 1 and 5), at most one of which is in state 1 at any time. Each of these control wires is connected to 4,096 different conjunction elements, whose other input wires are the 4,096

distinct  $\underline{p_i}$ 's. Since at most one of the control wires  $\underline{\underline{S}_{rp}}$ ,  $\underline{\underline{S}_{rt}}$ ,  $\underline{\underline{S}_{t}}$  is activated at any time, and exactly one of the Address Decoder's output wires  $\underline{p_0}$ ,  $\underline{p_1}$ , ...,  $\underline{p_{4095}}$  is activated at any given time, there is at any given time at most one bin  $\underline{n}$  for which any of the control wires  $\underline{\underline{R}_p^n}$ ,  $\underline{\underline{R}_t^n}$ ,  $\underline{\underline{T}_t^n}$  is activated at that time, and, if there is such a bin  $\underline{n}$ , at most one of those three control wires  $\underline{\underline{R}_p^n}$ ,  $\underline{\underline{R}_t^n}$ ,  $\underline{\underline{T}_t^n}$  is activated at that time. The equations which describe the circuits diagrammed in Fig. 5 are of the form:  $\underline{\underline{R}_p^n} \equiv (\underline{\underline{S}_{rp}} \cdot \underline{\underline{p}_n})$ ,  $\underline{\underline{R}_t^n} \equiv (\underline{\underline{S}_{rt}} \cdot \underline{\underline{p}_n})$ ,  $\underline{\underline{T}_t^n} \equiv (\underline{\underline{S}_{t}} \cdot \underline{\underline{p}_n})$ .

For example, in the execution of instruction 4 of Fig. 2, ADD X, the operand 0100 of that instruction causes control wire  $\underline{S}_t$  to be stimulated and the address  $\underline{x}_4\underline{x}_5...\underline{x}_{15}$  enters the input wires of the Address Decoder to stimulate its output wire  $\underline{p}_x$ . That stimulates  $\underline{T}^x$ , the output wire of a conjunction element whose two input wires are  $\underline{S}_t$  and  $\underline{p}_x$ , to make the number in bin  $\underline{X}$  pass onto the trunk where it is available to the ARITHMETIC UNIT.

Here and throughout this paper we speak as if the electrical response of a circuit were instantaneous, which is not strictly accurate. For our remarks to be made unobjectionable we need only make the duration of the time interval we refer to as a "moment" sufficiently large to permit the signal to pass from any part of the machine to any other part during that interval. Our "moments" need

not all be of the same duration, of course, and intervals of any different durations may lie between what we refer to as "successive moments." It should be kept in mind that the shorter the durations of these "moments" and the shorter the time lapses between them, the higher the speed of computation that can be achieved by the machine.

These remarks should suffice to indicate that the states 0 and 1 of our wires need not be pulses, but can alternatively be static states. It is, of course, part of the idealized representational function of our diagrams that they permit of either interpretation.

In practice a relatively uncomplicated physical device may correspond to a very complex logical net; no one-to-one correspondence is suggested between the elements of our diagrams and the physical components of the computing machine which realizes them. For example, our general design for the parallel storage (less the keys) can be realized physically without using separate delay lines, as by a Williams, tube cathode ray storage device which consists of many tubes and associated circuits. The delay elements in our diagrams represent the fact that information is stored, but do not represent the specific physical devices that may be used to accomplish that storage function. Our design is intended to represent the logical role rather than the physical constitution of a computer and its parts. Hence many

of the details of the circuits involved in the Williams' tube storage (pulse shaper, etc.) are not represented by our diagrams. Nor is the breakdown into parts similar, for a single tube will store bits from many bins (say, 1024 of them), with the contents of a single bin distributed over sixteen different tubes.

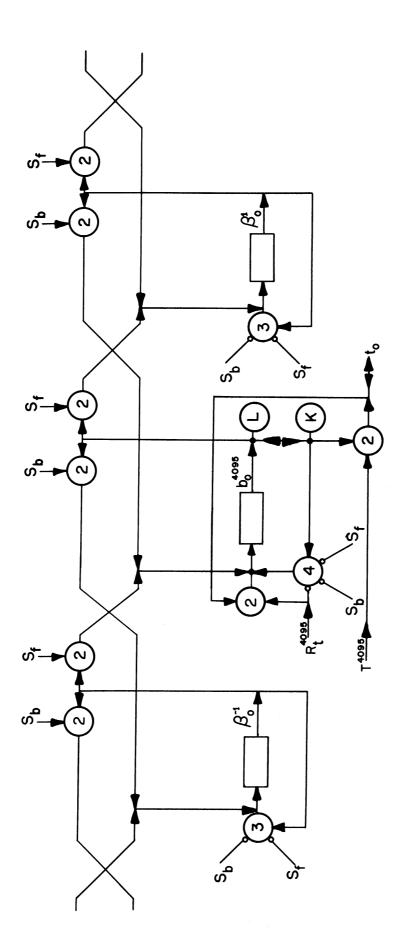

### 4.4. Serial Storage.

In addition to the relatively limited parallel storage already described, our computer has a theoretically infinite serial storage, which supplements the parallel storage. The serial storage consists of sixteen parallel strings of cells, every cross section of which may be regarded as a storage bin. Our computer is so designed that exactly one storage bin belongs to both the parallel storage and the serial storage. For definiteness, we specify it to be bin 4095 of the parallel storage, which must be given somewhat more complicated cells to enable it to play its dual role. In Fig. 6, which shows only three cells of the topmost string, the middle cell diagrammed belongs to this special bin. Each string is to be thought of as extending indefinitely in both directions.

It is clear from the diagram that if neither of the control wires  $\underline{S}_b,\underline{S}_f$  is activated, every bin of the serial storage save  $\underline{b}^{4095}$  continues to store whatever information

it contains, and if  $\underline{R}_p^{4095} \equiv \underline{R}_t^{4095} = 0$ , then  $\underline{b}^{4095}$  also continues to store whatever information it contains. Now, if control wire  $\underline{S}_b$  ( $\underline{S}_f$ ) is activated at time  $\mathcal{T}$ , the internal circulation or storage of information in each cell is interrupted at the threshold-3 element in each ordinary cell and at the threshold-4 element in each special cell of the shared bin, and any bit of information in each cell will pass up the wire to the right of its delay element, through the left (right) conjunction element above, and down to the input wire of the delay element of the cell to its left (right).

If we assign the labels ...,  $\beta_{i}^{-2}$ ,  $\beta_{i}^{-1}$ ,  $\beta_{i}^{0}$ ,  $\beta_{i}^{1}$ ,  $\beta_{i}^{2}$ , ... to the cells of the serial storage, where  $\beta_{i}^{0}$  is  $\underline{b}_{i}^{4095}$ , the behavior of the serial storage is described by the expression

$$\begin{split} \overline{\mathbb{E}}_{p}^{4095} \cdot \overline{\mathbb{E}}_{t}^{4095} \supset & \left\{ \mathcal{S}_{i}^{n}(\tau + 1) \equiv \left[ \underline{s}_{b}(\tau) \cdot \beta_{i}^{n+1}(\tau) \vee \underline{s}_{f}(\tau) \cdot \beta_{i}^{n-1}(\tau) \vee \underline{s}_{b}(\tau) \cdot \underline{s}_{f}(\tau) \cdot \beta_{i}^{n}(\tau) \right] \right\} \;\;, \end{split}$$

where  $\underline{n} = ..., -2, -1, 0, 1, 2, ...$

If a word located in an ordinary bin of the serial storage is to be used, the contents of the serial storage must be shifted backward or forward until that word occupies the special bin  $\underline{b}^{4095}$ , from which it is immediately available to the computer as described in Section 4.2. Hence the greater capacity of the serial storage is purchased, so to

speak, at the expense of ready availability of its contents.

At this point the analogy should be noted again between our diagrammatic conventions and the process of definition. Just as a single term can be introduced as an abbreviation for a whole sequence of other terms, so some parts of our diagrams are to be understood as definitional abbreviations for other, more complicated parts. We have already pointed out that each right-hand diagram in Figs. 3b, c, d, f, and g is a definitional abbreviation of the diagram to its left. Similarly, in Fig. 5 each box bn is to be understood as a shorthand notation for the more detailed diagram of storage bin bn presented in Fig. 4. (Both, it should be noted, are connected to the same three control wires and the same sixteen components of the trunk.) And the block labeled STORAGE in Fig. 1 is a definitional abbreviation of the complete net whose parts are represented in Figs. 5 and 6, that is, of the combined and interconnected parallel and serial storages.

# 5. ARITHMETIC UNIT.

# 5.1. Machine Arithmetic.

Before describing the operation of the ARITHMETIC UNIT we must discuss the arithmetic of the machine.

A binary numerical expression  $+0.\underline{x}_1...\underline{x}_{15}$  ( $\geq 0$ ) is directly represented in the machine by the word  $0\underline{x}_1...\underline{x}_{15}$ , and a binary number  $-0.\underline{x}_1...\underline{x}_{15}$  (< 0) by the word  $2-.\underline{x}_1...\underline{x}_{15}$ . For example, +.110...0 (+3/4) is directly represented by 0.110...0, and -.110...0 (-3/4) by 1.010...0. Clearly any binary number  $\underline{x}$  in the range  $-1 < \underline{x} < 1$  can be directly represented in the machine to within  $2^{-15}$ . Numbers outside this range can be indirectly represented in the machine through shifting them into the range by multiplying them by  $2^{-n}$  with some appropriate  $\underline{n}$ .

The binary point of a number is not directly represented in the machine. However, it is convenient to imagine, and sometimes to show, a binary point to the right of the leftmost bit of every machine word that directly represents a number.

It will be convenient to introduce an additional convention at this time. Just as a symbol like  $\underline{b_i}$  may either name a wire or symbolize a function (which takes on one of the two values 0,1 at each time  $\tau$ ) (see Section 3), so a symbol like  $\underline{b}$  may either name a sequence of sixteen

wires  $\underline{b}_0$ , ...,  $\underline{b}_{15}$  or symbolize a function (which takes on one of the  $2^{16}$  values: 0.0...00, 0.0...01, ..., 1.1...10, 1.1...11 at each time  $\mathcal{T}$ ). Our earlier use of  $\underline{t}$  (Section 2) to stand for the trunk consisting of the wires  $\underline{t}_0$ , ...,  $\underline{t}_{15}$  accords with this convention.

We shall introduce four operations on machine words: machine addition, machine subtraction, machine doubling, and machine halving; defining them so as to maintain a certain correspondence with the analogous operations of ordinary arithmetic. Where x and y are machine words which directly represent the numbers lpha and eta , respectively, and z is the result of performing machine addition on  $\underline{x}$  and  $\underline{y}$ , then if  $\alpha + \beta$  can be directly represented in the machine, it is directly represented by z, whereas if  $\alpha + \beta$  can not be directly represented in the machine, z directly represents a number congruent to  $\alpha + \beta$  modulo 2. Similar remarks apply for the other three operations also. We will hereafter use the signs x+y, -x+y, 2y, and (1/2)y to denote our four machine operations. Basically, the machine does arithmetic modulo 2 with a precision of one part in  $2^{15}$ . For example, 0.110...0+0.110...0=1.100...0, i.e., 3/4+3/4=-(1/2), since  $3/4 + 3/4 \equiv -(1/2)$  modulo 2; and halving 0.0...01  $(2^{-15})$  gives 0, while halving 1.1...11  $(-2^{-15})$  gives -2<sup>-15</sup>

The machine operations of addition, subtraction, doubling, and halving are the only machine arithmetic operations for which there are instructions in Fig. 2. However, other machine operations (e.g., multiplication, division), as well as machine operations on numbers which cannot be directly represented in the machine, can be programmed; that is, there exist routines (sequences of instructions of Fig. 2) for making the machine perform these additional operations.

Our machine arithmetic operations are to be performed by nets constructed out of our logical elements, and these nets must all be realized by our ARITHMETIC UNIT. The machine arithmetic operations performed on sixteen digit words  $(\underline{x},\underline{y})$  must be defined in terms of logical operations performed on the several bits  $(\underline{x}_i,\underline{y}_i)$  of those words.

We first define machine addition. Our task is to express

$$(A) \qquad z = x + y$$

as a logical relation between  $\underline{x}_i$ ,  $\underline{y}_i$ , and  $\underline{z}_i$ . It is helpful to define the auxiliary word  $\xi$  whose  $\underline{i}$ -lst bit  $\underline{\xi}_{i-1}$  ( $\underline{i}$  > 0) is the carry digit from the addition of the three summands:  $\underline{x}_i$ ,  $\underline{y}_i$ , and the carry digit  $\underline{\xi}_i$ . It is clear that  $\underline{\xi}_{15}$  is 0, and that  $\underline{z}_i$  is 1 if and only if an odd number of the summands  $\underline{x}_i$ ,  $\underline{y}_i$ ,  $\underline{\xi}_i$  are 1. The

result concerning inequivalence established in Section 3 enables us to express this rule by

$$(A_1) \qquad \underline{z_1} = (\underline{x_1} \neq \underline{y_1} \neq \underline{\xi_1}).$$

And since  $\xi_{i-1}$  is 1 just in case at least two of the three summands are 1, we have the equations:

$$(A_2) \qquad \xi_{i-1} \equiv (\underline{x}_i \underline{y}_i \underline{v} \underline{x}_i \xi_i \underline{v} \underline{y}_i \xi_i) \quad \text{for } \underline{i} > 0,$$

$$(A_3)$$

$\xi_{15} = 0.$

Before defining machine subtraction we introduce the machine operation of complementation  $\underline{C}$ , whose field consists of words. We define  $\underline{C}(\underline{x})$  to be the machine representation of that number within the range  $-1 < \underline{x} < 1$  which is congruent modulo 2 to  $2-\underline{x}$ . The complementation operation is very useful because a negative number  $-.\underline{x}_1...\underline{x}_{15}$  is directly represented in our machine by  $\underline{C}(0.\underline{x}_1...\underline{x}_{15})$ . Machine complementation is related to logical complementation (negation) in the following way. We define

$$\overline{\underline{x}} =_{df} \overline{\underline{x}}_0 \cdot \overline{\underline{x}}_1 \cdots \overline{\underline{x}}_{15};$$

and refer to  $\bar{x}$  as the bitwise complement of  $\bar{x}$ . Now 2 is the arithmetic sum of 1.11...11 and  $2^{-15}$ , and clearly  $\bar{x} = 1.11...11-x$ , whence

$$\underline{\mathbf{c}}(\underline{\mathbf{x}}) = \underline{\overline{\mathbf{x}}}_0 \cdot \underline{\overline{\mathbf{x}}}_1 \dots \underline{\overline{\mathbf{x}}}_{15} + 0.0 \dots 01.$$

Machine complementation is therefore performed on a number by adding  $2^{-15}$  to the bitwise complement of that number.

Since the arithmetic operation of subtracting  $\varpropto$  from  $\beta$  is equivalent to the addition of the negative of  $\varpropto$  to  $\beta$  ,

we can define machine subtraction in terms of complementation and addition. Thus, the formula for machine subtraction

(S)

$$\underline{z} = -\underline{x} + \underline{y}$$

becomes

$$\underline{z} = \underline{C}(\underline{x}) + \underline{y} = \underline{\overline{x}} + \underline{y} + 0.0...01.$$

By using  $(A_1)$  and  $(A_2)$  we can translate  $\underline{z} = \overline{\underline{x}} + \underline{y}$  into logical terms; and since  $\xi_{15}$  is one of the summands in the rightmost digital position, the addition of  $2^{-15}$  can be accomplished by setting  $\xi_{15}$  equal to 1. Thus, machine subtraction of the word  $\underline{x}$  from the word  $\underline{y}$  can be defined in terms of the following logical relations among the bits

$$\underline{x}_i$$

,  $\underline{y}_i$ ,  $\underline{\xi}_i$ , and  $\underline{z}_i$ .

$$(s_1) \qquad \underline{z}_i \equiv (\underline{\overline{x}}_i \not\equiv \underline{y}_i \not\equiv \underline{\xi}_i),$$

(S<sub>2</sub>)

$$\xi_{i-1} = (\overline{\underline{x}}_i \underline{y}_i \vee \overline{\underline{x}}_i \xi_i \vee \underline{y}_i \xi_i)$$

for  $\underline{i} > 0$ ,

$$(s_3)$$

$\xi_{15} = 1.$

To define machine doubling we want to express

(D)

$$\underline{z} = 2\underline{y}$$

in logical terms. Since a 1 in the <u>i</u>th position has twice the value of a 1 in the <u>i</u>+lst position, doubling consists merely of shifting each digit of  $\underline{y}$  left one binary position with respect to the binary point. We express (D) in terms of the logical operations on the bits  $\underline{y}_i$  by

$$(D_1) \underline{z_i} \equiv \underline{y_{i+1}} \text{for } \underline{i} < 15,$$

$$(D_2)$$

$\underline{z}_{15} = 0.$

Similarly, halving is accomplished by a right shift. We define machine halving,

$$(H) \underline{z} = (1/2)\underline{y},$$

bу

$$(H_1) \qquad \underline{z}_1 \equiv \underline{y}_{1-1} \quad \text{for} \quad \underline{i} > 0,$$

$$(H_2) \qquad \underline{z}_0 \equiv \underline{y}_0.$$

# 5.2. Operation of the CONTROL.

Instructions 4, 5, 6, 7, 8, 9, 10, and 11 of Fig. 2 all involve the ARITHMETIC UNIT. Before describing how the ARITHMETIC UNIT is to function in their execution, we must explain briefly how the CONTROL affects the ARITHMETIC UNIT. Exactly how the CONTROL performs the functions we are going to describe will be explained later in Section 6.

Since the instructions involving the ARITHMETIC UNIT all refer to a "number in the ARITHMETIC UNIT", it will be convenient to have a way of referring to this number. We will stipulate that it is located on the sequence of wires a.

At any time  $\mathcal{T}$  the wire sequence  $\underline{d}_0$ ,  $\underline{d}_1$ ,  $\underline{d}_2$ ,  $\underline{d}_3$  is in exactly one of sixteen distinct states. These sixteen states, together with the state of the CONTROL CLOCK, completely determine the states of the thirteen control wires labeled  $\underline{A}$ ,  $\underline{S}$ , and  $\underline{C}$  with appropriate subscripts. (When the machine is inoperative, none of the wires is stimulated.) Fig. 2 tells what control wires are activated for the various

states of  $\underline{d}_0$ ,  $\underline{d}_1$ ,  $\underline{d}_2$ ,  $\underline{d}_3$  when the machine is operating; control wires not marked as active are stipulated to be inactive. The state llll can occur only by a mistake in programming; when it does occur, no control wires are activated, and it produces no effect.

When one of the instructions 4, 5, 6, 7 is being executed, the CONTROL will activate  $\underline{S}_t$  and also send the address  $\underline{X}$  to  $\underline{s}_4$ , ...,  $\underline{s}_{15}$ , thereby causing the STORAGE to transmit the number in storage bin  $\underline{X}$  to the trunk  $\underline{t}$ . Hence we may assume that when these instructions are being executed the number in storage bin  $\underline{X}$  is on  $\underline{t}$  and therefore available to the ARITHMETIC UNIT.

When instruction 10 or 11 is being executed, the CONTROL will activate  $\underline{S}_{rt}$  or  $\underline{S}_{rp}$ , respectively, and will also send the address  $\underline{X}$  to  $\underline{s}_4$ , ...,  $\underline{s}_{15}$ , causing bin  $\underline{X}$  to receive in the desired fashion any number on the trunk  $\underline{t}$ . Hence we must so design the ARITHMETIC UNIT that these instructions cause the contents of  $\underline{a}$  to occupy  $\underline{t}$ .

We may summarize the effect of the CONTROL on the ARITHMETIC UNIT as follows. When one of the instructions 4 through 11 is being executed, control wires  $\underline{A}_r$ ,  $\underline{A}_h$ ,  $\underline{A}_c$ ,  $\underline{A}_{1s}$ ,  $\underline{A}_{rs}$ ,  $\underline{A}_{tt}$  are in the states shown in Fig. 2; at any other time these wires are all inactive. When instruction 4, 5, 6, or 7 is being executed, the number in bin  $\underline{X}$  is also on the trunk  $\underline{t}$ . Finally, when instruction 10 or 11 is

being executed, the CONTROL causes whatever number the ARITHMETIC UNIT places on  $\underline{t}$  to be properly received by the correct bin.

#### 5.3. The Functions of the ARITHMETIC UNIT.

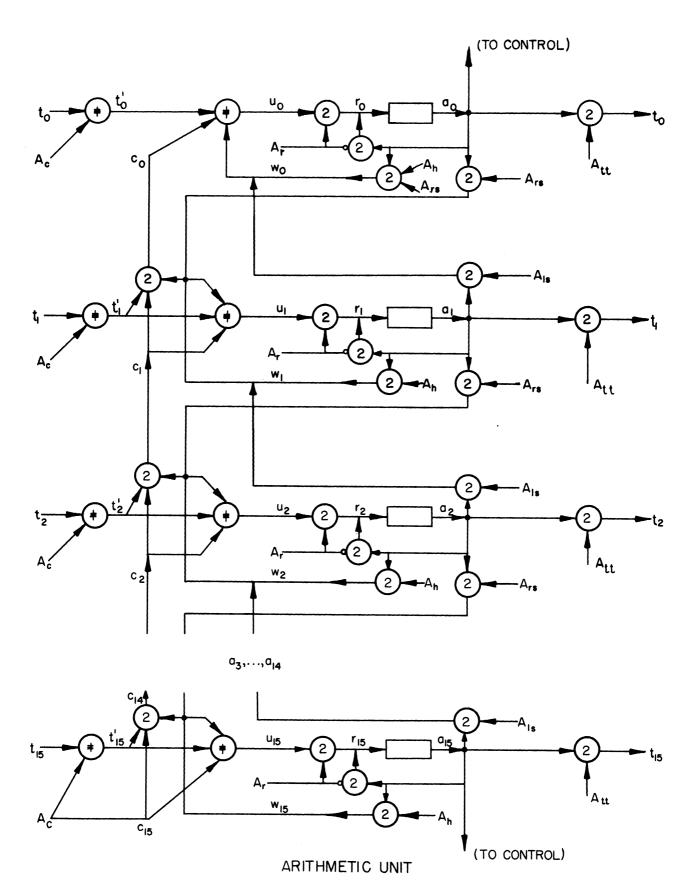

In the previous subsection we described every possible way for information to be directed to the ARITHMETIC UNIT by the CONTROL. In this subsection we consider three general functions performed by the ARITHMETIC UNIT on the basis of this information, and explain how it performs the first two.

The first function is the transmission of information. When either instruction 10 or 11 is executed, the ARITHMETIC UNIT is to transmit its contents onto the trunk  $\underline{t}$ . If either of these instructions is executed (see Fig. 2)  $\underline{A}_{tt}$  will be stimulated, hence we want the machine to realize the expression

$$\underline{A}_{tt} \supset (\underline{a}_i = \underline{t}_i).$$

This function is accomplished by the conjunction elements to the right in Fig. 7. The ARITHMETIC UNIT is also to supply the bits  $\underline{a}_0$  and  $\underline{a}_{15}$  to the CONTROL, which is accomplished simply by running wires from these cells to the CONTROL as indicated in Fig. 7. We will simplify the discussion of the remainder of this section by ignoring the transmission function of the ARITHMETIC UNIT (and the relevant parts of Fig. 7).

The second function performed by the ARITHMETIC UNIT is storage. It is clearly required that when the ARITHMETIC UNIT is not executing any of the instructions 4 through 9, it must continue to store the number  $\underline{a}$ . Inspection of Fig. 2 shows that  $\underline{A}_{\mathbf{r}}$  is activated when and only when one of the instructions 4 through 9 is being executed. Hence when  $\underline{A}_{\mathbf{r}}(\mathcal{T}) = 0$  we want  $\underline{a}(\mathcal{T}) = \underline{a}(\mathcal{T}+1)$ . This storage may be accomplished by using sixteen delay elements, with input wires  $\underline{r}_0, \ldots, \underline{r}_{15}$  and output wires  $\underline{a}_0, \ldots, \underline{a}_{15}$ , as in Fig. 7, so connected that

$$\overline{\underline{A}}_{r} \supset (\underline{r}_{i} \equiv \underline{a}_{i}).$$

Since  $\underline{a}_{i}(\tau+1) = \underline{r}_{i}(\tau)$ , the ARITHMETIC UNIT does perform the desired storage function.

The third function performed by the ARITHMETIC UNIT is the modification of its contents from  $\underline{a}(\mathcal{T})$  to  $\underline{a}(\mathcal{T}+1)$  in accordance with instruction 4, 5, 6, 7, 8, or 9, which we shall refer to as arithmetic instructions. The design of a net which will realize the arithmetic instructions is the most complicated and difficult part of the task of designing the machine. To it we devote both the following subsection and Appendix E.

## 5.4. Execution of the Arithmetic Instructions.

In this subsection we shall derive a set of formulas which the ARITHMETIC UNIT must realize for the arithmetic instructions to be executed. We derive them by combining the various arithmetic instructions with the equations (A), (S), (D), and (H) of Section 5.1, which define the various machine arithmetic operations. We note that the result of an operation performed at time  $\mathcal{T}$  is to appear at  $\underline{r}$  at time  $\mathcal{T}$  and at  $\underline{a}$  at time  $\mathcal{T}+1$ .

Instruction 4 demands that r contain the result of performing the machine addition of the number at t to the number at a. For the ARITHMETIC UNIT to fulfill its intended function, it must realize the conditional If ADD X is enjoined, then  $\underline{r} = \underline{t} + \underline{a}$ . Now by Fig. 2, ADD X is the only instruction which involves the stimulation of  $\underline{A}_r$  and  $\underline{A}_h$  but not  $\underline{A}_c$ . Hence the antecedent of  $(A^m)$  may be replaced by  $\underline{A}_r \underline{A}_h \overline{\underline{A}}_c$ . And a translation of the consequent of (A<sup>m</sup>) into a logical formula concerning the states of individual wires may be made by using  $(A_1)$ ,  $(A_2)$ , and  $(A_3)$ , substituting  $\underline{r}_1$  for  $\underline{z}_1$ ,  $\underline{t}_1$ for  $\underline{x}_i$ , and  $\underline{a}_i$  for  $\underline{y}_i$ . In the ARITHMETIC UNIT we are constructing, the auxiliary word & will be realized by the set of wires  $\underline{c_0}$ ,  $\underline{c_1}$ , ...,  $\underline{c_{15}}$ ; hence we also substitute  $\underline{c}_1$  for  $\xi_1$  in the (A) equations. We thus obtain the following formulas for the ARITHMETIC UNIT to realize:

$$(A_1^m) \qquad \underline{A}_r \underline{A}_h \overline{\underline{A}}_c \supset \{\underline{r}_i \equiv (\underline{t}_i \not\equiv \underline{a}_i \not\equiv \underline{c}_i)\},$$

$$(A_2^m) \qquad \underline{A}_r \underline{A}_h \underline{\overline{A}}_c \supset \{\underline{c}_{i-1} \equiv (\underline{t}_i \underline{a}_i \vee \underline{t}_i \underline{c}_i \vee \underline{a}_i \underline{c}_i) \} \text{ for } \underline{i} > 0,$$

$$(A_3^m) \qquad \underline{A}_r \underline{A}_h \underline{\overline{A}}_c \supset \{\underline{c}_{15} = 0\}.$$

A set of formulas for the ARITHMETIC UNIT to realize to execute instruction 5 may be derived from the (S) equations in a parallel way. We thus obtain

(S<sup>m</sup>) If SUBTRACT X is enjoined, then

$$\underline{r} = -\underline{t} + \underline{a}$$

,

$$(S_1^m) \qquad \underline{A}_r \underline{A}_h \underline{A}_c \supset \left\{ \underline{r}_i \equiv (\overline{\underline{t}}_i \neq \underline{a}_i \neq \underline{c}_i) \right\} ,$$

$$(S_2^m) \qquad \underline{A}_r \underline{A}_h \underline{A}_c \supset \{\underline{c}_{i-1} \equiv (\underline{\overline{t}}_i \underline{a}_i \vee \underline{\overline{t}}_i \underline{c}_i \vee \underline{a}_i \underline{c}_i)\} \text{ for } \underline{i} > 0,$$

$$(S_3^m) \qquad \underline{A}_r \underline{A}_h \underline{A}_c \supset \{\underline{c}_{15} = 1\} .$$

Instruction 6 demands the replacement of  $\underline{r}$  by  $\underline{t}$ . For it to be executed, the ARITHMETIC UNIT must realize the conditional

(T<sup>m</sup>) If TRANSFER X is enjoined, then  $\underline{r} = \underline{t}$ . Consulting Fig. 2, we find that this can be represented as  $(T_1^{\underline{m}})$   $\underline{A}_{\underline{r}}\underline{\overline{A}}_{\underline{h}}\underline{\overline{A}}_{\underline{c}} \supset (\underline{r}_{\underline{i}} = \underline{t}_{\underline{i}})$ .

Instruction 7 demands that  $\underline{r}$  be replaced by  $-\underline{t}$ ; for it to be executed the ARITHMETIC UNIT must realize the conditional

(TC<sup>m</sup>) If TRANSFER COMPLEMENT X is enjoined, then  $\underline{r} = \underline{C}(\underline{t})$ . Since  $-\underline{t} = -\underline{t} + 0$ , the formulas required here can be regarded as special cases of the (S) formulas, with 0 substituted for  $\underline{y}$ . After that substitution has been made,

the resulting formulas easily simplify to

$$(TC_1^m) \qquad \underline{A}_{\underline{r}}\underline{\overline{A}}_{\underline{h}}\underline{A}_{\underline{c}} \supset \{\underline{r}_{\underline{i}} \equiv (\underline{\overline{t}}_{\underline{i}} \neq \underline{c}_{\underline{i}})\},$$

$$(TC_2^m) \qquad \underline{A}_r \underline{\overline{A}}_h \underline{A}_c \supset \{\underline{c}_{i-1} \equiv (\underline{\overline{t}}_i \underline{c}_i)\} \text{ for } \underline{i} > 0,$$

$$(TC_3^m) \qquad \underline{A}_r \underline{\overline{A}}_h \underline{A}_c \supset \{\underline{c}_{15} = 1\},$$

which the ARITHMETIC UNIT must realize to execute instruction 7.

Instruction 8 demands that  $\underline{r}$  be replaced by  $2\underline{a}$ ; for it to be executed the ARITHMETIC UNIT must realize the conditional

(D<sup>m</sup>) If DOUBLE is enjoined, then  $\underline{r} = 2\underline{a}$ .

Again substituting  $\underline{r}$  for  $\underline{z}$  and  $\underline{a}$  for  $\underline{y}$ , this time in the (D) formulas, and consulting Fig. 2, we obtain

$$(D_1^m) \qquad \underline{A}_{\underline{r}}\underline{A}_{1s} \supset \{\underline{r}_i \equiv \underline{a}_{i+1}\} \text{ for } \underline{i} > 0,$$

$$(D_2^m) \qquad \underline{A}_{r}\underline{A}_{ls} \supset \{\underline{r}_{15} = 0\}.$$

These formulas must be realized by the ARITHMETIC UNIT for it to execute instruction 8.

Instruction 9 demands that  $\underline{r}$  be replaced by  $(1/2)\underline{a}$ ; for it to be executed the ARITHMETIC UNIT must realize the conditional

(H<sup>m</sup>) If HALVE is enjoined, then  $\underline{r} = (1/2)\underline{a}$ .

Again we substitute  $\underline{r}$  for  $\underline{z}$  and  $\underline{a}$  for  $\underline{y}$ , this time in the (H) formulas, and consult Fig. 2, to obtain

$$(H_1^m)$$

$\underline{A}_{\underline{r}}\underline{A}_{\underline{r}}\underline{S} \supset \{\underline{r}_i \equiv \underline{a}_{i-1}\}$  for  $\underline{i} > 0$ ,

$$(H_2^m) \qquad \underline{A}_{r}\underline{A}_{rs} \supset \left\{\underline{r}_0 \equiv \underline{a}_0\right\}.$$

These must be realized by the ARITHMETIC UNIT if it is to execute instruction 9.

$$(K) \qquad \underline{\overline{A}}_{r} \supset (\underline{r}_{1} \equiv \underline{a}_{1})$$

and

(K')

$$\underline{a}_{i}(T+1) \equiv \underline{r}_{i}(T),$$

complete specification of the ARITHMETIC UNIT (since we have agreed to neglect its transmission function). Any logical net which realizes these sixteen defining formulas will be a satisfactory ARITHMETIC UNIT. It is readily verified that Fig. 7 is such a net, by observing that the last formula above is satisfied by the delay elements, and then taking each of the remaining formulas in turn and determining that under the conditions stated each ri has the proper relations to ai and ti. Performing this verification will facilitate understanding how the ARITHMETIC UNIT works.

# 6. CONTROL.

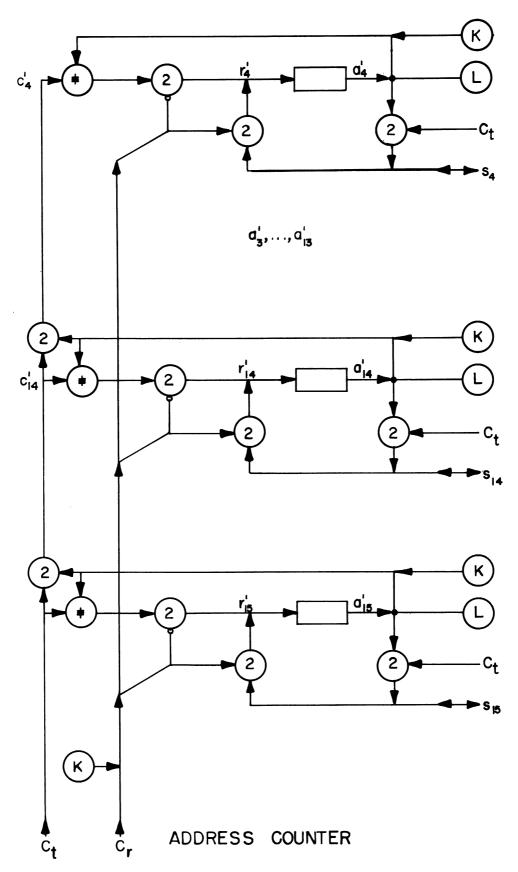

## 6.1. ADDRESS COUNTER.

Apart from "jump" instructions (12, 13, 14 of Fig. 2) the computer executes in order the instructions stored in a sequence of bins of the parallel storage. To do so it must count off those instructions as they are executed, and this function is performed by the ADDRESS COUNTER diagrammed in Fig. 8.

Each of its twelve cells  $\underline{a}_{1}^{1}$ ,  $\underline{a}_{5}^{1}$ , ...,  $\underline{a}_{15}^{1}$  can receive and store one bit of information, so the ADDRESS COUNTER as a whole can receive and store a twelve digit number  $\underline{x}_{4}\underline{x}_{5}...\underline{x}_{15}$ . If all control wires are in state 0 and no keys are activated, each cell a! continues to store whatever information it contains. Any number in the ADDRESS COUNTER is the address of some bin of the parallel storage. To load the ADDRESS COUNTER with the address of the bin containing the first instruction we want the machine to execute, we must be able to change the contents of the ADDRESS COUNTER. The keys shown in Fig. 8 enable us to make any desired change. Activating the key at the lower left (when the machine is idle) clears all of its cells to O, and activating the key of cell  $\underline{\mathbf{a}}_{\mathbf{i}}^{\mathbf{i}}$  at time  $\mathcal{T}$  makes  $\underline{\mathbf{a}}_{\mathbf{i}}^{\mathbf{i}}(\mathcal{T}+1) = 1$ ; thus we can load the ADDRESS COUNTER with any number we please.

As remarked at the bottom of the TABLE OF INSTRUCTIONS on Fig. 2, at every even numbered time  $\mathcal{T}=2\underline{k}$  when the machine is operating, control wires  $\underline{S}_t$  and  $\underline{C}_t$  are activated. At any such time, then,  $\underline{C}_t=1$  permits the bit stored in cell  $\underline{a}_1^*$  to pass through the rightmost conjunction element onto  $\underline{s}_1$  ( $\underline{i}=4,5,\ldots,15$ ). Since  $\underline{s}_4$ ,  $\underline{s}_5$ , ...,  $\underline{s}_{15}$  are input wires to the Address Decoder (see Fig. 5), and since  $\underline{S}_t$  is also activated then, that storage bin whose address is contained in the ADDRESS COUNTER at any even numbered time  $\mathcal{T}=2\underline{k}$  will transmit its contents onto the trunk at that time.

Hence when the computer begins to solve a problem the first instruction it executes is the one stored in that bin whose address is stored in the ADDRESS COUNTER, usually bin 0. To keep track, whenever the ADDRESS COUNTER sends an instruction from the nth bin onto the trunk it must count, that is, add a 1 to the number it contains at that time.

(Any twelve digit number  $\underline{x}_{4}\underline{x}_{5}...\underline{x}_{15}$  contained in the ADDRESS COUNTER is the address of some bin of the parallel storage, and can also constitute the address part of an instruction word, as in  $\underline{d}_{0}\underline{d}_{1}\underline{d}_{2}\underline{d}_{3}\underline{x}_{4}\underline{x}_{5}...\underline{x}_{15}$ . Whenever we consider the numerical aspect of a word we must keep in mind the discussion of range presented in Section 5, and the convention that a binary point is imagined to follow

Let us suppose that the number in the ADDRESS COUNTER at time  $\mathcal{T}$  is  $\underline{x}_{4}\underline{x}_{5}...\underline{x}_{15}$ , and to it we wish to add 1, which is  $\underline{y}_{4}\underline{y}_{5}...\underline{y}_{15}$  where  $\underline{y}_{15}=1$  and  $\underline{y}_{4}=\underline{y}_{5}=...=\underline{y}_{14}=0$ . The sum  $\underline{z}_{4}\underline{z}_{5}...\underline{z}_{15}$  of these two numbers is recursively defined (see Section 5) by the equations:

$$\underline{z}_{i} \equiv (\underline{x}_{i} \neq \underline{y}_{i} \neq \underline{\xi}_{i})$$

and

$\xi_{i-1} = (\underline{x}_i \underline{y}_i \vee \underline{x}_i \xi_i \vee \underline{y}_i \xi_i) \text{ where } \xi_{15} = 0.$  Since  $\xi_{15} = 0$  and  $\underline{y}_{15} = 1$ , by the first defining equation we have  $\underline{z}_{15} = \underline{x}_{15}$ , and by the second defining equation we have  $\xi_{14} = \underline{x}_{15}$ . Now for every  $\underline{i} < 15$ ,  $\underline{y}_i = 0$ , whence  $\xi_{i-1} = \underline{x}_i \xi_i$ , and also  $\underline{z}_i = (\underline{x}_i \neq \xi_i)$ . These formulas

must be realized by the ADDRESS COUNTER if it is to perform its counting function correctly.

For the formulas developed in the preceding paragraph to be realized by a circuit, that circuit must contain wires corresponding to  $\underline{x}_4$ ,  $\underline{x}_5$ , ...,  $\underline{x}_{15}$ , to  $\underline{\xi}_4$ ,  $\underline{\xi}_5$ , ...,  $\underline{\xi}_{14}$ , and to  $\underline{z}_4$ ,  $\underline{z}_5$ , ...,  $\underline{z}_{15}$ , and these wires must be so connected that their behavior is described by those formulas. If net wires  $\underline{a}_1^i$ ,  $\underline{c}_1^i$ , and  $\underline{r}_1^i$  correspond to  $\underline{x}_1$ ,  $\underline{\xi}_1$ , and  $\underline{z}_1$ , respectively, those wires must realize the equations  $\underline{r}_1^i \equiv (\underline{a}_1^i \neq \underline{c}_1^i)$  and  $\underline{c}_{1-1}^i \equiv \underline{a}_1^i\underline{c}_1^i$  for  $\underline{i} \leq 15$ ,  $\underline{r}_{15}^i \equiv \overline{a}_{15}^i$ , and  $\underline{c}_{1A}^i \equiv \underline{a}_{15}^i$ .

The diagram in Fig. 8 satisfies the preceding equations when  $\underline{C}_r = 0$  and  $\underline{C}_t = 1$ . By assumption,  $\underline{a}^{\dagger} \equiv \underline{x}$ , and since  $\underline{C}_r = 0$  and  $\underline{C}_t = 1$  at every even numbered moment  $\mathcal{T} = 2\underline{k}$ , at every such moment  $\underline{r}^{\dagger}$  will contain the immediate successor of the number in  $\underline{a}$ , and that successor will occupy  $\underline{a}$  at the following moment  $\mathcal{T} = 2\underline{k} + 1$ .

If at an odd numbered moment  $\mathcal{T}=2\underline{k}+1$  a "jump" is to be made in executing instruction 12, 13, or 14 of Fig. 2, control wire  $\underline{C}_{\mathbf{r}}=1$  and  $\underline{C}_{\mathbf{t}}=0$ , and the address  $\underline{X}$  of bin  $\underline{X}$  referred to in the "jump" instruction OBEY X (or OBEY X IF MINUS or OBEY X IF  $\underline{a}_{15}$  IS 1) occupies wires  $\underline{s}_4$ ,  $\underline{s}_5$ , ...,  $\underline{s}_{15}$  (as will be explained in the following section). Since  $\underline{C}_{\mathbf{t}}=0$ , no signal can pass from  $\underline{a}_{\mathbf{t}}^{\mathbf{t}}$  onto

since  $\underline{C}_r = 1$ , no signal can pass from  $\underline{a}_1^!$  to  $\underline{r}_1^!$  through the conjunction element to the left of  $\underline{a}_1^!$ . But the lower left-hand conjunction element permits any bit of information on  $\underline{s}_1$  to pass onto  $\underline{r}_1^!$  at time  $\mathcal{T} = 2\underline{k} + 1$  and to occupy  $\underline{a}_1^!$  at time  $\mathcal{T} = 2\underline{k} + 2$ . Hence the address  $\underline{X}$  of bin  $\underline{X}$  referred to in the "jump" instruction OBEY X will be contained in the ADDRESS COUNTER at time  $\mathcal{T} = 2\underline{k} + 2$ . At that even numbered moment both  $\underline{S}_t$  and  $\underline{C}_t$  are automatically activated, which makes bin  $\underline{X}$  of the parallel storage transmit its contents onto the trunk at time  $\mathcal{T} = 2\underline{k} + 2$ , and causes the ADDRESS DECODER to contain, at the following moment  $\mathcal{T} = 2\underline{k} + 3$ , the address of bin  $\underline{X} + 1$ .

# 6.2. CONTROL CLOCK.

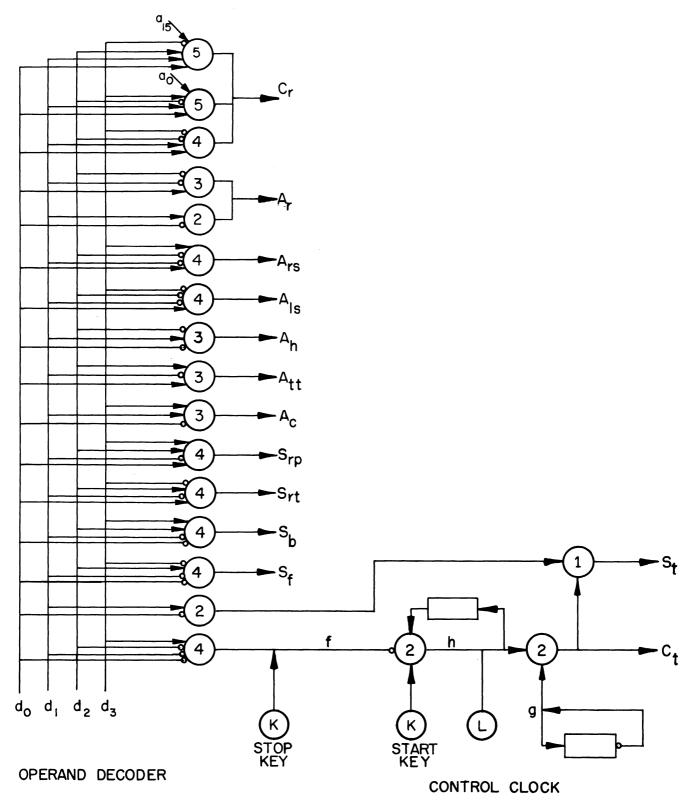

We wish to be able to start the machine at any time, and we want control wires  $\underline{S}_t$  and  $\underline{C}_t$  to be automatically activated at every even numbered moment while the machine is solving a problem. Our device for accomplishing this function is the CONTROL CLOCK, which occupies the lower right-hand part of Fig. 9. The behavior of the right-hand delay circuit, which may be described as a "blocking oscillator circuit", is described by the equation  $\underline{g}(\mathcal{T}) = (\mathcal{T} \equiv 0 \mod 2)$ . Thus  $\underline{g}$  is activated at  $\mathcal{T} = 0$ , 2, 4, ...,  $2\underline{k}$ , ... independently of anything that may happen elsewhere in the machine.

The left-hand delay circuit operates somewhat differently. If the wire  $\underline{f}$  is inactive, then activating the START KEY at time  $\mathcal{T}$  will activate  $\underline{h}$ . At time  $\mathcal{T}+1$  the signal will emerge from the delay element above, and if  $\underline{f}$  is still inactive, the signal will pass onto  $\underline{h}$  again and up again to the delay element. Thus, so long as  $\underline{f}=0$ , activating the START KEY at time  $\mathcal{T}$  will activate  $\underline{h}$  at times  $\mathcal{T}$ ,  $\mathcal{T}+1$ ,  $\mathcal{T}+2$ , ...

The two delay circuits work together to produce the following result. So long as  $\underline{f}=0$ , if the START KEY is activated at either time  $\mathcal{T}=2\underline{k}-1$  or  $2\underline{k}$ ,  $\underline{h}$  will be activated at times  $2\underline{k}$ ,  $2\underline{k}+1$ ,  $2\underline{k}+2$ , .... The other input wire  $\underline{g}$  is activated by the right-hand delay circuit at times  $2\underline{k}$ ,  $2\underline{k}+2$ ,  $2\underline{k}+4$ , .... Hence the output wire controlling  $\underline{C}_{\underline{t}}$  and  $\underline{S}_{\underline{t}}$  is activated at times  $2\underline{k}$ ,  $2\underline{k}+2$ ,  $2\underline{k}+4$ , and so on. Once started, the computer's activity is cyclic, with control wires  $\underline{S}_{\underline{t}}$  and  $\underline{C}_{\underline{t}}$  activated at every even part of the cycle, starting at the moment the START KEY is activated if that is done at an even numbered moment, or at the following moment if the START KEY was activated at an odd numbered moment.

We wish also to be able to stop the machine, both manually and by instruction 1 of Fig. 2. To stop the machine we must activate  $\underline{f}$ , which will prevent any signal from the upper delay element passing onto  $\underline{h}$ , thus

clearing the left-hand delay circuit. As Fig. 9 shows,  $\underline{f}$  can be activated either by activating the STOP KEY or by activating  $\underline{d}_3$  but not  $\underline{d}_0$ ,  $\underline{d}_1$ , or  $\underline{d}_2$ . Hence the operand 000l signals the machine to stop. This circuit is part of the OPERAND DECODER, which is discussed in the following subsection.

## 6.3. OPERAND DECODER.

We have shown in Sections 4 and 5 how the STORAGE and the ARITHMETIC UNIT function when their various control wires are activated, and we have listed in Fig. 2 the various different instruction words that activate different sets of control wires. It is the operand or first four binary digits of an instruction word which specifies which control wires are to be activated for the instruction to be executed. The OPERAND DECODER which occupies the left-hand part of Fig. 9 is a switching mechanism which activates the proper set of control wires when it receives the four digits of an operand.

The four wires  $\underline{d}_0$ ,  $\underline{d}_1$ ,  $\underline{d}_2$ ,  $\underline{d}_3$  are connected to various threshold elements in the way indicated. That the desired functional connections are realized by the OPERAND DECODER is easily verified. For example, the control wire  $\underline{A}_r$ , which must be activated for the execution of instruction 4, 5, 6, 7, 8, or 9 of Fig. 2, is

activated by any of their operands, as described by the following equation:

$$\underline{\mathbf{A}}_{\mathbf{r}} \equiv (\underline{\overline{\mathbf{d}}}_{0}\underline{\mathbf{d}}_{1}\underline{\overline{\mathbf{d}}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\overline{\mathbf{d}}}_{0}\underline{\mathbf{d}}_{1}\underline{\overline{\mathbf{d}}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\overline{\mathbf{d}}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\overline{\mathbf{d}}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\overline{\mathbf{d}}}_{1}\underline{\overline{\mathbf{d}}}_{2}\underline{\overline{\mathbf{d}}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\overline{\mathbf{d}}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf{d}}_{3} \vee \underline{\mathbf{d}}_{0}\underline{\mathbf{d}}_{1}\underline{\mathbf{d}}_{2}\underline{\mathbf$$

That equation can be simplified to

$$\underline{\mathbf{A}}_{\mathbf{r}} \equiv (\underline{\overline{\mathbf{d}}}_{0}\underline{\mathbf{d}}_{1} \vee \underline{\mathbf{d}}_{0}\underline{\overline{\mathbf{d}}}_{1}\underline{\overline{\mathbf{d}}}_{2}),$$

which is obviously realized by the address decoder as diagrammed in Fig. 9. The functional connections between operands and various sets of control wires could be specified in many different ways: the present arrangement was selected to permit simplifications of the kind indicated.

## 6.4. Operation of the CONTROL.

Four parts of our computer are represented by blocks in Fig. 1, and each has been explained in detail. We have now to explain the rest of the CONTROL, which consists of sixteen conjunction elements and sixteen delay elements, together with the wires connecting them to the other parts of the computer. Each component  $\underline{t}_1$  of the trunk is connected to an input wire of one of these conjunction elements, whose other input wire is connected to control wire  $\underline{C}_t$ . The output wires  $\underline{t}_1^m$  of those conjunction elements lead to separate delay elements, whose output wires lead to  $\underline{d}_0$ ,  $\underline{d}_1$ ,  $\underline{d}_2$ ,  $\underline{d}_3$  and  $\underline{s}_4$ ,  $\underline{s}_5$ , ...,  $\underline{s}_{15}$ .

The functioning of these parts can best be explained by showing how they operate when the machine is executing an instruction under the direction of the CONTROL. the machine is engaged in solving a problem, at any even numbered moment T = 2k control wires  $S_t$  and  $C_t$ automatically activated, making the ADDRESS COUNTER send the address of some storage bin down wires  $\underline{s}_4$ ,  $\underline{s}_5$ , ...,  $\underline{s}_{15}$ to the STORAGE. The STORAGE is thereby caused to transmit the instruction word from that bin onto the trunk. sixteen digits of that instruction word pass through the sixteen conjunction elements above (since  $\underline{C}_{t}(2\underline{k}) = 1$ ) to occupy the sequence of wires t. At the following moment T = 2k + 1 (an odd cycle) the sixteen bits of the instruction word emerge from the sixteen delay elements. The first four bits (its operand) pass along  $\underline{d}_0$ ,  $\underline{d}_1$ ,  $\underline{d}_2$ ,  $\underline{d}_3$  to the OPERAND DECODER, and the last twelve bits (its address) pass along  $\underline{s}_4$ ,  $\underline{s}_5$ , ...,  $\underline{s}_{15}$  either up to the ADDRESS COUNTER, if its operand causes the OPERAND DECODER to activate control wire  $\underline{C}_r$ , or down to the STORAGE if its operand causes the OPERAND DECODER to stimulate either control wire  $\underline{S}_t$ ,  $\underline{S}_{rt}$ , or  $\underline{S}_{rp}$ .

Thus we see that at every even cycle the computer brings a new instruction word from STORAGE onto its trunk, and at each following odd cycle the computer executes the instruction enjoined by that instruction word. We will

now illustrate this process.

Consider the actual sequence of occurrences when the computer begins a routine whose first two instructions TRANSFER 101 and OBEY 6 IF  $\underline{a}_{15}$  IS 1 are in bins 0 and 1, respectively. 8 Now if the ADDRESS COUNTER contains all zeros, and we activate the START KEY at either time T = 2k-1 or T = 2k, the machine will begin its run at T = 2k, when  $S_t = C_t = 1$ , and the ADDRESS COUNTER transmits 00...00, the address of bin 0, along wires  $\underline{s}_{L}$ ,  $\underline{s}_{5}$ , ...,  $\underline{s}_{15}$ , to the STORAGE. Bin 0 transmits its contents 0110000001100101 onto the trunk, up through the conjunction elements onto  $\underline{t}_{i}^{m}$ . Then at  $\mathcal{T} = 2\underline{k} + 1$  those bits emerge from the delay elements, the operand OllO going along  $\underline{d}_0$ ,  $\underline{d}_1$ ,  $\underline{d}_2$ ,  $\underline{d}_3$  to cause the OPERAND DECODER to activate control wires  $\underline{S}_{t}$  and  $\underline{A}_{r}$ . At the same time the address 000001100101 goes down  $\underline{s}_4$ ,  $\underline{s}_5$ , ...,  $\underline{s}_{15}$  to the STORAGE, which transmits the number  $\underline{x}$  from bin 101 onto the trunk, and then into the cells of the ARITHMETIC UNIT, since  $\underline{A}_r$  is activated. At  $T = 2\underline{k} + 2$  we have  $\underline{S}_t = \underline{C}_t = 1$ again, and the ADDRESS COUNTER transmits 00...01, the address of bin 1, along  $\underline{s}_4$ ,  $\underline{s}_5$ , ...,  $\underline{s}_{15}$  to the STORAGE, which transmits its contents 111000000000110 onto the trunk, up through the conjunction elements onto  $\underline{t}^{\dagger}$ . at T = 2k + 3 those bits emerge from the delay elements,

1110 along  $\underline{d}_0$ ,  $\underline{d}_1$ ,  $\underline{d}_2$ ,  $\underline{d}_3$  to the OPERAND DECODER, and 00...0110 onto  $\underline{s}_4$ ,  $\underline{s}_5$ , ...,  $\underline{s}_{15}$ . Now what control wires the OPERAND DECODER activates will depend upon the present contents of the ARITHMETIC UNIT, which contains the number  $\underline{x}_0\underline{x}_1\cdots\underline{x}_{15}$ . If the rightmost digit  $\underline{x}_{15}$  of that number is 1,  $\underline{a}_{15}$  = 1, and control wire  $\underline{c}_r$  is stimulated by the OPERAND DECODER. In this case the address 00...0110 now occupying wires  $\underline{s}_4$ ,  $\underline{s}_5$ , ...,  $\underline{s}_{15}$  enters the ADDRESS COUNTER, which at the following time T = 2k + 4 will transmit it down to the STORAGE to cause the instruction word in bin 6 to pass onto the trunk. But if the right- $\underline{x}_{15}$  is 0,  $\underline{a}_{15}$  = 0, and the OPERAND DECODER most digit activates no control wires. In this case the address in the ADDRESS COUNTER remains 00...010, and at the following time T = 2k + 4 it is transmitted down to the STORAGE to cause the instruction word in bin 2 to pass onto the trunk.

#### Footnotes

1. The writing of this paper was done under the sponsorship of the Burroughs Corporation, Research Center, Paoli, Pennsylvania.

The logical design and analysis is primarily the work of the first author (A.W.B.) and the exposition is largely the work of the second author (I.M.C.). Thanks are due to Dr. R. L. Cartwright for helpful criticisms and suggestions.