ENGN UMR 1009

# ERRATA

| Page       |                                                              |

|------------|--------------------------------------------------------------|

| W <b>i</b> | Figure 3.5(b) caption: " $\pi/T$ " should read " $\tau/T$ ." |

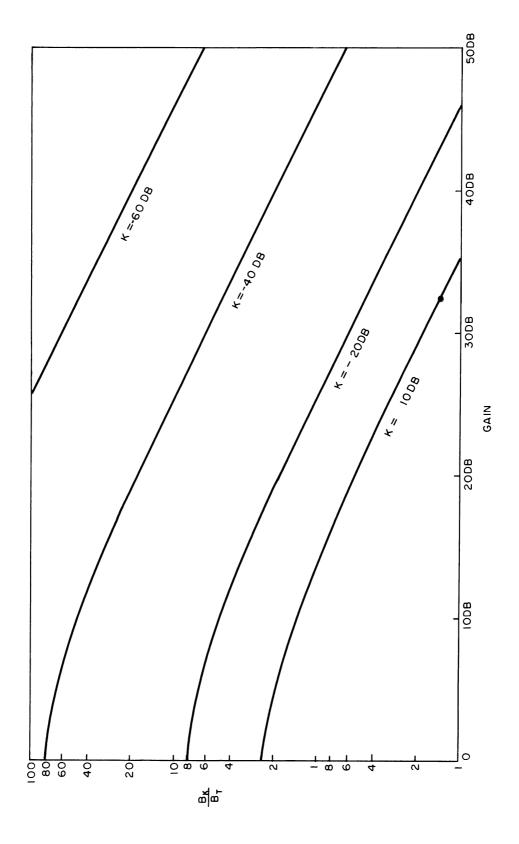

| 74         | Figure 3, 20, bottom curve: "K=10DB" should read             |

|            | '' <b>K=-10DB</b> , ''                                       |

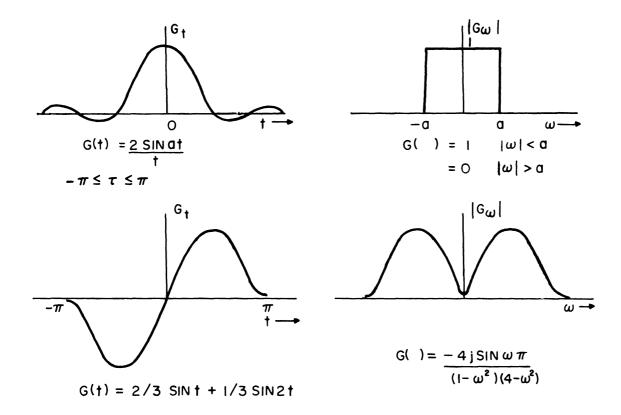

| 83         | Figure 3. 27, drawings on right side: "G( )=" should read    |

|            | "G(ω)=," two places.                                         |

| 84         | line 12: "automatic-phase control" should read               |

|            | "automatic phase-control"                                    |

| 137        | line 6: "If in" should read "If an."                         |

# THE UNIVERSITY OF MICHIGAN OFFICE OF RESEARCH ADMINISTRATION ANN ARBOR

# PRECISE FREQUENCY SYNTHESIS USING NONPRECISE TUNING COMPONENTS

Technical Report No. 120

2899-52-T

Cooley Electronics Laboratory

Department of Electrical Engineering

By: T. W. Butler, Jr.

Approved by:

B. F. Barton

Project 2899

TASK ORDER NO. EDG-4

CONTRACT NO. DA-36-039 sc-78283

SIGNAL CORPS, DEPARTMENT OF THE ARMY

DEPARTMENT OF ARMY PROJECT NO. 3A99-06-001-01

Submitted in partial fulfillment of the requirements for the Degree of Doctor of Philosophy in The University of Michigan

June 1961

UMP1009

#### ACKNOWLEDGMENTS

The author wishes to express sincere appreciation to all members of his committee for their encouragement and helpful criticism in the preparation of this work. The technical guidance of the Chairman, Professor J. A. Boyd and members Professor H. W. Farris and Dr. L. W. Orr was particularly helpful.

The author wishes also to thank Mr. Robert E. Graham and Mrs. Alice Brockus for their intensive efforts in preparing the material for publication.

### TABLE OF CONTENTS

|             |                                                     | Page                  |

|-------------|-----------------------------------------------------|-----------------------|

| ACKNOWLED   | GMENTS                                              | ii                    |

| LIST OF F   | IGURES                                              | v                     |

| ABSTRACT    |                                                     | х                     |

| ר שאסתקים ד | . INTRODUCTION                                      | 1                     |

|             | Statement of the Problem                            | 1                     |

|             | Survey of Other Methods of Precision Frequency      | _                     |

|             | Synthesis                                           | 3<br>4                |

|             | 1.2.1 Tunable LC Oscillator                         |                       |

|             | 1.2.2 Crystal Oscillator                            | 4                     |

|             | 1.2.3 Multiple Crystal Frequency Synthesizer        | 4                     |

| 3 0         | 1.2.4 Single Crystal Frequency Synthesizer          | 5                     |

| 1.3         | Stabilized Master Oscillator Frequency Synthesizer  | 6                     |

|             | 1.3.1 Servo System 1.3.2 Sampled Data System        | 0                     |

| а. Ь        | The Status of Current WorkSummary                   | 4<br>5<br>6<br>7<br>9 |

|             | The boatus of ourient workbummary                   | 7                     |

| CHAPTER I   | I. HISTORICAL BACKGROUND ON THE STUDY OF ELECTRONIC |                       |

|             | TUNING METHODS USING SOLID-STATE DEVICES            | 11                    |

| 2.1         | Electronic Tuning                                   | 11                    |

|             | Magnetic Tuning                                     | <b>1</b> 2            |

| 2.3         | Electric Tuning                                     | 20                    |

|             | 2.3.1 Ferroelectric Capacitors                      | 20                    |

|             | 2.3.2 Voltage Variable Diode Capacitor              | 32                    |

| 2.4         | Conclusion                                          | 38                    |

| CHVDWDD I.  | II. ANALYSIS OF THE GENERALIZED DISCRETE FREQUENCY  |                       |

| CHAPTER I.  | SYNTHESIZER                                         | 40                    |

| 3.1         | System Concept                                      | 40                    |

|             | Discrete-Frequency Reference                        | 46                    |

| ٠           | 3.2.1 Definition of Peak Factor                     | 46                    |

|             | 3.2.2 Methods of Generating a Discrete-Frequency    | ,0                    |

|             | Reference                                           | 54                    |

|             | 3.2.3 Summary                                       | 83                    |

| 3.3         | Phase-Lock Oscillator                               | 84                    |

|             | 3.3.1 Theory of Operation                           | 85                    |

|             | 3.3.2 Design Procedure                              | 109                   |

| 3.4         | Analysis of Frequency Choices for the Frequency     | -                     |

|             | Synthesizer                                         | 119                   |

| CHAPTER T   | V. SYNTHESIZER DESIGN CONSIDERATIONS                | 125                   |

| 4.1         | Design Philosophy                                   | 125                   |

| _           | 4.1.1 Discrete-Frequency Reference                  | 127                   |

|             | 4.1.2 Phase-Lock Oscillator                         | 127                   |

|             | 4.1.2.1 Voltage-Controlled Oscillator               | 128                   |

|             | 4.1.4 Control Network                               | 132                   |

|             | 4.1.5 Messurements                                  | 1 3 J                 |

### TABLE OF CONTENTS (Cont.)

|                                                                                                                | Page                     |

|----------------------------------------------------------------------------------------------------------------|--------------------------|

| 4.1.5.1 Discrete-Frequency Reference Measurements 4.1.5.2 Phase-Lock Oscillator Measurements                   | 135<br>136               |

| CHAPTER V SUMMARY AND CONCLUSIONS 5.1 Introduction 5.2 Summary of Results 5.3 Suggestions for Further Research | 152<br>152<br>152<br>155 |

| APPENDIX A COMPARISON OF ELECTRONIC TUNING DEVICES                                                             | 158                      |

| APPENDIX B LIMITATIONS ON SRG USED FOR DECADE SPECTRAL DIVISION                                                | 159                      |

| LIST OF REFERENCES                                                                                             | 161                      |

| DISTRIBUTION LIST                                                                                              | 163                      |

## LIST OF FIGURES

| Figure |                                                                                                         | Page |

|--------|---------------------------------------------------------------------------------------------------------|------|

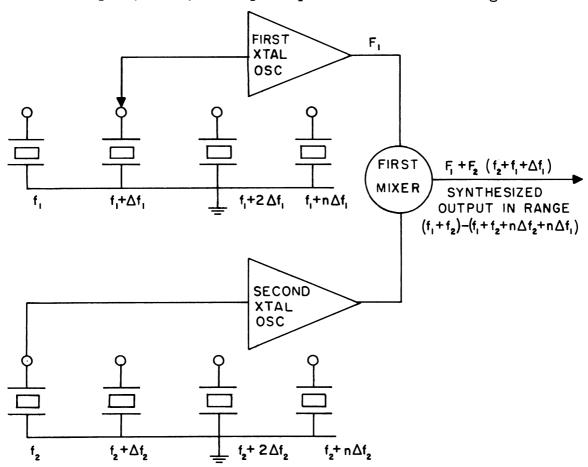

| 1.1    | Block diagram of a multiple crystal frequency synthesizer                                               | 4    |

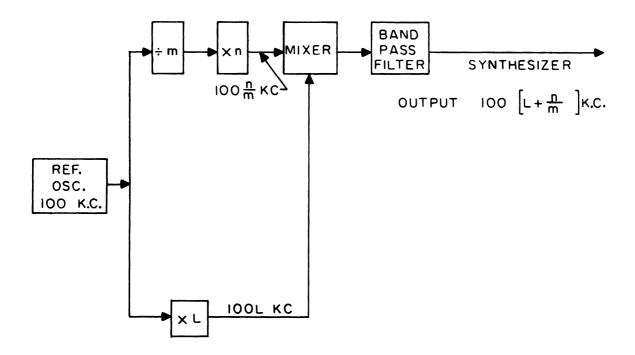

| 1.2    | Block diagram of a single crystal frequency synthesizer                                                 | 5    |

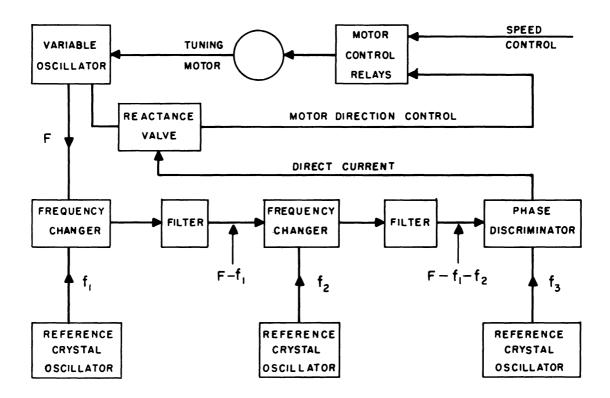

| 1.3    | Block diagram of a stabilized master oscillator frequency synthesizer (Servo System)                    | 6    |

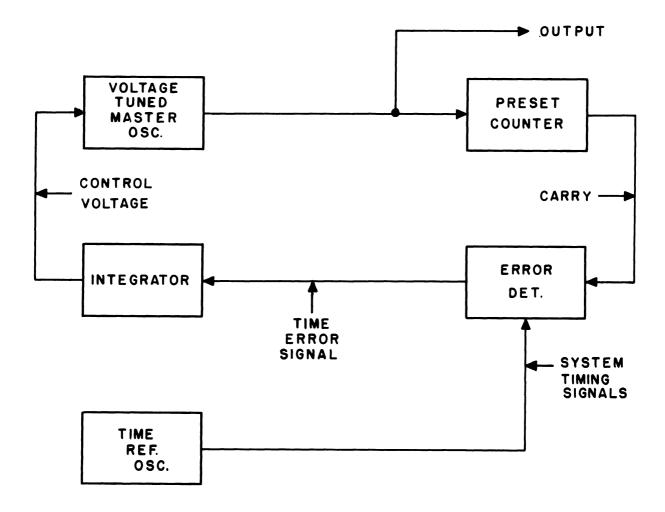

| 1.4    | Block diagram of a stabilized master oscillator frequency synthesizer (Sampled Data System)             | 8    |

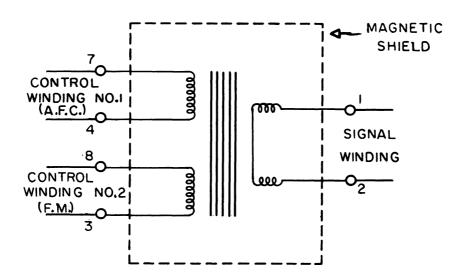

| 2.1    | Schematic diagram of a typical controllable inductor                                                    | 13   |

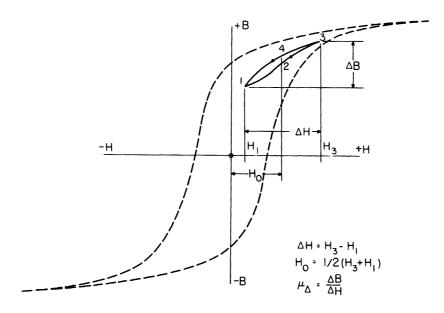

| 2.2    | Definitions of magnetic parameters                                                                      | 14   |

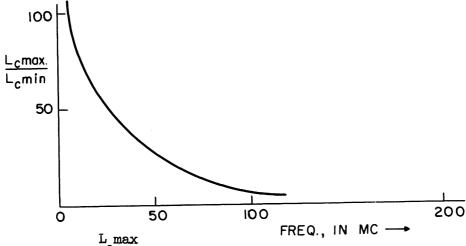

| 2.3    | $\frac{L_{c~max}}{L_{c~min}}$ of typical magnetic tuning unit vs. frequency                             | 16   |

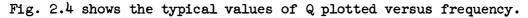

| 2.4    | Q of typical magnetic tuning units vs. frequency                                                        | 17   |

| 2.5    | Basic circuit for application of a controllable inductance $\mathbf{L}_{\mathbf{c}}$ in a tuned circuit | 17   |

| 2.6    | Ferroelectric capacitor hysteresis loop                                                                 | 22   |

| 2.7    | The static capacity-field butterfly loop for a typical ferroelectric ceramic                            | 26   |

| 2.8    | Ratio of capacitance, $\frac{C}{40}$ , vs. temperature in degrees centigrade $\frac{1}{40}$             | 27   |

| 2.9    | $\frac{C_{c \text{ max}}}{C_{c \text{ min}}}$ of typical ferroelectric capacitor vs. frequency          | 28   |

| 2.10   | Q of a typical ferroelectric capacitor versus frequency                                                 | 29   |

| 2.11   | Basic circuit for application of a ferroelectric capacitor in a tuned circuit                           | 30   |

| 2.12   | Voltage sensitivity of capacitance                                                                      | 33   |

| 2.13   | Q of a typical voltage variable diode capacitor vs. frequency                                           | 35   |

| 2.14   | Basic circuit for application of a voltage variable capacitance diode in a tuned circuit                | 36   |

| Figure |                                                                                                                                                    | Page |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.15   | Alternate method of increasing circuit Q                                                                                                           | 37   |

| 3.1    | Discrete frequency reference (DFR)                                                                                                                 | 40   |

| 3.2    | Phase-lock oscillator (PLO)                                                                                                                        | 41   |

| 3.3    | Discrete frequency generator (DFG)                                                                                                                 | 42   |

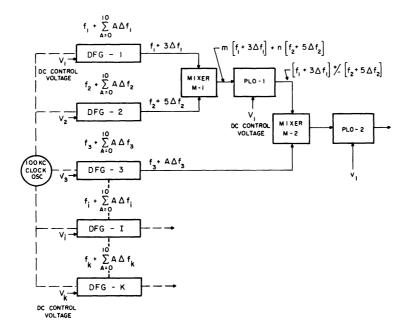

| 3.4    | Generalized discrete frequency synthesizer                                                                                                         | 43   |

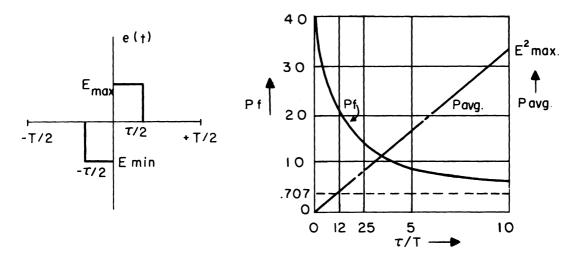

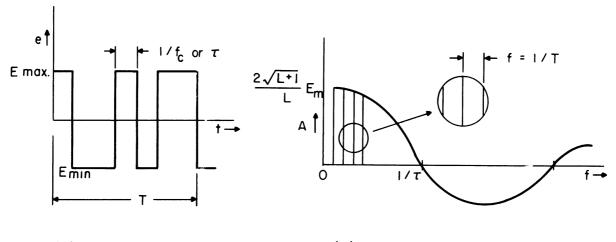

| 3.5    | (a) Rectangular function $e(t)$<br>(b) Peak factor (pf) and average power ( $P_{avg}$ ) of $e(t)$ versus the ratio $\pi/T$                         | 49   |

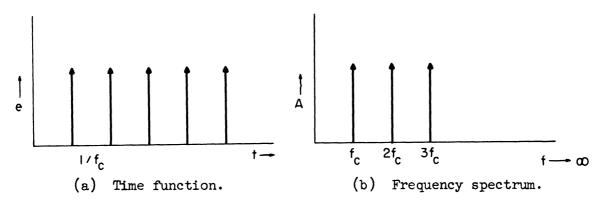

| 3.6    | Repetitive impulse ( $f_c = clock frequency$ )                                                                                                     | 54   |

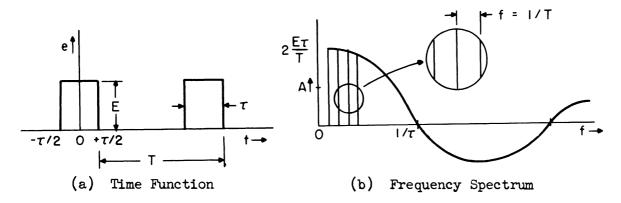

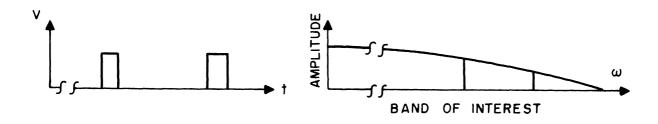

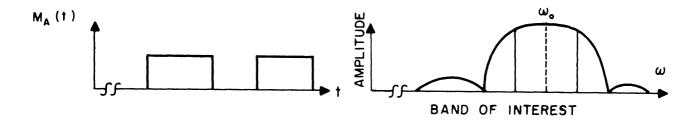

| 3.7    | Repetitive finite pulse                                                                                                                            | 55   |

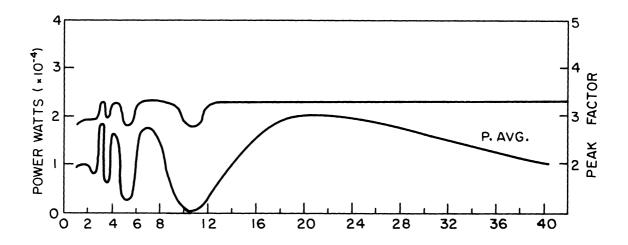

| 3.8    | Peak factor (pf) and average power ( $P_{avg}$ ) in the band of interest vs. the location of the lst zero (Z) in Mc for N = 11 spectral components | 58   |

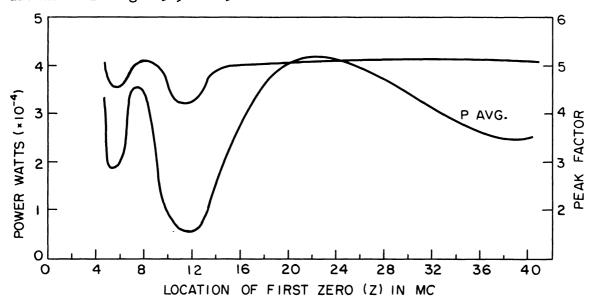

| 3.9    | Peak factor (pf) and average power $(P_{avg})$ in the band of interest vs. the location of the lst zero (Z) in Mc for N = 26 spectral components   | 59   |

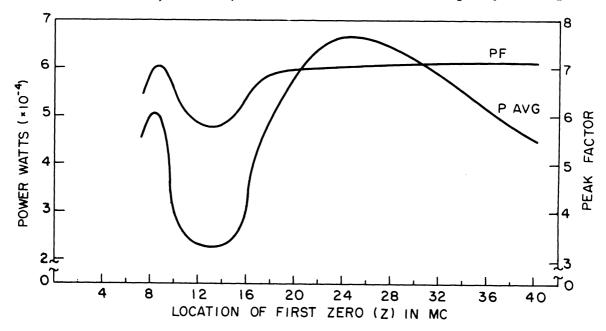

| 3.10   | Peak factor (pf) and average power ( $P_{avg}$ ) in the band of interest vs. the location of the 1st zero (Z) in Mc for N = 51 spectral components | 60   |

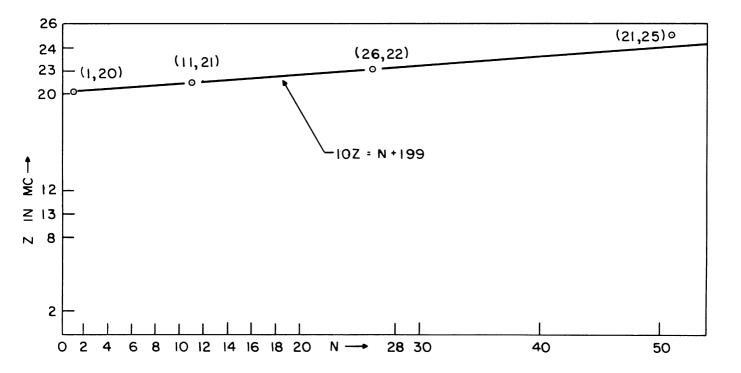

| 3.11   | Location of 1st zero (Z) in Mc vs. the number of spectral components (N) for maximum power in the band of interest                                 | 61   |

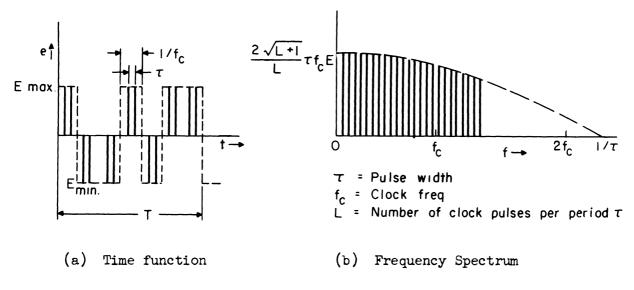

| 3.12   | Digitally-generated linear maximal sequence                                                                                                        | 62   |

| 3.13   | Digitally-generated linear maximal sequence where $\tau < 1/f_{_{\rm C}}$                                                                          | 63   |

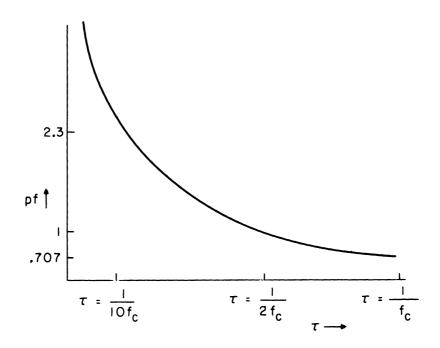

| 3.14   | Peak factor vs. pulse width $(\tau)$ for fixed clock frequency $(f_c)$                                                                             | 64   |

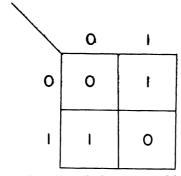

| 3.15   | Modulo-two addition table                                                                                                                          | 65   |

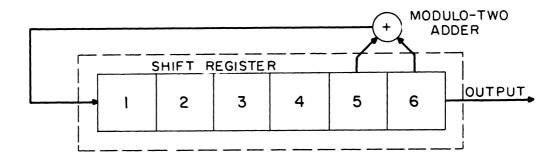

| 3.16   | A simple shift-register generator                                                                                                                  | 66   |

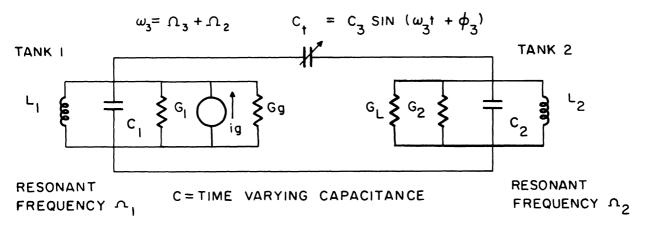

| 3.17   | An equivalent lumped circuit for the two-tank variable-parameter system                                                                            | 69   |

| Figure |                                                                                                           | Page |

|--------|-----------------------------------------------------------------------------------------------------------|------|

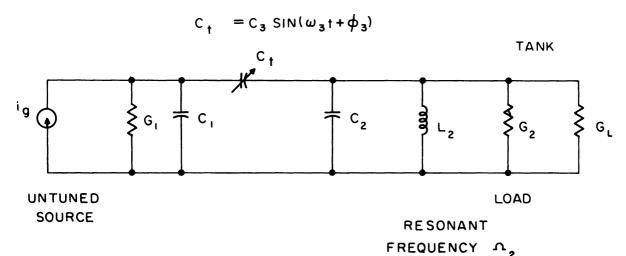

| 3.18   | Theoretical model of a single-resonance parametric amplifier                                              | 71   |

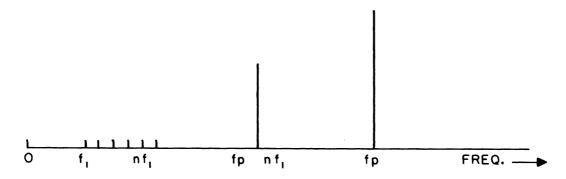

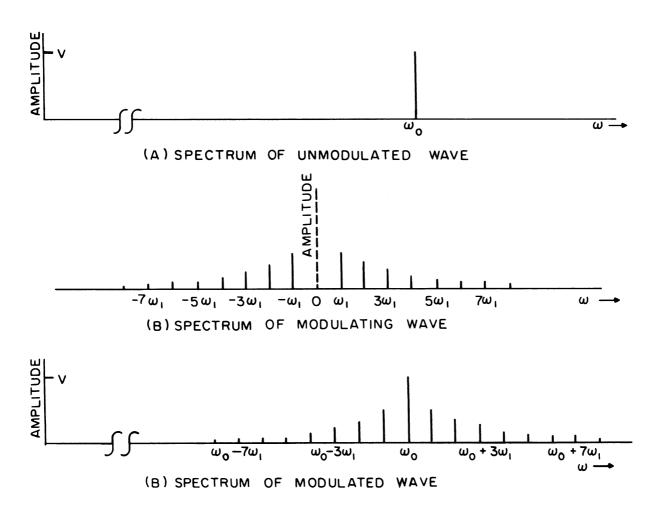

| 3.19   | Frequency spectrum of a single-resonance lower-side-<br>band up-converter                                 | 71   |

| 3.20   | Plot of $B_{K}/B_{\mathrm{T}}$ vs. amplifier gain for a given K                                           | 74   |

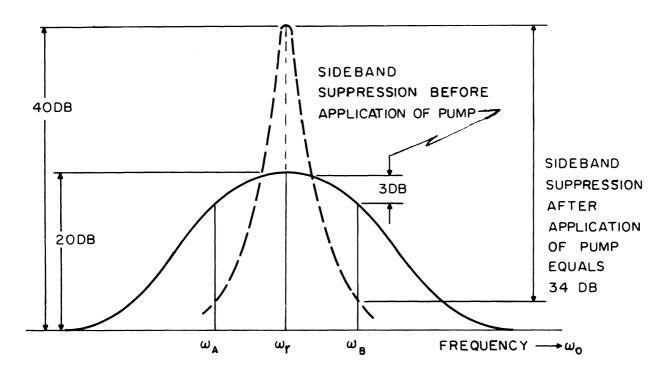

| 3.21   | Sideband suppression in output tank before (solid curve) and after (dotted curve) application of pump     | 75   |

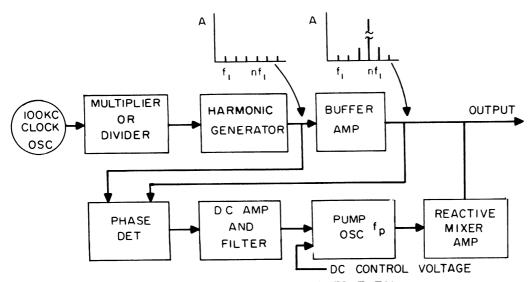

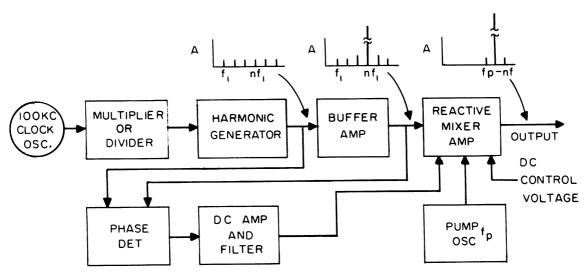

| 3.22   | Block diagram of error-correcting circuit for a single-resonance lower-sideband up-converter              | 77   |

| 3.23   | Spectrum of an AM wave                                                                                    | 79   |

| 3.24   | Comparison of the repetitive finite pulse and the amplitude-modulation technique                          | 80   |

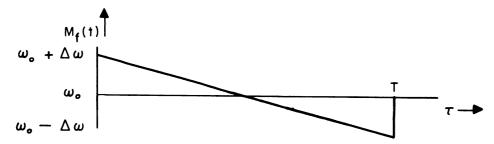

| 3.25   | Linear FM waveform                                                                                        | 81   |

| 3.26   | Frequency spectrum of the linear FM waveform                                                              | 82   |

| 3.27   | Examples of useful spectra and their associated time waveforms                                            | 83   |

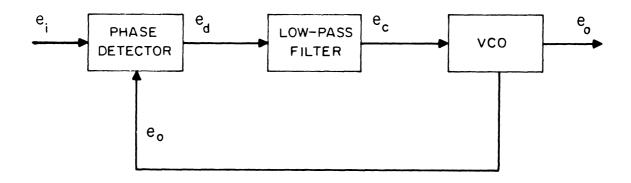

| 3.28   | Block diagram of phase-lock loop                                                                          | 86   |

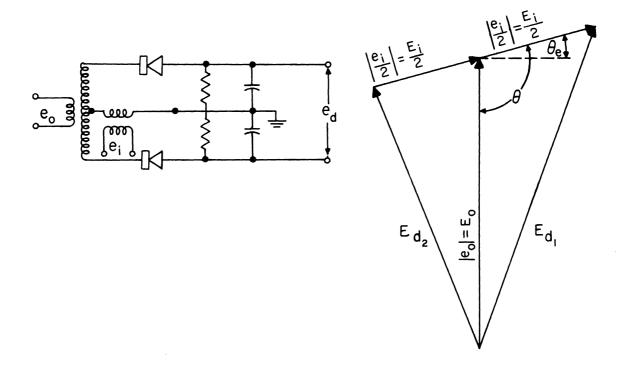

| 3.29   | Circuit and vector diagrams of phase-detector circuit                                                     | 88   |

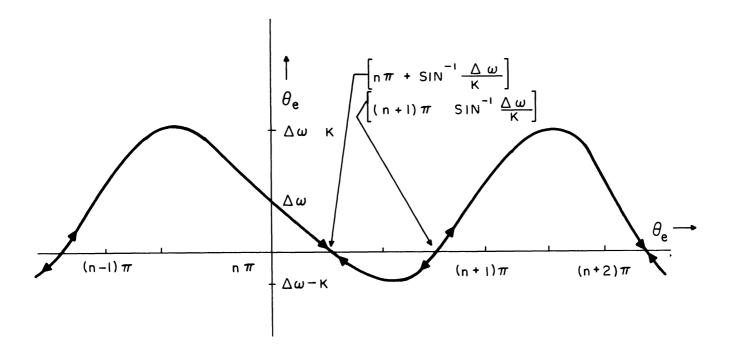

| 3.30   | First-order loop pull-in behavior (n even integer)                                                        | 91   |

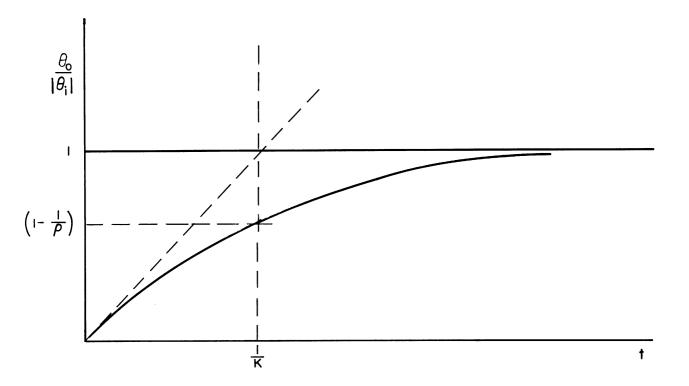

| 3.31   | Transient response plot of $\frac{\theta_{O}}{ \theta_{i} }$ (t) = 1-e <sup>-Kt</sup>                     | 93   |

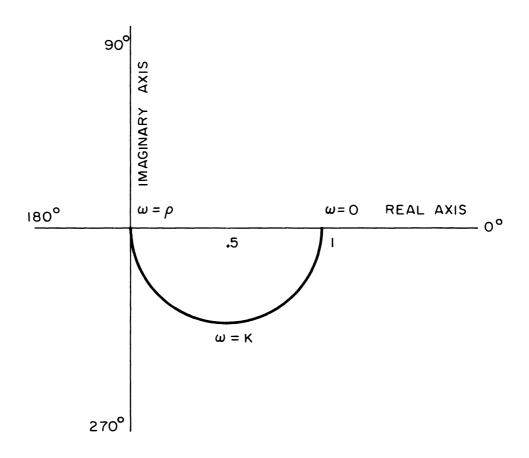

| 3.32   | Frequency response plot of $\frac{\theta_0}{\theta_1}$ (j $\omega$ ) = $\frac{1}{1 + j \frac{\omega}{K}}$ | 94   |

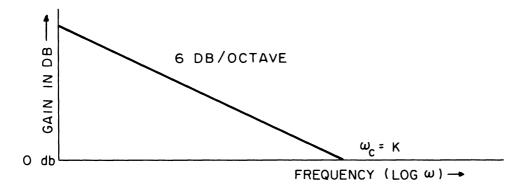

| 3.33   | Open-loop gain of system                                                                                  | 99   |

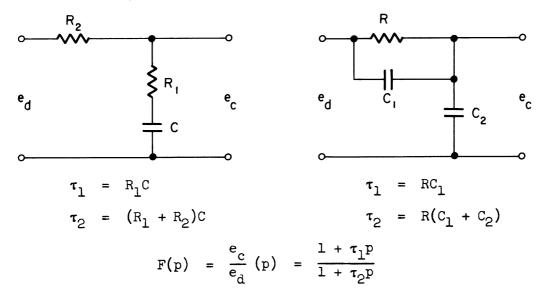

| 3.34   | Proportional plus integral control networks                                                               | 101  |

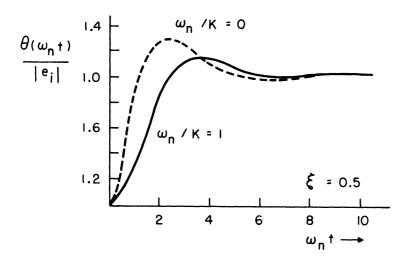

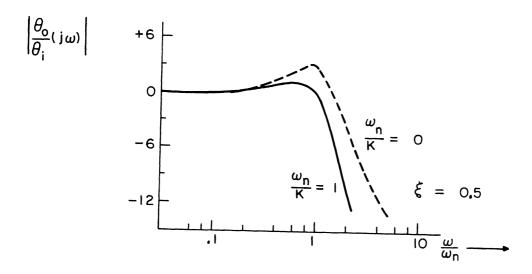

| 3•35   | Transient response of system                                                                              | 103  |

| 3.36   | Frequency response of system                                                                              | 105  |

| Figure |                                                                                          | Page |

|--------|------------------------------------------------------------------------------------------|------|

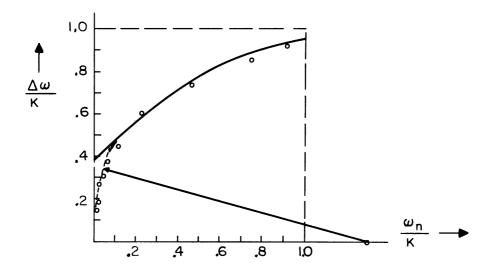

| 3.37   | Capture range of system                                                                  | 108  |

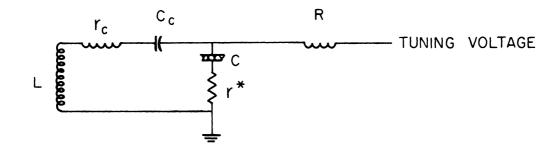

| 3.38   | Equivalent circuit of a typical oscillator tank circuit                                  | 112  |

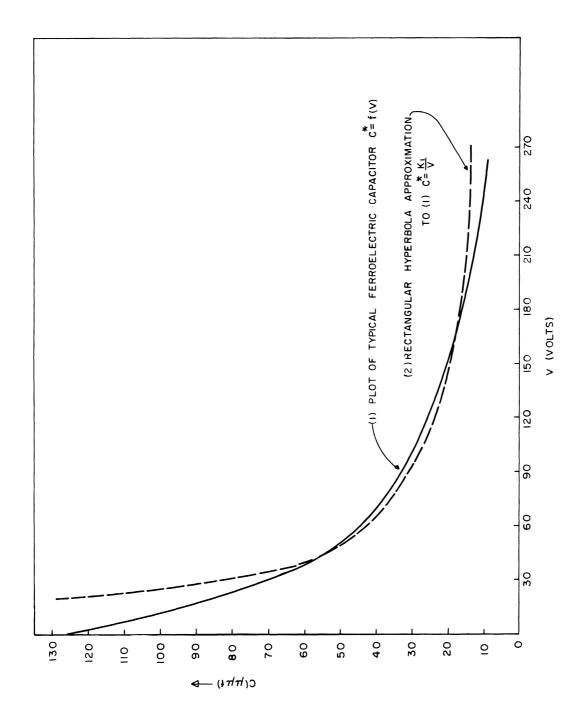

| 3.39   | Capacitance of ferroelectric capacitor vs. tuning voltage                                | 113  |

| 3.40   | Elementary frequency combining network                                                   | 120  |

| 3.41   | Frequency spectrum for case $N = 1$ , $G = 20 \text{ kc}$                                | 122  |

| 4.1    | Two-digit synthesizer                                                                    | 126  |

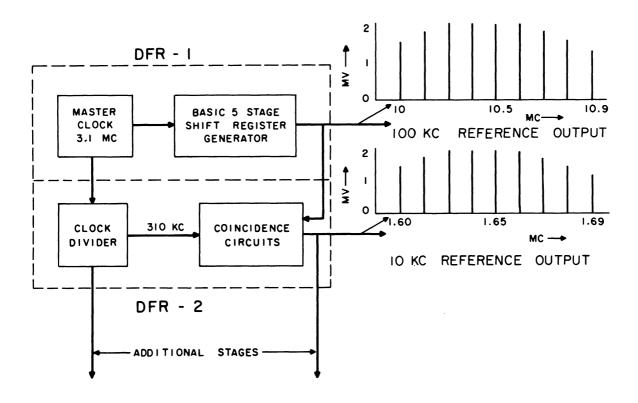

| 4.2    | Discrete-frequency reference                                                             | 127  |

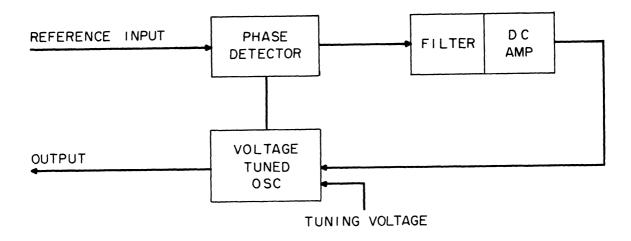

| 4.3    | Phase-lock oscillator                                                                    | 128  |

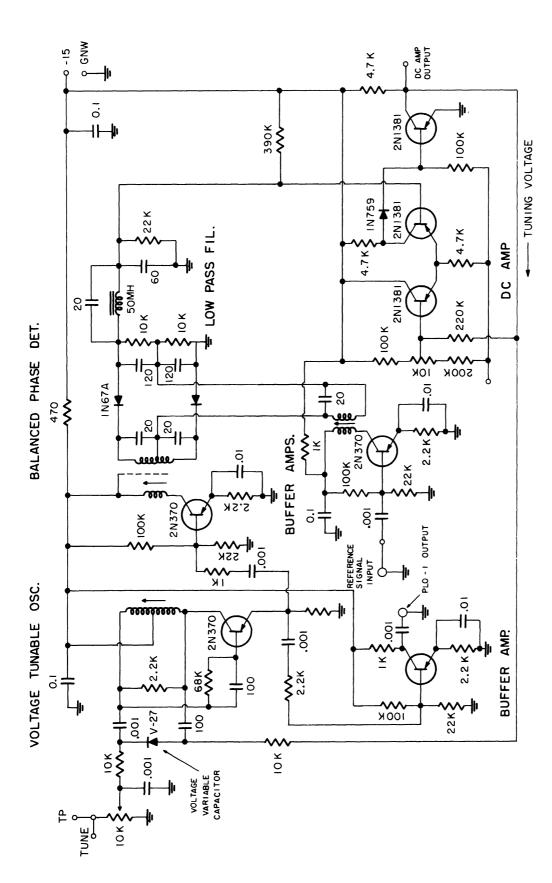

| 4.4    | Schematic diagram of PLO-1                                                               | 129  |

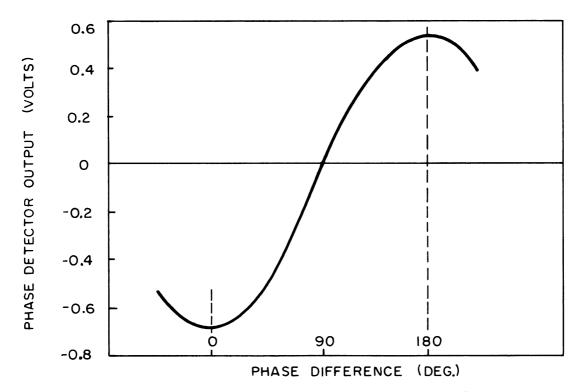

| 4.5    | Characteristic curve of the phase detector                                               | 130  |

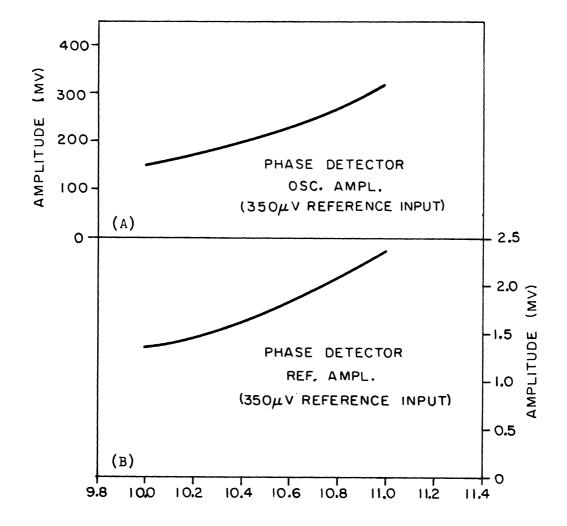

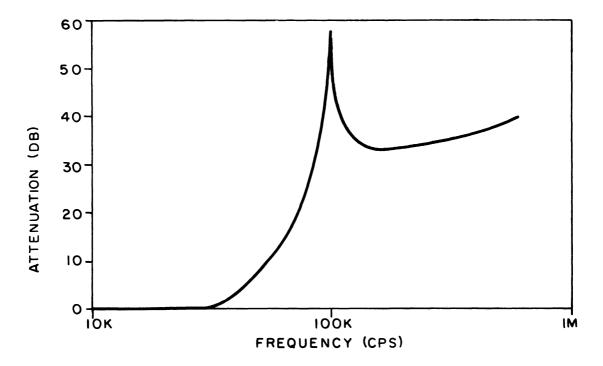

| 4.6    | Oscillator and reference amplitude at the phase detector coil as a function of frequency | 131  |

| 4.7    | Phase-detector frequency response                                                        | 132  |

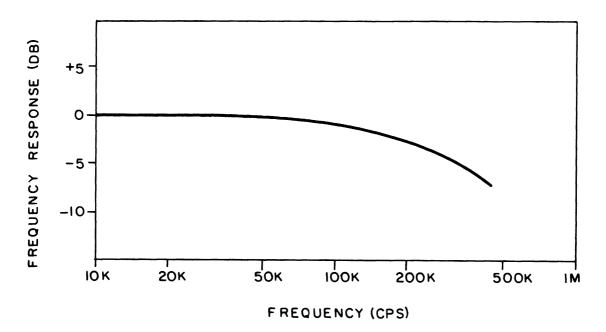

| 4.8    | Dc amplifier gain-frequency characteristic                                               | 133  |

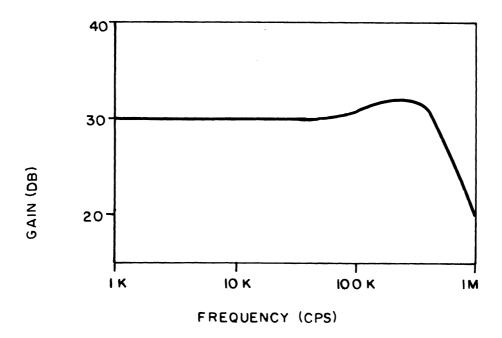

| 4.9    | Low-pass filter attenuation vs. frequency characteristics                                | 134  |

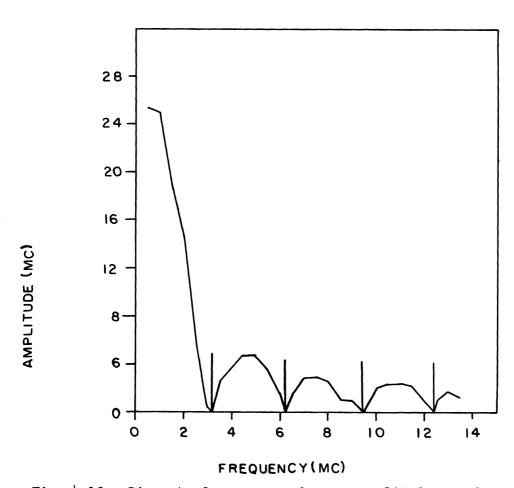

| 4.10   | Discrete-frequency reference amplitude vs. frequency                                     | 135  |

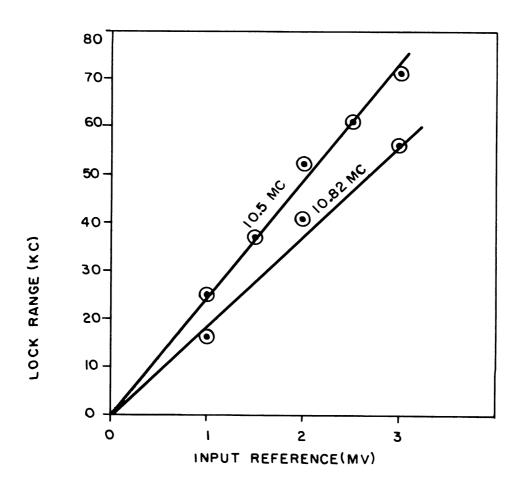

| 4.11   | Lock range vs. reference input of PLO-1                                                  | 136  |

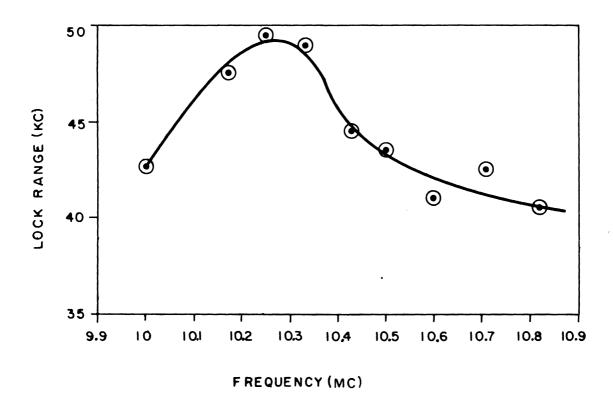

| 4.12   | Lock range vs. frequency of PLO-1 with a reference input of 2 mv                         | 137  |

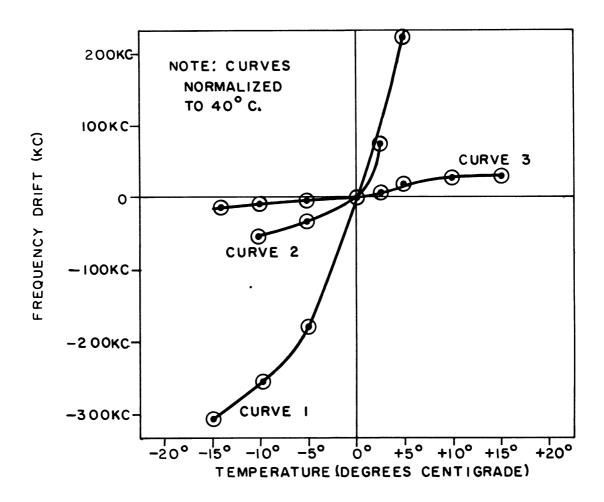

| 4.13   | Frequency stability vs. temperature for PLO-1                                            | 138  |

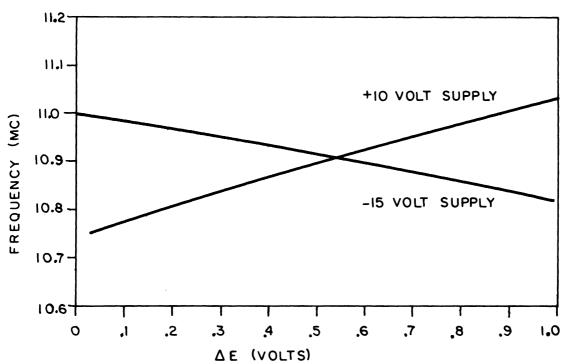

| 4.14   | Frequency in Mc vs. supply voltage changes ( $\Delta E$ ) in volts of PLO-1              | 139  |

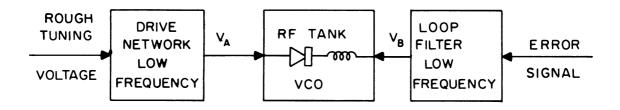

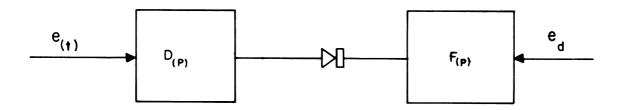

| 4.15   | Block diagram of VCO tuning circuit                                                      | 140  |

| 4.16   | Simplified diagram of VCO tuning circuit                                                 | 140  |

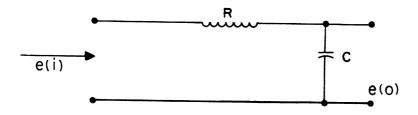

| 4.17   | Circuit of simplified drive network                                                      | 141  |

| Figure |                                                                                  | Page |

|--------|----------------------------------------------------------------------------------|------|

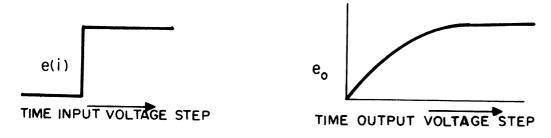

| 4.18   | Step response of simplified drive shown in Fig. 4.17                             | 141  |

| 4.19   | Circuit diagram of a more complex drive network                                  | 142  |

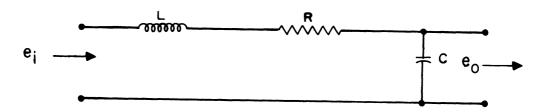

| 4.20   | Expected drive and control circuit operation under switching conditions          | 144  |

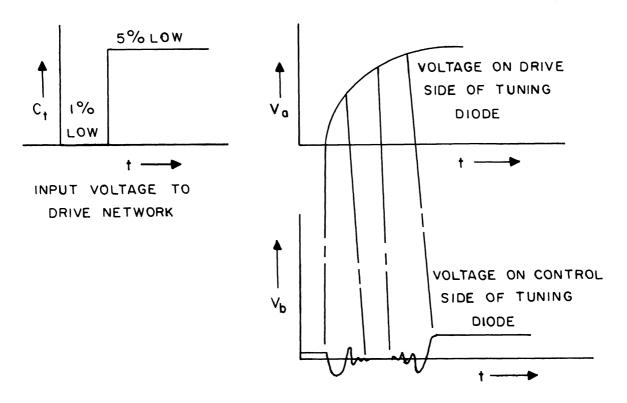

| 4.21   | Expected frequency variation under switching conditions                          | 145  |

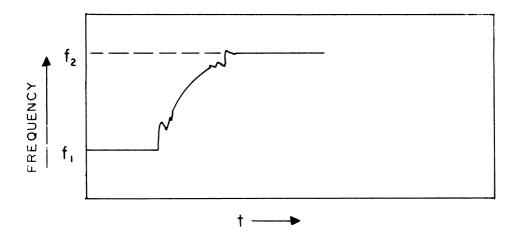

| 4.22   | Actual drive and control circuit operation under switching conditions            | 145  |

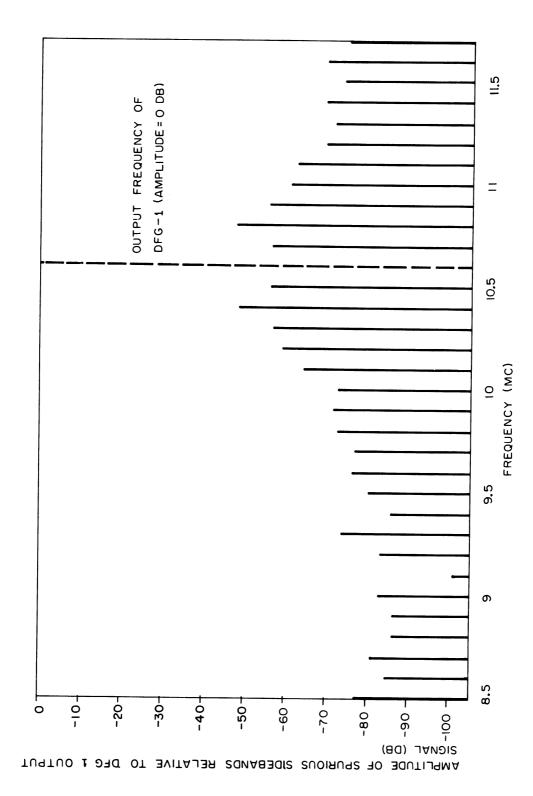

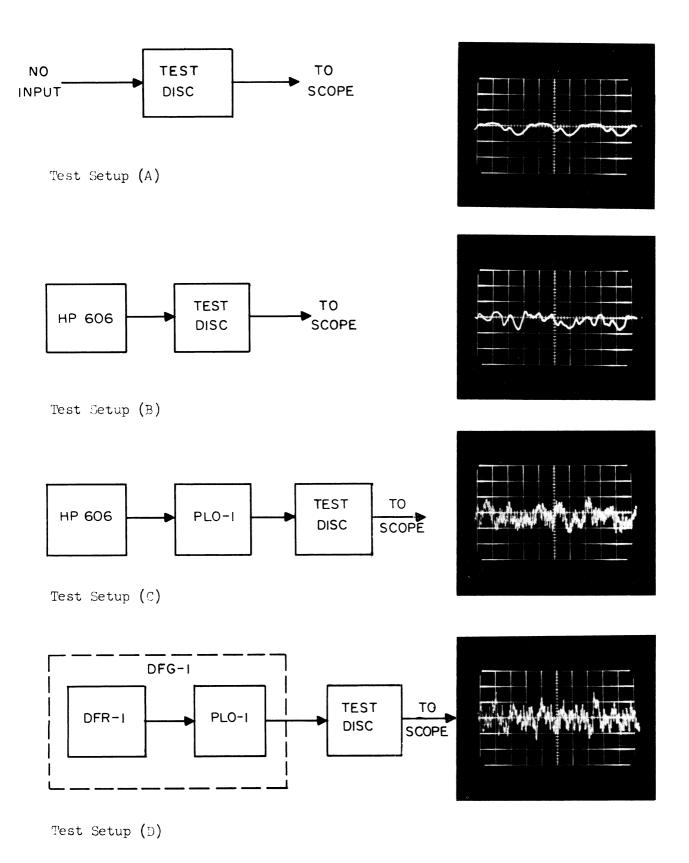

| 4.23   | Amplitude of spurious sidebands relative to DFG-1 output signal versus frequency | 148  |

| 4.24   | A relative measure of the noise output of the system                             | 149  |

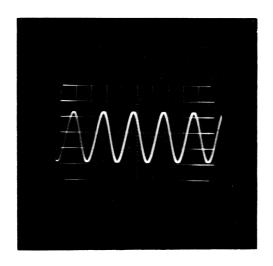

| 4.25   | 10 Mc output signal of DFG-1                                                     | 150  |

#### ABSTRACT

This dissertation treats the effective utilization of non-precise tuning components in unique techniques for precise frequency synthesis. Frequency synthesis is the generation of sinusoidal RF signals of precisely-controlled and accurately-known arbitrary frequencies.

Nonprecise components which are examined in detail under the several limiting conditions of operation are solid-state devices, such as variable capacitance diodes, ferroelectric capacitors, and controllable inductors.

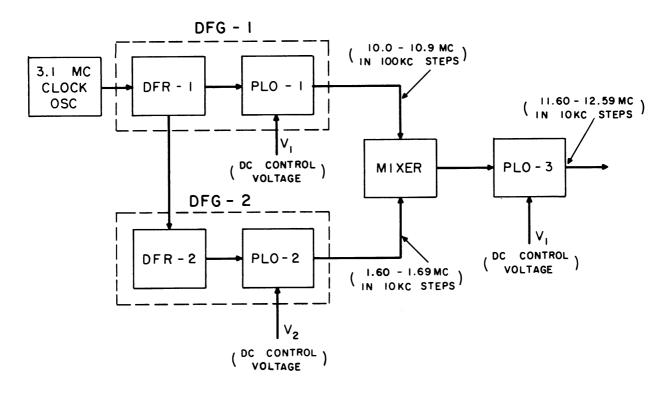

The significance of combining a discrete-frequency reference and an electronically-tuned phase-lock oscillator in the generation of precise frequencies is that it is possible to construct a unit whose output frequency can have certain discrete values.

This unit, called a discrete-frequency generator, has an output frequency which is precisely one of the harmonics of the discrete-frequency reference. By using several discrete-frequency generators, each with different incremental steps, combining, and taking the mixed output, it is possible to cover a wide over-all range in small incremental steps.

The design and construction of a discrete-frequency synthesizer which tunes over a 1-Mc range in 10-kc steps (two significant figures) is carried out to demonstrate the practicability of the proposed technique. The discrete-frequency reference is provided by a five-stage shift-register generator. The shift-register generator is synchronized by a crystal clock which has a long-term frequency stability of one part in 10<sup>5</sup>. The spurious output of the synthesizer is at least 55 db below the desired output.

The significant consequences of this investigation result from the extreme flexibility afforded by completely electronic tuning methods. The incorporation of the nonprecise components through the use of phase-lock circuitry has made it possible to develop a technique of frequency synthesis which permits the rapid selection of precise frequencies, is adaptable to remote control, may be readily programmed, and theoretically is unlimited in frequency range of operation.

#### CHAPTER I

#### INTRODUCTION

#### 1.1 Statement of the Problem

Frequency synthesis is the generation of sinusoidal RF signals of precisely-controlled and accurately-known arbitrary frequencies. This study treats the effective utilization of nonprecise tuning components in unique techniques for precise frequency synthesis.

Nonprecise components which are examined in detail under the several limiting conditions of operation are solid-state devices such as variable capacitance diodes, ferroelectric capacitors, and controllable inductors.

The significant consequences of this investigation result from the extreme flexibility afforded by completely electronic tuning methods. The incorporation of the nonprecise components through the use of phase-lock circuitry has made it possible to develop a technique of frequency synthesis which permits the rapid selection of precise frequencies, is adaptable to both remote control and electronic programming using analog or digital methods, and theoretically is unlimited in frequency range of operation.

This paper is divided into five chapters. The statement of the problem and a discussion of current techniques for providing precisely-controlled frequencies are presented in Chapter I.

A study of various electronic tuning methods using solid-state devices is carried out in Chapter II. This study formulates basic decisions regarding the limitations of tuning elements and voltage-controlled oscillator circuit parameters.

The system concept of a generalized discrete frequency synthesizer is presented in Chapter III. The significant contribution of combining a discrete frequency reference and an electronically-tuned phase-lock oscillator in the generation of precise frequencies is that it is possible to construct a unit whose output frequency can have certain discrete values. This unit, called a discrete-frequency generator, has an output frequency which is precisely one of the harmonics of the discrete-frequency reference. By using several discrete-frequency generators, each with different incremental steps, combining and taking the mixed output, it is possible to cover a wide over-all range in small incremental steps. The question of how to minimize for a given power spectrum the peak-to-peak amplitude of a signal is presented. A term peak factor is defined and a relationship which can be effectively used as a figure of merit in the design of an appropriate frequency spectrum is developed. In addition, a study and evaluation of various methods for the efficient production of high-order harmonics with balanced energy in the frequency band of interest is carried out.

Of the various methods presented for generating a discretefrequency reference, the shift register generator method is particularly

interesting. The digitally-generated linear maximal sequence fulfills

the condition of minimum peak factor while providing a reasonably uniform amplitude spectrum over a given band of interest. From a practical point of view, the shift register generator is simple to implement.

Logic modules can be taken off the shelf and put together to form a

discrete frequency reference. In addition, by using clock dividers

and coincidence gates in conjunction with the shift register generator,

it is possible to obtain any number of discrete frequency references

each with different incremental steps.

Also in Chapter III an analysis of the problem of combining two signal frequencies to obtain a single signal frequency in the form of their sum or difference while using phase-lock oscillators of a practical design is carried out.

Many authors have attempted to describe the various performance characteristics of the phase-lock oscillator loop but no one of these has treated the aspect in a manner sufficiently complete for the present purposes. Therefore, the basic operating principles of a phase-lock loop are presented and analyses are made in instances where the literature is not complete. For example, an analysis is carried out to determine frequency sensitivity, loading effects, and other characteristics of voltage variable capacitors when used as the tuning element in an oscillator tank circuit. Based on this analysis a figure of merit is developed which is defined as the product of the frequency sensitivity S and the Q of the oscillator tank circuit. In addition, equations for the convergence time of a phase-lock oscillator loop are developed.

In Chapter IV the design, construction, and testing of a two-digit synthesizer are carried out to demonstrate the practicability of the system.

Chapter V is devoted to a summary and conclusions. Suggestions for further research are presented and specific applications in which the proposed technique for precise frequency synthesis would be particularly useful are given.

#### 1.2 Survey of Other Methods of Precision Frequency Synthesis

The development of frequency control circuits will be traced briefly and the technical forces causing their evolution will be discussed.

1.2.1 Tunable LC Oscillator. The simple tunable LC oscillator was a practical way of generating channel frequencies when crowding of the spectrum was not a problem and frequency inaccuracies could be tolerated.

1.2.2 Crystal Oscillator. Crowding of the spectrum necessitated closer channel spacing and increased frequency accuracy. The increased frequency accuracy was provided by the crystal oscillator.

1.2.3 Multiple Crystal Frequency Synthesizer. As it became apparent in multi-channel equipment design that a choice of one of hundreds of channels was required, the multiple crystal synthesizer was developed (Ref. 1). The principle is illustrated in Fig. 1.1. The

Fig. 1.1. Block diagram of a multiple crystal frequency synthesizer.

frequencies of several crystal oscillators were mixed to produce the desired output frequencies. Each oscillator was provided a means of selecting one of ten or more crystals so that a large number of channel frequencies could be synthesized.

1.2.4 Single Crystal Frequency Synthesizer. To accommodate additional channels the channel spacing was reduced. This, however, necessitated maintaining channel frequencies within a tolerance as small as  $\frac{1}{2}$  part per million. A system proposed by H. J. Finden (Ref. 2) retains the advantages of the multiple crystal synthesizer but eliminates the problem of maintaining a large number of crystals to the same accuracy. The accuracy and stability of the output signal are esentially equal to that of the reference oscillator. The principle is illustrated in Fig. 1.2.

Fig. 1.2. Block diagram of a single crystal frequency synthesizer.

Basically, the single crystal frequency synthesizer is a circuit in which harmonics and subharmonics of a single standard reference oscillator are combined to form a multiplicity of output signals which are all harmonically related to a subharmonic of the standard reference oscillator.

# 1.3 Stabilized Master Oscillator Frequency Synthesizer

1.3.1 Servo System. A system proposed by E. W. Pappenfus (Ref. 3) and G. J. Camfield (Ref. 4) uses an indirect technique in which the output frequencies are obtained from a variable oscillator, which in turn is controlled by reference crystal oscillators. The principle is illustrated in Fig. 1.3. The control is both mechanical

Fig. 1.3. Block diagram of a stabilized master oscillator frequency synthesizer.

(Servo System)

by means of a tuning motor and electronic by means of a reactance tube. The frequency  $F_1$  of the variable oscillator is varied until the output from the second filter reaches the frequency  $f_3$ , at which time the phase discriminator operates and the tuning motor automatically stops. When the motor stops,  $F = f_1 + f_2 + f_3$ . F may be changed by altering any of the reference crystals. If the system used twenty crystals in two groups of ten each to control the first two reference oscillators (so that f, and f, could each have any one of ten values), then F could have any one of a hundred values. Admittedly, if ten harmonics of a single crystal-oscillator had been used for each group a hundred frequencies for only two crystals could be obtained. It was felt, however, that high-order harmonic selection involves the use of precision circuits which must be maintained accurately on tune and which may offer the possibility of being tuned to an incorrect harmonic. In addition, a unit comprising one crystal plus harmonicselection circuits tends, if anything, to be larger and to require more power than a unit using a number of crystals. For the system to operate satisfactorily, the open loop set-on accuracy of the master oscillator must be within ±5 kc. This is accomplished by constructing a very stable mechanically-tuned oscillator with a reactance tube in the tank circuit for lock-on purposes when the oscillator is brought within the ±5 kc limitation. The stability of the system described above depends upon the stability of the frequencies used at the translating mixers.

1.3.2 Sampled Data System. A system proposed by N. G.

Alexakis (Ref. 5) uses an entirely different principle, i.e., a preset frequency counter, to tune and stabilize a master oscillator. The

basic elements as shown in the block diagram of Fig. 1.4 are a voltage-

Fig. 1.4. Block diagram of a stabilized master oscillator frequency synthesizer. (Sampled Data System)

controlled oscillator, preset counter, timing signal and error detector.

The fixed reference time interval is compared with the variable interval required by the counter. If the variable time is less than the one-second fixed interval, then the master oscillator frequency is too high. If the variable time is greater than the reference interval, the master oscillator frequency is too low. The error signal thus developed is a constant-amplitude pulse of varying duration and either

positive or negative polarity. The voltage-controlled master oscillator requires a proper dc voltage to reduce the error to zero. This voltage is derived from the time-varying error signal by an integrating circuit.

#### 1.4 The Status of Current Work--Summary

As indicated in previous sections, several direct approaches to frequency synthesizers have been made. Using multiple decks of crystals and mixing the outputs of several crystal oscillators is one method.

A second method uses only one crystal oscillator of high precision which is fed to multiplier-divider chains and harmonic generators. The desired harmonic in each decade bank is selected by mechanically-tuned high Q filters, and the outputs of the various filters are suitably mixed to furnish the desired output frequency.

A further refinement in this area is the use of a variable frequency master oscillator to obtain the desired frequency. The master oscillator is in turn controlled by reference to crystal oscillators. The control in this case is both mechanical and electronic.

The final system described which uses a voltage-controlled oscillator and a preset counter to obtain the desired frequency output has much to recommend it since it is a straightforward and quite simple technique.

The significant consequences of the proposed technique result from the extreme flexibility afforded by completely electronic tuning methods. The incorporation of the nonprecise components through the use of phase-lock circuitry has made it possible to develop a technique of frequency synthesis which permits the rapid selection of

precise frequencies and is adaptable to both remote control and electronic programming, using analog or digital methods. Theoretically, this technique is unlimited in frequency range of operation.

#### CHAPTER II

# HISTORICAL BACKGROUND ON THE STUDY OF ELECTRONIC TUNING METHODS USING SOLID-STATE DEVICES

#### 2.1 Electronic Tuning

Electronic frequency control is flexible, versatile, and in many instances essential where fast frequency selection and low tuning power are required. During the past few years, two methods of electronic tuning using solid-state elements have evolved:

- (1) Magnetic tuning which uses the principle that

the inductance in a resonance circuit may be

varied by means of a magnetic bias field, and

- (2) Electric tuning which uses the principle that the capacitance of the resonant circuit may be varied by an electric bias field.

The ideal tuning element for frequency synthesis applications, whether it uses the principle of magnetic or electric tuning, should have the following characteristics:

- (1) RF loss is negligibly small.

- (2) Tuning capabilities should extend to at least 1000 megacycles with little change in Q.

- (3) The temperature coefficient of frequency should be zero from minus 50 degrees centigrade to plus 100 degrees centigrade.

- (4) Frequency ratios should be at least 10 to 1 with relatively small control power. In

- addition, the operating frequency should extend to 1000 megacycles with this ratio.

- (5) Frequency selection should be rapid, using step or continuous control.

- (6) Tuning elements should be small, compact and capable of large scale manufacture with only a small fraction of rejects.

- (7) Isolation of controlled and controlling signals should be possible.

Since this ideal does not exist and it is unlikely that it will be developed within the next few years, the present choice for a particular tuning method and tuning element must be a compromise to obtain a close approach to the ideal in those properties most important for a specific application.

#### 2.2 Magnetic Tuning

During the past fifty years, attempts have been made to construct controllable inductors without moving parts and cover as much of the frequency spectrum as possible at a reasonable expense of control power. A controllable inductor is a device comprising a number of windings. Some of these windings carry alternating current; others, carrying direct or slowly varying current, are used to determine the magnetic state of the core and thus to control the alternating current in the winding first mentioned. The usefulness of these earlier results was limited to very low radio frequencies. Although the laminated core technique used at that time was considerably improved by the use of nickel-iron alloys and etching processes to reduce the lamination thickness, difficult production methods and low Q's prevented any

made to develop an RF tuning element using powdered iron materials.

Those efforts did not produce units which could be called practical.

A representative example was developed by W. J. Polydorff (Ref. 6)

in 1944. The unit described produced a change of inductance of approximately 4 to 1 and had a Q of 50 in the frequency range of 200 to 400 kilocycles with a control power requirement of 25 watts. The weight of the unit was in excess of 25 pounds.

Since 1945, a new class of magnetic core materials called ferrites has been developed (Ref. 7). These materials, which have a wide variation of permeability with applied field, have enjoyed prominence in the magnetic tuning field because of their high resistivity and freedom from eddy-current losses at high frequency. Fig. 2.1 shows a schematic representation of a controllable inductor having one signal winding and two control windings. The signal winding is drawn in two sections, shown orthogonal to the control winding, to indicate that inductive coupling between the control and signal windings

Fig. 2.1. Schematic diagram of a typical controllable inductor.

has been cancelled. A magnetic shield surrounds the ensemble to prevent stray fields from influencing its behavior.

Ferrites used as magnetic core materials consist of oxides of metals and are formed at high temperatures. All materials that exhibit ferromagnetism are paramagnetic when heated above the Curie temperature. Permeability  $(\mu)$  of a magnetic material is defined as the ratio of B/H where B is the flux density in lines per square centimeter (gauss) and H the magnetizing force in gilberts per centimeter (oersteds). The permeability of the magnetic material is low at low flux density, maximum at some moderate flux density, and quite small when the core is saturated. The permeability at low magnetizing force (the limit as B and H approach zero) is called the initial permeability  $(\mu_0)$ .

In addition to the previous terms there is another term called incremental permeability ( $\mu_{\triangle}$ ) which is a function of  $\Delta H$  and  $H_{\odot}$ . The magnetic quantities involved are shown in Fig. 2.2. The dotted

Fig. 2.2. Definitions of magnetic parameters.

Curie temperature--point below which the material ceases to be paramagnetic.

curve represents a B/H or hysteresis loop for some magnetic material. The solid curve shows the change in magnetic flux density B under the influence of a small cyclical variation in magnetic field. Although B is a double-valued function of H, it is possible to define incremental permeability as  $\mu_{\triangle}$  =  $\Delta B/\Delta H$  as the material is cycled around the path 1-2-3-4-1. Ho is the mean value or dc component of the magnetic field. Incremental permeability is also defined as the permeability offered to an ac magnetizing force superimposed on a dc magnetizing force. In describing a ferrite material we must know its history, H, AH and the frequency of operation. The initial permeability  $\mu_{0}$  for very small or zero flux densities is an inherent property of the material under consideration. For various ferrite materials in which we are interested the  $\mu_{0}$  lies between 2 and 1500. The incremental permeability (  $\mu_{\triangle})$  of a ferrite material decreases monotonically with increasing  $\mathbf{H}_{\mathbf{O}}$  for a constant  $\Delta H$ . The maximum theoretical change in permeability is  $\mu_0/\mu_0$ where  $\mu_{\mbox{\scriptsize c}}$  is the permeability at saturation. Since  $\mu_{\mbox{\scriptsize c}}$  approaches unity, the maximum change in inductance is proportional to  $\boldsymbol{\mu}_{\text{O}}$  . The maximum change in frequency we can expect due to the permeability change is

$$\sqrt{\frac{\mathbf{f}_{\max}}{\mathbf{f}_{\min}}} = \mu_{o}$$

From a practical point of view the hysteresis effect simply means that if the control current is raised from zero to a given value, one signal inductance is obtained. If the same control current value is approached from a high current setting, a different value of signal inductance will occur.

Magnetic tuning units are now being produced with very good stability. By a suitable choice of core material there is generally a value of control current for which the temperature coefficient over a broad temperature range is substantially zero, with coefficients of opposite sign on either side of this current setting. Signal winding coefficients of 0.5%/°C are encountered, although more typical values are 0.1% to 0.2%.

At frequencies up to 10 megacycles, inductance change ratios in the hundreds are feasible. Typical units designed for applications between 10 and 50 megacycles have ratios in the order of 30 to 100. In the 50 to 100 megacycles range, this drops to between 3 and 6; and above 100 megacycles to less than 2. The curve of Fig. 2.3 shows the

Fig. 2.3.  $\frac{L_{c}}{L_{min}}$  of typical magnetic tuning unit vs. frequency.

ratio of maximum to minimum inductance plotted versus frequency.

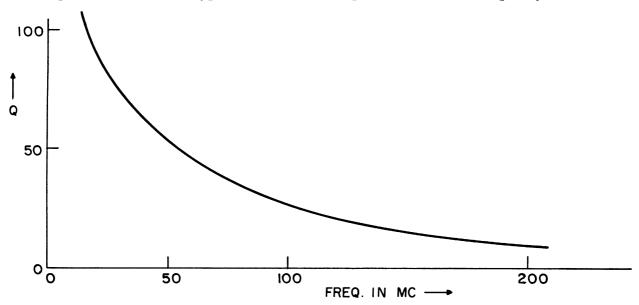

Representative Q values are in the low hundreds for frequencies up to several megacycles. They range between 40 and 100 for frequencies up to 50 megacycles, dropping to between 10 and 50 at 100 megacycles and perhaps 5 to 10 at 200 megacycles. The curve of

Fig. 2.4. Q of typical magnetic tuning units vs. frequency.

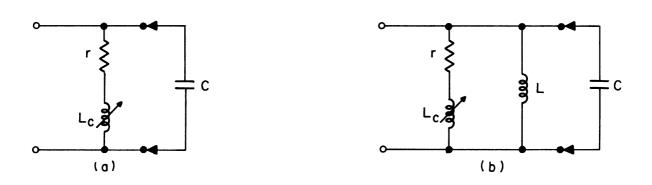

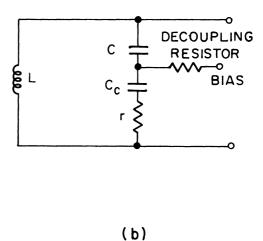

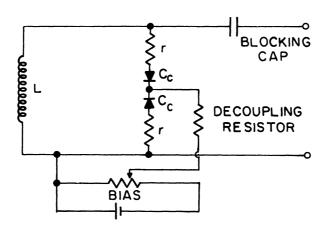

Figure 2.5a illustrates the basic circuit for application of

$L_{c}$  = controllable inductance

r = loss associated with controllable inductance

L = loss free inductance

C = total capacitance in tank circuit

Fig. 2.5. Basic circuit for application of a controllable inductance  $L_{\rm c}$  in a tuned circuit.

a controllable inductance in a typical tank circuit. It may frequently be true that the tuning ratio (TR) may be greater than necessary but the circuit Q may be unacceptable due to inherent losses in the controllable inductance. Fig. 2.5b depicts a method of increasing the tuned circuit Q by including a small loss-free coil in shunt with the controllable inductance.

$$Q_{\text{coil}} = \frac{\omega L_{\text{c}}}{r} \tag{2.1}$$

$$TR_{coil} = \frac{L_{c}^{max}}{L_{c}^{min}}$$

(2.2)

The Q of the controllable inductance with the loss-free coil in shunt is

$$Q_{circuit} = Q_{coil} \left[ \frac{L_c + L}{L} \right]$$

(2.3)

while the tuning ratio becomes

$$TR_{circuit} = TR_{coil} \left[ \frac{L_{c}^{min} + L}{L_{c}^{max} + L} \right]^{\frac{1}{2}}$$

(2.4)

If L >> L then the frequency range will be determined by the available inductance range of the controllable inductance. However, if L  $_{\rm c}$  >> L then a definite gain in Q may be achieved only through a loss in effective inductance variation range.

The control power required to obtain the full inductance variation of low level units is approximately 1 watt. Some commercially available inductors, however, have been made to operate at a level of about 0.1 watt. The control power is interrelated with the required

$\frac{L_{max}}{c}$  ratio and frequency and will vary somewhat. The relationship

between control current and signal inductance is nonlinear, the percentage change in inductance per unit control current being greatest for small control current values. Since this is undesirable, appropriate compensation circuitry has been developed.

Since step frequency control of the proposed synthesizer is envisioned, the problem of furnishing the electronic means for magnetic tuning may become quite difficult. The following typical example serves to illustrate the seriousness of the problem. In the frequency range 1 to 3 Mc, it is desired to step from 1 to 2 Mc in 1 microsecond. The circuit has the following properties:

Control inductance = 3 henries

Required control current shift = 10 ma

Control voltage  $e = L \frac{di}{dt} = 3 \times .01 \times 10^6 = 30,000 \text{ volts}$ Peak control power p = 300 watts

A voltage of 30,000 volts presents not only a serious problem in control circuit design, especially in transistor circuits, but also in voltage insulation in the design of the control winding itself.

The voltage across the control winding may be reduced at the expense of a larger control current. Since the magnetic field is proportional to the number of ampere turns (NI) and since the inductance of the control winding is proportional to  $N^2$ , then by reducing N by a factor 10 the control circuit has the following properties:

Control inductance = .03 henries

Required control current shift = 100 ma

Control voltage =  $L \frac{di}{dt}$  = .03 x .1 x 10<sup>6</sup> = 3,000 volts Peak control power = 300 watts

An improvement is achieved in the voltage across the control winding but at the expense of increased control current. In both cases the power calculation of 300 watts is an instantaneous or peak demand lasting only 1 microsecond.

In conclusion, the study and development of ferrite material has resulted in a controllable inductance having a volume less than one cubic inch, weighing slightly over one ounce, and being capable of tuning a frequency range of 7 to 1 at 1 Mc to 1.5 to 1 at over 200 Mc. Q's of the order of 100 - 10 are obtained over this frequency range and the average temperature coefficient of the elements is below .03%/°C.

#### 2.3 Electric Tuning

Increasing interest in the use of voltage-variable capacitors for electronic frequency control has resulted in the development of two different classes of capacitors:

- (a) The ferroelectric capacitor and

- (b) The voltage variable diode capacitor.

A clarification of the distinction between the ferroelectric capacitor and the voltage variable diode capacitor appears desirable and will be carried out in the following brief discussion.

2.3.1 Ferroelectric Capacitors. In the past decade there has been a considerable development of a new group of nonlinear dielectric materials called "ferroelectrics." These materials, although the name stems from the Latin word for iron, do not contain appreciable amounts of iron. Rather, the name indicates the close resemblance the mechanism of electrical polarization to that of the magnetization

of ferromagnetic materials discussed under Section 1.1.

Ferroelectricity can be described as a spontaneous polarization. Polarization in dielectric materials may be due to:

- (1) Alignment of permanent electric dipoles,

- (2) Displacement of the + and ions relative to one another (e.g., Na<sup>+</sup> and Cl<sup>-</sup> in NaCl) or

- (3) Displacement, relative to the positive nucleus of the negative charge of the electrons.

Ferroelectricity will occur if any one of these mechanisms, either singly or in combination occurs spontaneously, i.e., without the application of an external electric field. A number of materials exhibit ferroelectricity, but on the whole the phenomenon is rather rare. Ferroelectric materials are always piezoelectric but the converse is not always true, e.g., quartz. Barium titanate (BaTiO<sub>3</sub>) is, from a practical point of view, the most important ferroelectric and, when mixed with a nonferroelectric buffer material, such as strontium titanate, becomes a suitable material for many practical applications.

In a conventional capacitor a graph of Q vs. V is essentially linear, i.e., a straight line with slope (C) proportional to the dielectric constant ( $\epsilon$ ).

The relationship of these quantities is expressed as

$$Q = CV (2.5)$$

where Q is the charge stored, C is the capacitance and V is the applied voltage.

In a ferroelectric capacitor the plot of charge versus voltage is not a straight line; i.e., it is nonlinear. If a complete

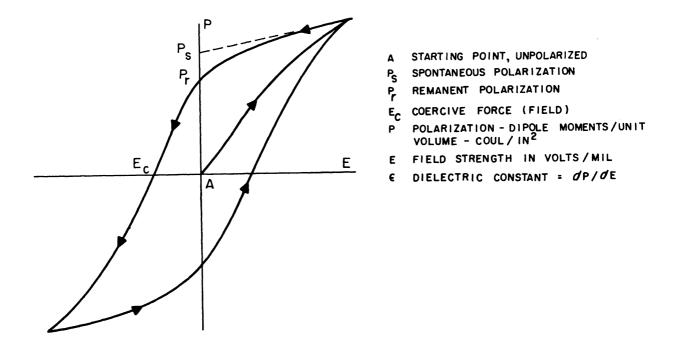

cycle of positive and negative voltages is applied, the result is a hysteresis loop as shown in Fig. 2.6. Although the hysteresis loop

Fig. 2.6. Ferroelectric capacitor hysteresis loop.

is not included in the definition on nonlinearity, it is exhibited by all nonlinear dielectrics and thus may be considered an inherent property.

The hysteresis loop can be explained by considering the behavior of the barium titanate crystal (Ref. 8).

At room temperature this crystal has a tetragonal form which is similar to a distorted cube in which one axis, the "c" axis, is elongated by a spontaneously occurring electric dipole along that direction, while the other two axes, both "a" axes, since they are identical in every respect, are shortened. The dielectric constant along the "a" axes is at least several times greater than that along the "c" axis.

Along the "c" axis the polarization may have two directions, oppositely oriented, which may be called positive and negative. When the voltage along the "c" axis is varied in sign, the dipole flips from one stable position to the other. Since a finite field is necessary to reorient the dipole, there is little change in polarization until a critical field level is reached. A rapid change in crystal polarization occurs when this level is reached, and subsequent increases in field strength produce little further change in polarization. When the field is reversed, this process is repeated, with opposite polarity conditions prevailing.

In the ceramic of which practical capacitors are formed, the barium titanate forms into a multitude of tiny crystallites whose spontaneous dipoles are randomly oriented. Therefore, there is no favored "c" direction, and the statistical average of the elemental orientations cancels to zero. With no biasing electric field applied to the dielectric the observed dielectric constant lies between that characteristic of the "c" direction and that of the "a" directions. It is somewhat closer to the "a" value since "a" axes are more abundant.

Referring to Fig. 2.6 and beginning at point A, there is initially no net polarization before voltage is applied. When a dc bias is applied to the material, some of the dipoles originally oriented randomly will align themselves with the field, and a partial "c" axis is induced perpendicular to the electrode faces. As a consequence, the dielectric constant decreases. As the biasing voltage (applied field) is increased, more and more dipoles are reoriented, and the dielectric constant continues to decrease as the polarization in the new "c" direction increases. This proceeds until a further increase

in bias fails to yield a proportionate increase in polarization. This presumably occurs as a result of the supply of randomly oriented dipoles becoming exhausted.

In the polycrystalline ceramic many of the elemental dipoles are incapable of being oriented perpendicularly to the electrode faces due to their position in the ceramic matrix. At best they can be elastically strained in the direction of the field.

When the field is reduced, these strains relax and some polarization is lost. However, since a large number of dipoles are oriented into a stable condition, they remain so and the charge stored in this manner is not recovered. This makes up the remanent polarization,  $P_r$ . When the field is reversed, a certain field strength,  $E_c$ , is required to reduce the polarization to zero and further increase in field switches the dipoles to the reverse direction. When the field is again reversed, the plot of polarization versus field duplicates the upper path. It is seen, therefore, that the point A is not traversed again and that the process is not reversible.

The behavior of a given capacitor can be shown graphically since its capacitance is proportional to the dielectric constant,  $\epsilon$ , which is the slope of the hysteresis loop.

The shape of the loop is affected by the peak field strength applied, temperature and frequency as well as the material of which the dielectric is composed. In general, the sides of the loop become more vertical and the saturation region flattens out with higher peak fields. The dipole switching occurs at a very fast rate. It has been known to follow pulses of the order of 1 microsecond and smaller. The zero bias dielectric constant does fall off somewhat above the region

of about 700 Mc/s, and it is to be expected that the hysteresis loop will change at the higher frequencies.

Another effect described by W. J. Merz (Ref. 9) which may be observed in certain ferroelectric ceramic materials is the double hysteresis loop phenomena. In this case the double hysteresis loop occurs over a rather large temperature range and is caused by a transition from a nonferroelectric state via a shift in the Curie temperature with applied field.

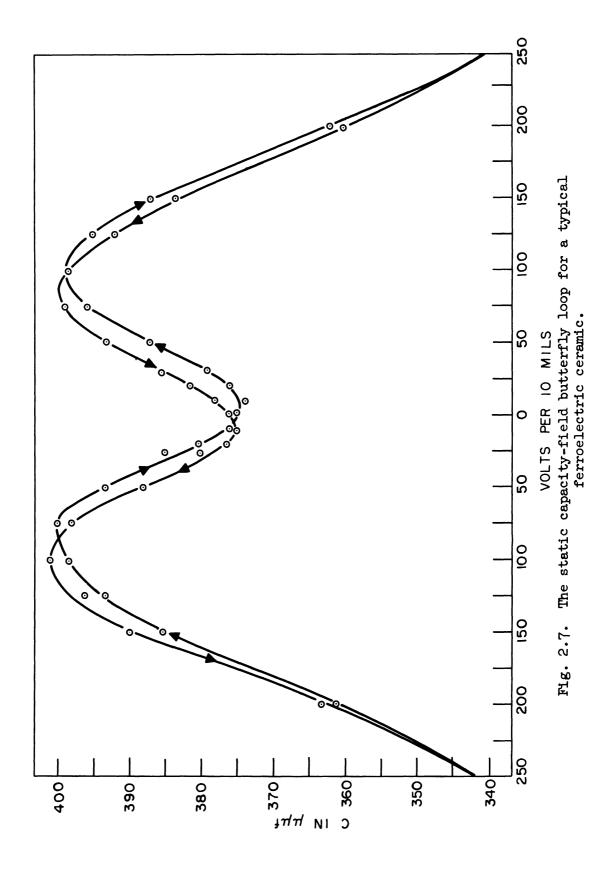

The double hysteresis loop phenomena may be demonstrated very graphically as shown in Fig. 2.7 by means of a butterfly plot (Ref. 10). For convenience, the incremental capacity, which is proportional to the  $\epsilon \Delta$  of the sample is plotted against the applied field. From a practical point of view the hysteresis effect means that if the control voltage is raised from zero to a given value, one signal capacitance is obtained. If the same value of control voltage is arrived at from a high voltage setting, a different value of signal capacitance will occur.

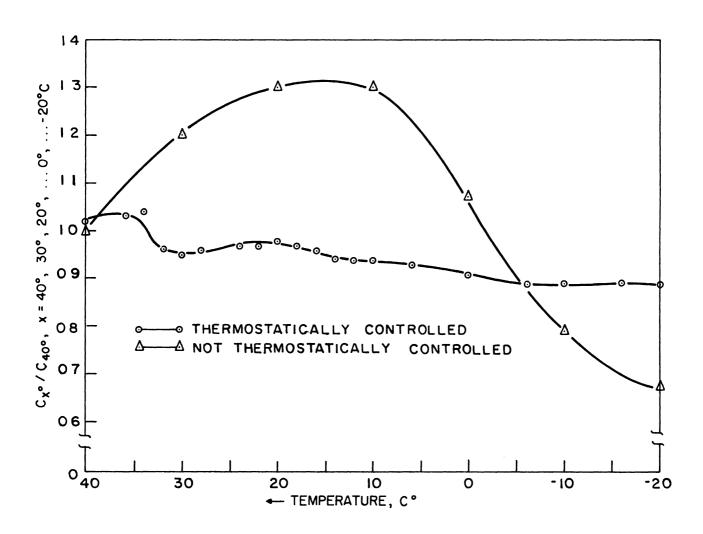

Presently available ferroelectric capacitors have relatively poor temperature stability (Ref. 11). There is no value of control voltage that gives a zero temperature coefficient over a wide temperature range as was the case in ferrite tuning. The design of circuits using ferroelectric tuning which must operate over a wide range of ambient temperatures must therefore include temperature control of the capacitors. This is not a serious peoblem, however, because of the very small volume occupied by the capacitors. It is not difficult to build a capacitor tuning unit and a low-watt thermostatically-controlled heater in a miniature oven having a volume of .01 cubic inch.

Figure 2.8 demonstrates the stability of a typical ferroelectric capacitor with and without the use of the thermostating techniques. The temperature of the environment was varied from  $+40^{\circ}$ C down to  $-20^{\circ}$ C. In both cases, the ratio of the value of capacity at various temperatures to that at  $40^{\circ}$ C was plotted as a function of temperature in degrees C.

Fig. 2.8. Ratio of capacitance, C /C , vs. temperature in degrees centigrade.

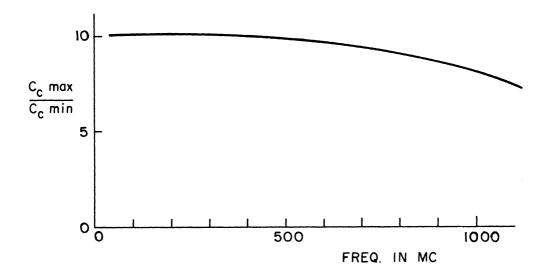

At frequencies up to 100 Mc ferroelectrics are available with capacitance change ratios in the order of 10:1 at a field strength of about 100 volts/mil. The capacitance tuning ratio drops to perhaps 8:1 at 1000 Mc and to about 2:1 at 3000 Mc for the same field strength. The curve of Fig. 2.9 shows the ratio of maximum to minimum capacitance plotted versus frequency.

Fig. 2.9.  $\frac{C_c max}{C_c min}$  of typical ferroelectric capacitor vs. frequency.

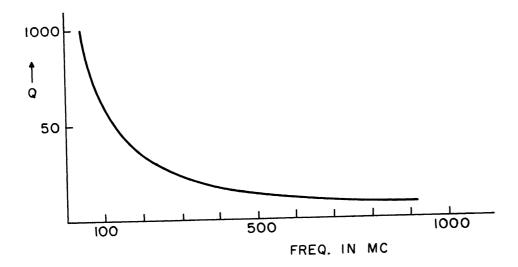

Representative Q values in the order of 100 are available for frequencies up to about 10 Mc. The Q values are in the order of 50 at 100 Mc, 10 at 1000 Mc, and about 3 to 6 at 3000 Mc. The curve of Fig. 2.10 shows typical values of Q plotted versus frequency. Since in a tuned tank circuit both Q and frequency increase with an increasing bias field, a reasonable Q is maintained over the tuning range.

Fig. 2.10. Q of a typical ferroelectric capacitor versus frequency.

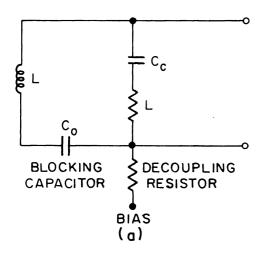

Figure 2.11a illustrates the basic circuit for application of a voltage variable capacitance in a tuned circuit. In many cases, the circuit Q may be satisfactorily high when this simple circuit is used, and if C<sub>O</sub> is chosen much larger than the maximum capacitance of the ferroelectric, the frequency range will be determined by the available capacitance range of the ferroelectric. However, it may often be true that the losses in the ferroelectric material cause an unacceptable decrease in circuit Q. Fig. 2.11b depicts a method of increasing the tuned circuit Q by including a small loss-free capacitor (C) in series with the ferroelectric.

L = total inductance in tank circuit

r = loss associated with ferroelectric capacitance

C = loss-free capacitance

C = controllable capacitance (ferroelectric)

Fig. 2.11. Basic circuit for application of a ferroelectric capacitor in a tuned circuit.

$$Q_{cap} = \frac{1}{\omega r C_c}$$

(2.6)

$$TR_{cap} = \frac{C_{c} max}{C_{c} min}$$

(2.7)

The Q of the ferroelectric capacitor with the loss-free capacitor (C) in series is

$$Q_{\text{circuit}} = Q_{\text{cap}} \left[ \frac{C_{c} + C}{C} \right]$$

(2.8)

while the tuning ratio becomes

$$TR_{circuit} = TR_{cap} \left[ \frac{C_{cmin} + C}{C_{cmax} + C} \right]^{\frac{1}{2}}$$

(2.9)

If  $C >> C_c$ , the frequency range will be determined by the available capacitance range of the ferroelectric. However, if  $C_c >> C$ , then a definite gain in Q may be achieved but only through a loss in effective capacitance variation range.

The energy required to obtain the full capacitance variation is

$$E = \int_{0}^{V \text{ max}} C(V) \cdot V dV \qquad (2.10)$$

This energy generally results in a power demand of a few milliwatts for most low frequency-swept devices.

The relationship between control voltage and signal capacitance is nonlinear, the percentage change in capacitance per unit control voltage being greatest for small control voltage values. Since in many cases this is undesirable, shaping of the control voltage must be done to compensate for the nonlinearity.

The problem of furnishing the electronic means for tuning a ferroelectric capacitor is not serious. An example of step frequency control is shown below: In the frequency range 1 to 3 Mc, it is desired to step from 1 to 2 Mc in 1 microsecond. The circuit has the following properties:

Control capacitance = 200 μμf

Required control voltage shift = 50 volts

Control current i =  $C \frac{de}{dt} = 200 \times 10^{-12} \times 50 \times 10^6 = 10 \text{ ma}$

Peak control power  $P = .010 \times 50 = .5$  watt for 1 microsecond

A control current of 10 ma may be easily obtained from transistor circuits, so the design problem is reasonably simple.

In conclusion the study and development of ferroelectric material has resulted in a controllable capacitance having a volume less than .001 cubic inch, weighing a few grams, and being capable of tuning a frequency range of 10 to 1 at 100 Mc to 3 to 1 at over 3000 Mc. Q's of the order of 100 - 3 are obtained over this frequency range. Coefficient of capacitor drift with temperature depends upon bias voltage and for a nominal bias voltage is about 1%/°C.

2.3.2 Voltage Variable Diode Capacitor. The voltage sensitivity of semiconductor junction capacitance was understood prior to 1940. Not until recently, however, has this property been exploited for broad use in electronic circuitry (Ref. 12).

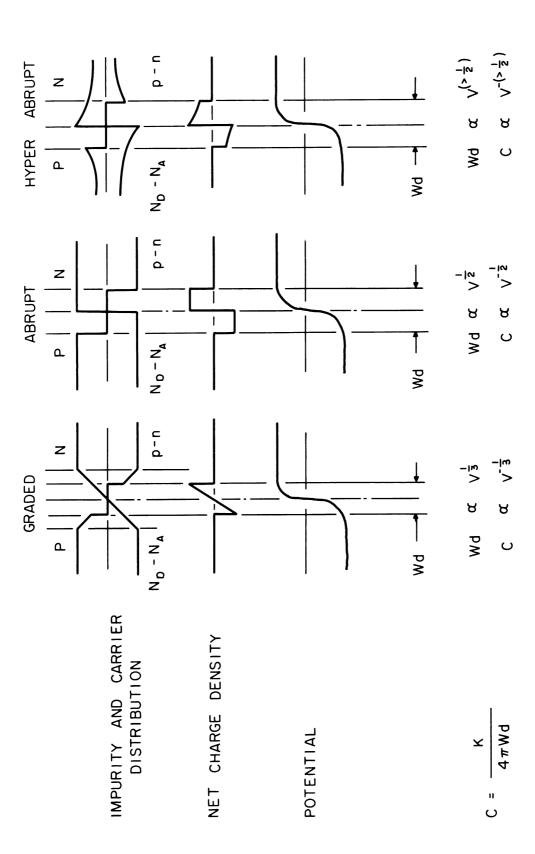

The reverse voltage on a semiconductor junction is supported by a region which is depleted of mobile carriers, as shown by Fig. 2.12. As the applied reverse voltage is changed, the depletion width (Wd) necessary to support the voltage changes. This depleted region acts as an insulator, resulting in a capacitance which varies in an inverse manner with applied voltage.

Voltage sensitivity of capacitance depends on the impurity distribution in the junction region. The more abrupt the junction, the greater the depletion width depends on applied voltage, resulting in a higher voltage sensitivity of capacitance.

For a parallel plate arrangement, the p-n junction has a capacitance equal to:

$$C = \frac{\epsilon A}{\overline{Wd}}$$

(2.11)

Fig. 2.12. Voltage sensitivity of capacitance.

$\epsilon$  = permittivity of the dielectric

A = junction area

Wd = width of the depletion region

For the case of an abrupt junction, the depletion width is given by:

$$Wd = 1 = K_1 \sqrt{V + V_0}$$

(2.12)

combining Eqs. (2.11) and (2.12) for an abrupt junction

$$C = \frac{\epsilon A}{K_1 \sqrt{V + V_0}}$$

(2.13)

where

K = a constant

$V_{\gamma}$  = applied bias voltage

V = internal contact potential (0.3 to 0.9 volts)

When V is small with respect to V an abrupt junction exhibits a capacitance which varies with the inverse square root of voltage.

Other capacitance voltage functions may be obtained across differently graded p-n junctions. If, for example, the semiconductor changes from p to n in a linear manner the capacitance varies as the inverse cube root of the applied voltage.

Voltage variable capacitance diodes have relatively good temperature stability (Ref. 13). The capacitance is fairly independent of temperature at the higher bias levels and becomes increasingly more sensitive with decreasing bias levels. This agrees quite closely with theory since the major uncompensated temperature effect is the internal contact voltage,  $V_0$ , term in Eq. (2.13). For silicon,  $V_0$  is approximately

.08 volts at 25°C and decreases to .04 volts at 150°C. The result is an approximately linear temperature sensitivity of about .15%/°C at 0.5 volts, .025%/°C at -4 volts, becoming negligible at higher voltages.

At frequencies up to 50 Mc voltage variable capacitance diodes are available with capacitance change ratios in the order of 5:1

with a voltage change of -2 volts to 100 volts. Using special fabrication techniques capacitance change ratios of 5:1 may be maintained up

to several hundred megacycles.

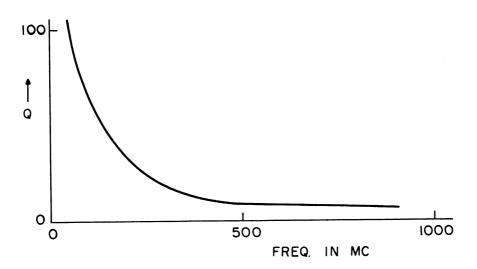

Representative Q values in the order of 100 at 50 Mc can be obtained commercially. The value of Q drops to about 10 at 500 Mc and to about 5 at 1000 Mc. The curve of Fig. 2.13 shows typical values of Q plotted versus frequency. Since the Q of the capacitor equals  $\frac{1}{\omega} \frac{1}{c_c r}$  and r remains practically constant over a wide frequency range, the product Qf remains practically constant, giving a curve which is a rectangular hyperbola.

Fig. 2.13. Q of a typical voltage variable diode capacitor vs. frequency.

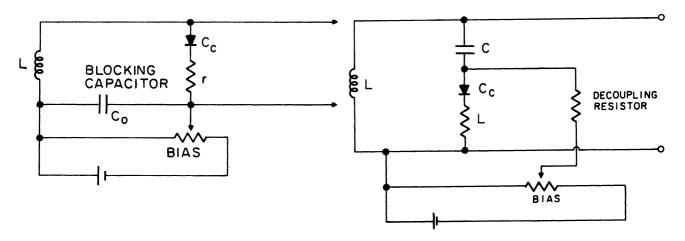

Figure 2.14 illustrates the basic circuit for application of a voltage variable capacitance diode in a tuned circuit. In many cases,

Fig. 2.14. Basic circuit for application of a voltage variable capacitance diode in a tuned circuit.

the circuit Q may be satisfactorily high when this simple circuit is used, and if C<sub>O</sub> is chosen much larger than the maximum capacitance of the diode, then the frequency range will be determined by the available capacitance range of the diode. However, it may often be true that the diode's reverse losses cause an unacceptable decrease in circuit Q. The same method of increasing the tuned circuit Q as described on pages 29-30. for the ferroelectric capacitor may also be used for the diode. Although the gain in Q is offset by loss in effective variation capacitance range, it does reduce the amount of ac across the diode--a desirable feature, because if the ac were an appreciable fraction of the lowest bias voltage applied, there would be modulation of the capacitance of the diode by the signal.

Figure 2.15 presents a suggested arrangement of two diodes in such a way as to increase the circuit Q (if this is found to be

seriously reduced by losses in a single diode), while retaining a relatively large available capacitance sweep.

Fig. 2.15. Alternate method of increasing circuit Q.

The energy required to obtain the full capacitance variation generally results in a power demand of a few milliwatts for most low frequency-swept devices.

As in the case of the ferroelectric capacitor the relationship between control voltage and signal capacitance is nonlinear, the

percentage change in capacitance per unit control voltage being greatest

for small control voltage values. Since in many cases this is undesirable, shaping of the control voltage must be done to compensate for

the nonlinearity.

The problem of furnishing the electronic means for tuning a voltage variable capacitance diode is not serious, and as in the case of the ferroelectric capacitance the control current may be easily obtained using transistor circuits.

In conclusion the study and development of voltage variable capacitance diodes has resulted in a controllable capacitance having a

volume less than .Ol cubic inches, weighing a few grams and being capable of tuning a frequency range of 5 to 1 up to several hundred Mc. Q's of 100 at 50 Mc dropping to a value of 10 at 500 Mc are readily available. The coefficient of capacitor drift with temperature depends upon bias voltage, and for a nominal bias voltage of -4 volts is about .O25%/°C.

From the foregoing discussion it is evident that the choice of a tuning element for frequency synthesis applications depends upon many factors such as frequency range of operation, tuning ratio, rapidity of frequency selection, temperature stability, control power, and environment in which the device is to be operated. No one tuning element possesses all the characteristics of the ideal tuning element discussed in Section 1.1. The controllable inductor, for example, has a high tuning ratio and Q, particularly in the lower frequency ranges with relatively small control power and good temperature stability. In addition, isolation of the controlled and controlling signals is possible. The controllable inductor presents some problems in control circuit design when step frequency operation is required and might create some difficulty if microminiaturization of the circuitry were a necessity.

The ferroelectric capacitor has a substantial tuning ratio and Q over a wide frequency range with almost negligible control power. The ferroelectric capacitor does not present any problems in control circuit design when step frequency operation is required and due to its very small size is well suited to microminiaturization. It has, however, rather poor temperature stability and in most cases would require a thermostatically controlled oven for proper operation. Since the controlling signal is nearly always at a lower frequency compared

39

to the controlled signal, isolation is easily accomplished using decoupling circuits.

The voltage variable capacitor diode has an adequate tuning ratio and Q for many applications over a wide tuning range and with negligible control power. It does not present any problems in control circuit design when step frequency operation is required and due to its small size is well suited to microminiaturization. It has good temperature stability and does not demonstrate any hysteresis effects. However, where high RF voltage may be developed across them, the junction must be back-biased far enough so that no part of the signal voltage swing causes the net voltage applied to the junction to go positive, or clipping will result. As in the case of the ferroelectric capacitor, isolation of the controlled and controlling signals is easily achieved by using a decoupling circuit.

The self-heating of ferroelectric and back-biased diode capacitors is considerably less than that of a controllable inductor for the same type of service. In addition, lead inductance limits controllable inductor operation at high frequencies whereas lead inductance does not necessarily dilute the tuning range of ferroelectrics and diodes.

In general it can be said that the present choice for a particular tuning element must be a compromise in order to obtain a close approach to the ideal in those properties most important for a specific application.

A comprehensive tabulated comparison of electronic tuning devices is carried out in Appendix A.

## CHAPTER III

ANALYSIS OF THE GENERALIZED DISCRETE FREQUENCY SYNTHESIZER

## 3.1 System Concept

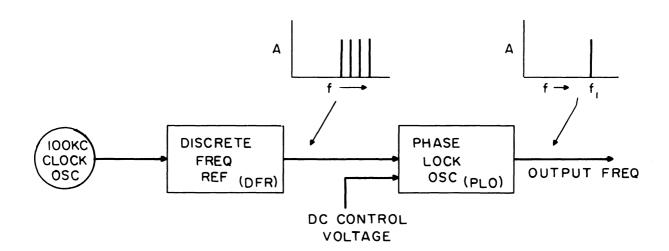

The analysis of the generalized discrete frequency synthesizer may be better understood by first considering the building blocks. The system is essentially comprised of two basic units:

- (1) A crystal (or other high precision frequency standard) controlled discrete-frequency reference (DFR).

- (2) A wideband phase-lock oscillator (PLO).

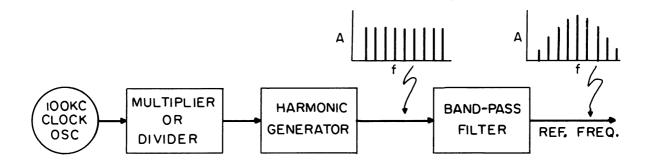

As shown in Fig. 3.1, the DFR consists of a crystal-controlled clock oscillator, multiplier or divider chains, a harmonic generator having an output rich in harmonics, and a band-pass filter.

Fig. 3.1. Discrete frequency reference (DFR).

Ideally, the filter output consists of a limited set of harmonics of approximately equal amplitude. For example, the filter output could contain components every kilocycle in the band from 110 to 120 kc. Thus the output of the DFR is the equivalent of many crystal oscillators, all with a precise harmonic relationship.

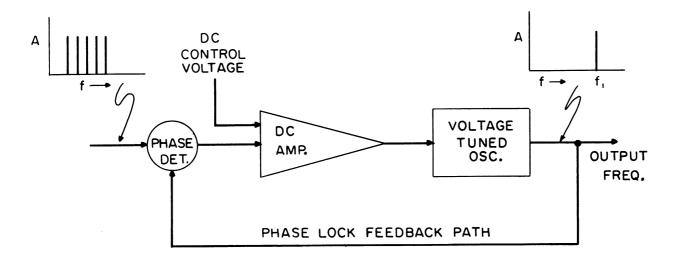

The PLO shown in Fig. 3.2 has the function of reproducing

Fig. 3.2. Phase-lock oscillator (PLO).

cleanly one of a number of frequency components applied to its input. It thus acts as a tunable narrowband filter. The voltage-tuned oscillator has its output frequency and phase compared in the phase detector with the desired harmonic of the input waveform. If these are of the same frequency, the output of the phase detector will be a dc voltage dependent upon the phase difference of the oscillator and the reference. This dc voltage is amplified and fed to the control element in the oscillator. If the oscillator frequency tends to drift or change in any way, this attempted change is first sensed as a phase-difference change in the phase detector. This produces a change in phase detector output voltage which acts to hold the oscillator frequency constant. In short, if the oscillator tends to drift, its output phase relative to that of the reference will change but its average frequency (f<sub>1</sub>) will remain fixed.

Note that in automatic frequency control systems the frequency

of the oscillator is compared to a reference frequency, e.g., the resonant frequency of a passive circuit, and the frequency difference—not phase difference—is used to generate a signal which tends to reduce the frequency difference. Such a system requires a small but finite error of the controlled variable (the output frequency) in order to operate. The phase—lock system, on the other hand, requires no steady—state error of the controlled variable but instead utilizes an error in the integral of the controlled variable, i.e., an error in phase difference.

When not in phase-lock the oscillator frequency may be brought within the capture range of the desired harmonic by means of the externally applied dc voltage.

By combining the discrete-frequency reference, Fig. 3.1, and the phase-lock oscillator, Fig. 3.2, it is possible to construct a unit whose output frequency can have certain discrete values. This unit, called a discrete-frequency generator (DFG), (Fig. 3.3) has an output

Fig. 3.3. Discrete-frequency generator (DFG).

frequency which is precisely one of the harmonics of the discrete-frequency reference. The number of different frequencies that can be selected is a function of the voltage-tuned oscillator set-on accuracy. If, for example, it is desired to tune the DFG over a 10 Mc range and, in addition, if it is assumed that the relatively unprecise tuning elements will not allow open-loop set-on accuracies greater than about  $^{\pm}$  5 percent, then the DFG can only cover the 10 Mc range accurately in 1 Mc steps. This, in effect, means that the discrete-frequency reference can not have components spaced any closer than 1 Mc over the 10 Mc band.

Starting with this as a basic unit to produce one digit of the desired frequency, decade units are added to furnish the desired number of significant figures.

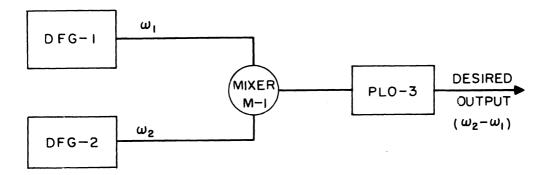

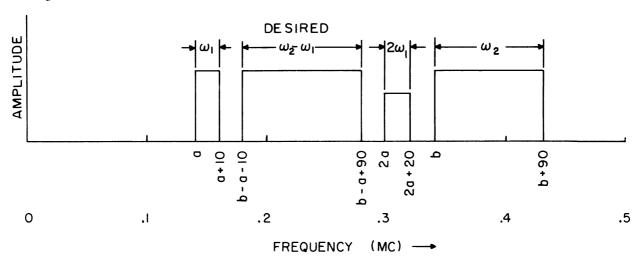

Operations and details of a proposed generalized discretefrequency synthesizer may be understood with the aid of the example shown in Fig. 3.4.

Fig. 3.4. Generalized discrete-frequency synthesizer.

A single clock oscillator and suitable multiplier divider chains furnish the basic frequency  $\Delta f_i$  (i = 1, 2, ..., k, for DFG-i; i = 1, 2, ..., k, where  $\Delta f_i$  is the harmonic spacing of DFG-i). The range of DFG-i is  $f_i$  to  $(f_i + 9\Delta f_i)$  in  $\Delta f_i$  steps, and if it is assumed that  $\Delta \mathbf{f}_1 > \Delta \mathbf{f}_2 > \dots > \Delta \mathbf{f}_k$  then the total range of the k-digit synthesizer is  $10\Delta f_1$  in  $\Delta f_k$  steps. For example, if  $\Delta f_1$  = 5 Mc and  $\Delta f_k$  = 100 kc, the range of the synthesizer is 50 Mc in 100-kc steps. As indicated in Fig. 3.4, the range of DFG-1 is  $f_1$  to  $(f_1 + 9\Delta f_1)$  in  $\Delta f_1$  steps, and of DFG-2 is  $f_2$  to  $(f_2 + 9\Delta f_2)$  in  $\Delta f_2$  steps. Single output frequencies, e.g.,  $f_1$  + A $\triangle f_1$  from DFG-1 and  $f_2$  + B $\triangle f_2$  from DFG-2, are fed to mixer (M-1). The output of the mixer contains components  $m(f_1 + A\triangle f_1) \stackrel{+}{=}$  $n(f_2 + B\Delta f_2)$ , where m and n are positive or negative integers. The output of the mixer is fed to the phase-lock oscillator (PLO-1), whose operating range is confined to the frequency range  $(f_1 + A\triangle f_1) + / (f_2 + B\Delta f_2)$ , where +/- means either + or -. Higher-order harmonics in the mixer output which happen to fall within this band are of such low amplitude that they are ignored by PLO-1.

The voltage-tuned oscillators in DFG-1 and DFG-2 are brought to the approximate vicinity of the selected reference components by means of rough tuning dc voltages  $V_1$  and  $V_2$ . The phase-lock loops then take over and bring the oscillators into precise frequency alignment with the selected components. The same rough tuning voltages  $V_1$  which are applied to DFG-1 are also applied to PLO-1. This brings the frequency of the voltage-tuned oscillator of PLO-1 within the capture range of the desired  $(f_1 + A\triangle f_1) + /- (f_2 + B\triangle f_2)$  frequency, where its phase-lock loop takes over and brings the oscillator into precise frequency alignment. The capture range of PLO-1 must be at

least  $9\Delta f_2$  wider than the capture range of DFG-1, so the same tuning voltage can effect capture at any frequency  $(f_1 + A\Delta f_1) + /- (f_2 + B\Delta f_2)$ .

Additional decades operate in a similar manner producing a final output frequency of  $(f_1 + A \triangle f_1) + /- (f_2 + B \triangle f_2) + /- \dots$ ,  $(f_k + j \triangle f_k)$  which has the desired range of 10  $\triangle f_1$  in  $\triangle f_k$  steps.

This example shows a generalized discrete-frequency synthesizer capable of producing frequencies to k digit accuracy with high precision, since the whole system is crystal-controlled by a single clock oscillator.

The synthesizer system may be further modified to give any desired frequency between the steps of the lowest order digit. This may be done by furnishing a vernier oscillator at the low frequency tuning range of  $\Delta f_k$ .

The operating range of the synthesizer may be placed in any desired position in the frequency spectrum up to approximately 300 Mc with presently available transistors and solid-state tuning elements.

As indicated in Chapter I, to achieve an efficient synthesis technique basic research in a number of problem areas is required. For example:

- (1) A study and evaluation of the various methods for the efficient production of high-order harmonics with balanced energy distribution over the frequency band of interest is required.

- (2) Basic research in phase-lock oscillator design with particular attention directed toward operation at higher frequencies and toward such dynamic characteristics as capture range, capture stability, rapid frequency convergence, and purity of the output signal is needed.

(3) An analysis of the problem of combining two signal frequencies to obtain a single signal frequency in the form of their sum or difference while using tunable narrowband filters, i.e., PLO's of a practical design with arbitrarily-limited frequency discrimination characteristics, is required.

These problem areas will be considered in detail in the following sections.

## 3.2 Discrete Frequency Reference

To initiate the study and evaluation of the various methods for the efficient production of high-order harmonics with balanced energy distribution over the frequency band of interest, a generalized statement of the problem is in order:

- (1) What class of time functions will produce a given frequency spectrum?

- (2) Of this class which functions will have the maximum amount of the total available spectrum energy in the band of interest and at the same time have a minimum peak-to-average voltage characteristic?

- (3) What practical methods are available for generating these desirable functions?

- 3.2.1 Definition of Peak Factor. Any periodic function with period T which may be represented by a Fourier Series has the form

$$e(t) = \frac{E_0}{2} + \sum_{n=1}^{\infty} E_n \cos(n\omega_0 t + \theta_n)$$

(3.1)

where  $E_0$ ,  $E_k$ ,  $\theta_k$  (k = 1, 2, 3, ...) are all real and  $\omega_0 = \frac{2\pi}{T}$ .

The average power of e(t) across a 1-ohm resistor is defined as follows:

$$P_{\text{avg}} = \frac{1}{T} \int_{0}^{T} [e(t)]^{2} dt \qquad (3.2)$$

Parseval's theorem states that whenever e(t) is bounded and integrable over the period then

$$\frac{1}{T} \int_{0}^{T} [e(t)]^{2} dt = \frac{1}{2} [E_{0}^{2} + \sum_{n=1}^{\infty} E_{n}^{2}]$$

(3.3)

Let

$$f(t) = A \cos (\omega t + \theta)$$

(3.4)

where f(t) is a single frequency function with peak value A. The average power of this single frequency function is

$$P_{avg} = \frac{1}{T} [A^2 \cdot \frac{T}{2}] = \frac{A^2}{2}$$

(3.5)

and is completely independent of both frequency and phase. If the average power of the single frequency function f(t) is equated to that of the arbitrary periodic function e(t), one finds that

$$\frac{A^{2}}{2} = \frac{1}{2} \left[ \frac{E_{0}}{2} + \sum_{n=1}^{\infty} E_{n}^{2} \right]$$

(3.6)

or

$$A = \sqrt{\frac{E_0^2}{2} + \sum_{n=1}^{\infty} E_n^2}$$

(3.7)