# LOW TEMPERATURE WAFER LEVEL VACUUM PACKAGING USING AU-SI EUTECTIC BONDING AND LOCALIZED HEATING

by

Jay S. Mitchell

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Mechanical Engineering) in The University of Michigan 2008

### **Doctoral Committee:**

Professor Khalil Najafi, Co-Chair Professor Yogesh B. Gianchandani, Co-Chair Professor Katsuo Kurabayashi Professor Kensall D. Wise Gholamhassan R. Lahiji, Visiting Research Scientist, University of Michigan © Jay S. Mitchell

All rights reserved

2008

To Mom, Dad and Grandma.

#### ACKNOWLEDGEMENTS

I would first and for most like to thank my parents, my grandparents and even my great grandparents. It is because of them that I have had such an easy life and have had the educational opportunities that I have had.

I would like to thank my advisor, Professor Khalil Najafi. Working here at the University has been one of the best experiences of my life and he has been an excellent mentor. I have learned a lot. I would also like to thank the rest of my committee members: Professor Yogesh Gianchandani, Professor Katsuo Kurabayashi, Professor Kensal Wise and Dr. Gholamhassan. They were always approachable and had useful advice.

I would like to thank all of my lab mates and friends at Michigan. They are the ones that made my time here so enjoyable and were always willing to help. This is not a comprehensive list, but here are some of the people I would like to thank: Warren (Neil) Welch, Joseph Potkay, Wen-Lung Huang Troy Olsson, Hanseup Kim, Amir Borna, Sang Woo Lee, Sang Hyun Lee, Sang Won Yoon, Ruba Borno, Scott Wright, Allan Evans, Mohamed A. Abdelmoneum, John R. Clark, Yuan Xie, Andrew Kuo, Andre Snellings, Andre Taylor, Andy Gross, Gayatri Perlin, Razi Haque, Burcu Ucok, Andrew DeHennis, Amar Basu, Christine Eun, Mark Richardson, Brian Stark, TJ Harpster, Niloufar Ghafouri and Robert Franklin. I would like to thank Tzeno Galchev and Jae Yoong Cho last because they helped less than anyone else.

I would like to thank the WIMS and MNF staff including: Gregg Allion, Katherine Beach, Ning Gulari, Brendan Casey, Ed Tang, Brian VanderElzen, Robert Gordenker, Joe Giachino, Trasa Burkhardt and Rob Hower.

I would also like to thank my Ann Arbor friends that supported me including: Dean Hildebrand, Asra Khan, Becky Kelley, Mayank Kansal, and Nathan Anderson.

I am so happy to be done, wahoo!!!

# **TABLE OF CONTENTS**

| DEDICATION                                                               | ii |

|--------------------------------------------------------------------------|----|

| ACKNOWLEDGEMENTS                                                         |    |

| LIST OF FIGURES                                                          |    |

| LIST OF TABLES                                                           |    |

| LIST OF APPENDICES                                                       |    |

| ABSTRACT                                                                 |    |

| CHAPTER 1 INTRODUCTION                                                   |    |

| 1.1 IC Wafer Level Packaging                                             |    |

| 1.2 MEMS Wafer Level Packaging                                           |    |

| 1.2.1 Physical Requirements                                              |    |

| 1.2.1.1 Packages with Access to the Environment                          |    |

| 1.2.1.2 Stiction and Non-Stick Coatings                                  |    |

| 1.2.1.3 Biomedical and Microfluidics Packaging                           |    |

| 1.2.1.4 Vacuum/Hermetic Encapsulation & Protection from the Environment  |    |

| 1.2.2 Electrical Connection & Integration                                |    |

| 1.2.3 Integration                                                        | 13 |

| 1.2.4 Thermal Requirements                                               | 15 |

| 1.3 MEMS Wafer Level Encapsulation Approaches                            | 16 |

| 1.3.1 Integrated Encapsulation (Thin Film Packaging)                     | 16 |

| 1.3.2 Post Processing (Packaging Using Wafer Bonding)                    | 18 |

| 1.3.2.1 Fusion (Direct) Bonding                                          |    |

| 1.3.2.2 Anodic Bonding                                                   |    |

| 1.3.2.3 Thermo-compression Bonding                                       |    |

| 1.3.2.4 Glass Frit Bonding                                               |    |

| 1.3.2.5 Spin on Glass (SOG) Bonding                                      |    |

| 1.3.2.6 Polymer/Adhesive Bonding                                         |    |

| 1.3.2.7 Solder/Eutectic Bonding                                          |    |

| 1.3.3 Localized Heating                                                  |    |

| 1.3.3.2 Inductive Heating                                                |    |

| 1.3.3.3 Electromagnetic Radiation Heating                                |    |

| 1.3.3.4 Laser Assisted Bonding                                           |    |

| 1.4 Previous Work in MEMS Vacuum Encapsulation                           |    |

| 1.4.1 Vacuum Encapsulation Using Thin Film Packaging                     |    |

| 1.4.2 Vacuum Encapsulation Using Wafer Bonding                           |    |

| 1.4.2.1 Applications of Getters in Micro-Packages                        |    |

| 1.5 Summary & Motivation                                                 |    |

| 1.5.1 Demand for Generic Wafer-Level Packaging                           |    |

| 1.5.1 Demand for Generic water-Level Packaging                           |    |

| 1.5.3 Motivation for Au-Si Eutectic Bonding & Backside Localized Heating |    |

| •                                                                        |    |

| 1.6 Contributions of this Thesis                                         | 50 |

| 1.7     | Organization of Thesis                                      | 36  |

|---------|-------------------------------------------------------------|-----|

| CHAPTER | 2 AU-SI EUTECTIC WAFER BONDING                              | 38  |

| 2.1     | Background & Previous Work                                  | 40  |

| 2.1     | 1.1 Silicon Diffusion into Au Thin Films                    | 42  |

|         | 2.1.1.1 Low Temperature Si Diffusion and Silicide Formation |     |

|         | 2.1.1.2 Oxide Formation on Au Thin Films                    |     |

| 2       | 2.1.1.3 Structure of Au/Si Films after Intermixing          |     |

| 2.2     | 1.2 Past work in Au-Si Eutectic Bonding at the Wafer Level  |     |

| 2.3     | Material requirements for Au-Si Eutectic Bonds              |     |

|         | 3.1 Wafer Fabrication for Bond Experiments                  |     |

| ۷       | 2.3.1.1 Cap Wafer Fabrication for Bond Experiments          |     |

|         | 2.3.1.2 "Dummy" Device Wafer Fabrication                    | 51  |

|         | 2.3.1.3 Wafer Preparation for Bond Experiments              |     |

| 2.3     | 3.2 A Discussion on the Cap Wafer Bond Rings                |     |

|         | 3.3 Bonds to Un-Doped Poly-Si                               |     |

|         | 3.4 Bonds to Phosphorous Doped Poly-Si                      |     |

| 2       | 3.5 Bonds to Au Films                                       |     |

|         | 2.3.5.1 Derrydration Bake                                   |     |

|         | 2.3.5.3 Bonds to Glass                                      |     |

| 2.4     | The Bond Recipe for Au-Si Eutectic Bonds                    |     |

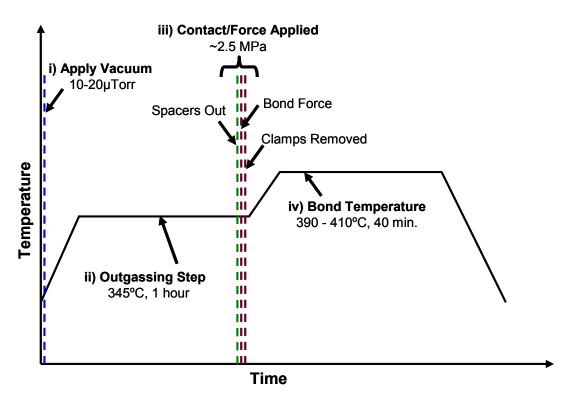

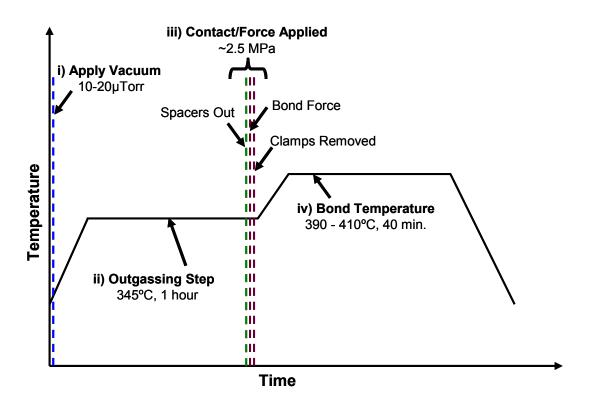

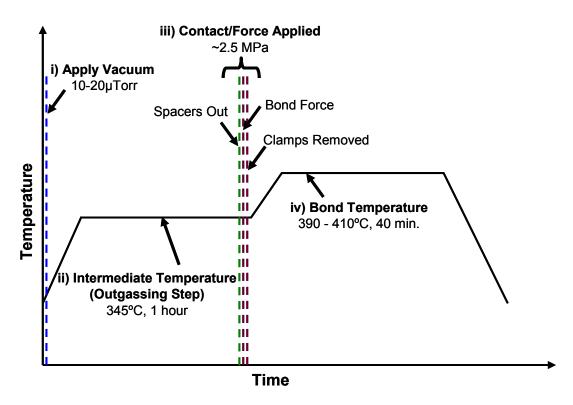

| 2.4     | 4.1 Step 1: Application of Vacuum                           | 72  |

| 2.4     | 4.2 Step 2: The Outgassing Step                             |     |

| 2.4     | 4.3 Step 3: Wafer Contact & Bond Force                      |     |

|         | 2.4.3.1 Low Bond Pressure Results (~1 MPa)                  |     |

|         | 2.4.3.2 High Bond Pressure Results (~10 MPa)                |     |

| 2 4     | 2.4.3.3 Timing of the Applied Bond Pressure                 |     |

| 2.5     | Au-Si Eutectic Lateral Flow                                 |     |

| 2.5     |                                                             |     |

|         | 5.2 Effects of an Anisotropic Etched Cavity                 |     |

| 2.5     | 5.3 Lateral Flow Onto Getters                               |     |

| 2.5     | 5.4 Analysis of Au-Si Alloy Flow                            |     |

| 2.6     | Summary of Bond Parameters                                  | 92  |

| CHAPTER | 3 WAFER LEVEL PACKAGING USING AU-SI EUTECTIC BONDING        | 95  |

| 3.1     | Cap Wafer Fabrication                                       | 97  |

| 3.2     | Device Wafer Fabrication                                    | 100 |

| 3.3     | Device Release                                              | 104 |

|         | 3.1 Hot Plate Release                                       |     |

|         | 3.2 Critical Point Dryer (CPD) Release                      |     |

| 3.4     | Bond ring & Device Layout                                   |     |

| 3.5     | Wafer Preparation for Bonding                               |     |

|         | 4 PIRANI (VACUUM) SENSOR DESIGN AND TESTING                 |     |

| 4.1     | Methods for Vacuum/Hermetic Characterization                |     |

| 4       | 1.1 Leak Rate Testers                                       | 112 |

|     | 4.1.2                   | Packaged Sensor                                                                           | 113 |

|-----|-------------------------|-------------------------------------------------------------------------------------------|-----|

|     | 4.2                     | Background & Previous Pirani Gauge Research                                               | 115 |

|     | 4.3                     | Approach and Design                                                                       | 119 |

|     | 4.3.1<br>4.3.2<br>4.3.3 | Confirmation of the Model                                                                 | 121 |

|     | 4.4                     | Fabrication of Pirani Gauge Test Structures                                               |     |

|     | 4.4.1<br>4.4.2          | Device Layout                                                                             | 127 |

|     | 4.4.3                   | e e e e e e e e e e e e e e e e e e e                                                     |     |

|     | 4.5                     | Pirani Gauge Characterization                                                             | 131 |

|     | 4.6                     | Implementation for Package Characterization                                               | 136 |

|     | 4.6.1                   |                                                                                           |     |

|     | 4.6.2                   |                                                                                           |     |

|     |                         | 6.2.1 Pressure Measurement Ranges                                                         |     |

|     | 4.<br>4.6.3             | 6.2.2 De-capping for Calibration Measurement Error                                        |     |

|     |                         | 6.3.1 Measurement Accuracy                                                                |     |

|     |                         | 6.3.2 Precision                                                                           |     |

|     | 4.                      | 6.3.3 Error Due to Temperature Fluctuation                                                | 144 |

|     | 4.                      | 6.3.4 Summary of Pirani Gauge Performance                                                 | 146 |

| CHA | APTER 5                 | VACUUM CHARACTERIZATION OF MICROPACKAGES                                                  | 147 |

|     | 5.1                     | Physical Leaks and Outgassing                                                             | 148 |

|     | 5.1.1                   | J                                                                                         |     |

|     | 5.1.2                   | Outgassing in Micro-Cavities                                                              | 150 |

|     | 5.2                     | Device Layout Considerations for Testing                                                  | 152 |

|     | 5.3                     | Vacuum Packaging Results                                                                  | 154 |

|     | 5.3.1                   | · · · · - · · · · · · · · · · · ·                                                         |     |

|     |                         | 3.1.1 Analysis of Bond #67                                                                |     |

|     |                         | 3.1.2 Analysis of Bond #100                                                               |     |

|     | 5.3.2                   | 3.1.3 Long Term Testing for Bonds without Getters Bonds with Getters, >100 mTorr Pressure |     |

|     |                         | 3.2.1 Analysis of Bond #103                                                               |     |

|     |                         | 3.2.2 Analysis of Bond #105                                                               |     |

|     |                         | 3.2.3 Long Term Testing for Bonds with Getters but Without an Outgassing Step             |     |

|     | 5.3.3                   |                                                                                           |     |

|     |                         | 3.3.1 Analysis of Bond #71                                                                |     |

|     |                         | 3.3.2 Analysis of Bond #78                                                                |     |

|     |                         | 3.3.3 Long Term Testing for Bonds with Getters and With an Outgassing Step                |     |

|     | 5.4                     | High Temperature Exposure, Thermal Cycling and Burn In                                    |     |

|     |                         | 4.1.1 Pressures after Transit                                                             |     |

|     |                         | 4.1.2 Temperature Ramping Experiments                                                     |     |

|     |                         | 4.1.3 Thermal Cycling Tests                                                               |     |

|     | 5.5                     | Summary of Vacuum Testing Results                                                         |     |

| Сп  |                         | DIFFERENTIAL LOCALIZED HEATING                                                            |     |

| СПА |                         |                                                                                           |     |

|     | 6.1                     | Modeling & Analysis                                                                       | 193 |

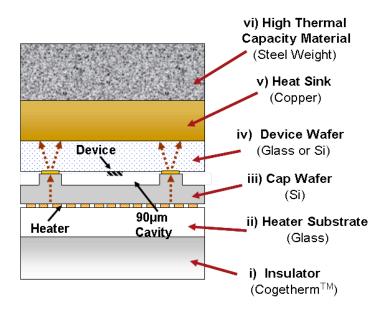

| 6.1.1 Materials and Thermal Design                                                   |     |

|--------------------------------------------------------------------------------------|-----|

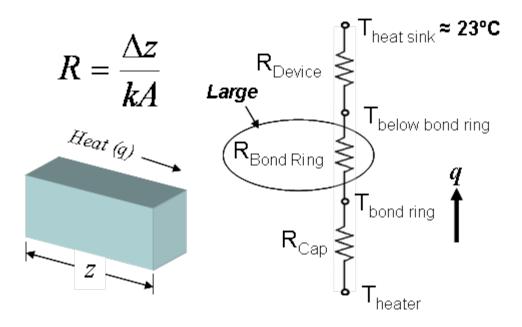

| 6.1.2 A 1-D Circuit Electrical Equivalent Model                                      |     |

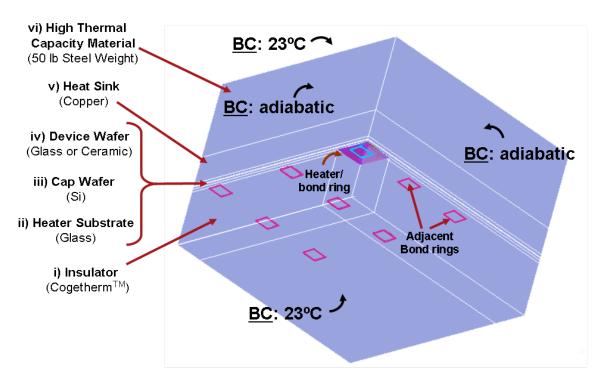

| 6.1.3 A 3-D Model of the Test Setup                                                  |     |

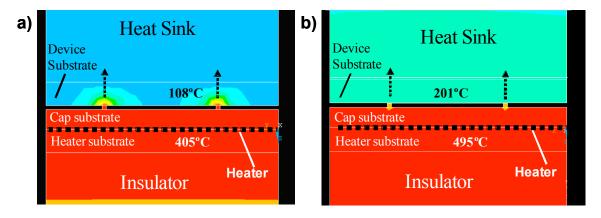

| 6.1.3.1 Si to Glass Bonds                                                            |     |

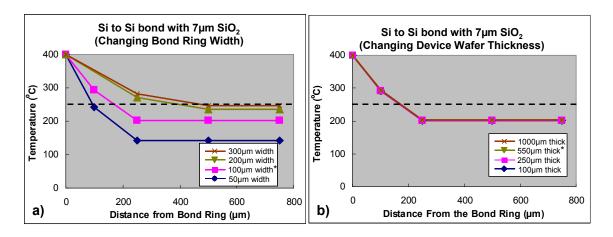

| 6.1.3.2 Si to Si Bonds                                                               |     |

| 6.1.4 Summary of Modeling Results                                                    |     |

| 6.2 Wafer Fabrication for Bond Experiments                                           |     |

| 6.2.1 Cap Wafer Fabrication                                                          |     |

| 6.2.2 Device Wafer Fabrication                                                       |     |

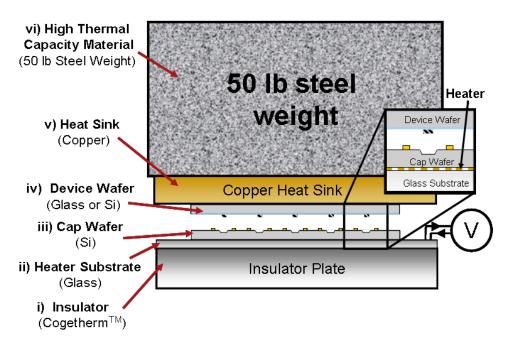

| 6.3 Test Setup Design & Assembly                                                     | 212 |

| 6.3.1 Test Setup Design                                                              | 213 |

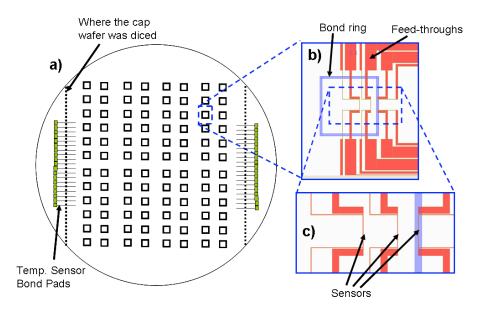

| 6.3.2 Layout of the Device Wafers                                                    |     |

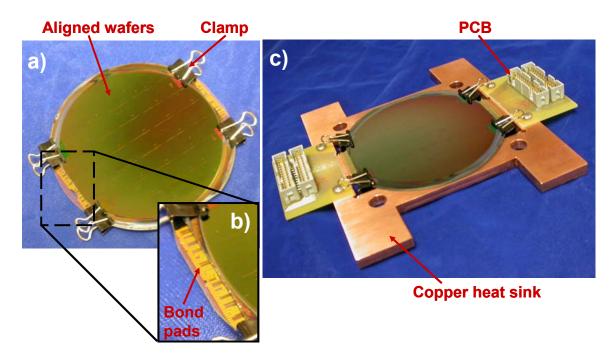

| 6.3.3 Assembly of the Test Setup                                                     |     |

| 6.3.3.1 Step 1: Device and Cap Wafers Alignment                                      |     |

| 6.3.3.2 Step 2: Integration of the Copper Heat Sink                                  | 216 |

| 6.3.3.3 Step 3: Integration of the Heaters Substrate & Cogetherm <sup>TM</sup> Plate |     |

| 6.3.3.4 Step 4: The Final Assembly                                                   |     |

| 6.3.4 Temperature Sensor Design & Calibration                                        |     |

| 6.3.5 Heater Design & Calibration                                                    |     |

| 6.4 Results & Discussion                                                             |     |

| 6.4.1 Bond Experiment #1 (Si to Glass)                                               |     |

| 6.4.1.1 Heater Characterization                                                      |     |

| 6.4.1.2 Temperature Sensor Measurement                                               |     |

| 6.4.1.3 Au-Si Eutectic Bonding Using Localized Heating                               |     |

| 6.4.2 Bond Experiment #2 (Si to Si with a 7 μm SiO <sub>2</sub> layer)               |     |

| 6.4.2.1 Heater Characterization                                                      |     |

| 6.4.2.2 Temperature Sensor Measurement                                               |     |

|                                                                                      |     |

| 6.5 Conclusion                                                                       | 239 |

| 6.6 Considerations for Application of Differential Localized Heating                 |     |

| 6.6.1 The Full Wafer Model                                                           |     |

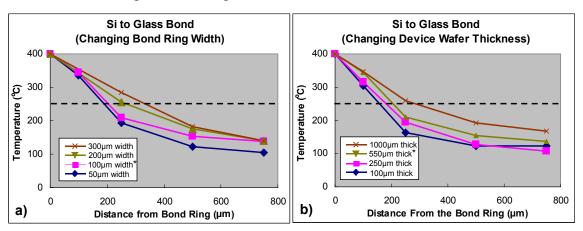

| 6.6.2 Parametric Analysis                                                            | 243 |

| 6.6.2.1 The Si to Glass Bond                                                         |     |

| 6.6.2.2 The Si to Si Bond with a 7 μm thick SiO <sub>2</sub> Layer                   |     |

| 6.6.2.3 Summary of Parametric Analysis                                               |     |

| 6.6.3 Effects of CTE Mismatch                                                        |     |

| CHAPTER 7 CONLUSION                                                                  | 252 |

| 7.1 Dissertation Summary                                                             | 252 |

| 7.2 Suggestions For Future Work                                                      | 255 |

| 7.2.1 The Au-Si Eutectic Bonding Process                                             | 255 |

| 7.2.2 Vacuum Packaging and Measurement                                               |     |

| 7.2.3 Differential Localized Heating                                                 |     |

| APPENDICES                                                                           |     |

| BIBLIOGRAPHY                                                                         | 291 |

# LIST OF FIGURES

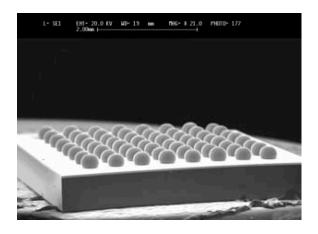

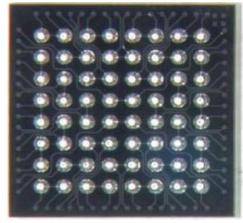

| Figure 1.1: An SEM (left) and microscope photograph (right) of mBGAs                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

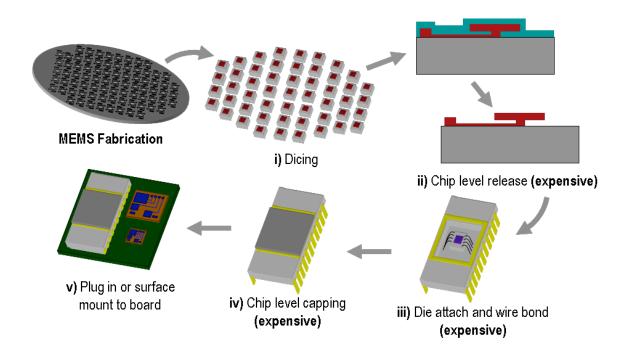

| Figure 1.2: A schematic showing the typical packaging steps in a MEMS chip level packaging process                                                                                                     |

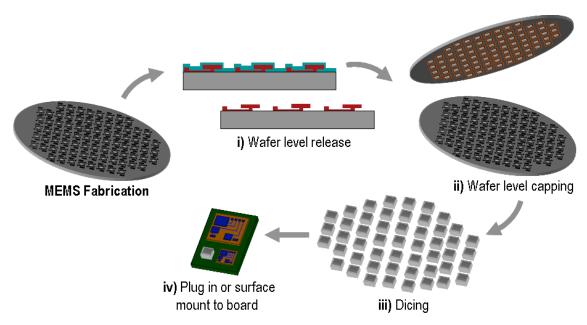

| Figure 1.3: A schematic showing the typical packaging steps in a MEMS wafer-level packaging process                                                                                                    |

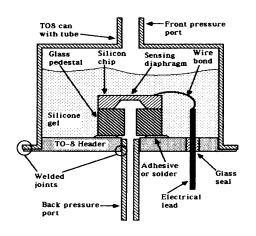

| Figure 1.4: A schematic of a MEMS pressure sensor package [14]                                                                                                                                         |

| Figure 1.5: A schematic of a MEMS microphone package [15]                                                                                                                                              |

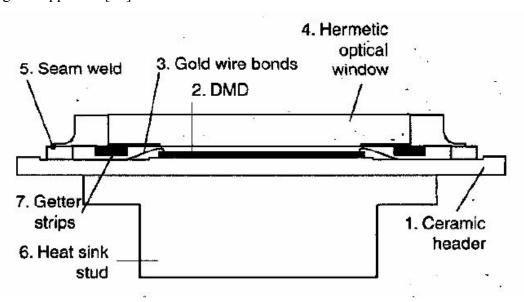

| Figure 1.6: A schematic of the encapsulation used for Texas Instruments micro-mirrors [21]9                                                                                                            |

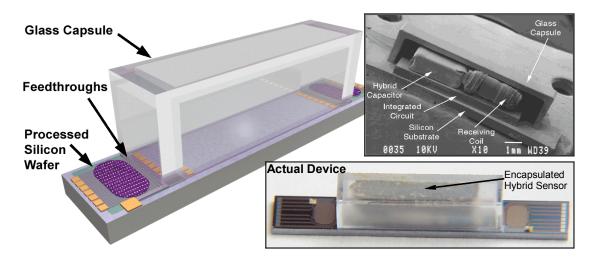

| Figure 1.7: An encapsulation approach for implantable devices done at the University of Michigan [26]                                                                                                  |

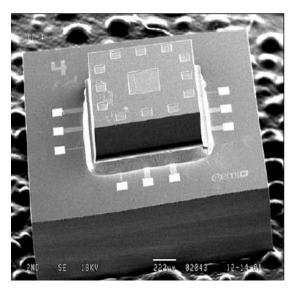

| Figure 1.8: A scanning electron microscope (SEM) picture a wafer-level packaged micro-switch manufactured by Radent MEMS [17]                                                                          |

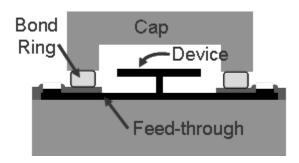

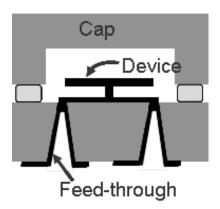

| Figure 1.9: A schematic illustrating lateral feed-throughs.                                                                                                                                            |

| Figure 1.10: A schematic illustrating vertical feed-throughs                                                                                                                                           |

| Figure 1.11: An SEM of a packaged accelerometer using vertical feed-throughs by Analog Devices [38]                                                                                                    |

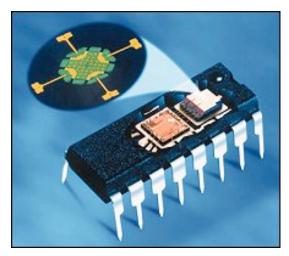

| Figure 1.12: A Motorola accelerometer using the 2 chip approach [39]                                                                                                                                   |

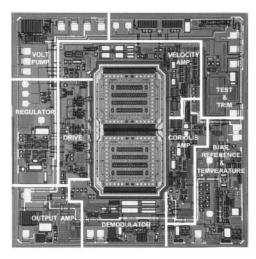

| Figure 1.13: An Analog Devices gyroscope using the 1 chip approach [40]15                                                                                                                              |

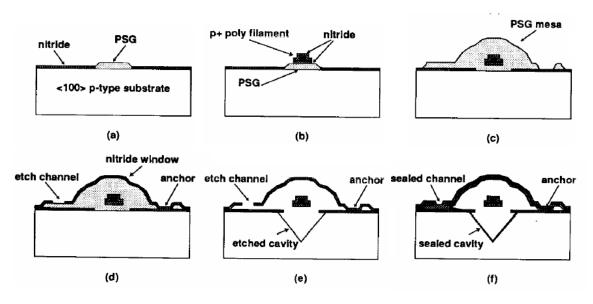

| Figure 1.14: A schematic showing the process flow for thin film encapsulation [44] 17                                                                                                                  |

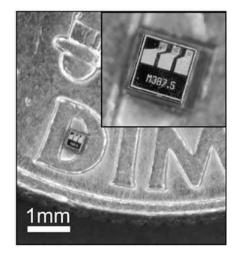

| Figure 1.15: A packaged accelerometer developed by Stanford University and Bosch [55]                                                                                                                  |

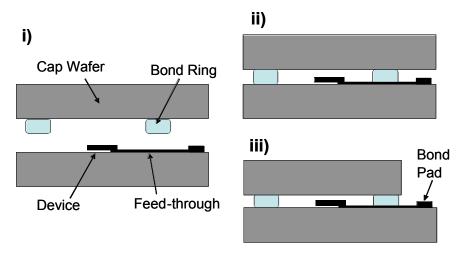

| Figure 1.16: One encapsulation scheme using i) a cap wafer and a bond ring where ii) the wafers are bonded and iii) part of the top wafer is removed in order to access a bond pad for interconnection |

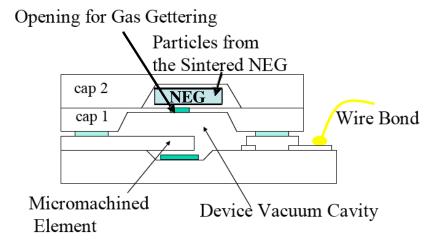

| Figure 1.17: In application of NEGs, a separate compartment is often used to house the NEG getters [5].                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

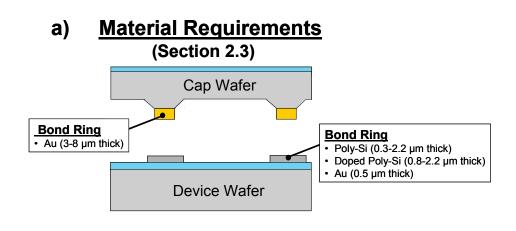

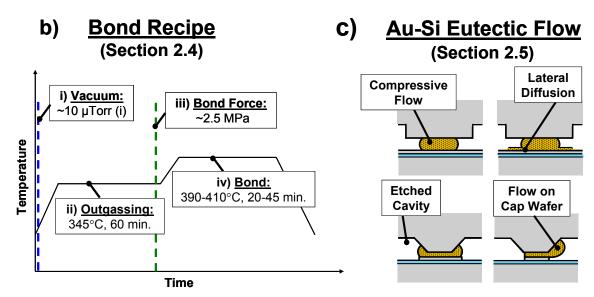

| Figure 2.1: A summary of the three sets of bond issues discussed in this chapter for Au-Si eutectic bonding. They are a) the material requirements, b) the bond recipe and Au-Si eutectic flow.                                                  |

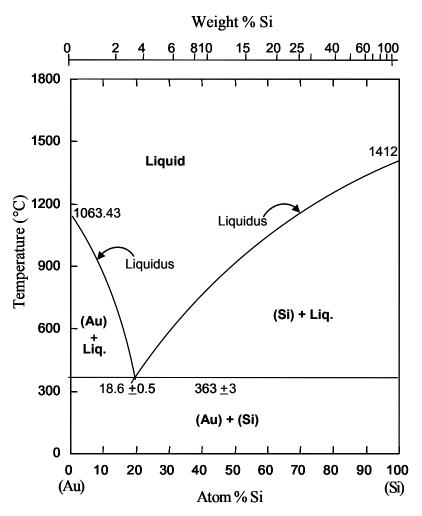

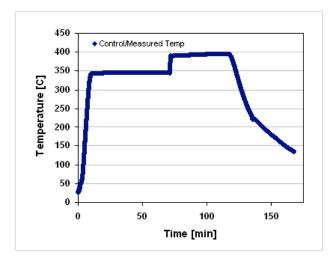

| Figure 2.2: The Au-Si eutectic phase diagram [152].                                                                                                                                                                                              |

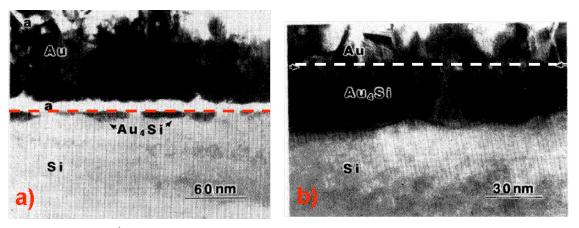

| Figure 2.3: A ~1400Å thick film deposited on (100) Si at 80°C that sat in air at room temperature for a) 60 days and the b) 150 days [176]                                                                                                       |

| Figure 2.4: Illustrates the method in which Mei [102] used for characterizing vacuum packages                                                                                                                                                    |

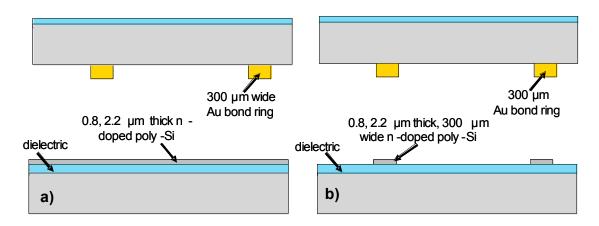

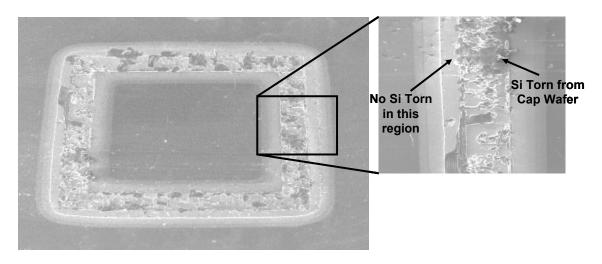

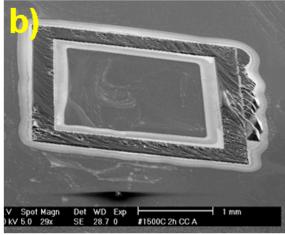

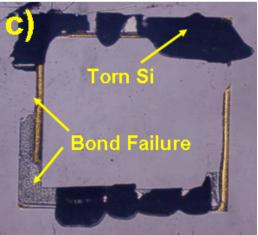

| Figure 2.5: a) A picture where a wafer was partially diced so that caps were arrayed across the wafer, and b) a picture of a "dummy" device wafer substrate after a cap was torn off where Si tore for the entire circumference of the bond ring |

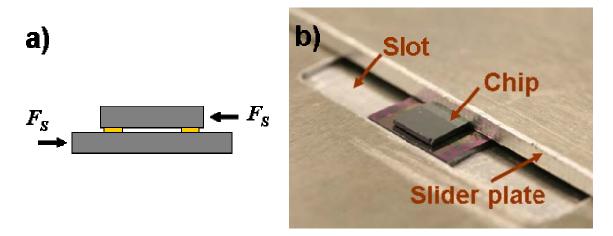

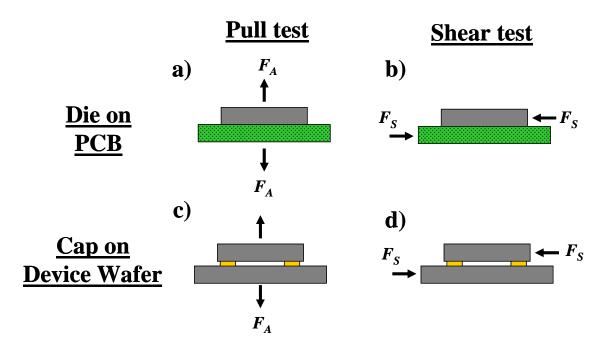

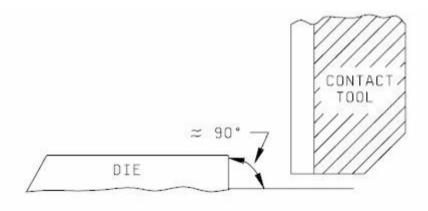

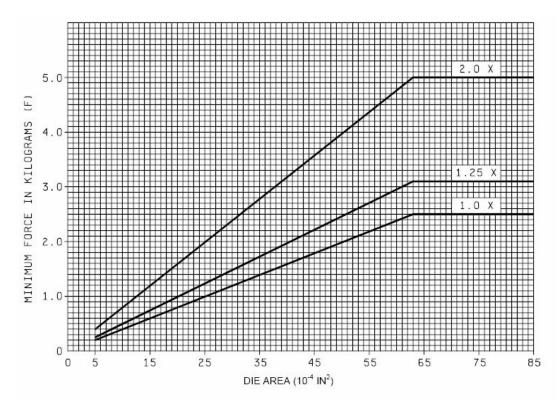

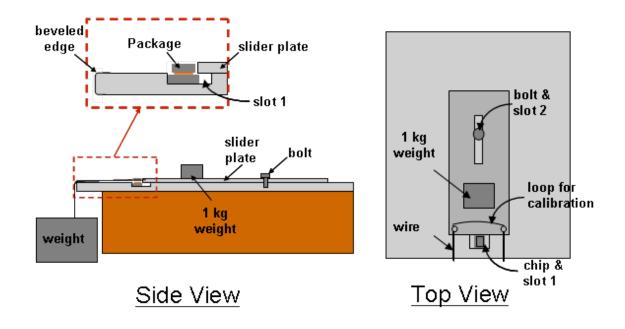

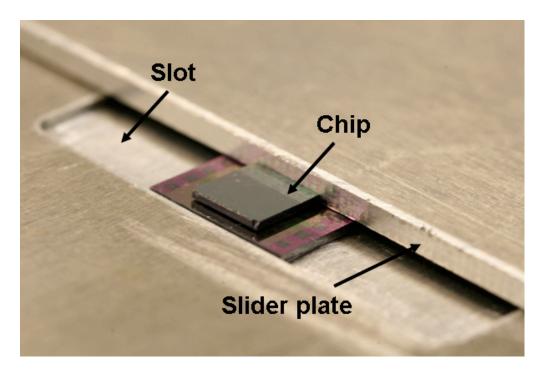

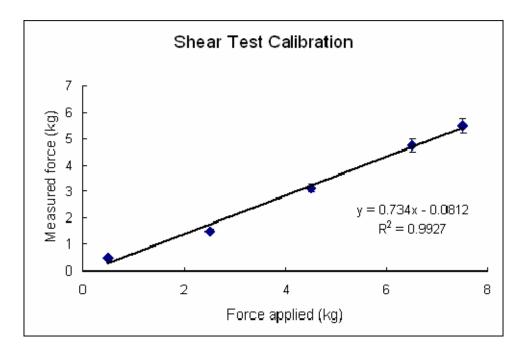

| Figure 2.6: a) A schematic of how the shear force is applied and b) a picture of a diced package inside of the shear test setup                                                                                                                  |

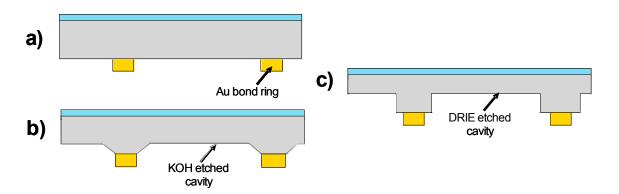

| Figure 2.7: Schematics of the cap wafer configurations used for bond experiments in Chapter 2 showing: a) a cap wafer without an etched cavity, b) a cap wafer with a KOH or TMAH etched cavity and c) a cap wafer with a DRIE etched cavity51   |

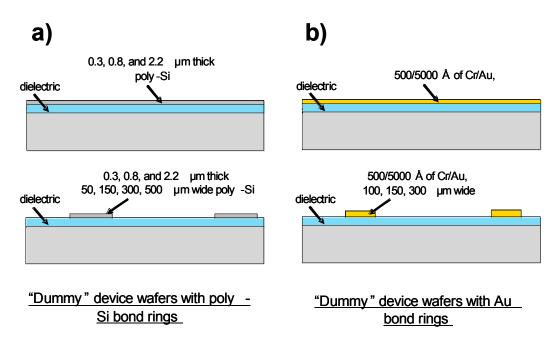

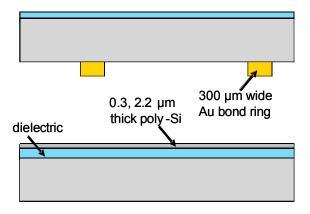

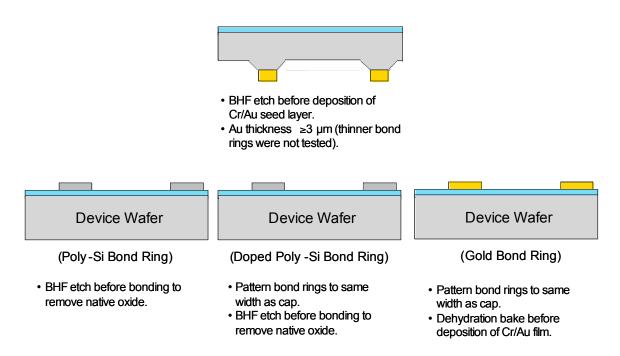

| Figure 2.8: Schematics of the different "dummy" device wafer configurations for bonds to poly-Si and Au                                                                                                                                          |

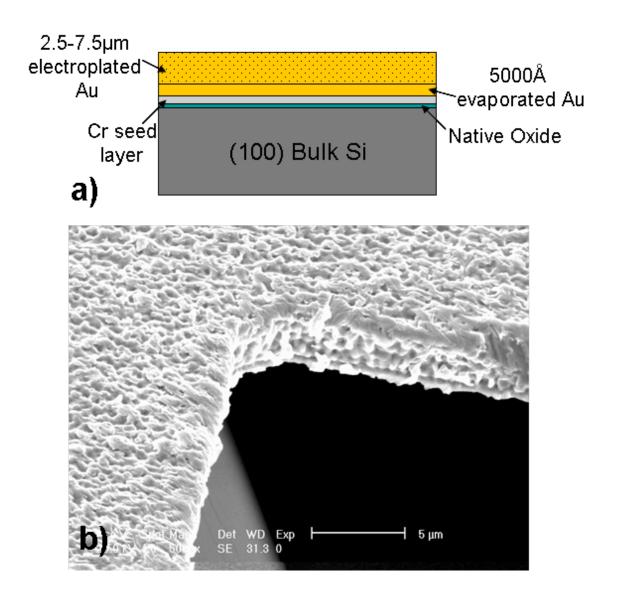

| Figure 2.9: a) Schematic of the thin film stack where a native SiO <sub>2</sub> and a Cr layer act as a potential diffusion layer for between the Si and the Au and b) an SEM of the rough electroplated Au layer.                               |

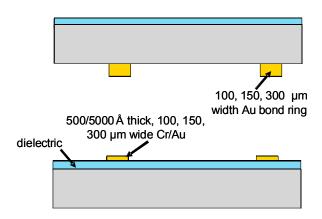

| Figure 2.10: The dimensions of the films for bonds from the experiments shown in Table 2.2.                                                                                                                                                      |

| Figure 2.11: The dimensions of the films for bonds from the experiments shown in a)  Table 2.6 and b) in Table 2.8.                                                                                                                              |

| Figure 2.12: a) Photograph of the "dummy" device wafer after pulling the two bonded wafers apart for bond #31 and b) a schematic showing how the poly-Si was pulled of off the underlying dielectric.                                            |

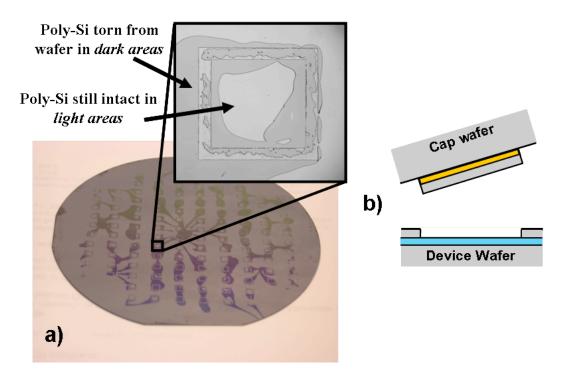

| Figure 2.13: An SEM of a bond ring from bond #101 after the cap was torn off of the device wafer.                                                                                                                                                |

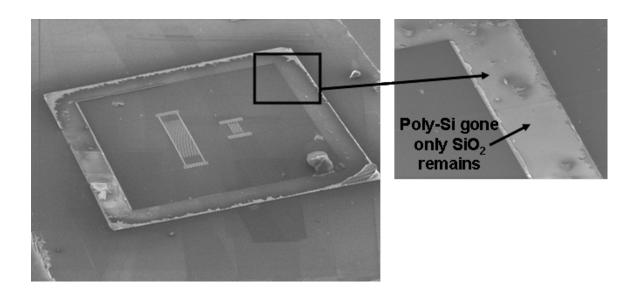

| Figure 2.14: The dimensions of the films for bonds from the experiments shown Table 2.12.                                                                                                                                                        |

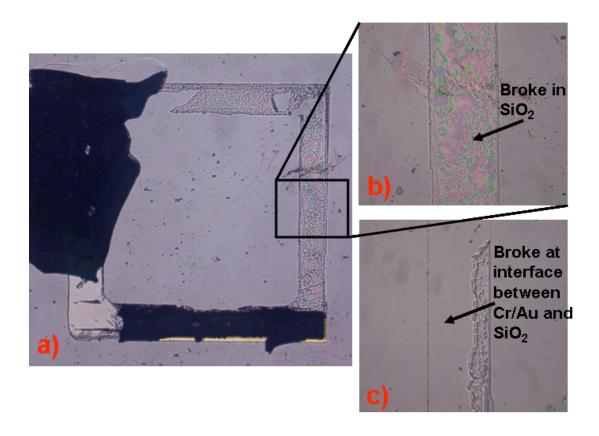

| Figure 2.15: Microscope photographs of a) the "dummy" device side of a bond ring from bond #92 where in some parts of the bond ring silicon tore from the other wafer indicating a strong bond, in some parts the Cr/Au delaminated from the wafer and it some parts part of the SiO <sub>2</sub> was pulled off of the device wafer. b) Shows a close of view of an area where oxide was torn off and c) shows an area (on a different bond ring) where the Cr/Au delaminated from the device wafer                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

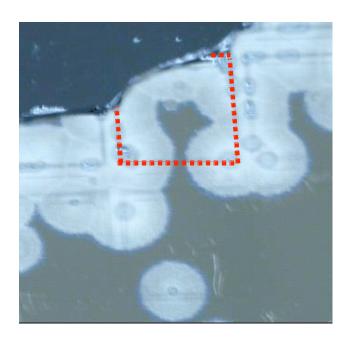

| Figure 2.16: The device side of bond #32 where a bond was done to an un-patterned Au thin film. The dotted line shows the location of one of the bond rings                                                                                                                                                                                                                                                                                                                                                         |

| Figure 2.17: The generic bond recipe.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Figure 2.18: The "dummy" device substrate after a cap was sheared off for bond #537.                                                                                                                                                                                                                                                                                                                                                                                                                                |

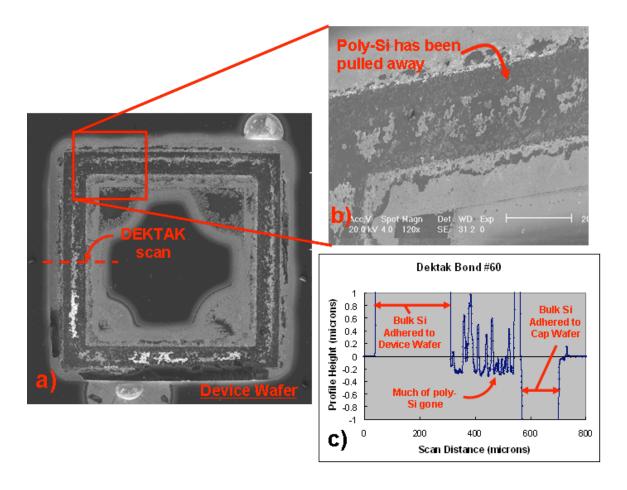

| Figure 2.19: For bond #60, an SEM of a) the top view of the bond ring on the "dummy" device wafer after the cap has been pulled off, b) a closer look at the bond ring, and c) a DEKTAK scan of a portion of this bond ring.                                                                                                                                                                                                                                                                                        |

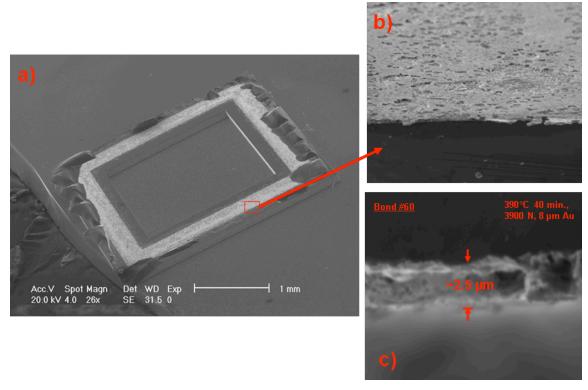

| Figure 2.20: SEM of a) the cap side of the one of the bond rings from bond #60, b) a closer look at the Au-Si alloy layer which still adheres to the cap side, and c) a cleaved section which show the thickness of this Au-Si alloy layer                                                                                                                                                                                                                                                                          |

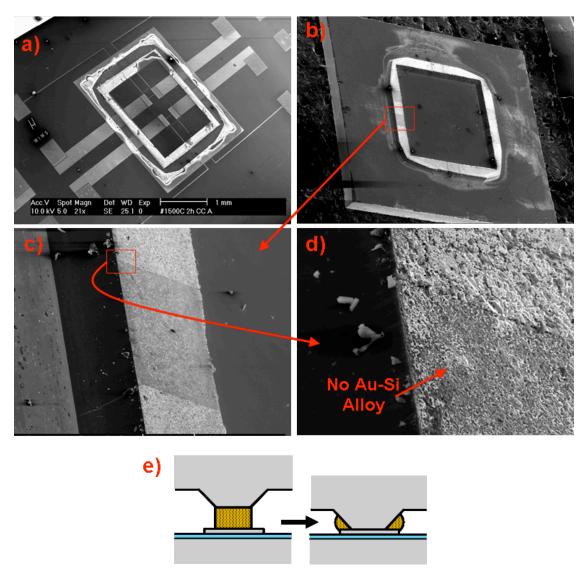

| Figure 2.21: SEM of a) the device side of the one of the bond rings from bond #49 wher mist of the Au-Si alloy has squeezed out from the bond joint, b) the cap side of bond #49, and c),d) a closer look at one of the feed-through indentations showing that the feed-through had pressed flush against the Si surface of the cap wafer squeezing out nearly all of the Au-Si liquid. e) Shows a schematic of how the silicon from the cap wafer appears to press nearly flush to the surface of the device wafer |

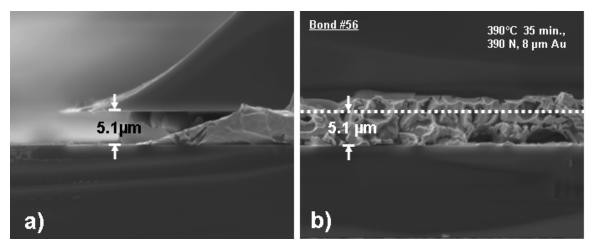

| Figure 2.22: SEMS of a cleaved bond ring from bond #56 showing a) the final distance between the original interfaces between the cap and device wafers and b) a cross-section of the bond ring where the dotted line shows the distance between the original interface at the cap wafer and the "dummy" device interface                                                                                                                                                                                            |

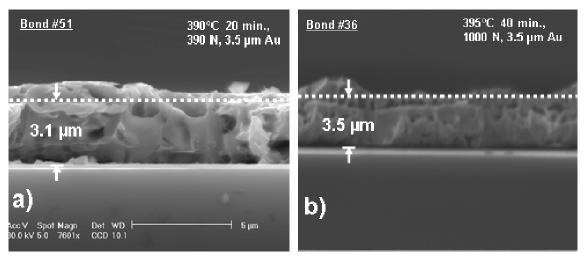

| Figure 2.23: SEMS of a cleaved section of bond rings showing a cross-section where the dotted line shows the distance between the original interface at the cap wafer and the "dummy" device interface for a) bond #51 and b) bond #36                                                                                                                                                                                                                                                                              |

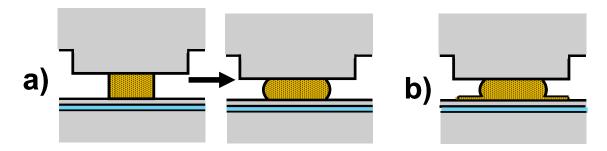

| Figure 2.24: A schematic showing how Au-Si alloy a) squeezes laterally, widening the effective bond width for bonds in which the cap wafer was not patterned or was patterned with a DRIE etch. b) Shows Au-Si lateral flow where only a thin layer of Au-Si eutectic spread.                                                                                                                                                                                                                                       |

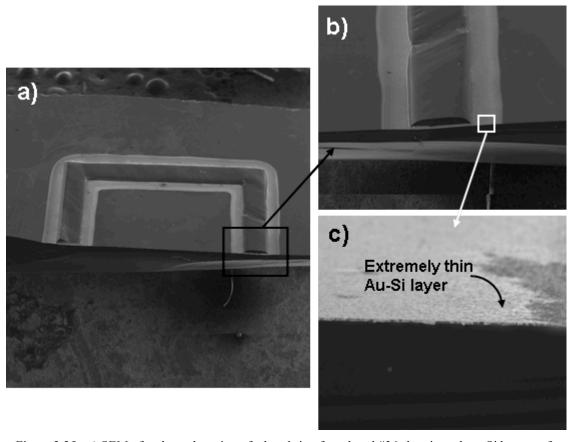

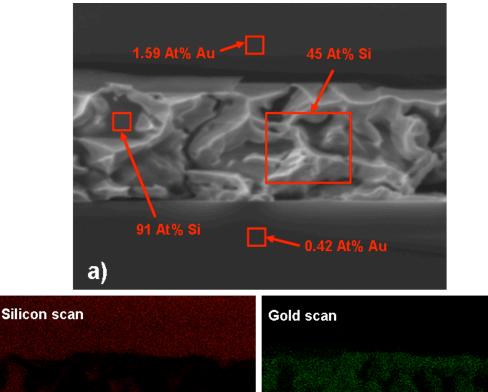

| Figure 2.25: a) SEM of a cleaved section of a bond ring from bond #36 showing where Si has torn from the cap wafer and the light area is Au-Si alloy which has spread laterally across the surface. b, c) A closer look at this Au-Si that has spread across the top surface of the poly shows that it is only l0s of nanometers or even angstroms thick.                                                                                                                                                           |

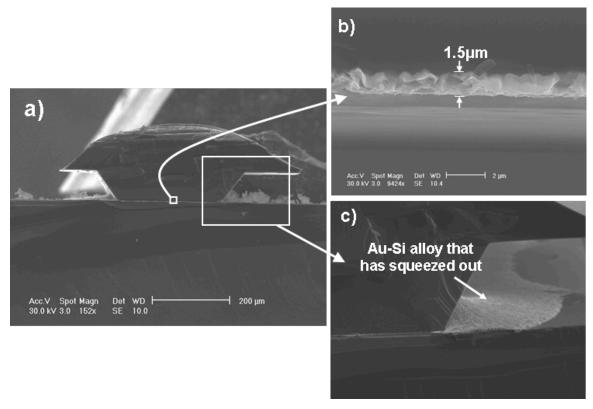

| Figure 2.26: a) An SEM of the cross-section of one of the bond rings from Bond #71 which shows the anisotropically etched side walls, b) a closer look showing the bond interface, and c) a look at the right side of the anisotropically etch side wall showing the large volume of Au-Si alloy which has squeezed out                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

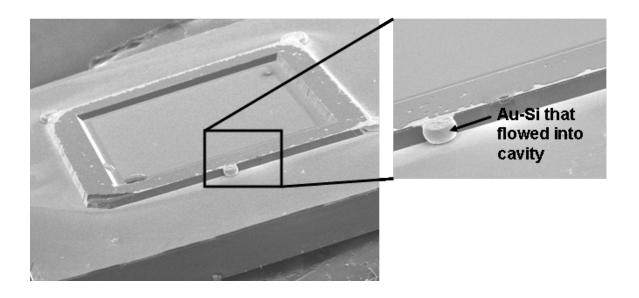

| Figure 2.27: An SEM photograph of the cap side of bond #101 where Au-Si alloy has flowed on the cap side                                                                                                                                                                                                                                                                                                                                                                                                                    |

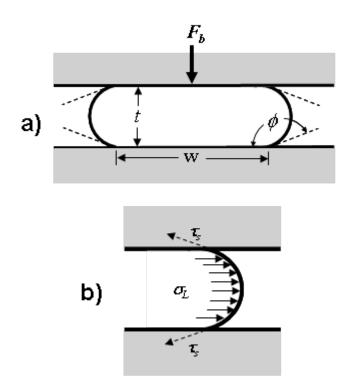

| Figure 2.28: a) A schematic showing the different parameters which effect the calculations for achieving static equilibrium in the bond ring, and b) a closer look at how the pressure in the liquid is balanced by the surface tension90                                                                                                                                                                                                                                                                                   |

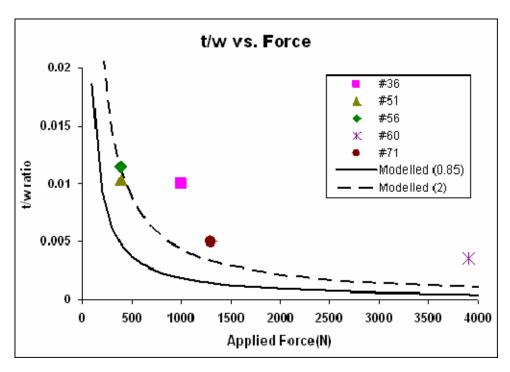

| Figure 2.29: A graph of t/w vs. the applied force for several of the bonds discussed in section 2.6.2 and the modeled t/w vs. the applied bond force assuming a contact angle of 152° and a surface tension of 0.85 and 2 N/m                                                                                                                                                                                                                                                                                               |

| Figure 2.30: A summary of the material requirements for bonds between a cap wafer with a Au bond ring and a device wafer with: an un-doped poly-Si thin film, a heavily phosphorous doped poly-Si thin film and gold thin film                                                                                                                                                                                                                                                                                              |

| Figure 2.31: A summary of the important parameters in the bond recipe94                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

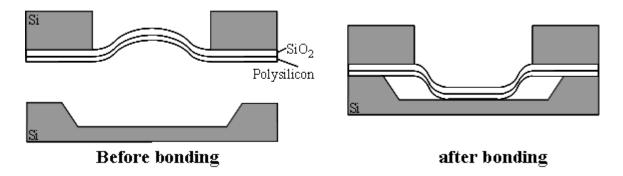

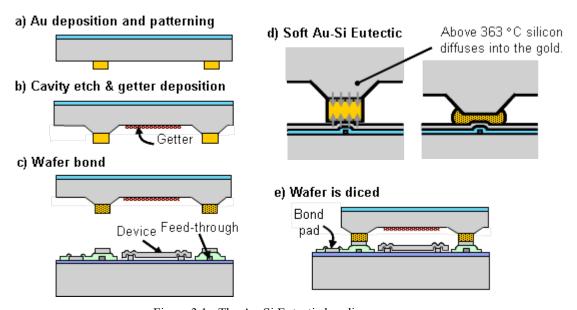

| Figure 3.1: The Au-Si Eutectic bonding process. 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

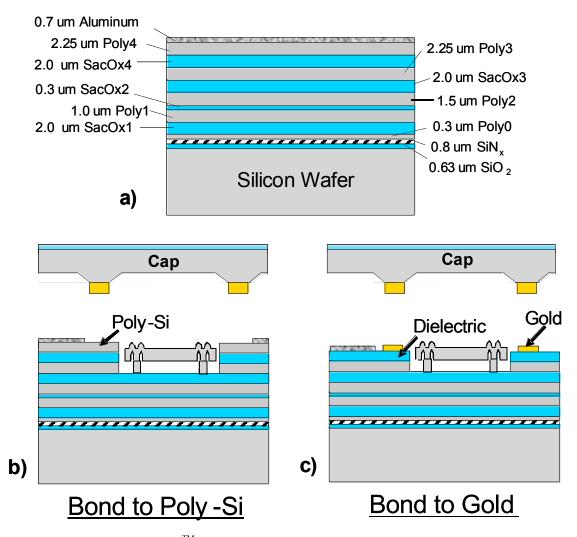

| Figure 3.2: a) The SUMMiT V <sup>TM</sup> thin film stack as an example of a CMOS process, b) bonding to the Poly-Si in this thin film stack and c) bonding to gold layer deposited on top of this thin film stack                                                                                                                                                                                                                                                                                                          |

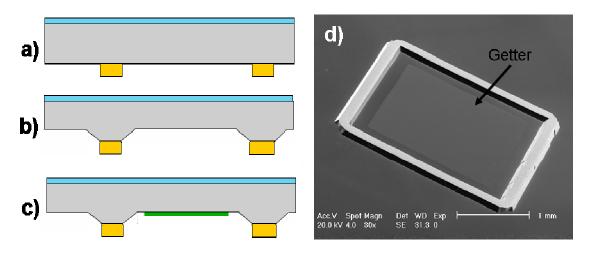

| Figure 3.3: A summary of the bond ring fabrication process where a) the bond rings are patterned and electroplated, b) the cavity is KOH etched and c) the getter is patterned and deposited. d) An SEM of a fabricated 150µm which encircles a getter.                                                                                                                                                                                                                                                                     |

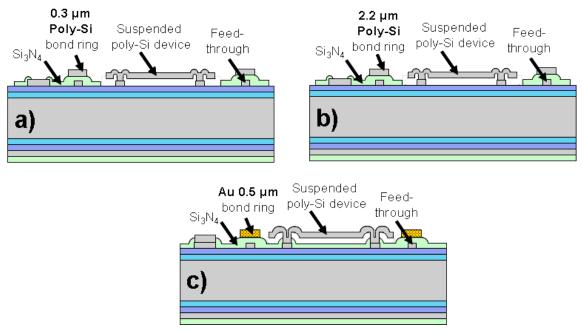

| Figure 3.4: The final structure of the device wafers for a) process #1 with a 0.3 µm thick poly-Si bond ring, b) process #2 with a 2.2 µm thick poly-Si bond ring and c) process #3 with a 0.5 µm thick Au bond ring                                                                                                                                                                                                                                                                                                        |

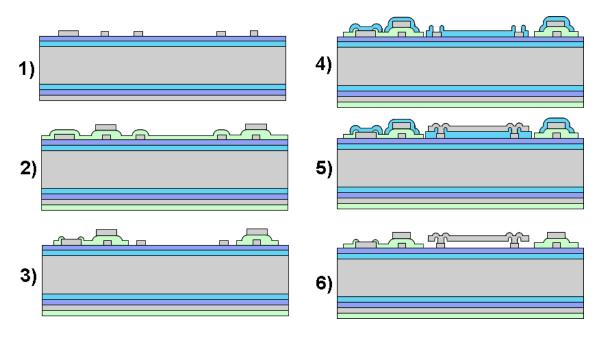

| Figure 3.5: The process steps for process 1 with 0.3 µm thick poly-Si bond rings included: 1) the deposition of dielectrics and the poly-Si used for the feed-throughs, 2) deposition of the Si <sub>3</sub> N <sub>4</sub> later that insolated the feed-throughs and deposition and patterning of the poly-Si bond ring, 3)patterning of the Si <sub>3</sub> N <sub>4</sub> layer, 4) deposition and patterning of the sacrificial layer, 5) deposition and patterning of the device layer, and 6) release of the device. |

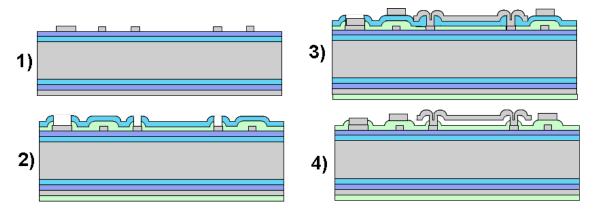

| Figure 3.6: The process steps for process 2 with 2.2 μm thick poly-Si bond rings included: 1) the deposition of dielectrics and the poly-Si used for the feed-throughs, 2) deposition and patterning of the Si <sub>3</sub> N <sub>4</sub> insulation layer and the SiO <sub>2</sub> sacrificial                                                                                                                                                                                                                            |

| layer, 5) deposition and patterning of the device layer, and 6) release of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

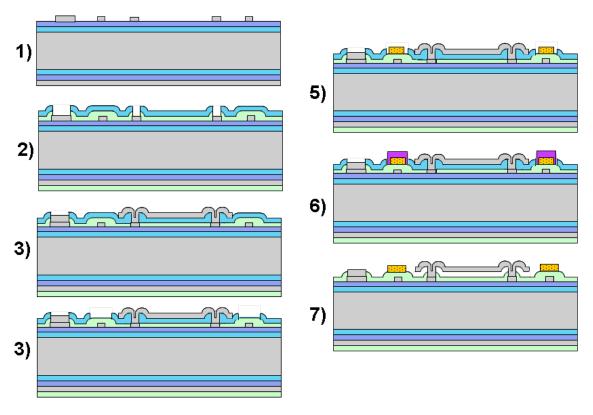

| Figure 3.7: The process steps for process 3 with 0.5 µm thick Au bond rings included: 1) the deposition of dielectrics and the poly-Si used for the feed-throughs, 2) deposition and patterning of the Si <sub>3</sub> N <sub>4</sub> insulation layer and the SiO <sub>2</sub> sacrificial layer, 3) deposition and patterning of the device layer, 4) another patterning step on the sacrificial layer, 5)deposition of the Cr/Au bond ring, 6) deposition and patterning of a photoresist protective layer and 7) release of the device followed by removal of the photoresist layer. |

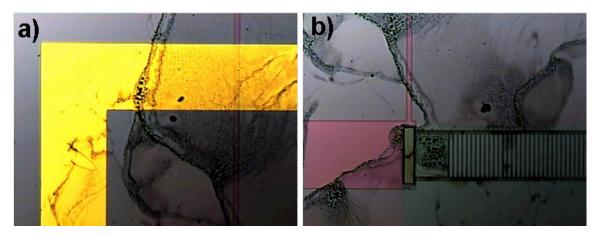

| Figure 3.8: Scum left over after the release process on a) a bond ring and b) on a device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

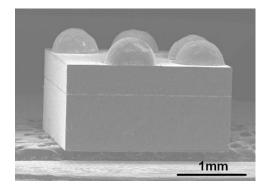

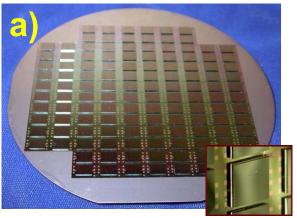

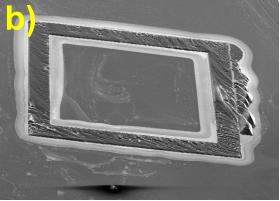

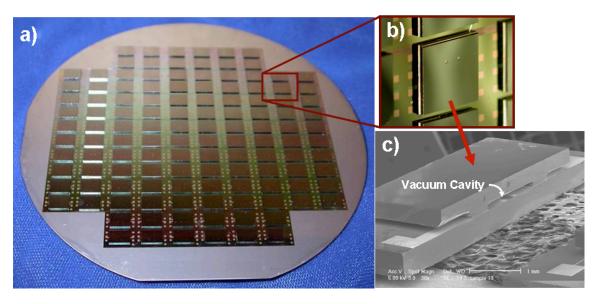

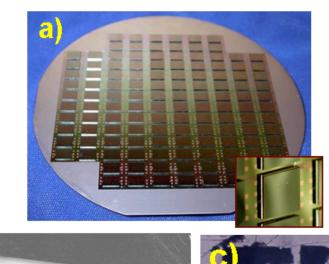

| Figure 3.9: a) A wafer with 124 vacuum encapsulated devices, b) a closer view of one of the packages and c) an SEM of a diced package showing the micro-vacuum cavity.                                                                                                                                                                                                                                                                                                                                                                                                                   |

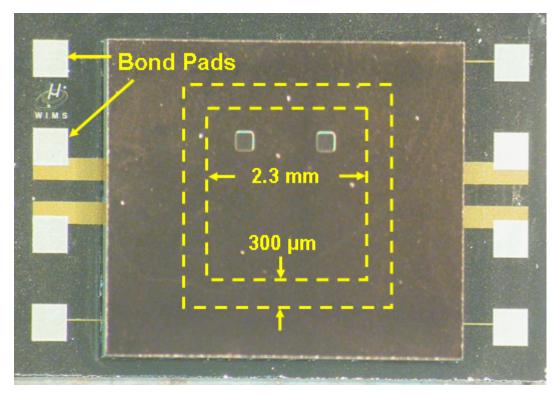

| Figure 3.10: a) A top view of one of the caps showing the bond ring dimensions and the bond pads used for interconnection.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

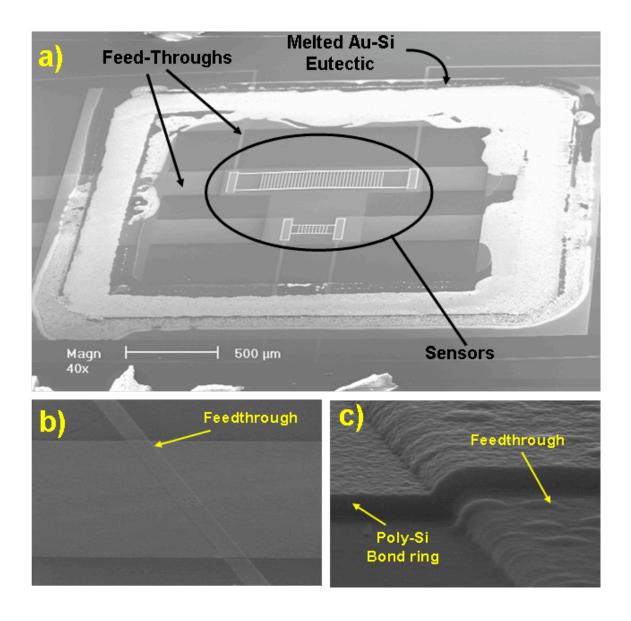

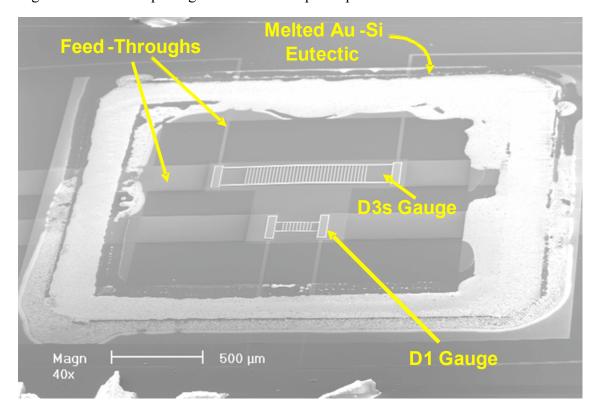

| Figure 3.11: a) A closer view where the Au-Si eutectic has been melted in order to remove the cap, b) an SEM of on of the feed-throughs running underneath a feed-through and c) a closer look at one of the feed-throughs                                                                                                                                                                                                                                                                                                                                                               |

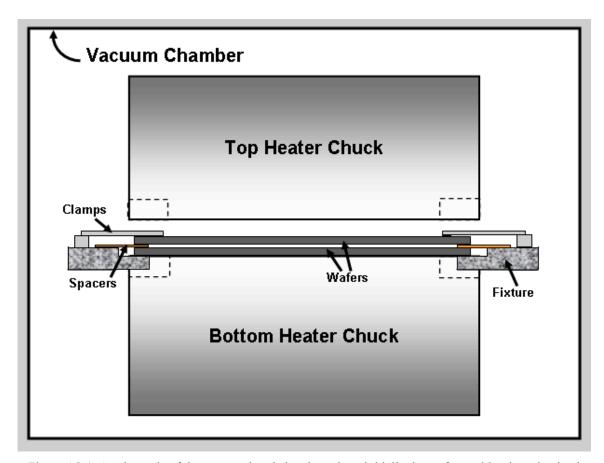

| Figure 3.12: The bond process used for vacuum encapsulation of sensors (Pirani gauges) in Chapter 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

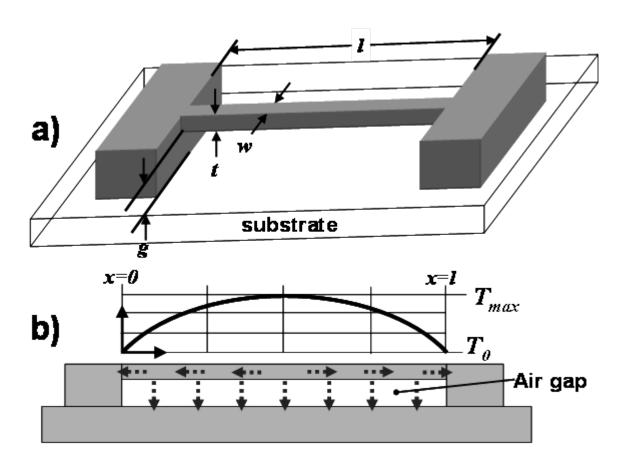

| Figure 4.1: a) A single beam micro-bridge structure, b) an illustration of the heat loss through the gas, $H_g$ vs. the heat loss through the anchors, $H_a$ , and the temperature profile across the beam.                                                                                                                                                                                                                                                                                                                                                                              |

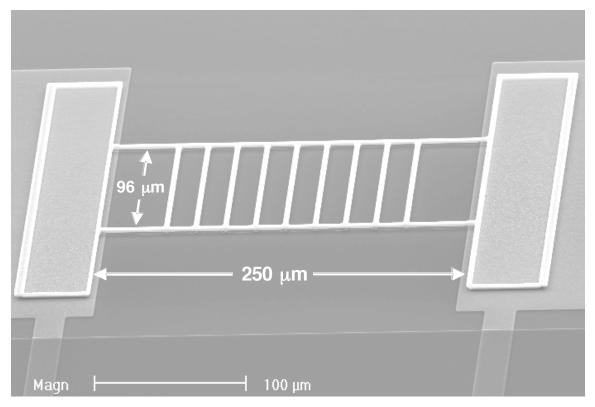

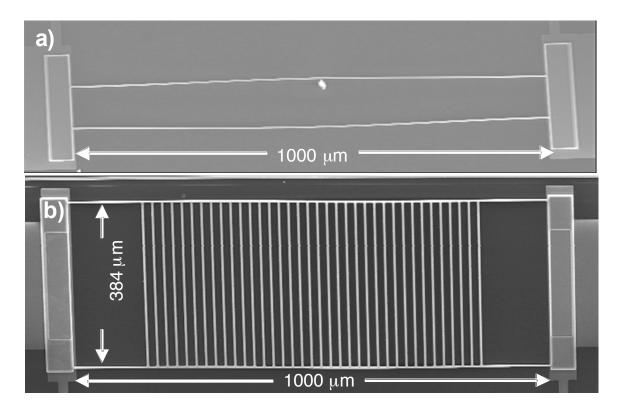

| Figure 4.2: An SEM of the design 1 (D1) ladder structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

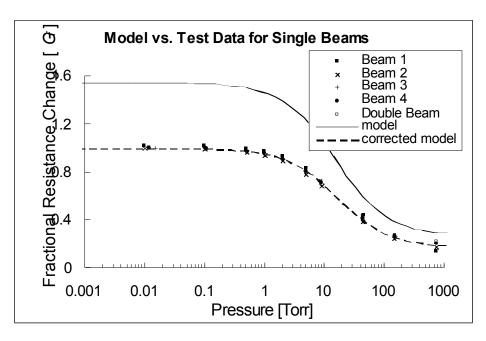

| Figure 4.3: The measured data for 4 single 4µm×2µm×250µm micro-bridges and two parallel micro-bridges as compared to the modeling data. Adding a correction factor, the modeling data maps directly over the measured data. * See the note in Table 1 on the double beam structure                                                                                                                                                                                                                                                                                                       |

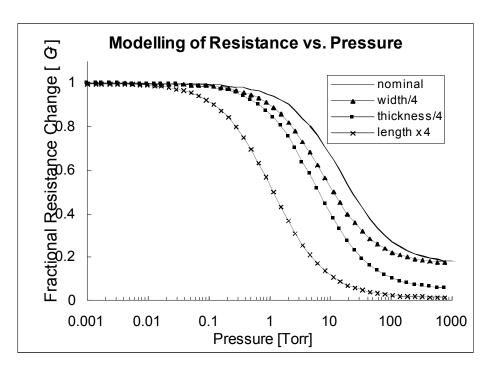

| Figure 4.4: Modeling data comparing the nominal case (a single $4\mu m \times 2\mu m \times 250\mu m$ beam) with a single beam that is a quarter of the width, a quarter of the thickness, or four times the length.                                                                                                                                                                                                                                                                                                                                                                     |

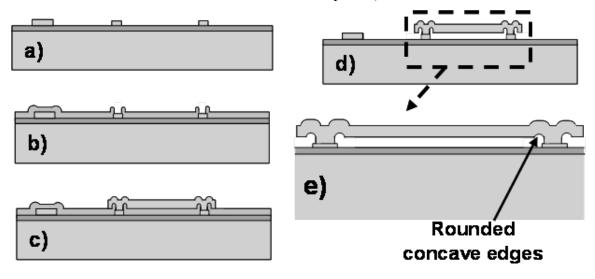

| Figure 4.5: Fabrication of the suspended beam structure consists of the deposition and patterning of a) poly-Si which forms the leads and bond pads, b) SiO <sub>2</sub> which acts as a sacrificial layer and, c) a poly-Si structural layer. d) After dicing, the devices are release in buffered hydrofluoric acid (BHF) and then soaked in methanol. e) One                                                                                                                                                                                                                          |

| possible reason for the tendency of beams to buckle upwards are the rounded concave edges created due to photolithography                                                                                                                                                                                                                                                                                       | 6       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

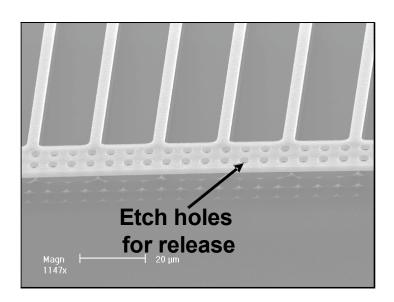

| Figure 4.6: A SEMS of one of the D4s structures showing a close up view                                                                                                                                                                                                                                                                                                                                         | 8       |

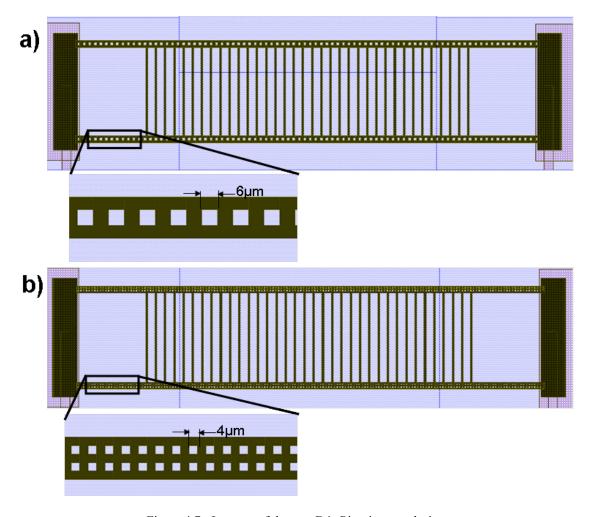

| Figure 4.7: Layouts of the two D4s Pirani gauge designs                                                                                                                                                                                                                                                                                                                                                         | 9       |

| Figure 4.8: a) Parallel 4µm×2.2µm×1000µm suspended beams which buckled along bot axis and pulled down to the substrate, and b) the design 3 ladder structure which was successfully released, only buckling in the <i>out-plane-plane</i> direction, away from the substrate.                                                                                                                                   | as<br>e |

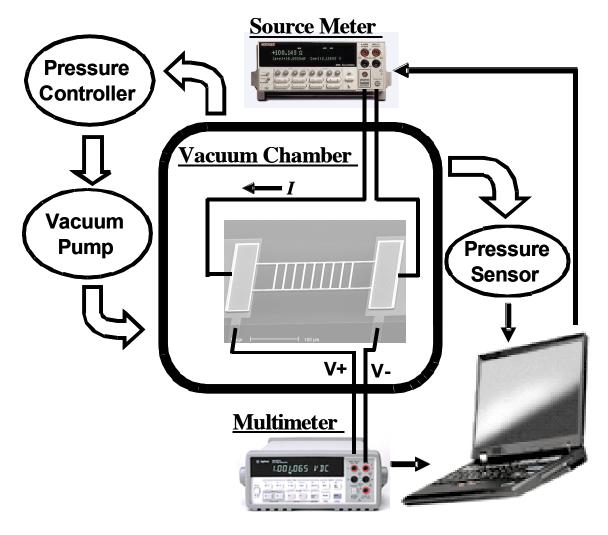

| Figure 4.9: A schematic of the test setup where the Pirani gauges were tested in a 4-point probe configuration using a source meter to provide current and a multimeter to sense the voltage drop across the Pirani gauge. The Pirani gauges were tested inside of a vacuum chamber where pressures were dialed in using a pressure controller. A separate pressure sensor was used for measuring the pressures | e       |

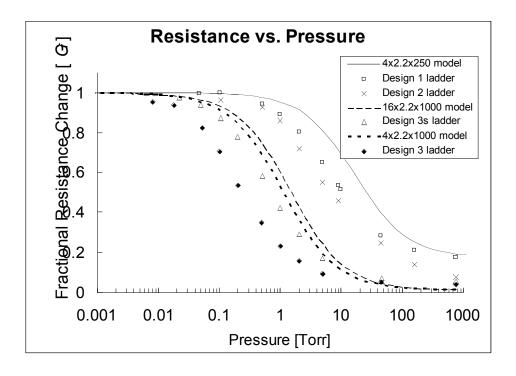

| Figure 4.10: A plot of $G_f$ vs. pressure for design 1, 2, 3s and 3 ladder structure Pirani gauges as compared to models of the $4\mu m \times 2.2\mu m \times 250\mu m$ , the $16\mu m \times 2.2\mu m \times 1000\mu m$ and $4\mu m \times 2.2\mu m \times 1000\mu m$ model for single beam Pirani gauges.                                                                                                    | 4       |

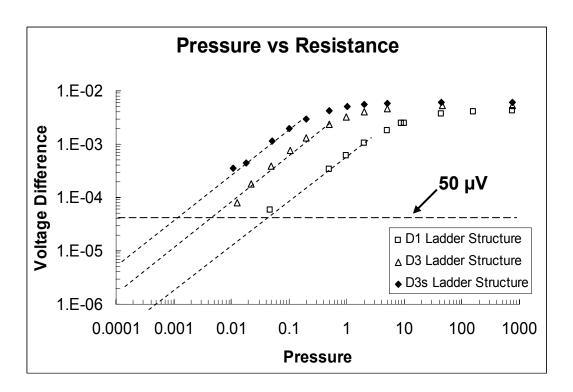

| Figure 4.11: The data for the Design 1, 3s and 3 gauges (from Figure 4.10) graphed in terms of $\Delta V$ ( $\Delta V = V_{max} - V_d$ ) vs. pressure. As illustrated, as the gauges approach the lower limits of there operation, there is a linear relation between voltage and pressure and therefore the lower limit of operation is limited by the ability to accurately measure voltage.                  | 6       |

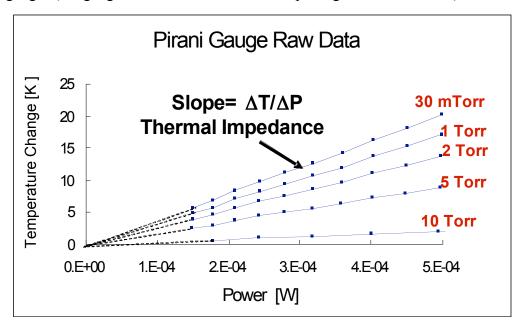

| Figure 4.12: Temperature verses power data for a D3s gauge illustrating the acquisition of thermal impedance data for pressure measurement                                                                                                                                                                                                                                                                      |         |

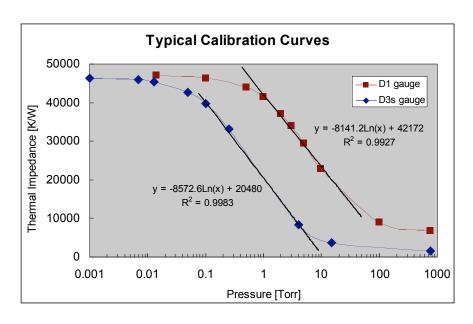

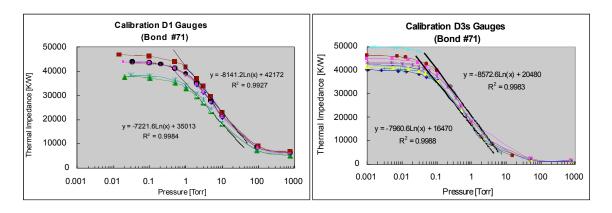

| Figure 4.13: Typical D1 and D3s calibration curves                                                                                                                                                                                                                                                                                                                                                              | 9       |

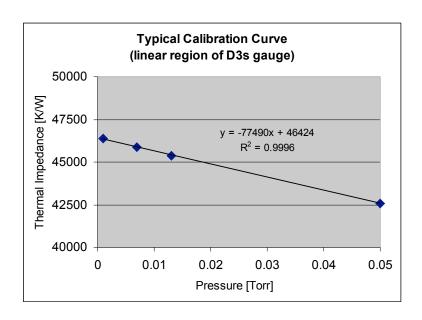

| Figure 4.14: The linear portion of the calibration curve from                                                                                                                                                                                                                                                                                                                                                   | 9       |

| Figure 4.15: Devices after de-capping                                                                                                                                                                                                                                                                                                                                                                           | 0       |

| Figure 4.16: Calibration curves across a single wafer for D1 gauges (left) and D3s gauges(right)                                                                                                                                                                                                                                                                                                                | .2      |

| Figure 4.17: Five packaged D3s Pirani gauges which were temperature cycled for reliability testing                                                                                                                                                                                                                                                                                                              | .5      |

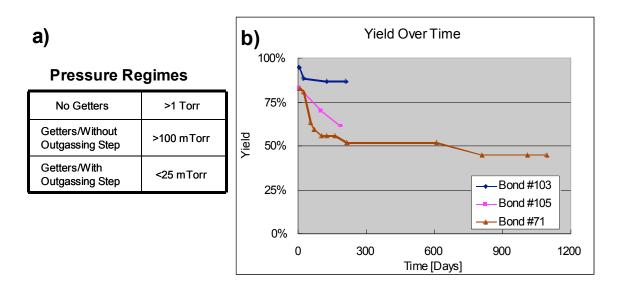

| Figure 5.1: A summary of the data presented in this chapter showing a) the different pressure regimes that were achieved, and b) the yield over time estimated across several wafers                                                                                                                                                                                                                            | .8      |

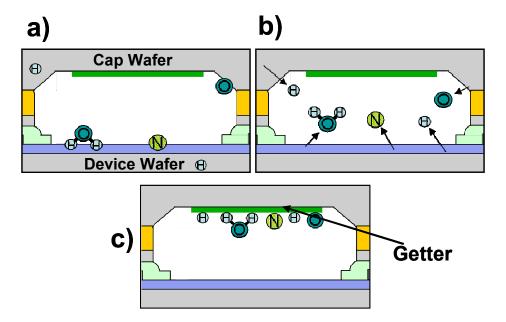

| Figure 5.2: An illustration of a) molecules which have adsorbed on the surface or into the bulk of the micro-vacuum chamber, b) molecules that desorb off of the chamber walls to increase the pressure and c) these molecules reacting with the getter to lower the package pressure. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

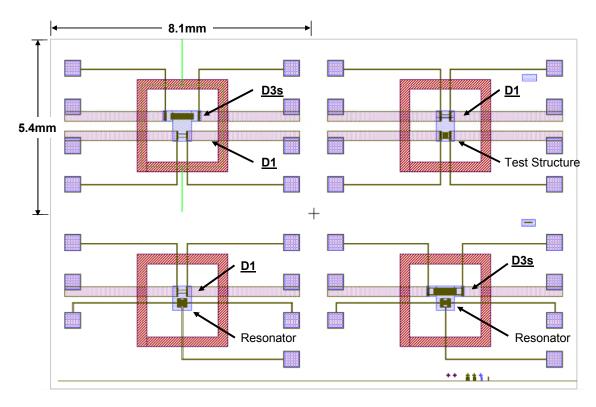

| Figure 5.3: Layout of the packaged sensors used for characterization of micro-packages.  The resonators and Test structures were not utilized in this work                                                                                                                             |

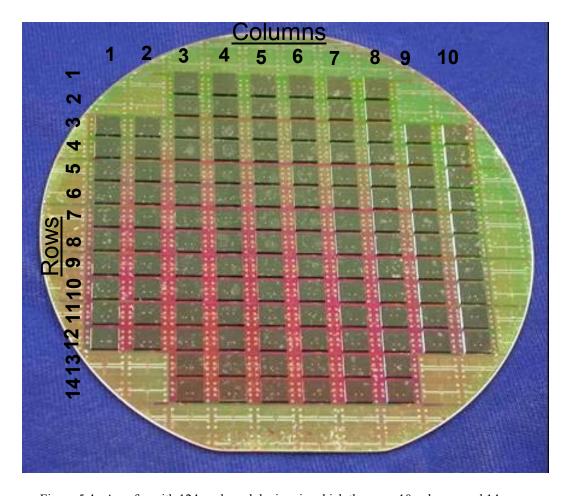

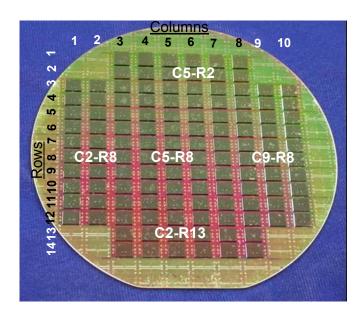

| Figure 5.4: A wafer with 124 packaged devices in which there are 10 columns and 14 rows                                                                                                                                                                                                |

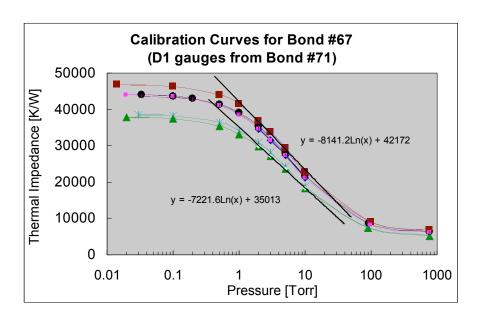

| Figure 5.5: Calibration curves for Pirani gauges from D1 gauges from bond #71.  Devices from these wafers, fabricated in the same lot, had nearly identical low current resistances and had atmospheric pressure measurements in the same range.  157                                  |

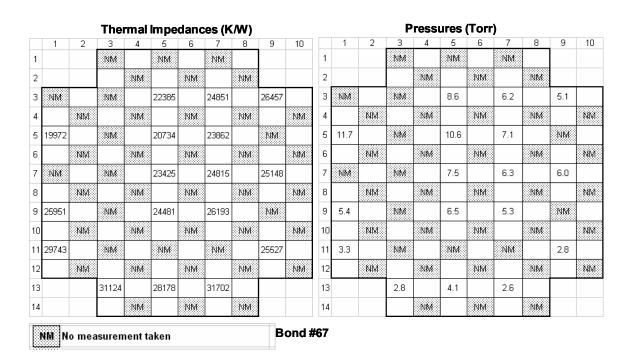

| Figure 5.6: The thermal impedance measured on gauges across bond #67 (left) and the estimated pressures corresponding to these measurements (right)                                                                                                                                    |

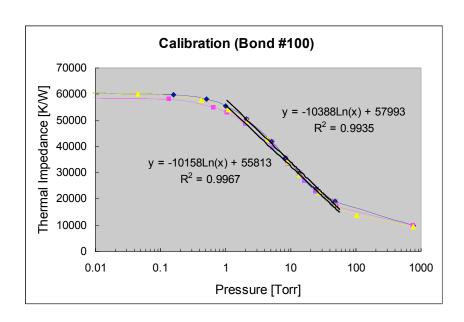

| Figure 5.7: Calibration curves for Pirani gauges from D1 gauges from bond #100. The devices used for calibration were taken from the top, bottom and center of the wafer and are highlighted in figure 4.11                                                                            |

| Figure 5.8: The thermal impedance measured on gauges across bond #100 (left) and the estimated pressures corresponding to these measurements (right)                                                                                                                                   |

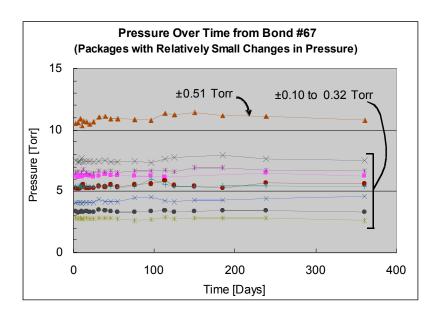

| Figure 5.9: Pressures determined from the measured thermal impedances over time using the calibration curves in Figure 5.5 to determine pressures. All of these devices had ±0.5 Torr or less pressure fluctuation over time                                                           |

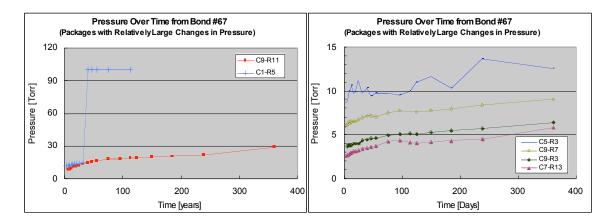

| Figure 5.10: Pressures determined from the measured thermal impedances over time using the calibration curves in Figure 5.5 to determine pressures. All of these devices had a >3 Torr pressure change over time                                                                       |

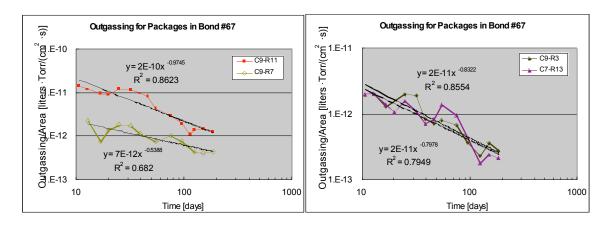

| Figure 5.11: The outgassing/area for 4 packages from bond #67                                                                                                                                                                                                                          |

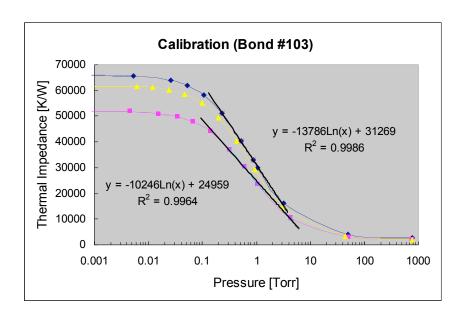

| Figure 5.12: Calibration curves for Pirani gauges from D3s gauges from bond #103. The devices used for calibration were taken from the top, bottom and center of the wafer and are highlighted in Figure 5.13.                                                                         |

| Figure 5.13: The thermal impedance measured on gauges across bond #103 (left) and the estimated pressures corresponding to these measurements (right)                                                                                                                                  |

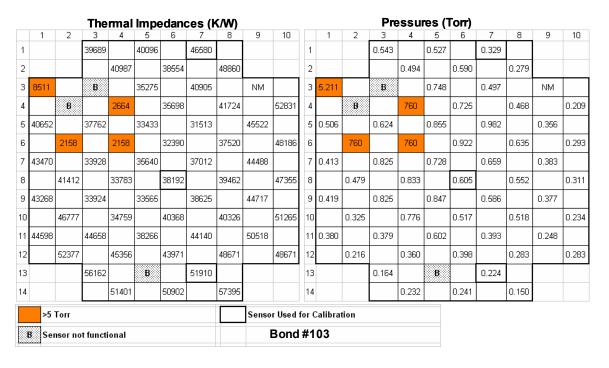

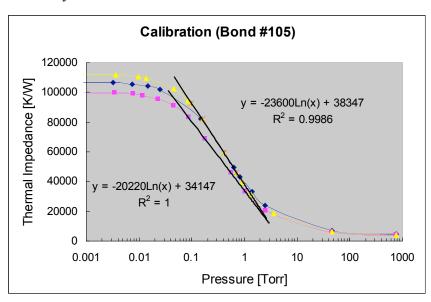

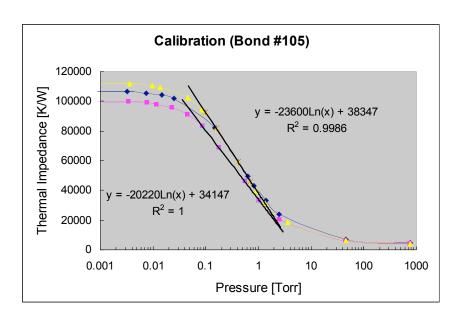

| Figure 5.14: Calibration curves for Pirani gauges from D3s gauges from bond #105. The devices used for calibration were taken from the top, bottom and center of the wafer and are highlighted in Figure 5.15                                                                          |

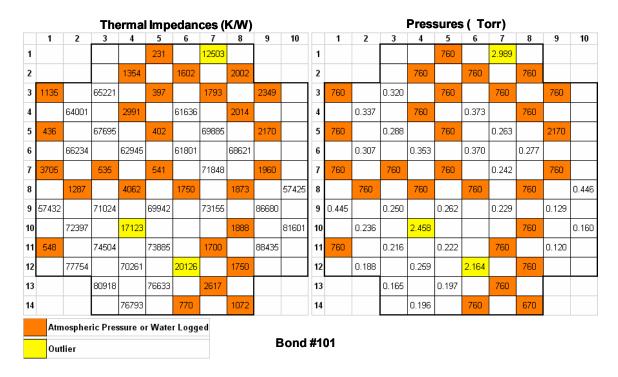

| Figure 5.15: The thermal impedance measured on gauges across bond #105 (left) and the estimated pressures corresponding to these measurements (right)                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

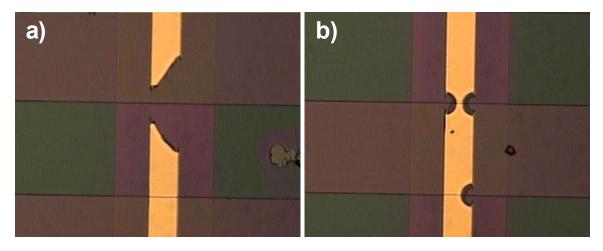

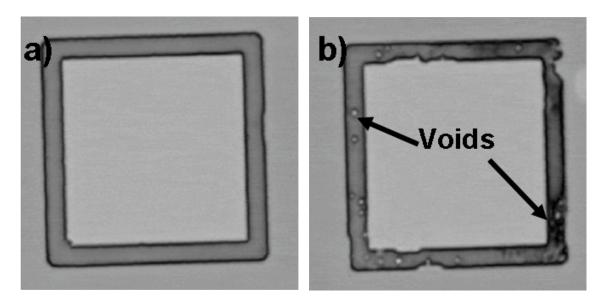

| Figure 5.16: a) A bond ring which was completely compromised and b) a bond ring which was partially compromised on the device wafer substrate of bond #105 166                                                                                                                                                                         |

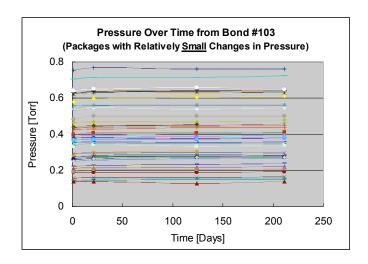

| Figure 5.17: Packages from bond #103 which demonstrated changes of pressure from ±1 to ±25mTorr. These pressures were determined from the measured thermal impedances on bond #103 over time using the calibration curves in Figure 5.12167                                                                                            |

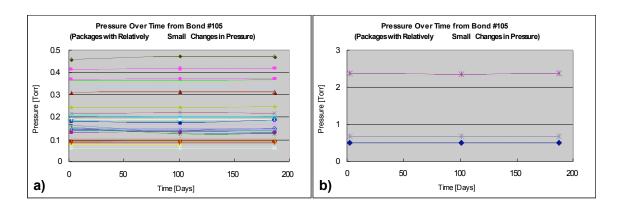

| Figure 5.18: Packages from bond #105 which demonstrated changes of pressure from ±1 to ±25mTorr. These pressures were determined from the measured thermal impedances on bond #105 over time using the calibration curves in Figure 5.14 167                                                                                           |

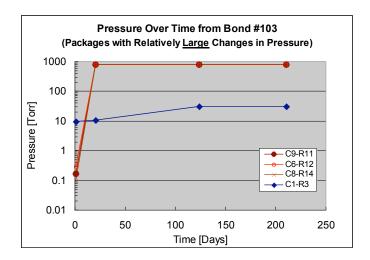

| Figure 5.19: Packages with relatively large changes in pressure from bond #103. These pressures were determined from the measured thermal impedances on bond #103 over time using the calibration curves in Figure 5.12                                                                                                                |

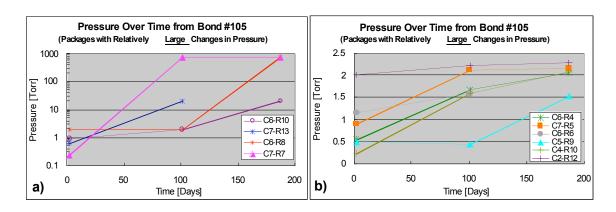

| Figure 5.20: Packages with relatively large changes in pressure from bond #105. These pressures were determined from the measured thermal impedances on bond #105 over time using the calibration curves in Figure 5.14                                                                                                                |

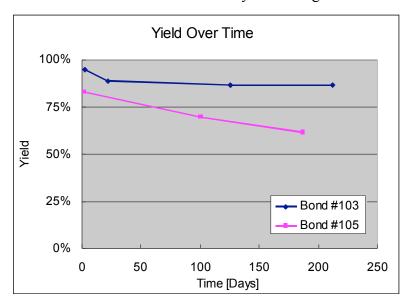

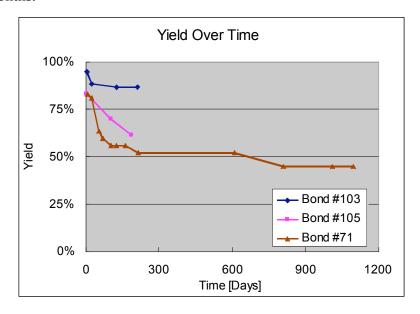

| Figure 5.21: The yield over time for bond #103 and #105                                                                                                                                                                                                                                                                                |

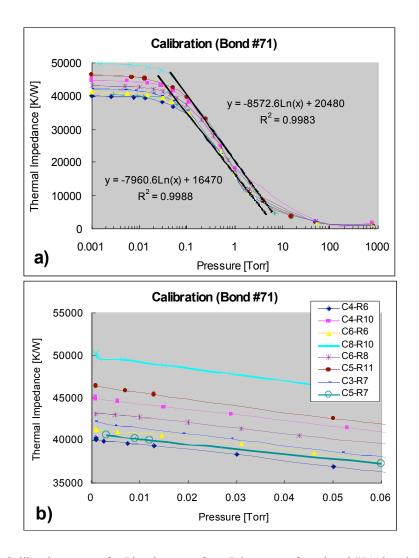

| Figure 5.22: Calibration curves for Pirani gauges from D3s gauges from bond #71 showing a) the entire plot on a log-linear plot and b) the linear portion of each of the 8 calibrated Pirani gauges.                                                                                                                                   |

| Figure 5.23: The thermal impedance measured on gauges across bond #71 and the estimated pressures corresponding to several packages which were de-capped and calibrated                                                                                                                                                                |

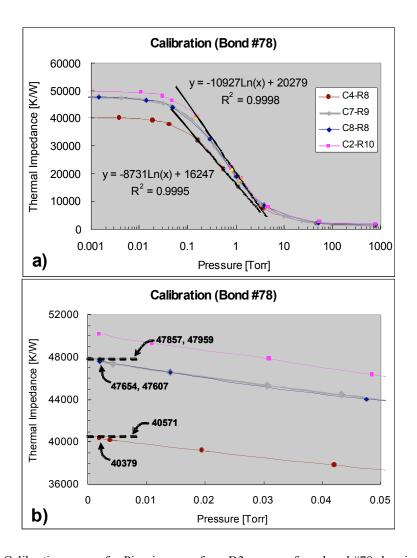

| Figure 5.24: Calibration curves for Pirani gauges from D3s gauges from bond #78 showing a) the entire plot on a log-linear plot and b) the linear portion of each of the 4 calibrated Pirani gauges. The dotted lines show the measured thermal impedance while the device was still capped for C4-R8, C7-R9 and C8-R8                 |

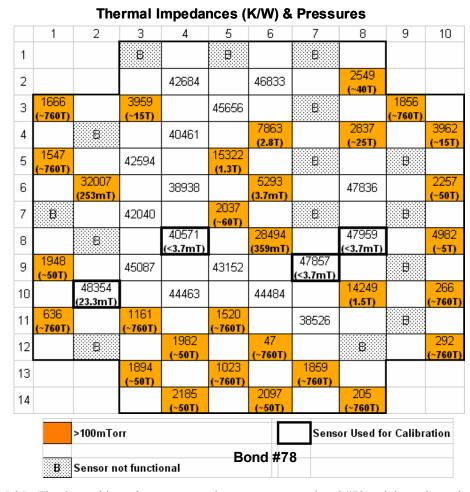

| Figure 5.25: The thermal impedance measured on gauges across bond #78 and the estimated pressures corresponding to several packages which were de-capped and calibrated                                                                                                                                                                |

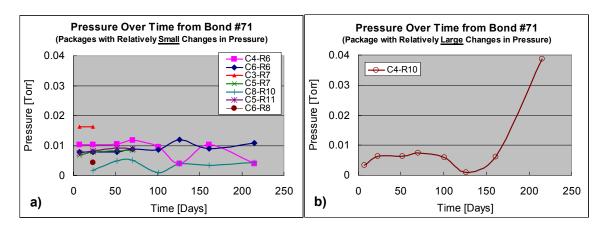

| Figure 5.26: Graphs of pressures over time for packages which were individually decapped and calibrated where Figure 5.22 shows the calibration curves. a) Shows packages with changes in pressure over time of ±2 mTorr or less and b) shows one package in which the pressure increased to around 40 mTorr at the 215 day of testing |

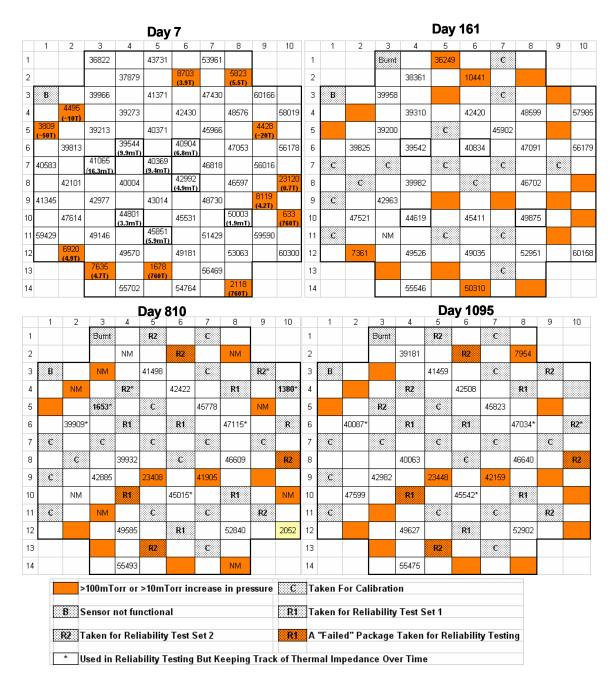

| on day 7, 161, 810 and 1095. The legend at the bottom of the figure shows which packages failed over time (increased by >5mTorr), which packages were taken for calibration and which packages where taken for reliability testing                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

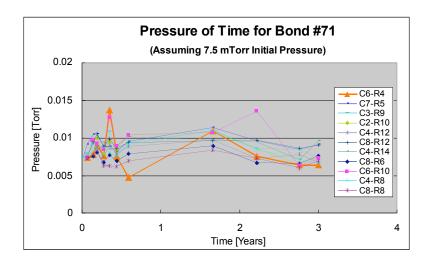

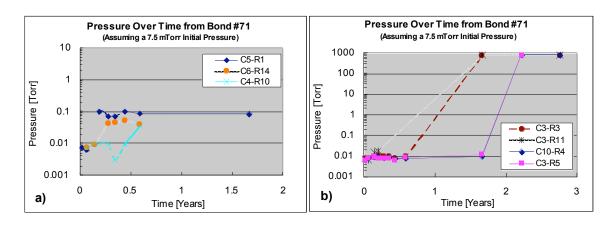

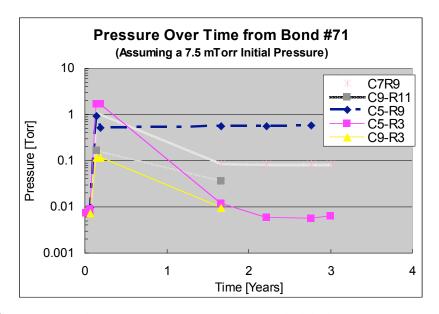

| Figure 5.28: The estimated pressure over time for 11 packages which maintained pressures to with in ±5 mTorr over 3 years of testing                                                                                                                        |

| Figure 5.29: The estimated pressure over time for 7 packages which had significant changes in pressure over time                                                                                                                                            |

| Figure 5.30: The estimated pressure over time for 5 packages which had an initial increase then decrease in pressure                                                                                                                                        |

| Figure 5.31: The yield over time for bond #71                                                                                                                                                                                                               |

| Figure 5.32: Five packages which were taken out of the controlled environment (after 215 days). Large pressure fluctuations were observed                                                                                                                   |

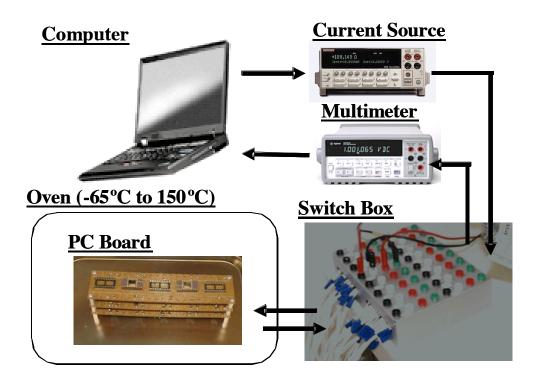

| Figure 5.33: Packaged vacuum sensors were tested inside of an oven using a Labview program, a current source, a multimeter and a switch box to test each sensor during and ever ramping cycles                                                              |

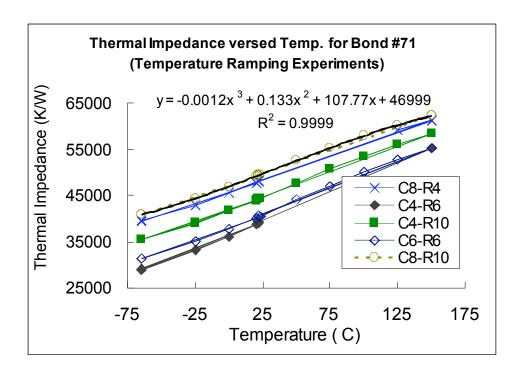

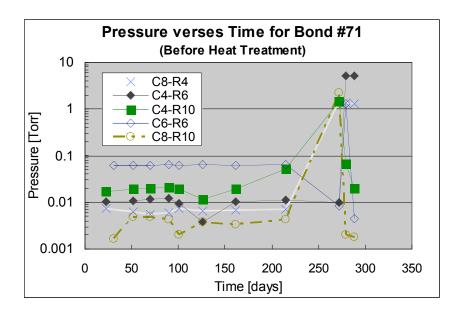

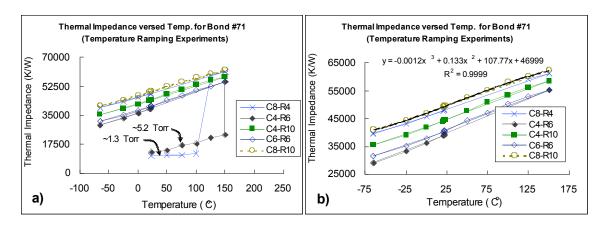

| Figure 5.34: Thermal Impedance vs. temperature for the 5 packages taken through high/low temperature exposure tests. a) Shows a plot of each data point in the temperature ramping and b) shows a plot without the initial data points for C8-R4 and C4-R6. |

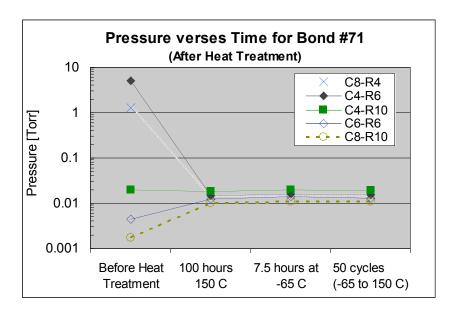

| Figure 5.35: A summary of the results through various heat treatment steps                                                                                                                                                                                  |

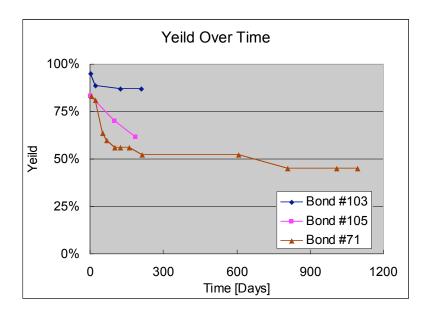

| Figure 5.36: A summary of the yields over time for bonds #103, #105 and #71189                                                                                                                                                                              |

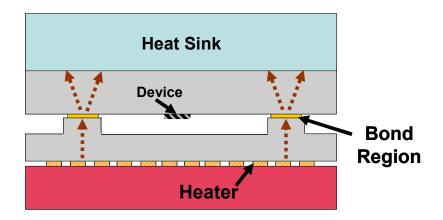

| Figure 6.1: A schematic illustrating the concept behind <i>differential localized heating</i> where heat gets pulled through the bond rings towards the heat sink, heating up the bond ring while keeping the device relatively cool                        |

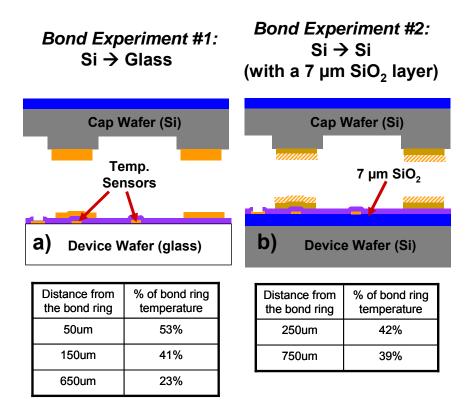

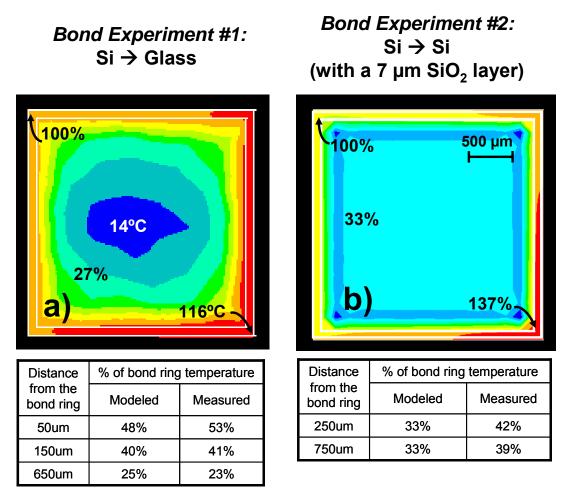

| Figure 6.2: A schematic of the bond experiments conducted in this chapter along with the measured temperatures relative to the bond ring temperatures for each of these bond experiments.                                                                   |

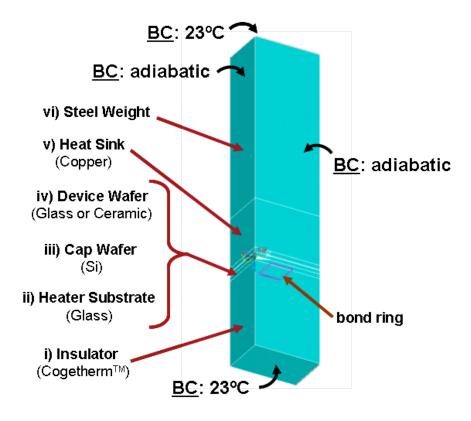

| Figure 6.3: Shows the layers in the test setup which will be described in Section 6.3194                                                                                                                                                                    |

| Figure 6.4: The 1-D representation of how heat flows from the heater through the bond rings to the heat sink.                                                                                                                                               |

| Figure 6.5: The structure of the model used for modeling the test setup                                                                                                                                                                                     |

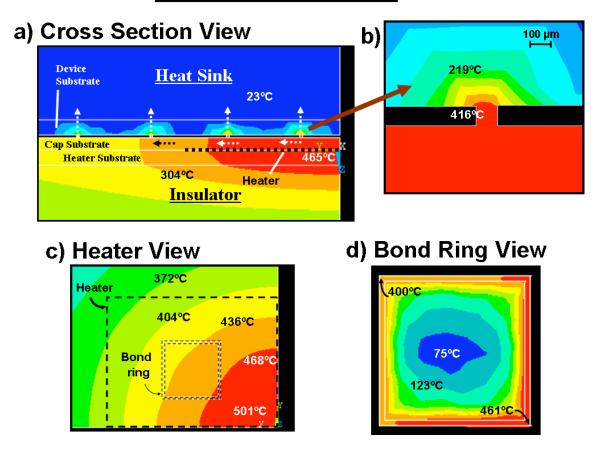

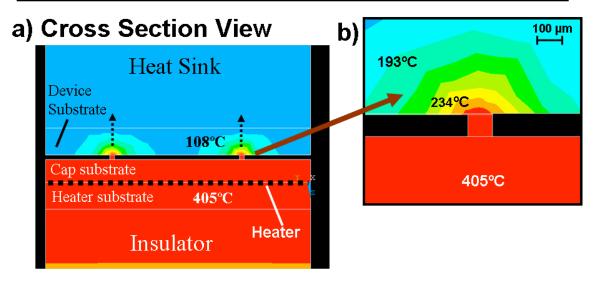

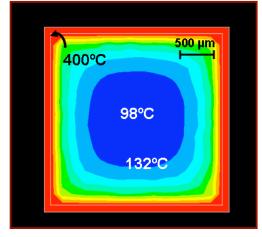

| Figure 6.6: Results from the "test setup model," for a <i>Si to glass bond</i> showing a) a cross-section view showing how the heat flows into the heat sink, b) a closer look at the cross-section of the bond ring, c) a section of the heater, and d) the heat distribution across the bond ring and inside of the bond ring                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

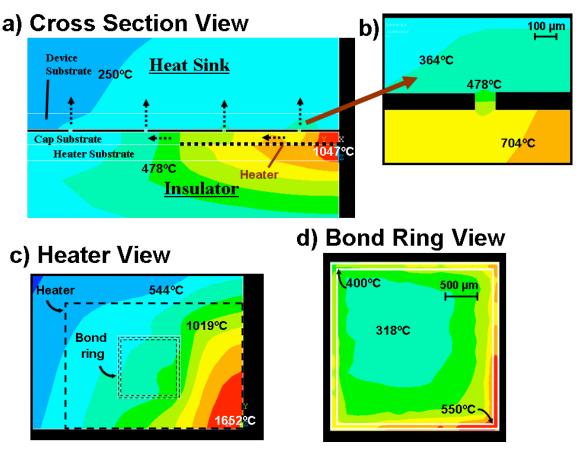

| Figure 6.7: Results from the "test setup model," for a <i>Si to Si bond</i> showing a) a cross-section view showing how the heat flows into the heat sink, b) a closer look at the cross-section of the bond ring, c) a section of the heater, and d) the heat distribution across the bond ring and inside of the bond ring                                                                                                                                                                                    |

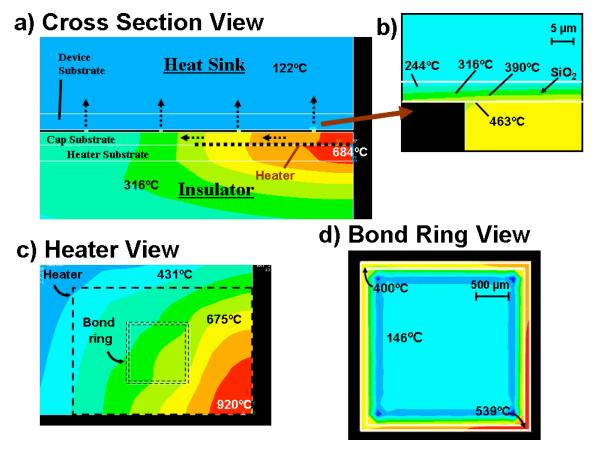

| Figure 6.8: Results from the "test setup model," for a <i>Si to Si bond with a 7 μm thick SiO</i> <sub>2</sub> <i>layer</i> showing a) a cross-section view showing how the heat flows into the heat sink, b) a closer look at the cross-section of the bond ring, c) a section of the heater, and d) the heat distribution across the bond ring and inside of the bond ring 203                                                                                                                                |

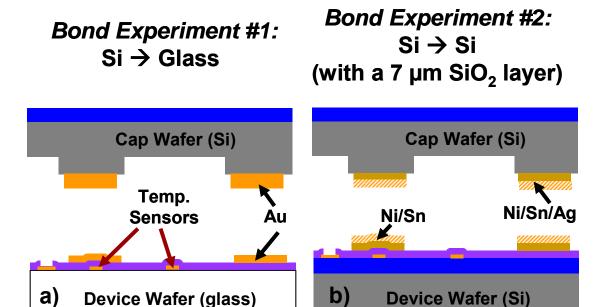

| Figure 6.9: Schematics of the cap and device wafers fabricated for bond tests for a) the Si to glass bonding process and b) the Si to Si wafer with 7 µm of SiO <sub>2</sub> 207                                                                                                                                                                                                                                                                                                                                |

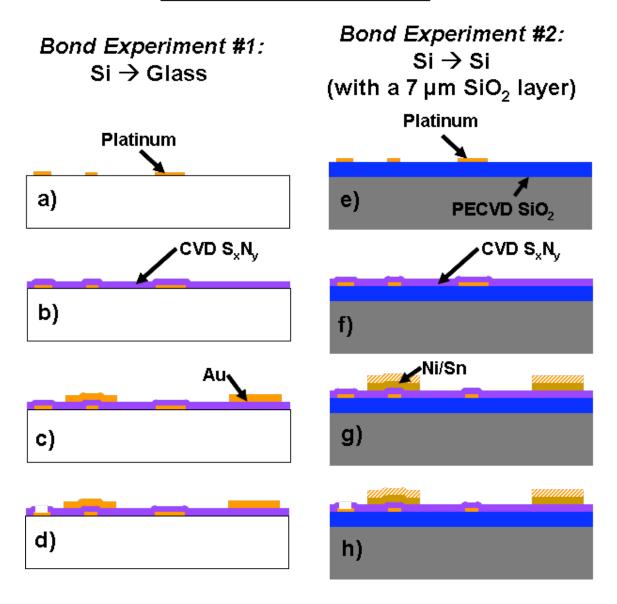

| Figure 6.10: The fabrication process for cap wafers for a-d) Si to glass bonds and e-h) Si to Si bonds with a 7 µm thick oxide layer                                                                                                                                                                                                                                                                                                                                                                            |

| Figure 6.11: The fabrication processes for the cap and device wafers for a-d) Si to glass bonds and e-h) Si to Si bonds with a 7 µm thick oxide layer                                                                                                                                                                                                                                                                                                                                                           |

| Figure 6.12: Schematics showing cross-sections of the test setup                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 6.13: A schematics showing how the temperature sensors were laid out across the wafer.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 6.14: a) The aligned cap and device wafers which were held together using clamps, b) a closer look at the edge of these aligned wafers showing how the diced away portion of the cap wafer allows access to bond pads on the device wafer that run to temperature sensors, and c) the aligned wafers that sit on top of the copper heat sink. PCBs on either side of the wafer pair were wire bonded to the bond pads on the device wafer in order to access the temperature sensors near the bond ring. |

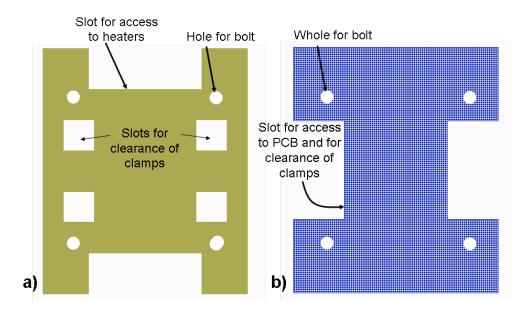

| Figure 6.15: The layout of the a) copper heat sink and b) Cogetherm <sup>TM</sup> insulator plate.                                                                                                                                                                                                                                                                                                                                                                                                              |

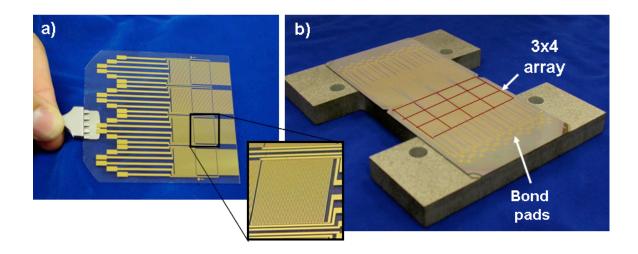

| Figure 6.16: a) A heater substrate and b) two heater substrates placed on the Cogetherm plate.                                                                                                                                                                                                                                                                                                                                                                                                                  |

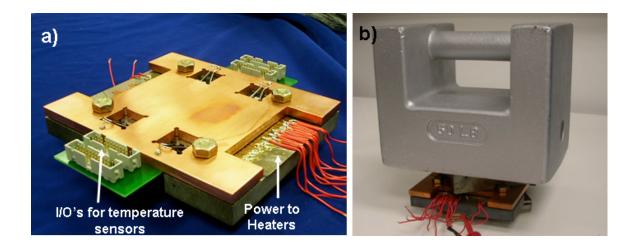

| Figure 6.17: a) The entire assembly where the copper plate and the Cogetherm <sup>TM</sup> sandwiched the heaters and the wafer pair and, b) a $1 \times 4 \times 4$ " steel block and a 50lb weight on top of this assembly                                                                                                                                                                                                                                                                                    |

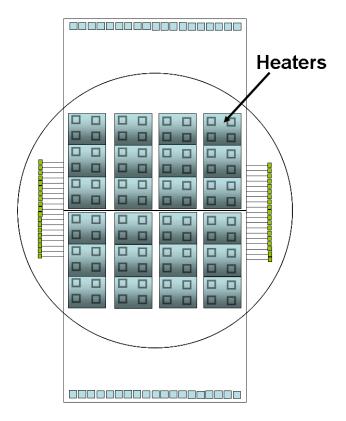

| Figure 6.18: A schematic showing how the heaters lined up with the bond rings across the wafer                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

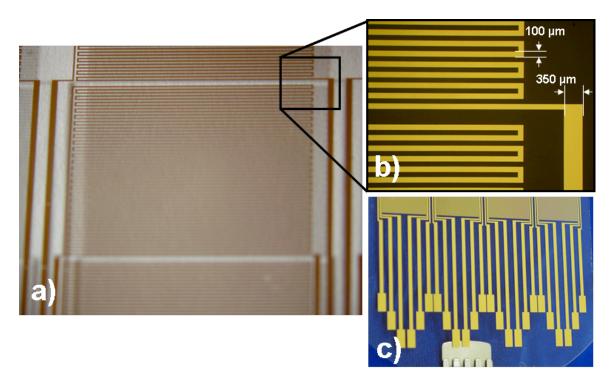

| Figure 6.19: Shown is a) a heater, b) a closer look at some of 100 μm wide coils in one of these heaters and the 350 μm wide lead running from the heater, and c) the portion of the leads running to the bond ring which were 1000 μm wide                                                                                                      |

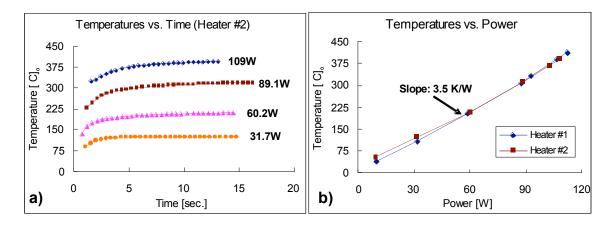

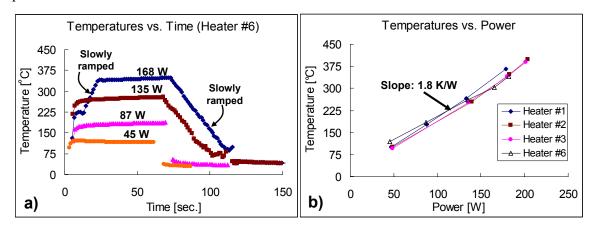

| Figure 6.20: a) The average measured temperature across one of the heaters for different powers and b) the temperature vs. power (after holding power for 10 seconds) for two different heaters that were tested in bond experiment #1                                                                                                           |

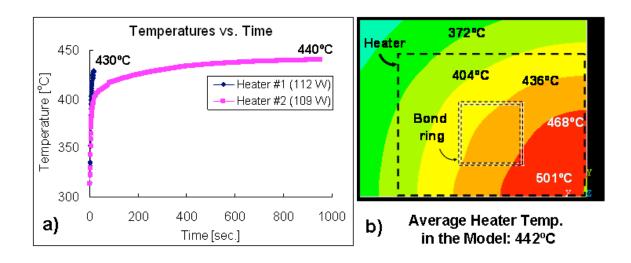

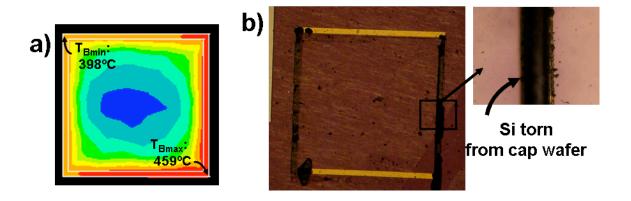

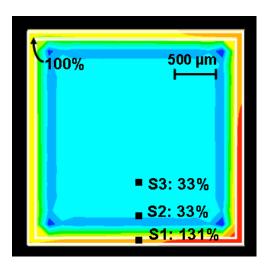

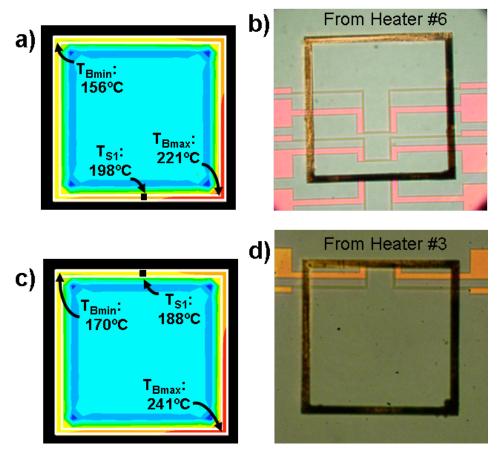

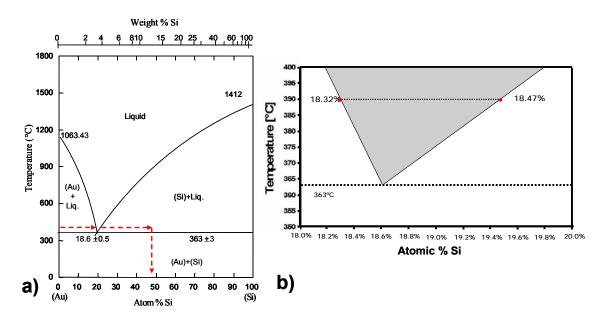

| Figure 6.21: a) The temperature vs. time for two heaters that failed with applied powers of 112 and 109 W at temperatures of 430°C and 440°C respectively and, b) the case which was modeled in Section 6.1.3.1 where there was an average temperature of 442°C for <i>bond experiment #1</i>                                                    |

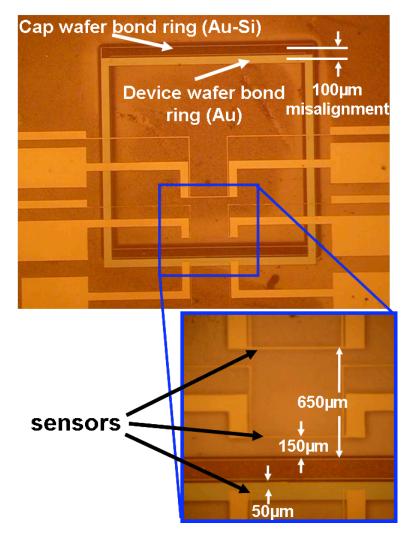

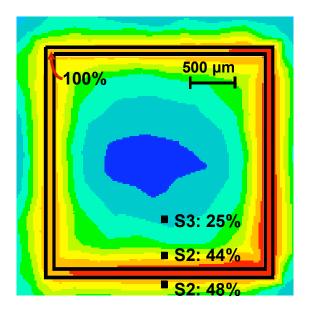

| Figure 6.22: The aligned cap and device wafers as seen through the backside of the glass device wafer in <i>bond experiment #1</i> . As illustrated, these bond rings were misaligned vertically by 100 μm resulting in the temperature sensors being 50, 150 and 650 μm from the edge of the bond ring                                          |

| Figure 6.23: The modeled temperature profile showing the temperatures relative to the minimum bond ring temperatures (R <sub>BR</sub> ) at different distances from the bond ring for bond experiment #1                                                                                                                                         |

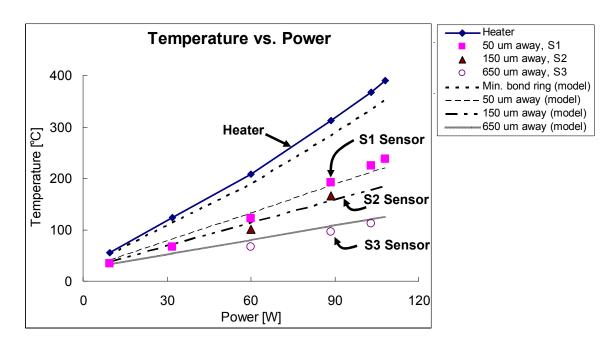

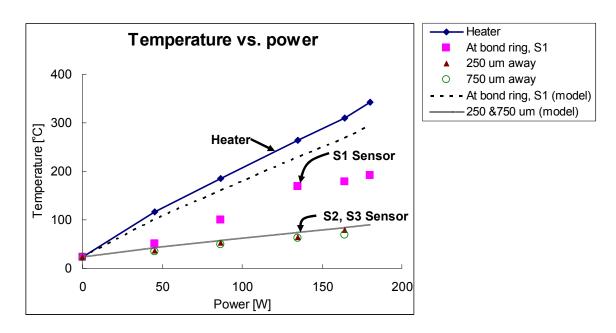

| Figure 6.24: A comparison of the measured heater temperature and the temperatures at different distances from the bond ring to the modeling results for <i>bond experiment</i> #1                                                                                                                                                                |

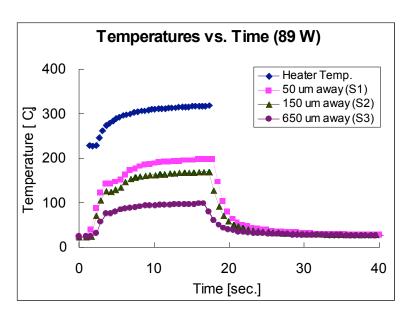

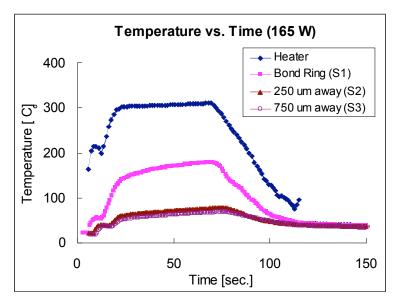

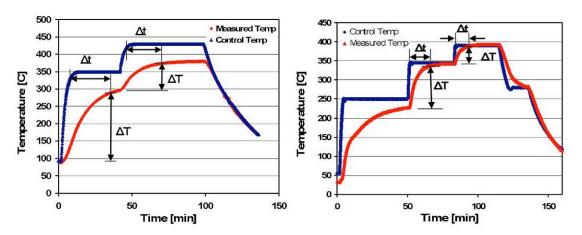

| Figure 6.25: The temperature over time for one of the temperature ramping tests from bond experiment #1 showing the temperatures at each one of the temperature sensors.                                                                                                                                                                         |

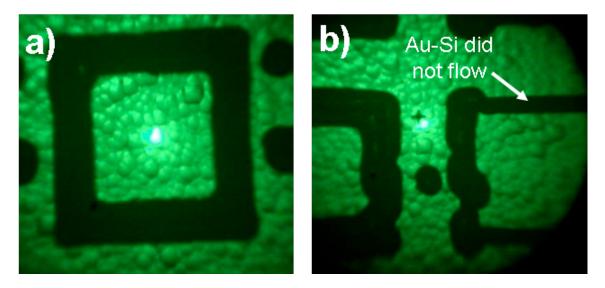

| Figure 6.26: a) Modeling results for the case where the average heater temperature is 440°C and b) one of the bond rings under heater #2 after the cap and device wafers were pride apart after the bond experiments                                                                                                                             |

| Figure 6.27: a) The average measured temperature across one of the heaters for different powers and b) the temperature vs. power (after holding power for 10 seconds) for four different heaters that were tested for <i>bond experiment</i> #2                                                                                                  |

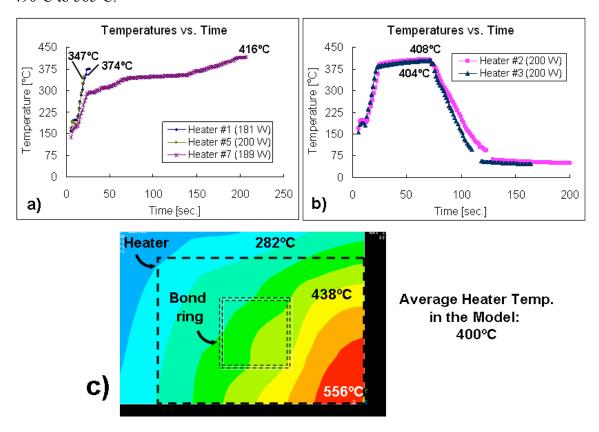

| Figure 6.28: a) The temperature vs. time for three heaters that failed with applied powers of 181, 200 W and 189 W at temperatures of 374, 357 and 416°C respectively, b) two heaters that did not fail with applied powers of 200W and, c) a plot of the modeled case from Section 6.1.3.3 with an assumed average heater temperature was 400°C |

| Figure 6.29: The modeled temperature profile showing the temperatures relative to the minimum bond ring temperatures ( $R_{BR}$ ) at different distances from the bond ring for bond experiment #2                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.30: A comparison of the measured heater temperature and the temperatures at different distances from the bond ring to the modeling results for the experiment #2 bond tests                                                                                                                                                                                        |

| Figure 6.31: The temperature over time for one of the temperature ramping tests from bond experiment #2 showing the temperatures at each one of the temperature sensors.                                                                                                                                                                                                    |

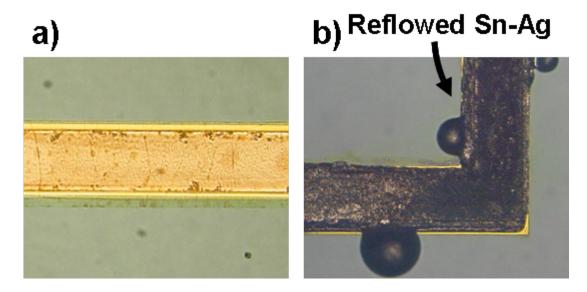

| Figure 6.32: a) A Ni/Sn film on the device wafer which was not heated up, showing no evidence of Sn-Ag intermixing, and b) another bond ring which has darkened and flowed seeming to indicate Sn-Ag intermixing and viscous flow                                                                                                                                           |