# Novel Amorphous Silicon Thin-Film Transistor Structure for Flat-Panel Displays

## By

### Alex Kuo

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2008

### **Doctoral Committee:**

Professor Jerzy Kanicki, Chair Professor Stephen R. Forrest Professor Anthony H. Francis Professor Fred L. Terry Jr. Assistant Professor Jamie D. Phillips

# © Alex Kuo

2008

All rights reserved.

| т |   |                | 1   | •   | ٠,٠  |   |   |

|---|---|----------------|-----|-----|------|---|---|

| ı | ) | $e^{\epsilon}$ | 111 | ica | at 1 | n | n |

To my parents Florence and Tzu-Lien, and sisters Michelle and Claudia.

### Acknowledgements

I would like extend my sincere gratitude to my thesis advisor Professor

Jerzy Kanicki for his support and guidance throughout my research. I would

like to thank my doctoral committee members, for their valuable reviews

and feedbacks for my dissertation. A special appreciation goes out to

Professor Anthony Francis, of whom I worked with in my earlier research

career. I would like to thank all MNF staffs for their advices. I am very

grateful for Dr. Tae-Kyoung Won of AKT America, Inc. for his help in the

deposition of the semiconductor materials used in my dissertation.

I am grateful of the financial support provided by the National Science Foundation IGERT Program, AKT America Inc., and Defense Advanced Research Project Agency.

I would like to thank my parents, sisters, friends, and colleagues for their support and encouragement throughout my career. Lastly, I would like to thank Katie for her love and encouragement.

# Table of Contents

| Dedic  | ation   |                                                     | ii   |

|--------|---------|-----------------------------------------------------|------|

| Ackno  | owledg  | ements                                              | iii  |

| List o | f Figur | es                                                  | vii  |

| List o | f Table | PS                                                  | xii  |

| List o | f Abbro | eviations/Acronyms                                  | xiii |

| Gloss  | ary     |                                                     | xiv  |

| Abstr  | act     |                                                     | xv   |

|        |         |                                                     |      |

| Chap   | ter     |                                                     |      |

| 1.     | Intro   | oduction                                            |      |

|        | 1.1.    | Background and Motivation                           | 1    |

|        | 1.2.    | Organization of Dissertation.                       | 5    |

| 2.     | Fabr    | ication and Characterization                        |      |

|        | 2.1.    | Thin-Film Etching.                                  | 10   |

|        |         | 2.1.1. Mechanism and Terminology                    | 10   |

|        |         | 2.1.2. Wet Etch                                     | 15   |

|        |         | 2.1.3. Dry Etch                                     | 18   |

|        |         | 2.1.4. Dry and Wet Etching Non-Idealities           | 22   |

|        |         | 2.1.5. Etch Process Control.                        | 25   |

|        | 2.2.    | Fabrication Process.                                | 27   |

|        |         | 2.2.1. Gate Metal Sputtering and Patterning         | 28   |

|        |         | 2.2.2. Plasma Enhanced Chemical Vapor Deposition    | 30   |

|        |         | 2.2.3. Island Patterning.                           | 31   |

|        |         | 2.2.4. Gate Via Patterning                          | 32   |

|        |         | 2.2.5. Source/Drain Metal Sputtering and Patterning | 33   |

|        |         | 2.2.6. Back Channel Etch and Thermal Annealing      | 34   |

|    | 2.3.   | Amorphous Silicon TFT Characterizations.                       | 36  |

|----|--------|----------------------------------------------------------------|-----|

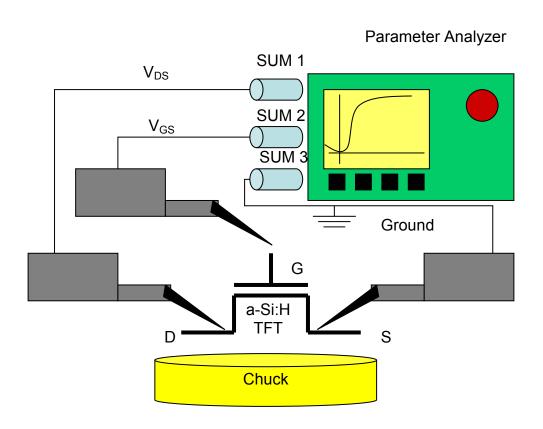

|    |        | 2.3.1. Measurement Setup                                       | 36  |

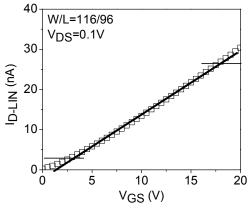

|    |        | 2.3.2. Parameter Extraction – Linear Fit                       | 37  |

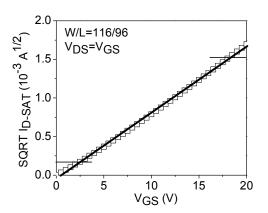

|    |        | 2.3.3. Parameter Extraction – Quadratic Fit                    | 39  |

|    |        | 2.3.4. Conductance Method                                      | 40  |

|    |        | 2.3.5. Subthreshold Swing and Off-Current Extraction           | 41  |

|    |        | 2.3.6. Intrinsic Characteristic Extraction.                    | 42  |

| 3. | Chanı  | nel Tailoring                                                  |     |

|    | 3.1.   | Introduction                                                   | 48  |

|    | 3.2.   | Traditional Amorphous Silicon TFT Performance                  | 51  |

|    | 3.3.   | Parameter Extraction Methodology.                              | 53  |

|    | 3.4.   | Result and Discussion.                                         | 60  |

|    | 3.5.   | Conclusion.                                                    | 64  |

| 4. | Back   | Channel Etch Chemistry                                         |     |

|    | 4.1.   | Introduction                                                   | 69  |

|    | 4.2.   | a-Si:H TFT Fabrication.                                        | 71  |

|    | 4.3.   | Result and Discussion.                                         | 74  |

|    |        | 4.3.1. Impact of the Gate and Source/Drain Metal Wet Etch      | 74  |

|    |        | 4.3.2. Impact of the a-Si:H Film Etching Depth                 | 75  |

|    |        | 4.3.3. Impact of the Back Channel Etchant Chemistry            | 81  |

|    | 4.4.   | Conclusion                                                     | 84  |

| 5. | Recess | s Etch                                                         |     |

|    | 5.1.   | Introduction                                                   | 89  |

|    | 5.2.   | Fabrication of the TFT with Recess Source/Drain Contacts       | 90  |

|    | 5.3.   | Result and Discussion.                                         | 93  |

|    |        | 5.3.1. On- and Subthreshold Regions Electrical Characteristics | 93  |

|    |        | 5.3.2. Off Region Electrical Characteristics.                  | 97  |

|    |        | 5.3.3. Possible Advantage of this Structure                    | 97  |

|    | 5.4.   | Conclusion.                                                    | 98  |

| 6. | High ' | Temperature Electrical Performance and Stability               |     |

|    | 6.1.   | Introduction                                                   | 103 |

|    | 6.2. | Experimental                                     | 104 |

|----|------|--------------------------------------------------|-----|

|    | 6.3. | Result and Discussion.                           | 108 |

|    |      | 6.3.1. Temperature Effect on a-Si:H TFT          | 108 |

|    |      | 6.3.2. Bias Instability of a-Si:H TFT            | 115 |

|    |      | 6.3.3. Current Instability of a-Si:H TFT         | 118 |

|    | 6.4. | Impact of the Threshold Voltage Shift on AM-OLED | 121 |

|    | 6.5. | Conclusion.                                      | 128 |

| 7. | Summ | nary and Recommendation for Future Work          |     |

|    | 7.1. | Summary of the Thesis                            | 135 |

|    | 7.2. | Recommendation for Future Research               | 137 |

# List of Figures

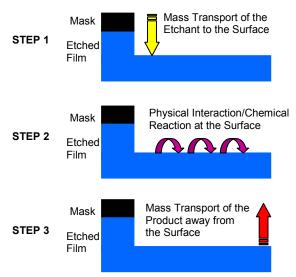

| Figure 2-1:  | Figure 2-1: Schematic of the etching process                            | 10         |  |

|--------------|-------------------------------------------------------------------------|------------|--|

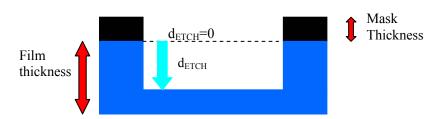

| Figure 2-2:  | Schematic describing etching depth.                                     | 11         |  |

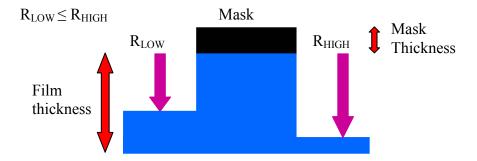

| Figure 2-3:  | Schematic describing etching uniformity                                 | 12         |  |

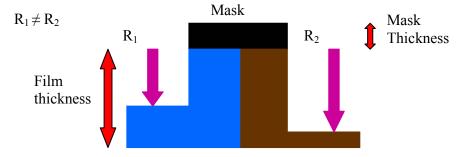

| Figure 2-4:  | Schematic describing etching selectivity                                | 12         |  |

| Figure 2-5:  | Schematic describing undercut during etching                            | 13         |  |

| Figure 2-6:  | Schematic describing anisotropy                                         | 13         |  |

| Figure 2-7:  | Schematic of an isotropic etch, where A=0                               | 13         |  |

| Figure 2-8:  | Schematic of a perfect anisotropic etch, where A=1                      | 14         |  |

| Figure 2-9:  | Schematic of an under-etched film.                                      | 14         |  |

| Figure 2-10: | Schematic describing an over-etched film                                | 14         |  |

| Figure 2-11: | Etching rate characterization plots for G1 and G2 silicon nitride       | 17         |  |

| Figure 2-12: | SF <sub>6</sub> etching rate characterization plots                     | 20         |  |

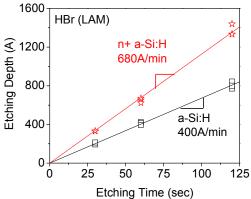

| Figure 2-13: | HBr etching rate characterization plots.                                | 20         |  |

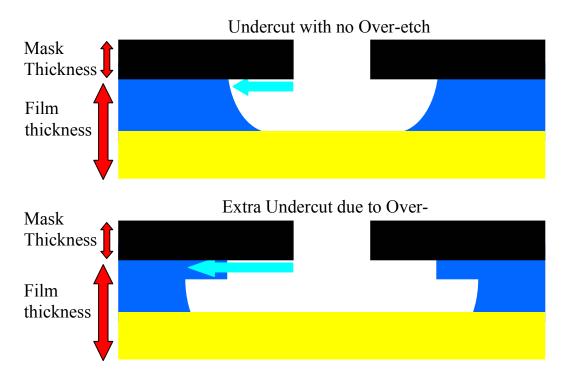

| Figure 2-14: | Schematic of extra undercut caused by excess over-etch                  | 23         |  |

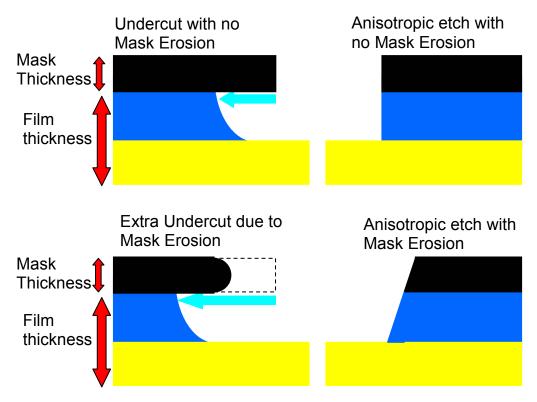

| Figure 2-15: | Schematic of extra undercut caused by mask erosion                      | 25         |  |

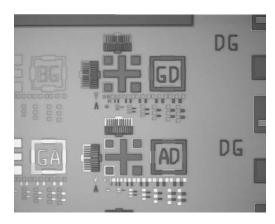

| Figure 2-16: | Gate level alignment and Vernier marks                                  | 29         |  |

| Figure 2-17: | Example of TFT structures after the gate patterning                     | 29         |  |

| Figure 2-18: | Schematic cross-section of the TFT gate metal sputtering and I          | patterning |  |

|              | process                                                                 | 30         |  |

| Figure 2-19: | Schematic cross-section of the PECVD of G2 and G1 a-SiN <sub>X</sub> :H | I, A1 and  |  |

|              | A2 a-Si:H and n+ a-Si:H films for the TFT                               | 31         |  |

| Figure 2-20: | Gate-to-Island level alignment and Vernier marks                        | 32         |  |

| Figure 2-21: | Example of TFT structures after the island patterning                   | 32         |  |

| Figure 2-22: | Schematic cross-section of the TFT island patterning step               | 32         |  |

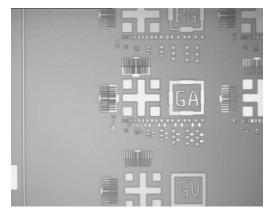

| Figure 2-23: | Gate-to-via level alignment and Vernier marks                           |            |  |

| Figure 2-24: | Example of TFT structures after the via patterning                      | 33         |  |

| Figure 2-25: | Schematic cross-section of the TFT gate via patterning process33             |  |  |

|--------------|------------------------------------------------------------------------------|--|--|

| Figure 2-26: | Schematic cross-section of the source/drain metal sputtering and             |  |  |

|              | patterning process                                                           |  |  |

| Figure 2-27: | Gate-to-contact level alignment and Vernier marks                            |  |  |

| Figure 2-28: | Example of TFT structures after the back channel etch35                      |  |  |

| Figure 2-29: | Schematic cross-section of the final TFT structure                           |  |  |

| Figure 2-30: | Schematic of TFT I-V measurement setup                                       |  |  |

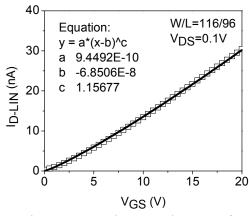

| Figure 2-31: | Linear region transfer characteristics of TFT: data (figure) and linear fit  |  |  |

|              | (line)                                                                       |  |  |

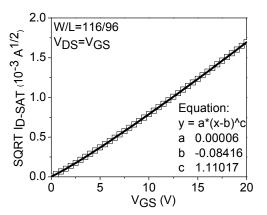

| Figure 2-32: | Saturation region transfer characteristics of TFT: data (figure) and linear  |  |  |

|              | fit (line)                                                                   |  |  |

| Figure 2-33: | Linear region transfer characteristics of TFT: data (figure) and fit (line)  |  |  |

|              | 40                                                                           |  |  |

| Figure 2-34: | Saturation region transfer characteristics of TFT: data (figure) and fit     |  |  |

|              | (line)40                                                                     |  |  |

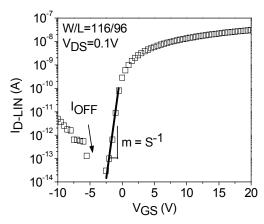

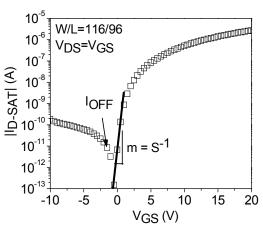

| Figure 2-35: | Linear region transfer characteristics of TFT on semi-log plot41             |  |  |

| Figure 2-36: | Saturation region transfer characteristics of TFT on semi-log plot41         |  |  |

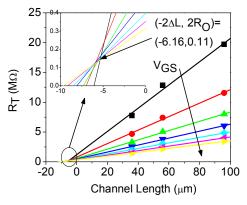

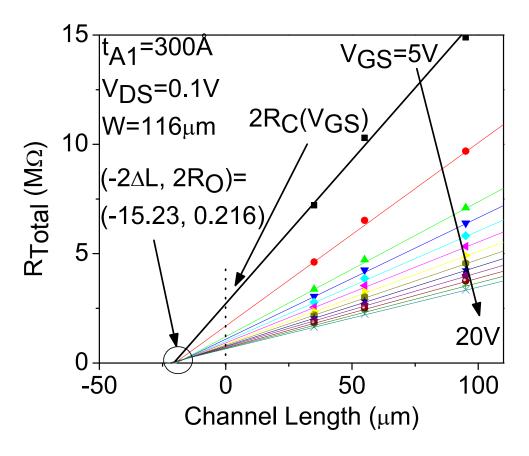

| Figure 2-37: | Total resistance for different TFT channel lengths                           |  |  |

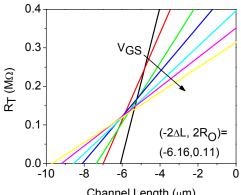

| Figure 2-38: | Cross-point in the $R_T$ vs. L plot indicating $\Delta L$ and $R_O$          |  |  |

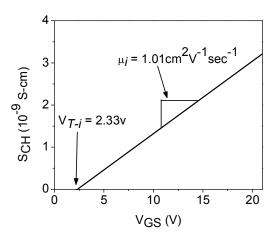

| Figure 2-39: | Extraction of intrinsic mobility and threshold voltage from the channel      |  |  |

|              | conductance                                                                  |  |  |

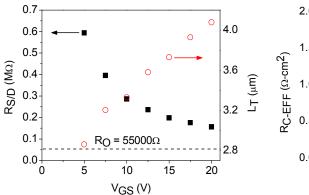

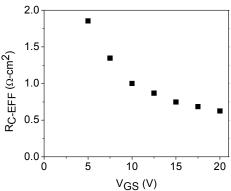

| Figure 2-40: | Contact resistance and effective length plot versus gate voltage44           |  |  |

| Figure 2-41: | Specific contact resistance versus gate voltage plot                         |  |  |

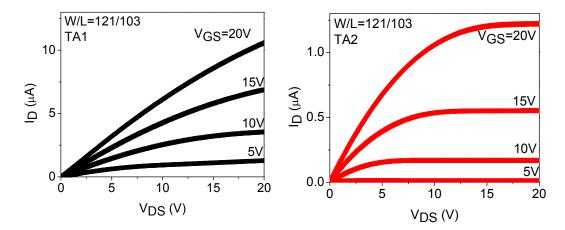

| Figure 3-1:  | Output characteristics of TA1                                                |  |  |

| Figure 3-2:  | Output characteristics of TA2                                                |  |  |

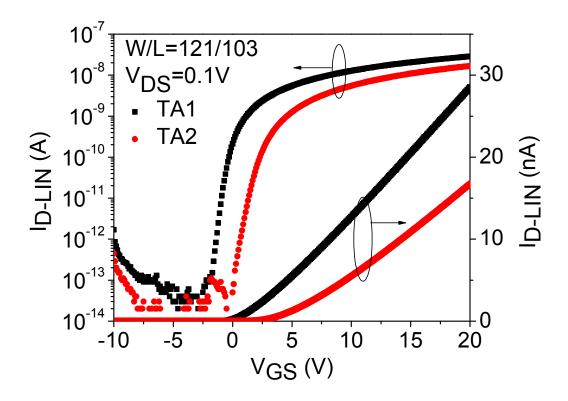

| Figure 3-3:  | Linear region transfer characteristics of traditional transistors fabricated |  |  |

|              | with only low-deposition-rate (TA1) and high-deposition-rate (TA2)           |  |  |

|              | amorphous silicon films                                                      |  |  |

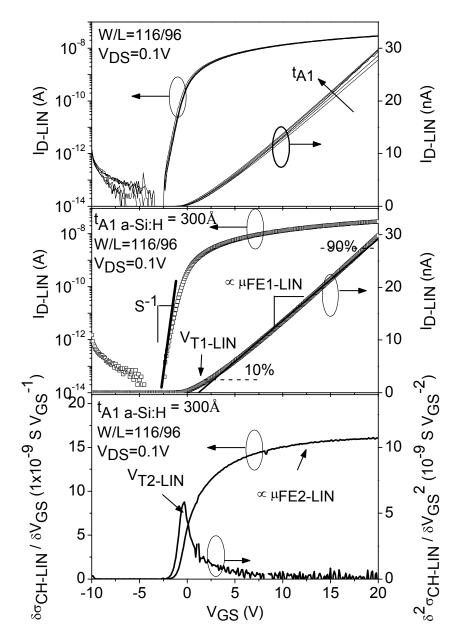

| Figure 3-4:  | Linear region transfer characteristics of a-Si:H TFT with different A1 and   |  |  |

|              | A2 a-Si:H thicknesses (top)                                                  |  |  |

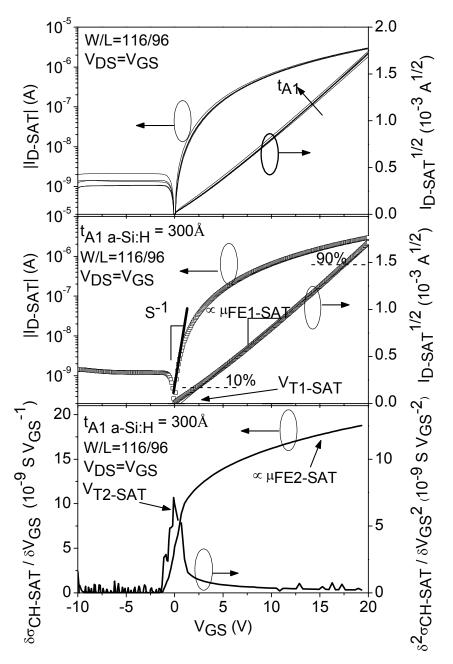

| Figure 3-5: | Saturation region transfer characteristics of a-Si:H TFT with different A1                                                                                          |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | and A2 a-Si:H thicknesses (top)57                                                                                                                                   |

| Figure 3-6: | Example of $R_{TOTAL}$ , $r_{CH}$ , $R_{C}(V_{GS})$ , $R_{O}$ , and $\Delta L$ value extraction using                                                               |

|             | TLM58                                                                                                                                                               |

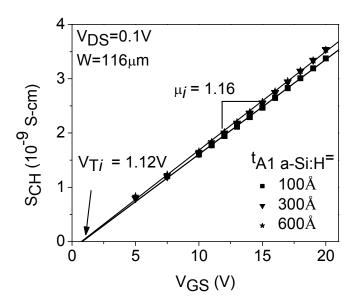

| Figure 3-7: | Extraction of an a-Si:H TFT's (t <sub>A1</sub> =100, 300, 600Å) intrinsic mobility and                                                                              |

|             | threshold voltage by using channel conductivity versus gate voltage plot                                                                                            |

|             | symbols and lines represent experimental data and the best-fit line                                                                                                 |

|             | respectively. Values of intrinsic mobility and threshold voltage shown                                                                                              |

|             | belong to TFT with t <sub>A1</sub> of 600Å59                                                                                                                        |

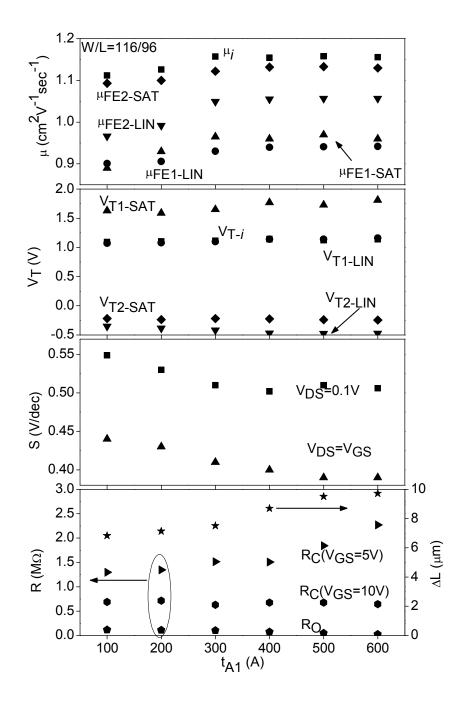

| Figure 3-8: | Intrinsic mobility and threshold voltage, and linear and saturation regions                                                                                         |

|             | field-effect mobility, threshold voltage, subthreshold swing, contact                                                                                               |

|             | resistances, and channel length deviation values for a-Si:H TFT's with                                                                                              |

|             | different A1 thicknesses investigated in this work                                                                                                                  |

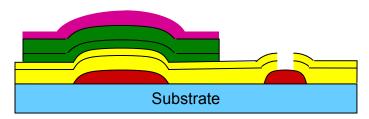

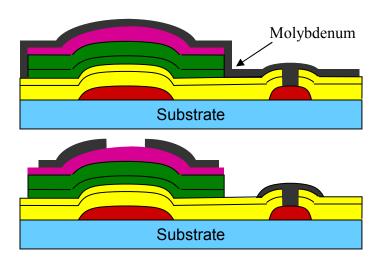

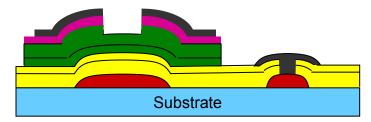

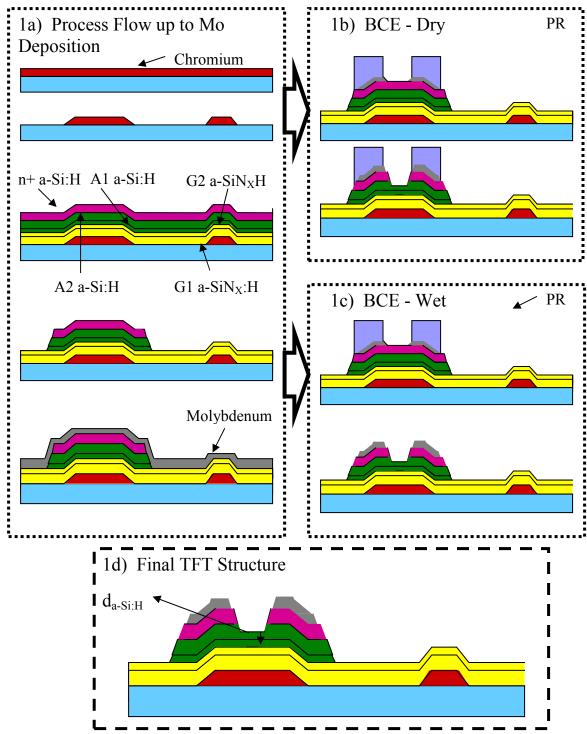

| Figure 4-1: | Complete fabrication schematic of a-Si:H transistor                                                                                                                 |

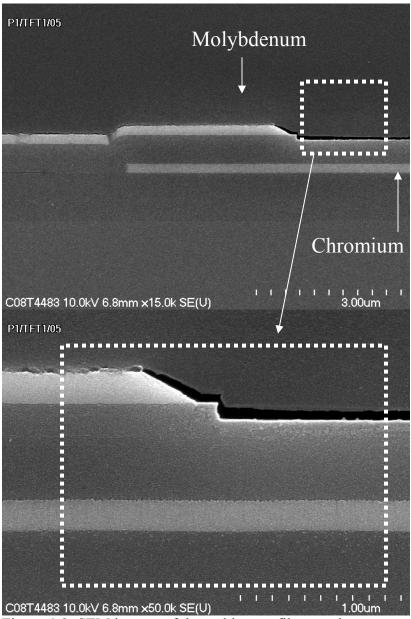

| Figure 4-2: | SEM images of the etching profile near the source terminal of the a-Si:H                                                                                            |

|             | TFT. The molybdenum is etched with Al Etchant Type A, and the n+ a-                                                                                                 |

|             | Si:H with HBr+Cl <sub>2</sub>                                                                                                                                       |

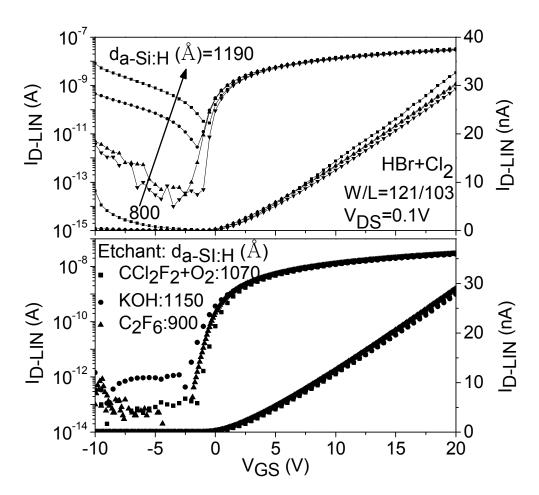

| Figure 4-3: | Linear region ( $V_{DS}$ =0.1V) transfer characteristics of a-Si:H TFT's etched                                                                                     |

|             | with HBr+Cl <sub>2</sub> (top) for different d <sub>a-Si:H</sub> , and CCl <sub>2</sub> F <sub>2</sub> +O <sub>2</sub> , C <sub>2</sub> F <sub>6</sub> , and KOH    |

|             | (bottom)                                                                                                                                                            |

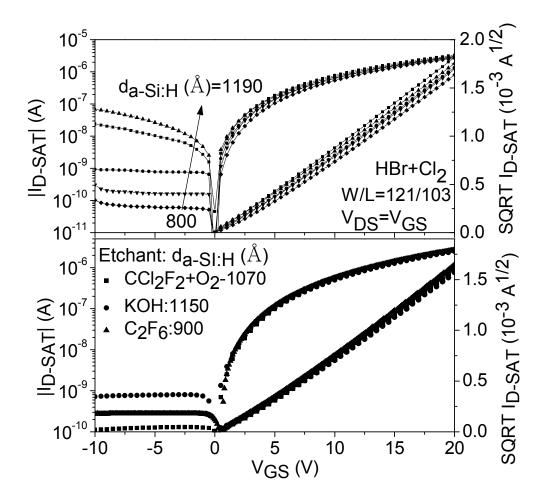

| Figure 4-4: | Saturation region (V <sub>DS</sub> =V <sub>GS</sub> ) transfer characteristics of a-Si:H TFT's                                                                      |

|             | etched with HBr+Cl <sub>2</sub> (top) for different d <sub>a-Si:H</sub> , and CCl <sub>2</sub> F <sub>2</sub> +O <sub>2</sub> , C <sub>2</sub> F <sub>6</sub> , and |

|             | KOH (bottom)                                                                                                                                                        |

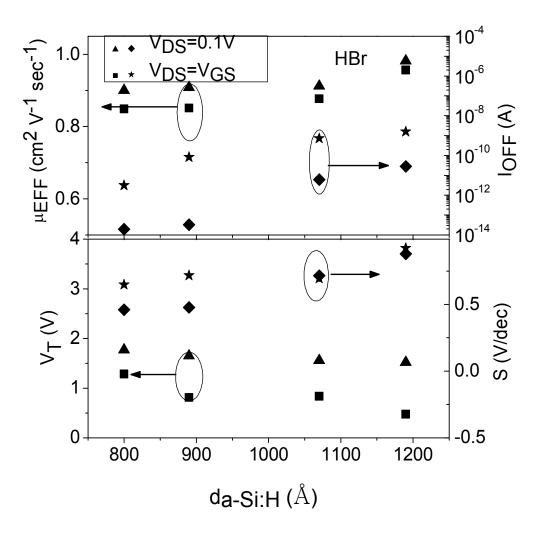

| Figure 4-5: | Amorphous silicon TFTs' field effect mobility, threshold voltage                                                                                                    |

|             | subthreshold swing, and off-current values change with da-Si:H. Al                                                                                                  |

|             | transistors are etched using HBr+Cl <sub>2</sub> 80                                                                                                                 |

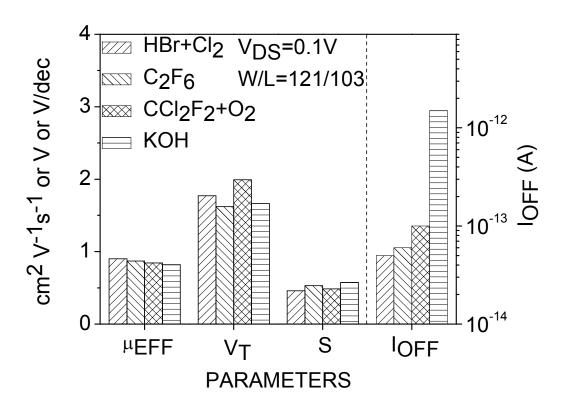

| Figure 4-6: | Optimum a-Si:H TFTs' field effect mobility, threshold voltage                                                                                                       |

|             | subthreshold swing, and off-current values comparison83                                                                                                             |

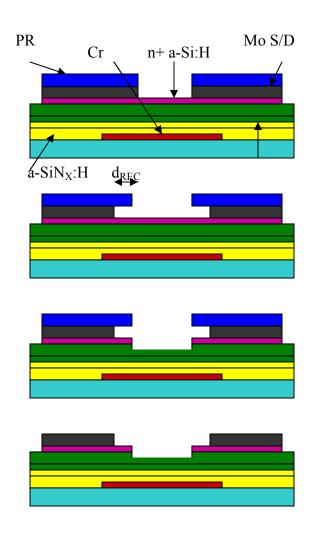

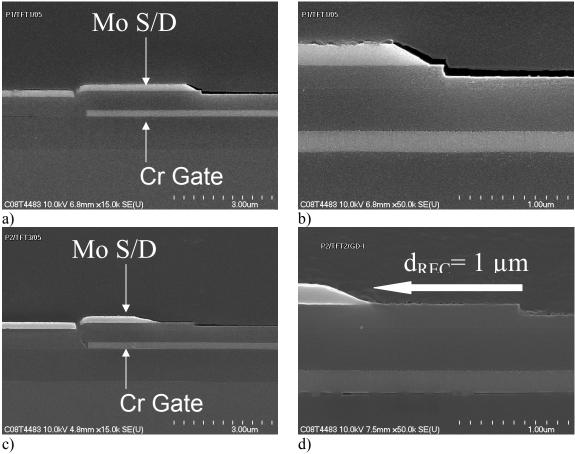

| Figure 5-1  | Schematic fabrication process for the recess contact TFT 90                                                                                                         |

| Figure 5-2  | Scanning electron microscope image of the a-Si:H TFT with normal S/D                               |

|-------------|----------------------------------------------------------------------------------------------------|

|             | profile (a and b), and recess S/D profile (c and d)91                                              |

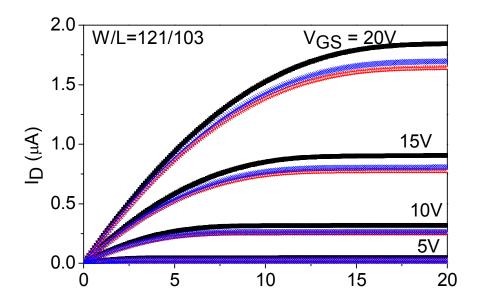

| Figure 5-3  | The output characteristics of the transistors are shown in this figure92                           |

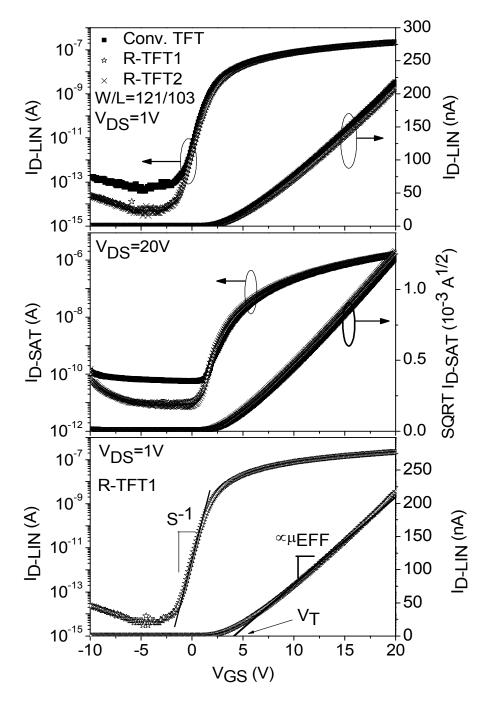

| Figure 5-4  | Linear (top) and saturation (middle) regions transfer characteristics of the                       |

|             | three types of a-Si:H TFT structures presented in this work. The bottom                            |

|             | plot shows an example of the parameter extraction94                                                |

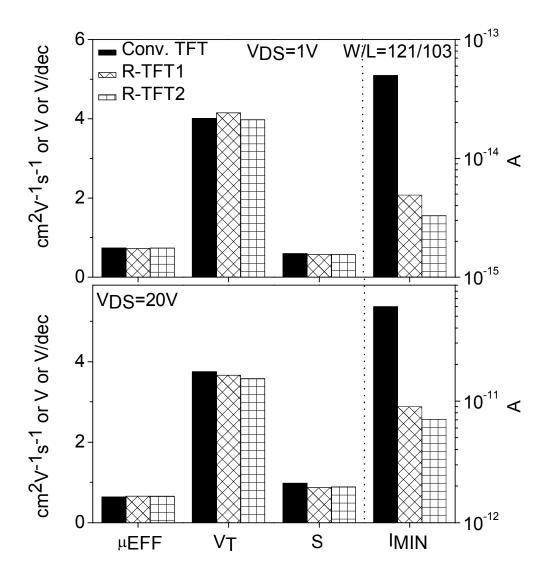

| Figure 5-5  | Summaries of the extrinsic electrical performance of the a-Si:H TFT's                              |

|             | fabricated using the conventional processing steps (Conv. TFT), and with                           |

|             | the inclusion of the recess etches (R-TFT1 and R-TFT2)95                                           |

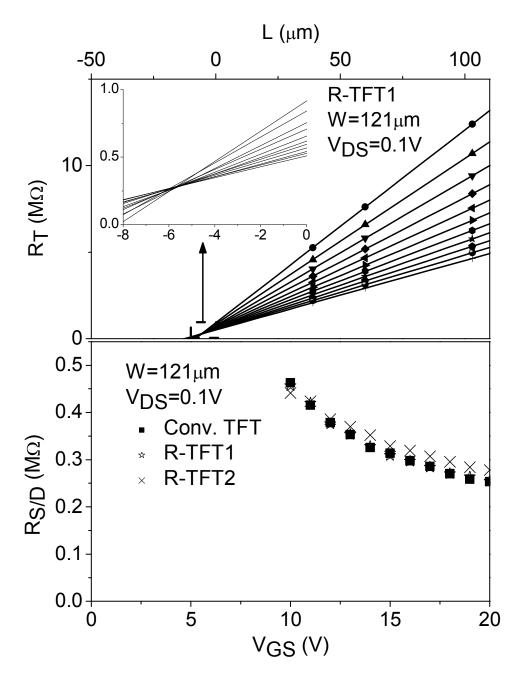

| Figure 5-6  | The extraction of $R_{S/D}$ for R-TFT1 is shown in the top figure. The bottom                      |

|             | figure shows the source/drain contact resistance values for all three                              |

|             | transistors structures at different gate biases96                                                  |

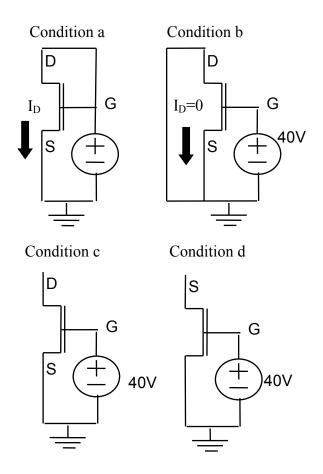

| Figure 6-1: | BTS experimental setups for four a-Si:H TFT stressing conditions                                   |

|             | described in the text                                                                              |

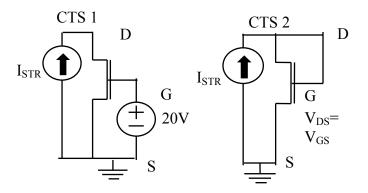

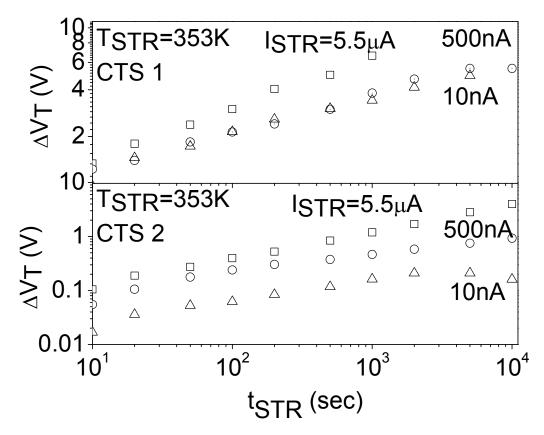

| Figure 6-2: | CTS experimental setups used in this work: CTS 1 ( $V_{GS}$ =20 V) and CTS 2                       |

|             | ( $V_{GS}$ = $V_{DS}$ ). The stress current ( $I_{STR}$ ) levels are 10 nA, 500 nA, and 5.5        |

|             | μΑ107                                                                                              |

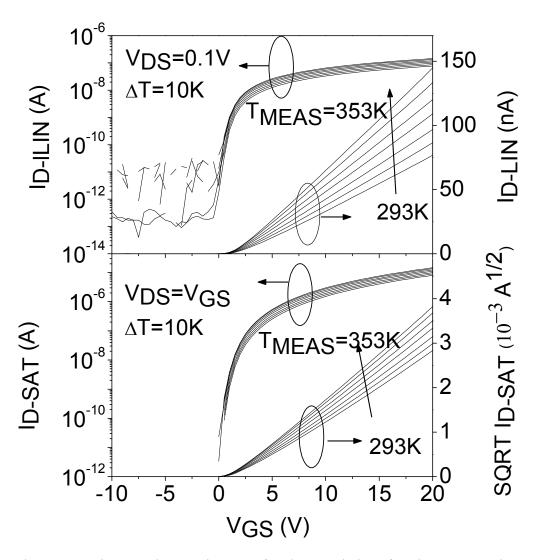

| Figure 6-3: | Linear and saturation transfer characteristics of a-Si:H measured from                             |

|             | $(T_{MEAS}) = 293 \text{ to } 353 \text{ K}.$ 109                                                  |

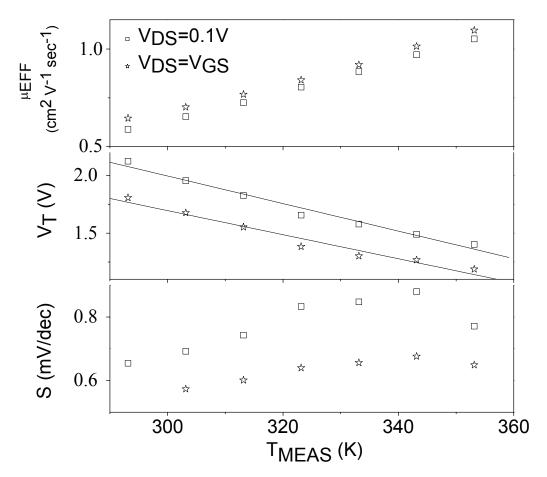

| Figure 6-4: | Field effect mobility, threshold voltage, and subthreshold swing change                            |

|             | with the measurement temperature. Symbols represent experimental data                              |

|             | and lines are numerical fit                                                                        |

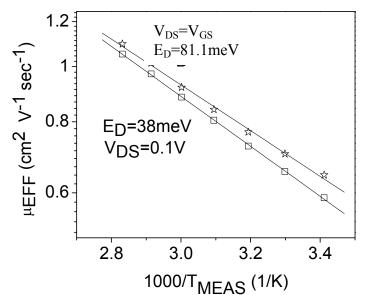

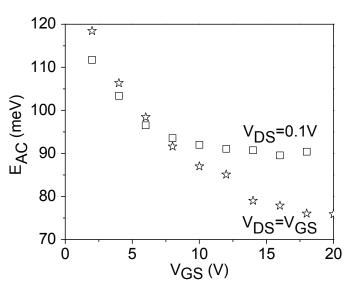

| Figure 6-5: | Field-effect mobility variation as function of 1/T <sub>MEAS</sub> for a-Si:H TFT used             |

|             | in this work111                                                                                    |

| Figure 6-6: | Drain current activation energy value versus gate voltage for linear                               |

|             | $(V_{DS}=0.1V)$ and saturation $(V_{DS}=V_{GS})$ regions of device operation115                    |

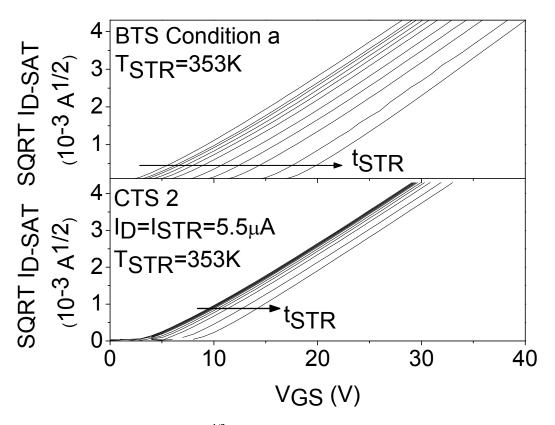

| Figure 6-7: | Example of I <sub>D-SAT</sub> 1/2 vs. V <sub>GS</sub> in the saturation region of operation during |

|             | BTS (top) and CTS (bottom)                                                                         |

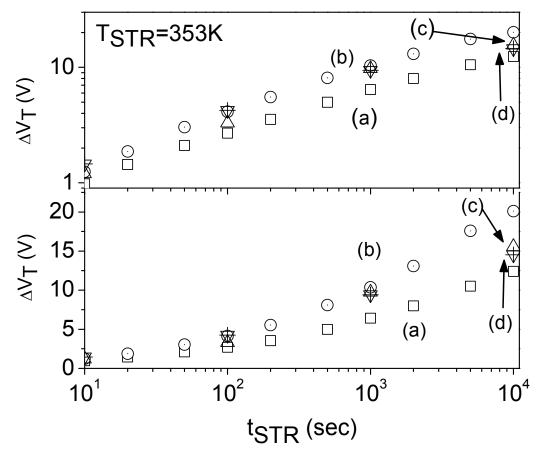

| Figure 6-8: | Variation of $\Delta V_T$ with the stress time on both log (top) and linear (bottom)               |

|             | scales, at $T_{STR}$ =353 K, for the following BTS conditions: a) $V_{GS}$ = $V_{DS}$ =40          |

|              | V, b) $V_{GS}$ =40 V and $V_{DS}$ =0 V, c) $V_{GS}$ =40 V and the drain is floating, and |

|--------------|------------------------------------------------------------------------------------------|

|              | d) $V_{GD}$ =40 V and the source is floating                                             |

| Figure 6-9:  | CTS induced $\Delta V_{\text{T}}$ extracted from figures with stress temperature at      |

|              | $T_{STR}$ =353 K for $V_{GS}$ =20 V (top) and $V_{GS}(t)$ = $V_{DS}(t)$ (bottom)121      |

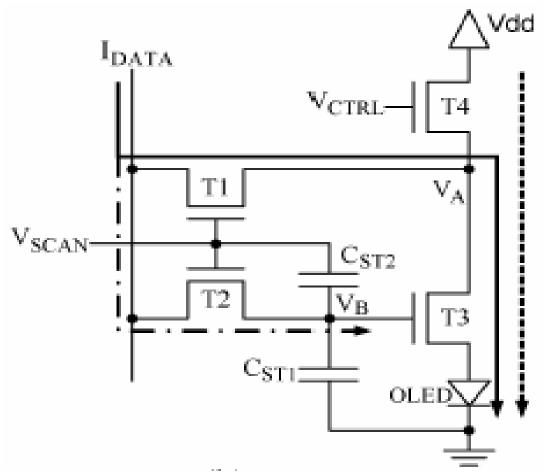

| Figure 6-10: | Schematic diagram of current-driven AM-OLED pixel electrode circuit                      |

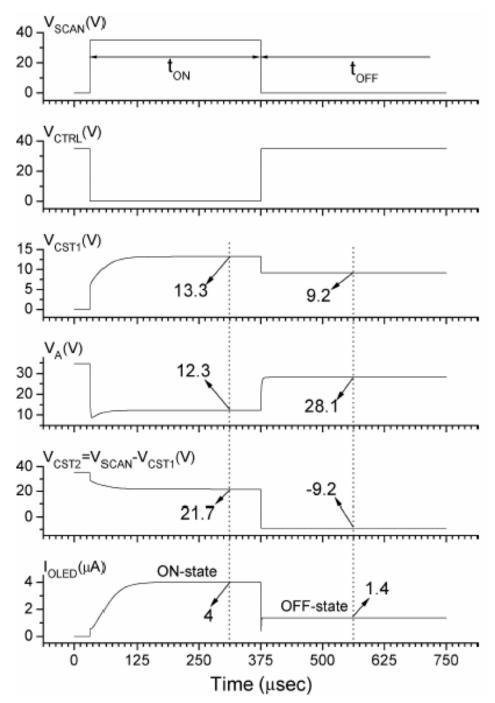

|              | proposed by Lin <i>et al</i> [21]                                                        |

| Figure 6-11: | Timing diagram of current-driven AM-OLED pixel electrode circuit                         |

|              | proposed by Lin <i>et al</i> [21]126                                                     |

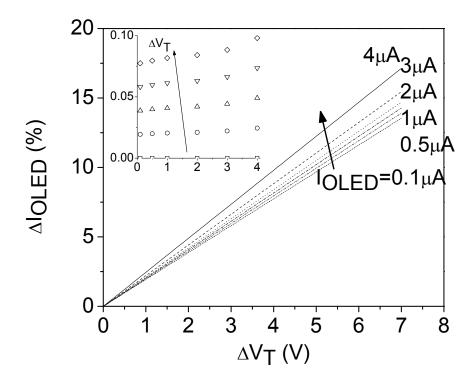

| Figure 6-12: | Simulated OLED current decrease with T4 threshold voltage shift and T3                   |

|              | channel length modulation factor of 0.05. The inset shows $\Delta I_{OLED}$ with         |

|              | $I_{OLED}$ ranging from 0.1 to $4\mu A$ for $\Delta V_T$ of 0 to $4V$                    |

# List of Tables

| Table 1-1: | Summary of common CVD systems used for the deposition of electronic     |

|------------|-------------------------------------------------------------------------|

|            | grade amorphous silicon films                                           |

| Table 2-1: | Common RIE etching recipe used for silicon transistor process19         |

| Table 2-2: | Etching chemistry and rates used for our a-Si:H TFT fabrication         |

|            | process                                                                 |

| Table 4-1: | Etching chemistry and conditions for back-channel etch process used in  |

|            | this chapter, and their respective etch rates for PECVD a-Si:H and n+ a |

|            | Si:H films                                                              |

# List of Abbreviations/Acronyms

A1 Low deposition rate (600 Å/min) hydrogenated amorphous silicon

A2 High deposition rate (1200 Å/min) hydrogenated amorphous silicon

BCE Back channel etch

BHF Buffered hydrofluoric acid

BTS Bias temperature stress

CTS Current temperature stress

DOS Density of states

G1 Low deposition rate (900 Å/min) N-rich amorphous silicon nitride

G2 High deposition rate (1800 Å/min) N-rich amorphous silicon nitride

PECVD Plasma-enhanced chemical vapor deposition

PR Photo-resist

RIE Reactive ion etch

S/D Source/drain

TFT Thin-film transistor

# Glossary

a-Si:H Hydrogenated amorphous silicon

a-SiN<sub>X</sub>:H Hydrogenated amorphous silicon nitride

$CF_4$  Tetrafluoromethane  $C_2F_6$  Hexafluoroethane

CCl<sub>2</sub>F<sub>2</sub> Dichlorodifluoromethane

HBr Hydrobromic acid

I<sub>OFF</sub> Off-current

KOH Potassium hydroxide

L Transistor channel length

$\mu_{EFF}$  Field-effect mobility

$\mu_i$  Intrinsic mobility

n+ a-Si:H Phosphorous doped (1%) hydrogenated amorphous silicon

S Subthreshold swing SF<sub>6</sub> Sulfur hexafluoride

TMAH Tetramethyl-ammonium hydroxide

V<sub>T</sub> Threshold voltage

V<sub>T-i</sub> Intrinsic threshold voltage

W Transistor channel width

#### **Abstract**

In the fabrication of active-matrix liquid crystal display (AM-LCD) and activematrix organic light-emitting diode (AM-OLED), the amorphous silicon thin-film transistor (a-Si:H TFT) technology forms the backbone of the driving electronics for the large-size displays. Transistors for such application need to have high electrical performance and stability, as well as a high production output. In this dissertation we present an advanced multi-layer amorphous silicon thin-film transistor structure with a tailored channel region for the flat-panel display application. This specially tailored channel allows the rapid deposition of the TFT's gate insulator and active material without significantly altering its electrical performance and characteristics. We first investigate the nominal film geometry that maximizes the production throughput of the transistor. We fabricate transistors with the conventional structure, and they show a field-effect mobility of 0.95 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, threshold voltage of 1.18 V, and subthreshold swing of 0.46 V/dec. We are able to produce multi-layer a-Si:H TFTs that show a fieldeffect mobility of 0.93 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, threshold voltage of 1.07 V, and subthreshold swing of 0.51 V/dec. However, our proposed TFT structure has a 40% shorter deposition time, which provides it with a competitive edge due to its higher throughput.

In order to further improve the applicability of our a-Si:H TFTs, we present a novel, recess contact TFT aimed to reduce the off-current level. We are able to produce TFTs with an off-current level below 10<sup>-14</sup> A. Compared to a conventional TFT, this low

off-current TFT has a comparable electrical performance in the on-regime of operation, but approximately one order of magnitude lower off-current.

Finally, we tested the electrical stability of the multi-layer a-Si:H TFTs with the tailored channel. This transistor has similar threshold voltage shift as the conventional transistors, even though the gate insulator is deposited at a high rate. Under 10,000 s of constant current bias (5.5  $\mu$ A) at an elevated temperature (353 K), our TFT (W/L=24/6) has a threshold voltage of less than 4 V.

# **Chapter 1**

#### Introduction

#### 1.1. Background and Motivation

In 1963, Richard Williams of the RCA David Sarnoff Research Center published the first observed electro-optic effect in liquid crystal [1, 2]. At the time RCA decided to commercialize liquid crystal displays (LCD) in mid-1960, capacitors and semiconductor diodes evaporated on glass were used for the addressing of each pixel. This addressing scheme, now known as the passive matrix, suffers various limitations from small display size to low frame rate. The introduction of the active-matrix addressing scheme in the mid-1970s realizes the possibility of making higher quality LCD's [3]. For the displays utilizing the active-matrix technology, each pixel contains independent semiconductorbased logic switching, and even memory elements. Consequently, there was a pressing need for a semiconductor material that can be deposited on the substrates used for the fabrication of LCD's. A very promising candidate appeared 10 yrs after the discovery of the liquid crystal, when Malhotra and Neudeck demonstrated the field effect conductance change in an evaporated amorphous silicon film [4]. This structure is the predecessor of the modern-day amorphous silicon thin-film transistor (a-Si:H TFT). In the early 1980's, researchers began to recognize the possibility of using a-Si:H TFT for the pixel electrode circuit of an active-matrix liquid crystal display (AM-LCD) [5-7]. Currently, the

amorphous silicon, together with the low-temperature polycrystalline silicon (LTPS) and cadmium selenide (CdSe) TFT technologies, form the backbone of the driving electronic in the TFT LCD industry. LTPS and CdSe technologies, despite having relatively high electrical performance, require extensive research to overcome uniformity and yield – related issues. The a-Si:H technology is leading the market due to its fabrication flexibility, low cost, and readiness to be used for large size displays. Today the entire TFT LCD industry amounts to an \$83 billion business, selling more than 400 million units of displays around the world every year [8]. Along with the recent emergence of the active matrix organic light emitting displays (AM-OLED), it is more important than ever for the realization of high performance a-Si:H TFTs.

The first a-Si:H TFT was fabricated by depositing aluminum source and drain, and electron-beam evaporated a-Si:H on top of heavily doped oxidized silicon wafers. Both hole and electron transports could be observed between the source and drain terminals. In 1977 and 1978, Fritzsche and Deneuville separately began using PECVD as a tool to deposit amorphous silicon film to be used for field-effect transistor, [9] and bipolar junction transistor [10], respectively. The operation and theory of a-Si:H TFT was confirmed and further analyzed by Matsumura and Nara [11], when they explicitly indicate both p and n channel conductions of the device. However, in both cases the apparent mobility is quite low and a large voltage is required to turn on the transistor. Hayama and Matsumura deposited an n+ a-Si:H layer between the a-Si:H and the metal, and this causes a great increase in on-and-off-current ratio due to the reduction of the TFT contact resistance [6]. Powell *et al* used silicon nitride as the gate insulator, and achieved a very low threshold voltage and subthreshold swing because of improvement in

the interface quality and the a-Si:H DOS [12]. Even though Le Comber  $et\ al$ . had already suggested the use of a-SiN<sub>X</sub>:H as the gate insulator [13], Powell's TFT showed great electrical performance, and the era for a-Si:H TFT began. Over the course of a decade, from the characterization of material by Walley, Brodsky, and LeComber to the emergence of the modern structure, a-Si:H TFT has since become the dominant technology in displays and sensors, with researchers all over the world seeking new ways to optimize its performance and broaden its application.

In order for the a-Si:H TFT technology to continue its current dominance in the AM-LCD industry, several of its drawbacks must be addressed as they can limit its potential applicability for large size displays. First of all, the a-Si:H TFT has a lower electrical performance than, say poly-silicon TFT, because the amorphous silicon film has smaller crystalline grain sizes. The distortion of the ideal tetrahedral silicon-tosilicon bond leads to the creation of the band-tail states along the conduction and valence band edges, while the unsatisfied dangling silicon bonds produce the deep-gap states [14]. Both types of states degrade the transistor's electrical performance, which in turn limits the sizes of both AM-LCDs and AM-OLEDs that use the a-Si:H TFT as the driving electronic [15, 16]. Secondly, the a-Si:H TFT can have a high leakage current, in part originating from its fabrication process. This deleterious effect can lead to AM-LCD luminance change during the driving stage of its pixel electrode circuit, due to the discharging of the storage capacitor through the channel of the switching transistor. Lastly, it is desirable to deposit the amorphous silicon films at a high deposition rate to increase the overall manufacturing throughput of the display, which in turn lowers its production cost. However, increasing the deposition rate of the a-Si:H film increases the

densities of both band-tail and deep-gap states. It is well-known that a-Si:H films with high band-tail states produces TFTs with low field-effect mobility [14], and this means that there exists a trade-off between throughput and performance. Typically, TFTs with higher electrical performance suffer even more performance degradation with increase in deposition rate. This phenomenon poses a challenge for engineers who want to maximize their displays' production throughput without compromising the integrity of the a-Si:H TFT's electrical performance.

At the time of this dissertation, there are numerous reports of high performance a-Si:H TFT's deposited at high deposition rates. Methods of a-Si:H film deposition include high frequency (HF), 13.6 MHz, plasma enhanced chemical vapor deposition (PECVD) [17], very high frequency (VHF), typically above 40 MHz, PECVD [18-20], catalytic CVD (Cat-CVD) [21, 22], and electron cyclotron resonance CVD (ECR-CVD) [23, 24]. However, only high and very high frequency PECVD systems are used for the production of the FPD panels. Although other deposition systems are capable of producing a-Si:H TFTs with high mobility values at high deposition rates, it is difficult for these tools to deposit a-Si:H over a large area. VHF PECVD systems can deposit a-Si:H over a large area, but require expensive setup to combat non-uniform deposition thickness and power loss problems caused by the standing evanescent wave at the surface of the capacitor electrodes [25]. Table 1-1 summarizes the benefits and limitations of some of the methods used for amorphous silicon film deposition.

Table 1-1: Summary of common CVD systems used for the deposition of electronic grade amorphous silicon films.

|                     | Field-Effect        | Threshold | Deposition | Suitable  | Uniformity |

|---------------------|---------------------|-----------|------------|-----------|------------|

|                     | Mobility            | Voltage   | Rate       | for Large | Over Large |

|                     | $(cm^2 V^1 s^{-1})$ | (V)       | (nm/min)   | Area?     | Area?      |

| HF PECVD [17]       | 1.45                | 1.9       | 50         | Yes       | Good       |

| VHF PECVD [18]      | 1.1                 | 1.1       | 60         | Possible  | Average    |

| Cat-CVD [21]        | 0.85                | 4.6       | 114        | Possible  | Good       |

| ECR-CVD [24]        | 15.3                | 3.7       | 120        | No        | Poor       |

| PECVD in this study | 0.93                | 1.1       | 102*       | Yes       | Good       |

<sup>\*</sup> effective deposition rate

The mission of this dissertation is to design and fabricate a commercially viable amorphous silicon transistor structure for the future flat-panel display industry. To achieve this, we propose a novel amorphous silicon thin-film transistor multi-layer structure with a specially tailored channel region to achieve the optimum electrical performance and stability, while maintaining a short overall deposition time. This structure can be used for the commercial fabrication of large-size FPDs due to its high mobility and high potential production throughput. Next, we formulate a meticulously tuned fabrication procedure that maximizes our transistor's electrical performance. This process is fully compatible with the commercial fabrication of FPDs. Additionally, we present a novel etching method that reduces our transistor's leakage current.

# 1.2. Organization of Dissertation

In chapter 2, we provide the detailed fabrication steps and characterization methods used to produce and analyze the proposed multi-layer amorphous silicon thin-film transistor with the tailored channel. This chapter includes the background information regarding semiconductor processing, description of the fabrication tools and

processes, setup of the analytical systems, and engineering controls and testing techniques used during the fabrication of the proposed a-Si:H TFT. Chapter 3 describes the geometric effect of the tailored channel on the electrical performance of the proposed transistor, and evaluates the trade-off between the film deposition time and the transistor's electrical performance. We successfully fabricated a-Si:H TFTs with the tailored channel, in a PECVD system used for the commercial manufacturing of FPDs, that exhibit field-effect mobility ( $\mu_{EFF}$ ) of 0.93 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, threshold voltage (V<sub>T</sub>) of 1V, and subthreshold swing of 0.51 V/dec.

In the following chapter, we present the effect of back channel etch (BCE) on the electrical properties of our a-Si:H TFT. We show the minimum thickness for the total amorphous silicon film deposited is  $\sim$ 1600 Å, and that HBr+Cl<sub>2</sub> is a promising dry etchant for the back channel etch process. Chapter 5 demonstrates a novel transistor structure with recessed source/drain contact electrodes that is specially designed to reduce the TFT's off-current. The recessed contact TFTs has off-current values of  $5x10^{-15}$  and  $1x10^{-11}$  A in the linear and saturation regions of operation, respectively, and shows no current crowding phenomenon. In chapter 6 we present the thermal and electrical performance and stability of the proposed a-Si:H TFT to demonstrate their applicability as the driving electronic for FPDs. Lastly, chapter 7 summarizes the work done in this dissertation and our recommendation for future research in the field of amorphous silicon thin-film transistors for display and other applications.

#### **Bibliography**

- 1. R. William, "Domains in liquid crystals," *Journal of Chemical Physics*, vol. 39, no. 2, pp. 384-388, Jul. 1963.

- 2. R. William, "Liquid crystals in an electric field," *Nature*, vol. 199, pp. 273-274, Jul. 1963.

- 3. T. P. Brody, "Large scale integration for display screens," *IEEE Transactions on Consumer Electronics*, vol. CE-21, no. 3, pp. 260-289, Aug. 1975.

- 4. A. K. Malhotra, G. W. Neudeck, "Field-effect conductance change in amorphous silicon," *Applied Physics Letters*, vol. 24, no. 11, pp. 557-559, Jun. 1974.

- 5. M. Matsumura, and H. Hayama, "Amorphous-silicon integrated circuit," *Proceedings of the IEEE*, vol. 68, no. 10, pp. 1349-1350, Oct. 1980.

- 6. H. Hayama and M. Matsumura, "Amorphous-silicon thin-film metal-oxide-semiconductor transistors" *Applied Physics Letters*, vol. 36, no. 9, pp. 754-755, May 1980.

- 7. A. J. Snell, W. E. Spear, P. G. LeComber, and K. Mackenzie, "Application of amorphous silicon field effect transistors in integrated circuits," *Applied Physics A: Solids and Surfaces*, vol. A26, no. 2, pp. 83-86, Oct. 1981.

- 8. Display Research http://www.displaysearch.com/cps/rde/xchg/SID-0A424DE8-1EB09283/displaysearch/hs.xsl/research\_paneltrack.asp

- 9. H. Fritzsche, "The nature of localized states and the effect of doping in amorphous semiconductors," *Chinese Journal of Physics*, vol. 15 no. 2, pp. 73-91, 1977.

- 10. A Deneuville and M.H. Brodsky, "Thin film metal base transistor structure with amorphous silicon," *Thin Solid Films*, vol. 55 no. 1, pp. 137-141, Nov. 1978.

- 11. M. Matsumura and Y. Nara, "High-performance amorphous-silicon field-effect transistors," *Journal of Applied Physics*, vol. 51, no.12, pp. 6443-6444, Dec. 1980.

- 12. M. J. Powell, B. C. Easton, and O. F. Hill, "Amorphous silicon-silicon nitride thin-film transistors," *Applied Physics Letters*, vol. 38 no. 10, pp. 794-796, May 1981.

- 13. P. G. Le Comber, W. E. Spear, and A. Ghaith, "Amorphous silicon field-effect device and possible application," *Electronic Letters*, vol. 15, no. 6, pp. 179-181, Mar. 1979.

- 14. R. A. Street, <u>Hydrogenated Amorphous Silicon</u>, Cambridge, MA, Cambridge University Press, 1991.

- 15. R. A. Street, "Large area electronics, applications and requirements," *Physica Status Solidi (A) Applied Research*, vol. 166, no. 2, pp. 695-705, Apr. 1998.

- 16. A. Kumar, A. Nathan, and G. E. Jabbour, "Does TFT mobility impact pixel size in AMOLED backplanes?" *IEEE Transactions on Electron Devices*, vol. 52, no. 11, pp. 2386-94, Nov. 2005.

- 17. C. Y. Chen and J. Kanicki, "High field-effect-mobility a-Si:H TFT based on high deposition-rate PECVD materials," *IEEE Electron Device Letters*, vol. 17, no. 9, pp. 437-439, Sep. 1996.

- 18. H. Meiling, J. Bezemer, R. E. I. Schropp, and W. F. Van Der Weg, "High-deposition-rate a-Si:H through VHF-CVD of argon-diluted silane," *Amorphous and Microcrystalline Silicon Technology 1997 Symposium*, pp. 459-470, 1997.

- 19. J. Hautala, Z. Saleh, J. F. M. Westendorp, H. Meiling, S. Sherman, and S. Wagner, "High deposition rate a-Si:H for the flat panel display industry," *Materials Research Society Symposium - Proceedings, v 420, Amorphous Silicon Technology*, pp. 83-92, 1996.

- 20. K. Takechi, Y. Nakagawa, V. Watabe, and S. Nishida, "High rate deposition of a-Si:H and a-SiN<sub>x</sub>:H by VHF PECVD," *Vacuum*, vol. 51, no. 4, pp. 751-755, Dec. 1998.

- 21. M. Sakai, T. Tsutsumi, T. Yoshioka, A. Masuda, and H. Matsumura, "High performance amorphous-silicon thin film transistors prepared by catalytic chemical vapor deposition with high deposition rate," *Thin Solid Films*, vol. 395, no. 1-2, pp. 330-4, Sep. 2001.

- 22. R. E. I. Schropp, B. Stannowsi, and J. K. Rath, "Hot wire deposited materials for thin film transistors," *37th International Conference on Microelectronics, Devices and Materials and the Workshop on Optoelectronic Devices and Applications*, pp. 15-27, Oct. 2001.

- 23. Y. J. Song and W. A. Anderson, "Stable amorphous silicon and improved microcrystalline silicon by photon-assisted electron cyclotron resonance chemical

- vapor deposition," *Materials Research Society Symposium Proceedings*, vol. 557, pp. 49-54, 1999.

- 24. L. Teng and W. A. Anderson, "Thin-film transistors on plastic and glass substrates using silicon deposited by microwave plasma ECR-CVD," *IEEE Electron Device Letters*, vol. 24, no. 6, Jun. 2003, pp. 399-401.

- 25. J. Rudiger, H. Brechtel, A. Kottwitz, J. Kuske, and U. Stephan, "VHF plasma processing for in-line deposition systems," *Thin Solid Films*, vol. 427, no. 1-2, pp. 16-20, Mar. 2003.

# **Chapter 2:**

#### **Fabrication and Characterization**

### 2.1. Thin-Film Etching

#### 2.1.1 Mechanism and Terminology

In modern day semiconductor processing, etching has become one of the most important steps in maintaining the quality of the products. Precise etching control, including etching profile, rate, and selectivity, allows engineers and scientists to fabricate devices with high accuracy, reproducibility, and uniformity. We will assess various etching methodologies used today in the processing of hydrogenated amorphous silicon

thin-film transistors. Traditionally etching is divided into wet etching and dry etching. Wet etching comprises of using solution as the primary etchant in the removing metal, semiconductor, and insulator films. On the contrary dry etching involves using a plasma to remove the desired films. Etching consists of three main steps: transport

Figure 2-1: Schematic of the etching process.

of etchant to the surface of the film to be etched, physical interaction and/or chemical reaction between the etchant and the film, and transport of the etching products away from the surface (figure 2-1).

The products of the etching process are generally in the gas or liquid phase to allow the completion of the last step of etching, namely the removal of the products. Masks are commonly used to define device structures, and typically, they should either be highly resistant to the etchant, or sacrificial layers that will not be included upon the completion of the device being fabricated. There are numerous criteria used to control and judge the quality and outcome of an etching process: etch directionality, etch rate, etch uniformity, etch selectivity, undercut, and repeatability.

**Etch depth (d**<sub>ETCH</sub>) – Amount of film removed during etching ( $d_{ETCH}$ ).

Figure 2-2: Schematic describing etching depth.

Etch rate ( $R_{ETCH}$ ) – Amount of specific film etched by an etchant in a given time, typically measured in nm/min or Å/min.

**Etch directionality** – Measure of the relative etch rates in different directions. A special case is the measure of vertical etch rate to lateral etch rate, also know as anisotropy (A).

Etch uniformity (U) – Percent of variation in etching depths across the entire wafer, from wafer to wafer, within a lot, or from lot to lot.

$$U = \frac{R_{HIGH} - R_{LOW}}{R_{HIGH} + R_{LOW}}$$

Figure 2-3: Schematic describing etching uniformity.

Etch selectivity (S) – Ratio of the etch rate of one film to the etch rate of another film for one specific etchant.

$$S = \frac{R_1}{R_2}$$

Figure 2-4: Schematic describing etching selectivity.

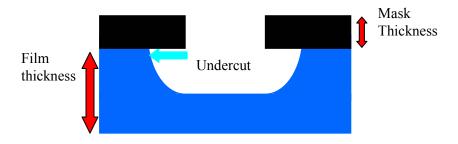

**Undercut** – Lateral etching of the target film underneath the etch mask.

Figure 2-5: Schematic describing undercut during etching.

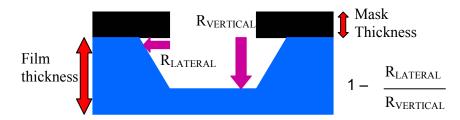

**Anisotropy** (A) – It is defined by the following relations:

$$A = 1 - \frac{R_{LATERAL}}{R_{VERTICAL}}$$

Figure 2-6: Schematic describing anisotropy.

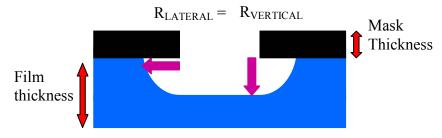

**Isotropic etch** – Etching of the film in all direction at the same etch rate, or A=0.

Figure 2-7: Schematic of an isotropic etch, where A=0.

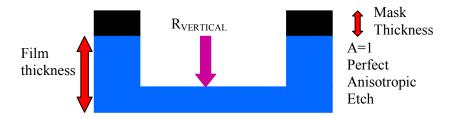

**Anisotropic etch** – Etching of the film in different directions at different etch rates.

Figure 2-8: Schematic of a perfect anisotropic etch, where A=1.

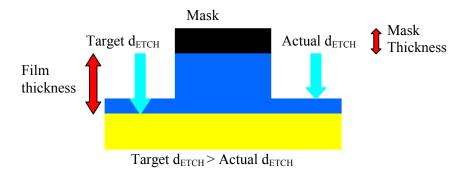

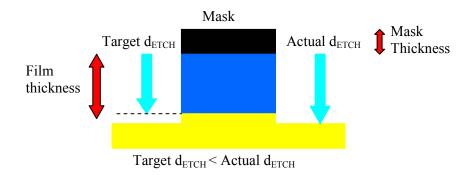

**Under-etch** – Etching step which the actual etching depth is smaller than the target etching depth.

Figure 2-9: Schematic of an under-etched film.

**Over-etch** – Etching step which the actual etching depth is larger than the target etching depth, potentially causing some etching of the underlying film.

Figure 2-10: Schematic describing an over-etched film.

**Loading** – Decrease in etch rate caused the depletion of etchant. This is caused by excess amount of particles from the film reacting with the etchant; the extensive reaction causes the concentration of the etchant to drop, leading to a decrease in the etch rate.

#### **2.1.2** Wet Etch

Wet etching, as the name suggests, uses liquid phase etchant to remove the target films. As the device substrate is submerged into the etchant, reactants in the solution diffuse across the stagnant layer near the surface of the film to reach the film surface. Next, chemical reaction between the reactants and the film particles take place. Lastly soluble products diffuse across the stagnant layer back into the bulk of the liquid to complete the etching process. Physical interaction, such as sandblasting, is not a significant component of the wet etching process. Typically a deionized water rinse immediately follows the chemical wet etch to stop further etching of the film by removing any solution left on the surface of the substrate. The wet etching process is highly sensitive to the etchant temperature, reactant concentration, and sometimes humidity. Since the reactant concentration near the surface decreases during the etching process as the product concentration increases, it is a common practice to stir the substrate during the wet etch to allow a more uniform distribution of reactant throughout the solution, resulting in a more consistent etch rate across the substrate during the etch. Another purpose for the stirring is to remove air bubbles that can form during the wet etch. Since the by-product of the etching process can be gaseous and liquid, air bubbles may be trapped on the surface of the substrate, especially in a viscous etchant. A trapped air bubble forms a "soft" etching mask that prevents the film underneath it to be in contact with the liquid etchant, thus producing a non-uniform etching of the film across the entire substrate.

In the fabrication of our a-Si:H TFT, the chromium gate, hydrogenated amorphous silicon nitride encapsulation, and molybdenum source/drain contacts are etched by the following solutions: CR-14 Chromium Etchant ( $C_2H_4O_2$  and  $Ce\{NH_4\}_2\{NO_3\}_6$ ), buffered hydrofluoric acid (HF, NH<sub>4</sub>F, and H<sub>2</sub>O), and Aluminum Etch Type A ( $H_3PO_4$ , HNO<sub>3</sub>, and  $C_2H_4O_2$ ), respectively. In a few experiments, the a-Si:H and n+ a-Si:H are removed using potassium hydroxide (KOH).

#### **Chromium Wet Etch**

The reactions of the chromium etch, is shown below [1]:

$3\text{Ce}(\text{IV})(\text{NH}_4)_2(\text{NO}_3)_{6(\text{AQ})} + \text{Cr} \rightarrow \text{Cr}(\text{III})(\text{NO}_3)_{3(\text{AQ})} + 3\text{Ce}(\text{III})(\text{NH}_4)_2(\text{NO}_3)_{5(\text{AQ})}.$  (2-1)

Chromium etching of the gate can be quite unpredictable as the etch rate fluctuates with changes in temperature, humidity, and/or concentration of the etchant. Therefore we used test wafers before, during, and after the etching of the device wafers. Test wafers for this step were glass wafers with a sputtered chromium layer of identical thickness as the gate metal layer. Since the color of chromium is metallic gray, sputtering chromium on glass turns the wafer from transparent to opaque. During the etching of chromium-onglass wafers in CR-14, the glass testing wafers turned from opaque to transparent, then opaque again, and finally transparent. This transition to the second transparent phase indicated a complete removal of the chromium layer. We believed that the after the first transition, there was still a thin layer of chromium or chromium oxide, which could short the gate level patterns if remained on the surface. Upon the completion of the etching, test wafers were removed from the clean room for resistivity testing. Every gate level

etching required monitoring the etch rate on the test wafers before and after the etching of the device plates for quality control.

#### Silicon Nitride Wet Etch

The wet etching of a-SiN $_X$ :H in buffered hydrofluoric acid has the following chemical reaction:

$$Si_3N_4 + 12HF \rightarrow 3SiF_4 + 4NH_3.$$

(2-2)

The silicon nitride in the equation is deposited at high temperature (i.e. via LPCVD process), therefore the ratio between silicon and nitrogen (3:4) is well defined. For the low temperature PECVD nitride we used in our experiment, the reaction is similar, but the Si/N ratio may vary. During the BHF etch of the amorphous silicon nitride, the ammonium fluoride maintains

the HF concentration, thus the pH of the solution. This buffering mechanism keeps the BHF etch rate constant, at about 500Å/min at room temperature. Figure 2-20 shows the BHF etching rate test performed on G1 and G2.

Figure 2-11: Etching rate characterization plots for G1 and G2 silicon nitride.

#### **Amorphous Silicon Wet Etch**

Selective KOH etching of silicon has the following reaction [2]:

$$Si + 2KOH + H_2O \rightarrow K_2SiO_3 + 2H_2$$

(2-3)

At 353 K and 50 weight percent versus deionized water, the etch rate reaches above 1 µm/min [3]. Moreover, this process is highly sensitive to temperature, and the etch rate varies up to 10 %/K. In order to have better control of the etch rate, we lowered the etching temperature down to 323 K and the concentration down to 10 weight percent in deionized water. The etch rate using such formula is approximately 1200 Å/min. More details regarding silicon wet etch will be discussed in chapter 4.

#### **2.1.3 Dry Etch**

Dry etching, typically done in a plasma chamber, consists of two distinct mechanisms that occur simultaneously during the actual etching process: chemical and physical etchings. The chemical etching begins by breaking the molecules of the etchant gas into subspecies and free radicals via ionization. Typically, for a plasma generated by a specific precursor gas combination, there will be a variety of ions and particles present in the reactive ion etcher at the same time; the particle that is primarily participating in the etching process, however, is the free radical. The highly reactive free radicals chemically bond with the atoms in the layer to be etched, resulting in the formation of gaseous etching products. Table 2-1 lists some of the common precursor gases used in the etching of silicon, poly-silicon, and amorphous silicon. Since in chemical etching, the process is reaction-based, typically the selectivity is very high; the cost of this advantage is that lateral etching increases. As a result, the anisotropy decreases and we begin to observe undercut beneath the mask. To mitigate this phenomenon, the physical component of the dry etch is included. Contrary to the chemical etching by the free

radicals, physical etching begins with accelerating the ionized species in the plasma toward the substrate layer to be etched. Particles on the surface of the target film begin to depart upon impact of the collision. This sandblasting process produces side-wall deposition of non-volatile etching products, which inhibits the lateral etching by the reactive particles in the plasma. Effectively, physical etching constantly deposits sacrificial masking layers, which can be oxide-like or polymer-like, onto the side-walls during the dry etching process. Another effect of ion bombardment is that it "knocks lose" the atoms on the film's surface, making the chemical reaction occur more easily for the free radicals and the film; this lowers the activation energy of the chemical reaction between the etchant and the material of the target film.

Table 2-1: Common RIE etching recipe used for silicon transistor process.

| Material            | Etchant                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Reference                                                                                                                                                                                                                                                                              |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Silicon/<br>Poly-Si | 1. SF <sub>6</sub> /SF <sub>6</sub> +C <sub>2</sub> ClF <sub>5</sub> 2. SF <sub>6</sub> +C <sub>2</sub> Cl <sub>3</sub> F <sub>3</sub> 3. SF <sub>6</sub> +O <sub>2</sub> 4. SF <sub>6</sub> +H <sub>2</sub> /He/N <sub>2</sub> /O <sub>2</sub> /Ar 5. Cl <sub>2</sub> :O <sub>2</sub> (50:8) 6. HBr 7. HBr:O <sub>2</sub> (50:8) 8. HCl:O <sub>2</sub> (50:8) 9. CF <sub>4</sub> :CHF <sub>3</sub> :Ar:CO (20:30:300:150) 10. CF <sub>4</sub> :CHF <sub>3</sub> :Ar:C <sub>4</sub> F <sub>8</sub> | <ol> <li>Castan et al. [4]</li> <li>Yunkin et al. [5]</li> <li>Wells et al. and Syau et al. [6, 7]</li> <li>Arora et al. [8]</li> <li>Desvoivres et al. [9]</li> <li>Nakamura et al. [10]</li> <li>Wahlbrink et al. [11]</li> <li>Komeda et al. [12]</li> <li>Komeda et al.</li> </ol> |

| a-Si:H              | 1. SiCl <sub>4</sub> +Ar/CF <sub>4</sub> /O <sub>2</sub><br>2. HBr+Cl <sub>2</sub> +He+O <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                              | 1. Kuo <i>et al</i> . [13]<br>2. Yost <i>et al</i> . [14]                                                                                                                                                                                                                              |

| n+ a-Si:H           | 1. CF <sub>3</sub> Cl<br>2. CF <sub>2</sub> Cl <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1. Kuo <i>et al</i> . [15]<br>2. Kuo <i>et al</i> .                                                                                                                                                                                                                                    |

## SF<sub>6</sub> Etching of Silicon

For SF<sub>6</sub> etching of amorphous silicon, the primary reaction is [6-8]

$$Si + 2SF_6 \rightarrow SiF_4 + 2SF_4. \tag{2-4}$$

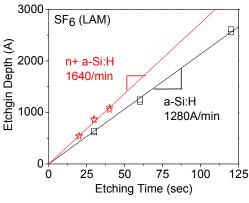

The fluorine radicals come from the dissociation of the  $SF_6$  molecules. Free radicals are highly reactive, and bond with the silicon atoms; both products in this reaction are volatile, and get pumped out of the plasma chamber quickly via the pump. During the plasma etch of silicon, superficial  $SiO_2$  can also be removed by the fluoride radicals to form oxyhalides [16]. This avoids the need to perform native oxide removal prior to the island etch process as  $SF_6$  etches both silicon dioxide as well as silicon.  $SF_6$  dry etching is highly reaction based, which means that the lateral etch can occur. We use the  $SF_6$  based chemistry to perform the island etch due to its high etch rate (figure 2-12). Since in our experiment a photo-resist layer was used as the mask, polymer residues may be left on the substrate after the etching. An oxygen plasma treatment, commonly known as an ashing process, can remove all the organic-based residues.

Figure 2-12: SF<sub>6</sub> etching rate characterization plots.

Figure 2-13: HBr etching rate characterization plots.

## **HBr Etching of Silicon**

Similarly, the etching of amorphous silicon using HBr has the following reaction [17]:

$$Si + 4HBr \rightarrow SiBr_4 + 2H_2. \tag{2-5}$$

The atomic bromine comes from the dissociation of the HBr molecule. HBr dry etching has a more than 200:1 selectivity between silicon and oxide [18]. In this case native oxide can impede the etching of the amorphous silicon, even if an HF dip is performed right before the dry etch. A breakthrough etch using Cl<sub>2</sub> is necessary to remove the native oxide, and expose the amorphous silicon layer for the main HBr etching. Throughout the dry etching process, some non-volatile by-product may be deposited on the side-wall, or the surface of the film to be etched. To prevent any micro-masking by the by-product, we include Cl<sub>2</sub> in our HBr etching recipe (with a 1-to-1 ratio) to constantly remove the by-product. This addition also increases the overall etch rate of the amorphous silicon. Our HBr recipe etches amorphous silicon at 400 Å/min and n+ amorphous silicon at 680 Å/min (figure 2-13).

In general, wet etching tends to show higher etching rate because of the higher concentration of etchant. It does not expose semiconductor films to plasma, which have been reported to degrade the electrical properties of the transistors. However, the downside to wet etching is its lack of anisotropy, or the direction of etching. A few solution-based etching, such as KOH used on silicon, does provide some directionality as KOH etches different planes of silicon at different etch rates. But in general it is difficult to control the anisotropy of the wet etch process. Dry etching on the other hand, provides much improved anisotropy due to the side-wall inhibitor deposition and the ion

bombardment. In terms of selectivity, both wet and dry etchings have benefits and shortcomings. Many wet etchants used in semiconductor processing are acid-based. While these etchants can have very high selectivity among the insulator and semiconductor films, they will, to some degree, attack the metallic films that are ubiquitous in the fabrication of thin-film transistors. An example is, HF, which is commonly used to etch SiO<sub>2</sub>, has a very high selectivity over silicon. However, HF also etches titanium (Ti), which is commonly used as the contact or inter-connect metal. Dry etchants, on the other hand, often etch insulator and semiconductor films at comparable rates, but rarely can etch metal effectively. It is thus important to take all these factors into consideration during the fabrication of a-Si:H TFT.

## 2.1.4 Dry and Wet Etching Non-Idealities

#### **Under-etch**

Under-etch occurs when the actual etching depth is smaller than the target etching depth. This leaves a layer of the target film on the surface, even though it is supposed to be removed entirely. Under-etch poses a very serious problem during the definition of the gate, n+ a-Si:H, and source/drain. Intuitively, it is obvious that the under-etching of any one of these layers leads to undesirable shorts in the amorphous silicon TFT. In the case of the chromium gate etch, residual chromium left on the substrate effectively shorts all the gates on the substrates together. An adverse outcome of under-etching the gate is that the transistors' gate level leakage is going to increase significantly. For the n+ a-Si:H layer, under-etching can lead to larger TFT off-current in both linear and saturation regimes of operation. Lastly, there is the catastrophic effect of the under-etching the

molybdenum source/drain contact. Any under-etching of the Mo layer leads to the shorting of the contacts together. A thin layer of Mo acts as a mask for the subsequent back channel etch process, which means that during the BCE, the etchant may not remove the n+ a-Si:H at all. This is especially true when we use KOH etching for the BCE of the a-Si:H TFT, because KOH does not etch molybdenum aggressively.

#### Over-etch

Contrary to an under-etch, an over-etch happens when the actual etching depth is larger than the target etching depth. Slight over-etch of the gate, source and drain, or the back channel will decrease gate and contact overlap because the undercut begins to diminish the area of the metal pads. One possible effect of this type of undercut is the raise in contact resistance. With a higher contact resistance the effective mobility can

Figure 2-14: Schematic of extra undercut caused by excess over-etch.

decrease as more drain voltage is dropped across the contact. A severe case of contact resistance degradation caused by large undercut is that the source and drain contacts no longer behave as ohmic contacts. When this happens, the source and drain terminals become schottky contacts. Another over-etch problem that is exclusive to the back channel etch process is the degradation of the device characteristics. When performing the back channel etch, it is imperative to control the etching depth of the n+ a-Si:H and a-Si:H layers to prevent over-etch. The effect of over-etching of the a-Si:H film will be discussed in chapter 4.

#### Mask Erosion

In some cases the etchant attacks the mask used to define the features. If the etchant is not perfectly anisotropic, then it will etch laterally into the mask. An example of this is the oxygen plasma ashing the photo-resist mask during an RIE process. Mask erosion distorts the features of the device. It may produce tapered profile and/or excessive undercut. Mask erosion often takes place during dry etch, where the etching selectivity between the film and the mask tends to be lower than wet etching. If the plasma etching includes oxygen as one of the precursor gases, there certainly will be some photo-resist mask erosion. The effect of mask erosion on the film is similar to over-etching, where there is an increase in the undercut. In our process, both gate and source/drain processes use acid based solutions to etch the respective profiles. Since acid can attack photoresist, unwanted lateral etching of the metallic contacts can occur as a result of mask erosion. This may decrease the gate and source/drain overlap area, which in turn increases the contact resistance of the TFT.

Figure 2-15: Schematic of extra undercut caused by mask erosion.

## 2.1.5 Etch Process Control

Even with carefully characterized etch rate, there are many factors that can lead to non-ideal etching of the device film. As mentioned before, such non-ideality can degrade device performance, or lead to device failure. To prevent such mishap from happening, we use additional ways to detect, mitigate, or even resolve the problems.

#### **End Point Detection - RIE**

Some modern reactive ion etchers are equipped with end point detection systems. Such systems detect film color change due to the thickness change, or the product gas concentration. Film color changes with thickness because of interference effect; the detail is discussed in many books regarding semiconductor processing such as <u>Silicon</u>

<u>VLSI Technology</u> by Plummer, Deal, and Griffin, and will not be reiterated here [19]. The second type of end point detection detects the concentration of product gas originated from the reaction between the etchant and the film. This technology relies on the difference in plasma etching chemistry between the film to be etched and the underlying film. Optical detectors measure the concentration of the etchant product releasing from the surface of the film during the plasma etch. Once the film is etched through, the etchant begins to react with the exposed underlying film, and the etching products change. This change in gaseous product is detected by optical detectors, and alerts users. End point detection is very useful during the island etch, because the films we try to etch are a-Si:H and n+ a-Si:H, and the underlying film is a-SiN<sub>X</sub>:H. We observe a drastic change in output gas concentrations when we etch through the two target layers. LAM 9400 possesses end point detection based on product gas concentration.

#### Over-etch

The most common method to avoid problems caused by the under-etching of the film is over-etching. Typically we perform 5-10 % over-etch to ensure etching through of the film, except for the back channel etch. This over-etch reduces the possibility of under-etching caused by the loading effect, or other unexpected variations that occur before and during the etching process. During the gate and source/drain metallization, we routinely carry out a 5 % over-etch.

#### **Use of Test Wafers**

On top of all the quality control techniques mentioned above, it is still a good idea to use test wafers for all the etching processes. Test wafers have identical films compositions, lithographic patterns, and thicknesses as the device wafers; they are being etched concurrently with the device wafers. These are used to measure the depth of the etching process, without removing the etching masks on the device wafers. The assumption is that the etching depth of the test wafer is the same as the device wafer, and as long as the etching uniformity is high during the process, test wafers are very useful to detect under-etching. For every thin-film deposition, photolithography, and etching step in this dissertation, we use test wafers to improve the accuracy and reliability of the fabrication process.

#### 2.2. TFT Fabrication Process

Our devices were fabricated on 4" oxidized silicon substrates with 10kÅ of thermally grown wet oxide. All photolithography steps were performed on a Karl Suss MA-6 Aligner using 5" chromium/quartz masks. The names of the masks are included in curly brackets for rest of this section; the critical dimension (CD) for all the masks are below 0.5 µm. We used 1.5 µm of Shipley 1813 photo-resist (PR) as the etching mask for all the wet etching steps, and 3 µm of Shipley 1827 photo-resist for the dry etching steps. Prior to the deposition of a new layer of material or photo-resist, we rinsed the surface with acetone, isopropyl alcohol (IPA), and deionized water (DI), and cleaned in a spin-dryer to dry the wafers. This procedure removed dust and organic contaminants that may be present on the surface. It is especially important to perform this cleaning step before

photolithography, as any particulate on the surface creates streaks during the spin-coating of the photo-resist layer, causing non-uniform deposition of photo-resist. We developed (spinning) the photo-resist for 30 s in the metal-ion free (MIF) 319 developer using the ACS cluster tool. Emersion development could also be used, but the time should be increased. In order to prevent residual photo-resist left in the corner of any features, also known as "feet," we descummed the substrates for 30 s after each PR development. In any processing step that involves dry etching, the photo-resist layer was not hard-baked after the development to avoid cracking and reflowing of the film upon exposure to shortwave radiation and ions; for the photo-resist layer used as the mask during wet etching, we performed a hard-bake for 1 min at 388 K. This hard-bake removes extra solvent in the film in order to increase its structural stability and etching resistance. The removal of the photo-resist films after each fabrication process comprised of soaking the substrate in heated PRS-2000 solvent for 20 min, and an oxygen-plasma ashing for 5 min in the March Asher. The ashing condition is 250 mTorr, 250 W, and 17 % O<sub>2</sub> flow. It is absolutely essential to ash the photo-resist in addition to the PRS-2000 bath because both the radiation and dry etch by-product can leave insoluble residue on the surface of the film, making it difficult for the PRS-2000 to completely remove the photo-resist film. Throughout the entire fabrication of the device wafers, dummy wafers with identical films thicknesses and processing conditions were used in each step to ensure the quality and control of the amorphous silicon transistors. At the end of each subsection we will show the alignment marks, top-view picture, and schematic cross-section of the TFT at each step of the fabrication process.

## 2.2.1 Gate Metal Sputtering and Patterning

The TFT gate comprised of 2000 Å of sputtered chromium, which was deposited by an Enerjet Sputter at a rate of 270 Å/min on a rotational planetary platform (20 rpm). The deposition was done with a base pressure of at most  $5 \times 10^{-6}$  Torr, sputtering pressure of 7 mT, argon flow rate of about 40 sccm, and d.c. current of 3 A for 440 s. Subsequently, we lithographically patterned {GATE} and etched the gate metal using chromium etch (etch rate =  $\sim 1000$  Å/min at 323 K). One observation worth noting is that the sputtered chromium can form a transparent conductive oxide on the surface of the substrate; a few extra seconds of etching was necessary after the apparent removal of the chromium metal to ensure proper electrical insulation among the features on the substrate. Figure 2-16 shows the first level alignment marks: the cross and the surrounding windows are used for the alignment, and the Vernier marks on the top and the left are used to determine the degree of misalignment among different levels of photolithography. Gate level patterning includes all the gates for the TFTs, as well as the bottom electrode for the storage capacitors in the pixel electrode circuit. Figure 2-17

Figure 2-16: Gate level alignment and Vernier marks.

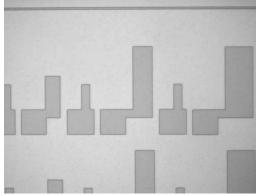

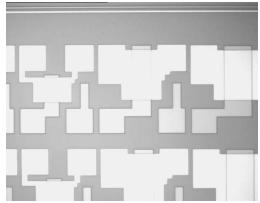

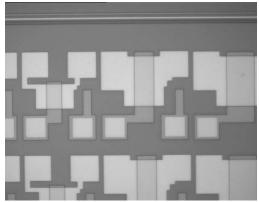

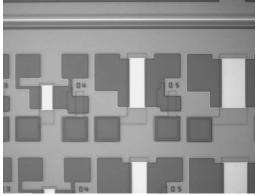

Figure 2-17: Example of TFT structures after the gate patterning.

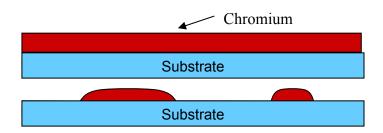

shows the top-view of an example of thin-film transistor's gate level pattern after the completion of the chromium wet etching, and figure 2-18 shows the corresponding schematic cross-section of the TFT.

Figure 2-18: Schematic cross-section of the TFT gate metal sputtering and patterning process.

# 2.2.2 Plasma Enhanced Chemical Vapor Deposition

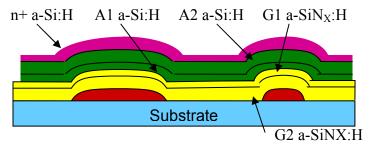

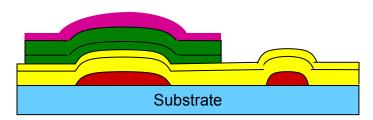

The novel amorphous silicon thin-film transistor with the tailored channel comprises of two layers of gate insulator and two layers of active material. A plasma enhanced chemical vapor deposition (PECVD) system for the commercial production of flat-panel display was used to deposit the gate insulator, amorphous silicon, and the contact layer. We deposited 3500Å of N-rich hydrogenated amorphous silicon nitride (a-SiN<sub>X</sub>:H) at a rate of 1800 Å/min (G2) and 500Å of a-SiN<sub>X</sub>:H at 900 Å/min (G1) as the gate insulator. Next, we deposited two layers of a-Si:H films: one at 600 Å/min (A1), and the second at 1200 Å/min (A2). A variety of plates with the following A1/A2 layer thicknesses ( $t_{A1}/t_{A2}$ ) have been fabricated: 1700/0 Å, 1600/100 Å, 1500/200 Å, 1400/300 Å, 1300/400 Å, 1200/500 Å, 1100/600 Å, and 0/1700 Å. Lastly 700 Å of 1 % phosphorous-doped amorphous silicon (n+ a-Si:H) was deposited at a uniform rate [20]. A 1000 Å of G2 encapsulation was deposited on top of the three layers to protect them

from oxygen, moisture, and organic contaminant. The film would be removed in buffered hydrofluoric acid (BHF) immediately prior to subsequent processing steps to minimize contamination (figure 2-19). The bi-layer a-SiN<sub>X</sub>:H surface roughness (RMS value) above the gate dielectric is about 1.1 nm. Both films have slightly different film stoichiometry, but are both N-rich (N/Si > 1.3); the Si-H content in the gate dielectric deposited at lower rate is rather small (< 0.5 %). Total hydrogen content in the silicon nitride deposited at the higher rate ( $\sim$ 36 $\pm$ 4%) is significantly larger in comparison to the film deposited at the lower rate ( $\sim$ 28.5 $\pm$ 1.5%). The Tauc optical gaps for the film deposited at the higher and lower rates are about 4.6 and 5.2 eV, respectively.

Figure 2-19: Schematic cross-section of the PECVD of G2 and G1 a-SiN<sub>X</sub>:H, A1 and A2 a-Si:H and n+ a-Si:H films for the TFT.

#### 2.2.3 Island Patterning

After the removal of sacrificial nitride, the island was defined {ISLAND} by photolithography, and etched with a  $SF_6+Cl_2+O_2+He$  (6:24:20:5) plasma in a LAM-9400 Transformer Coupled Plasma Reactive Ion Etcher<sup>TM</sup> (TCP-RIE). The selectivity between a-Si:H and a-SiN<sub>X</sub>:H is approximately 21:1 for this chemistry, and with precise control of the etch time, minimal etching of the gate insulator during the definition of the amorphous silicon island can be achieved. We show the gate-to-island level alignment

mark, the top-view, and schematic cross-section view of the TFT structures after the island patterning in figures 2-20, 2-21, and 2-22, respectively.

Figure 2-20: Gate-to-Island level alignment and Vernier marks.

Figure 2-21: Example of TFT structures after the island patterning.

Figure 2-22: Schematic cross-section of the TFT island patterning step.

#### 2.2.4 Gate Via Patterning

The gate via was then patterned  $\{VIA\}$  and etched in a PlasmaTherm Reactive Ion Etcher (PT-RIE) with a CF<sub>4</sub>+O<sub>2</sub> (20:1) plasma. The etch rate is 760 Å/min and we performed a 10% over-etch to ensure that the gate via reaches all the way to the gate pad for proper electrical contact with the molybdenum to be sputtered later. However, in the middle of the etching process, wafers were rotated 180° in the reactive ion etcher to