# Nano-structured InGaN Light-Emitting Diodes for Solid-State Lighting

by

# **Taeil Jung**

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2009

# **Doctoral Committee:**

Assistant Professor P. C. Ku, Chair Professor Pallab K. Bhattacharya Professor Rachel S. Goldman Associate Professor L. Jay Guo

To my wife, son, and daughter for their love and support

# ACKNOWLEDGMENTS

Looking back at the long journey toward this point in my academic career, I am indebted to many people for their help. Although there are too many people to list, I feel that there are some people who must be mentioned by name.

I would first like to give sincere acknowledgement to my advisor, Professor P. C. Ku, for his guidance, support, and patience during my doctoral study. He led me to the exciting world of optoelectronics, from device physics to applications. With his advice, I can continue pursuing interesting research topics such as material growth, device fabrication, and characterization, especially in III-Nitride materials. In addition, I would like to thank my committee members -- Professor Pallab Bhattacharya, Professor Rachel Goldman, and Professor Jay Guo -- for their valuable suggestions and comments on my research.

I really want to thank my colleagues, Min Kim and Luke Lee, for their help with my studies. Wille Bowen and Weiming Wang in Professor Phillips' group and Debashish Basu and Zhang Meng in Professor Bhattacharya's group helped me greatly on optical and electrical measurements. I also thank my friend David Aplin, former Thomas Swan engineer and staff research associate in UCSB, for his invaluable guidance which

deepened my knowledge and understanding of III-Nitride material growth and MOCVD systems. Ken Hess in Thomas Swan guided me in terms of understanding and maintaining the MOCVD. I appreciate Dennis Schweiger, LNF senior research supervisor, for his important assistance on MOCVD maintenance. I would like to thank Kai Sun, Haiping Sun, and Ying Qi in EMAL for their help and support for SEM and TEM imaging and XRD characterization. I enjoyed working with my former group members, Yi-Hao Chen, Geonwook Yu, and Dr. Hongbo Yu. The Korean graduate students of EECS also have made my time profitable.

I always owe a great deal to my Lord, Jesus Christ. Taking this opportunity, I also thank all of my friends of the Korean Bible Church of Ann Arbor for their love and fellowship. I will not forget enjoyable times with the families of my friends Suhan Choi, Ilju Na, Seunghyun Jung, Kyungsup Shin, and Kwangwon Lee. Their friendships filled my life with happiness and joy, which made an impact on my studies.

Last, I want to thank all my family members including my parents, my brother, my parents-in-law, and my brother-in-law. Without their unconditional love, support, and prayer, I could never have achieved this goal. Finally, I deeply thank my lovely wife, Sungsil, my son Jiwon, and my daughter Jihyo for their love, patience, and support. I especially dedicate all my work at the University of Michigan to my wife from the bottom of my heart.

# TABLE OF CONTENTS

| DEDICATION                                                                | ii   |

|---------------------------------------------------------------------------|------|

| ACKNOWLEDGMENTS                                                           | iii  |

| LIST OF FIGURES                                                           | viii |

| LIST OF TABLES                                                            | xii  |

| LIST OF ABBREVIATIONS                                                     | xiii |

| ABSTRACT                                                                  | xvi  |

| CHAPTER 1                                                                 |      |

| INTRODUCTION                                                              | 1    |

| 1.1 GALLIUM NITRIDE MATERIALS FOR OPTOELECTRONIC APPLICATIONS             | 1    |

| 1.2 InGaN LEDs FOR SOLID-STATE LIGHTING                                   | 3    |

| 1.3 LIMITING FACTORS FOR InGaN LEDs EFFICIENCY                            | 4    |

| 1.3.1 Materials Defects                                                   | 5    |

| 1.3.2 Polarization Charges                                                | 6    |

| 1.3.3 Photon Extraction.                                                  | 8    |

| 1.4 ORGANIZATION OF THE THESIS                                            | 9    |

| CHAPTER 2                                                                 |      |

| METAL-ORGANIC CHEMICAL VAPOR DEPOSITION FOR GALLIUM NITRIDE OPTOLECRONICS | 11   |

| 2.1 GALLIUM NITRIDE GROWTH                                                                              | 11 |

|---------------------------------------------------------------------------------------------------------|----|

| 2.1.1 GaN Growth Using MOCVD                                                                            | 13 |

| 2.1.2 GaN Doping                                                                                        | 26 |

| 2.2 InGaN QUANTUM WELLS                                                                                 | 31 |

| 2.2.1 InGaN Quantum Well Growth Optimization                                                            | 32 |

| 2.3 SUMMARY                                                                                             | 36 |

| CHAPTER 3                                                                                               |    |

| SEMI-POLAR InGaN LEDs USING SELECTIVE AREA EPITAXY                                                      | 38 |

| 3.1 FABRICATION OF INGAN <i>SEMI-</i> POLAR LEDs USING SELECTIVE AREA EPITAXY                           | 39 |

| 3.2 OPTICAL PROPERTIES OF InGaN SEMI-POLAR MQWs                                                         | 41 |

| 3.3 SUMMARY                                                                                             | 44 |

| CHAPTER 4  NANO-STRUCTURED <i>SEMI</i> -POLAR GALLIUM NITRIDE TEMPLATES USING <i>IN SITU</i> PROCESSING | 45 |

| 4.1 <i>IN SITU</i> SILANE TREATMENT                                                                     | 46 |

| 4.1.1 Overview of <i>In Situ</i> Silane Treatment                                                       | 46 |

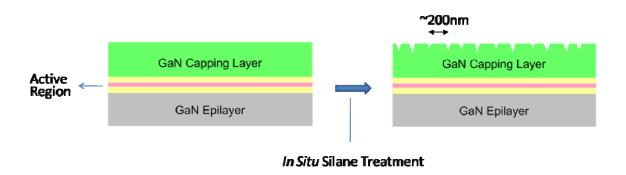

| 4.1.2 Formation of Nano-structured GaN Surface                                                          | 47 |

| 4.1.3 Mechanism of <i>In Situ</i> Silane Treatment                                                      | 51 |

| 4.1.4 Threading Dislocation Density Reduction Using <i>In Situ</i> Silane Treatment                     | 58 |

| 4.2 HIGH TEMPERATURE OVERGROWTH                                                                         | 60 |

| 4.2.1 Formation of Nano-structured Semi-polar Plane                                                     | 60 |

| 4.3 OPTICAL PROPERTIES OF NANO-STRUCTURED GaN                                                           | 62 |

| 4.3.1 Properties of <i>In Situ</i> Silane Treatment Treated GaN Template                                | 62 |

| 4.3.2 Optical Properties of Nano-structured Semi-polar GaN Template                                     | 64 |

| 4 4 SUMMARY                                                                                             | 66 |

# CHAPTER 5

| NANO-STRUCTURED SEMI-POLAR InGaN LEDs                                 | 67  |

|-----------------------------------------------------------------------|-----|

| 5.1 InGaN/GaN ACTIVE REGION ON NSSP GaN                               | 68  |

| 5.1.1 NSSP InGaN/GaN MQWs                                             | 68  |

| 5.1.2 NSSP InGaN/GaN LEDs                                             | 75  |

| 5.2 SUMMARY                                                           | 80  |

| CHAPTER 6                                                             |     |

| CURRENT SPREADING IN NANO-STRUCTURED <i>SEMI</i> -POLAR InGaN<br>LEDs | 82  |

| 6.1 STAIRCASE-LIKE DOPING PROFILES                                    | 83  |

| 6.2 GRADED DOPING PROFILES                                            | 87  |

| 6.3 SUMMARY                                                           | 92  |

| CHAPTER 7                                                             |     |

| IMPROVING PHOTON EXTRACTION USING NANO-STRUCTURED GaN                 | 93  |

| 7.1 NANO-STRUCTURED InGaN/GaN LIGHT EMITTERS                          | 94  |

| 7.1.1 Epitaxial Growth                                                | 95  |

| 7.1.2 LED Fabrication.                                                | 97  |

| 7.2 SUMMARY                                                           | 100 |

| CHAPTER 8                                                             |     |

| CONCLUSIONS AND FUTURE WORK                                           | 102 |

| 8.1 RESEARCH SUMMARY                                                  | 102 |

| 8.2 FUTURE WORK                                                       | 106 |

| APPENDICES                                                            | 108 |

| RIBI IOGRAPHY                                                         | 113 |

# LIST OF FIGURES

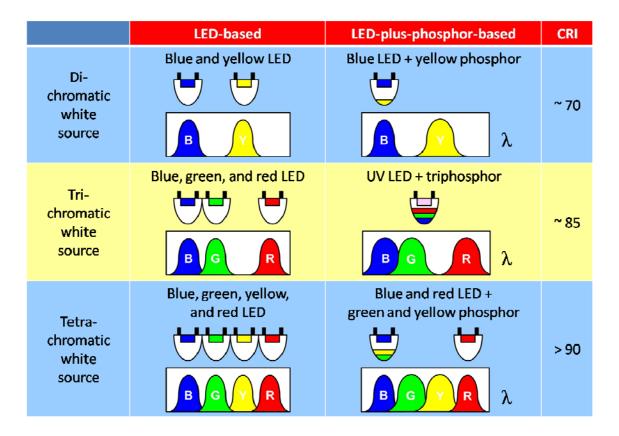

| Figure 1-1. Illustration of various potential white-light LEDs configurations                                                                                                                 | 4    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

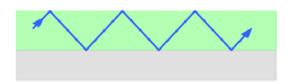

| Figure 1-2. Light traveling within waveguides (left) with a smooth interface and (right with a rough interface                                                                                | _    |

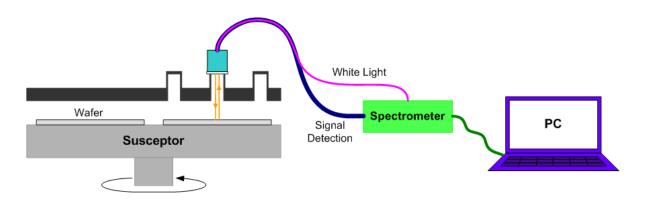

| Figure 2-1. Illustration of a home-made <i>in situ</i> reflectometry system integrated into the MOCVD system.                                                                                 |      |

| Figure 2-2. Typical growth conditions for GaN templates used in this research                                                                                                                 | . 14 |

| Figure 2-3. <i>In situ</i> reflectometry trace of GaN template growth                                                                                                                         | 15   |

| Figure 2-4. The comparison of GaN template qualities with respect to the reflection rabetween the LT NL surface and the sapphire substrate                                                    |      |

| Figure 2-5. Comparison of reflectance data for three different samples                                                                                                                        | 23   |

| Figure 2-6. Two different growth parts in HT GaN growth                                                                                                                                       | . 24 |

| Figure 2-7. The dependence of the growth rate on (a) TMG flow, (b) NH <sub>3</sub> flow, and (c) V/III ratio at given TMG flow and NH <sub>3</sub> flow, and (d) growth temperature           | _    |

| Figure 2-8. Relationship between the carrier mobility and the doping concentration in silicon doped n-type GaN (GaN:Si).                                                                      | 27   |

| Figure 2-9. Doping concentration and carrier mobility with respect to the silane vapor phase mole fraction ([Si]/[TMG]) and the growth rate (Gr; μm/hour) in n-type GaN:Si.                   |      |

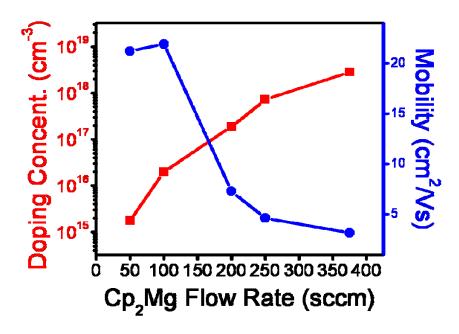

| Figure 2-10. Measured doping concentration and carrier mobility of p-type GaN:Mg f different Cp <sub>2</sub> Mg flow.                                                                         |      |

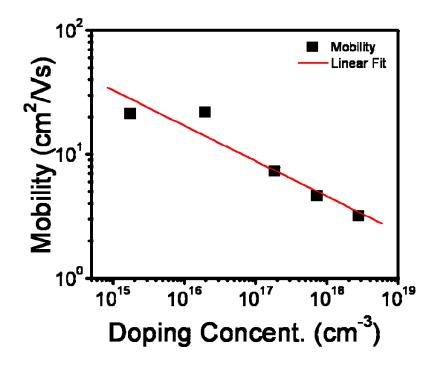

| Figure 2-11. Mobility vs. doping concentration of p-type GaN:Mg                                                                                                                               | 29   |

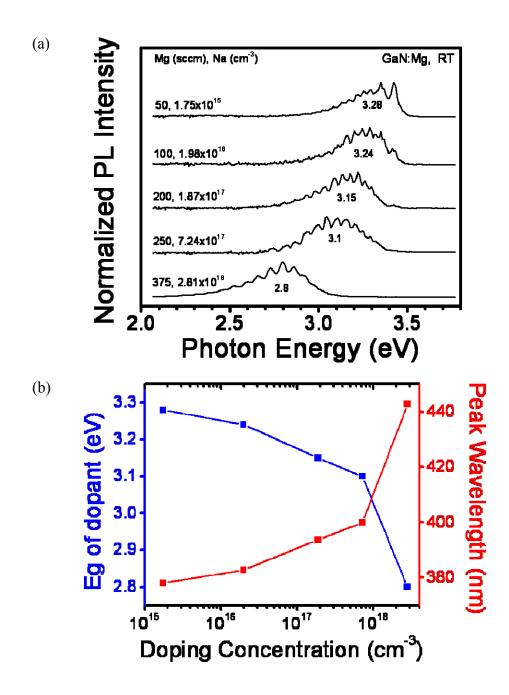

| Figure 2-12. Optical properties of GaN:Mg with different carrier concentration; (a) rot temperature PL spectra and (b) the Mg-related PL peak with respect to different doping concentrations |      |

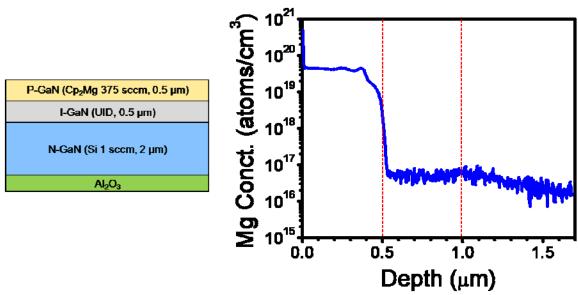

| Figure 2-13. As-grown PIN structure (left) and the corresponding SIMS analysis (right).                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-14. PL measurement data of the QWs grown at different growth temperatures 35                                                                                                                                   |

| Figure 2-15. PL measurement data of the QWs grown with different indium vapor-phase mole fractions at two different growth temperatures                                                                                 |

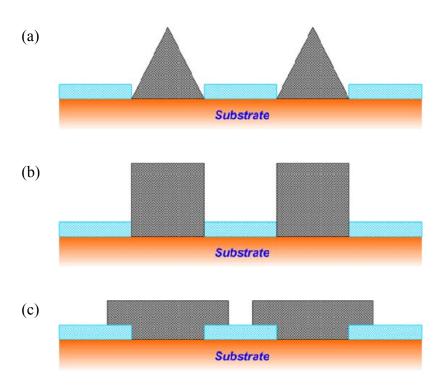

| Figure 3-1. Schematics of three possible SAE regrowth topologies: (a) triangular cross section, (b) vertical side wall type 1, and (c) vertical side wall type 2                                                        |

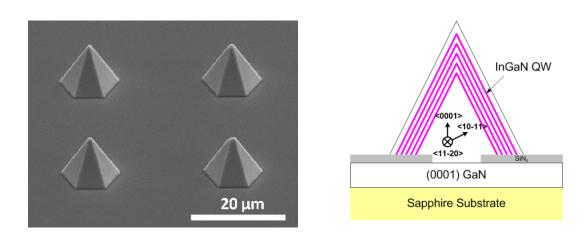

| Figure 3-2. (Left) SEM image of the generated {10-11} <i>semi</i> -polar planes using SAE; (Right) Schematic of five MQWs grown on {10-11} <i>semi</i> -polar planes                                                    |

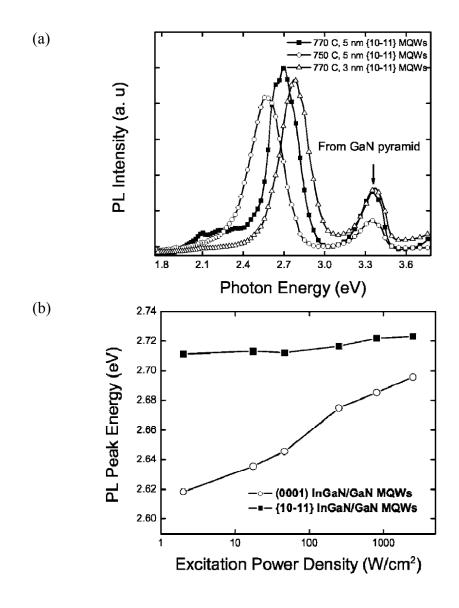

| Figure 3-3. (a) RT PL measurement data of the three samples and (b) RT excitation dependent PL measurement showing reduced QCSE in {10-11} <i>semi</i> -polar InGaN MQWs                                                |

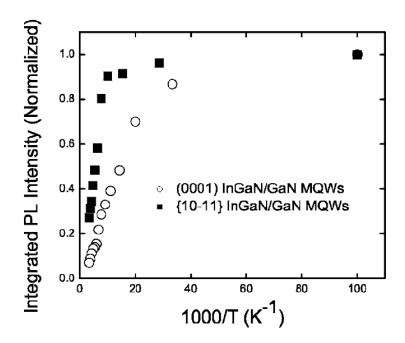

| Figure 3-4. Temperature dependence of the integrated PL intensity for both (0001) and {10-11} InGaN/GaN MQWs. The intensities are normalized to their values at 10 K.                                                   |

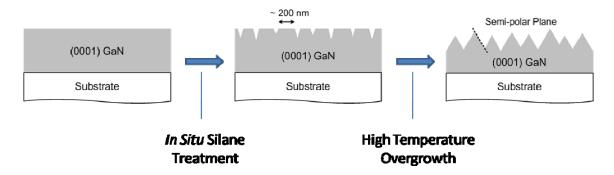

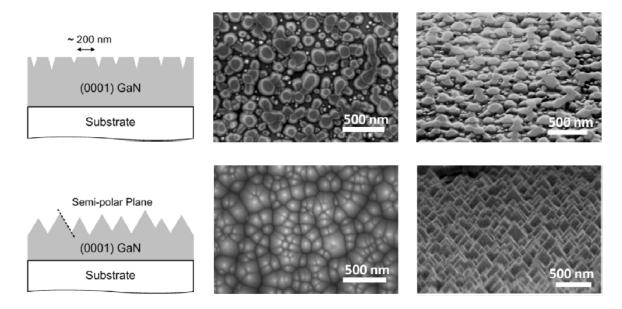

| Figure 4-1. Illustration of <i>in situ</i> silane treatment and high temperature overgrowth for nano-structured <i>semi</i> -polar GaN templates                                                                        |

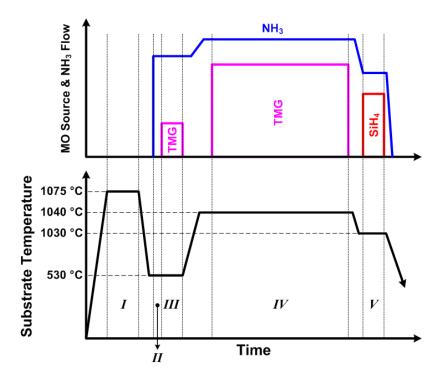

| Figure 4-2. Growth conditions used for the combined GaN template growth and ISST process. 48                                                                                                                            |

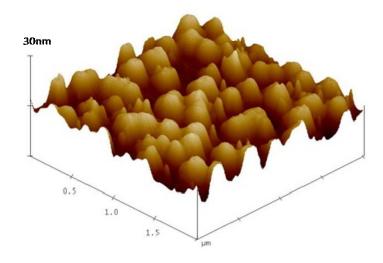

| Figure 4-3. AFM image of 150 sec ISST-treated sample. 49                                                                                                                                                                |

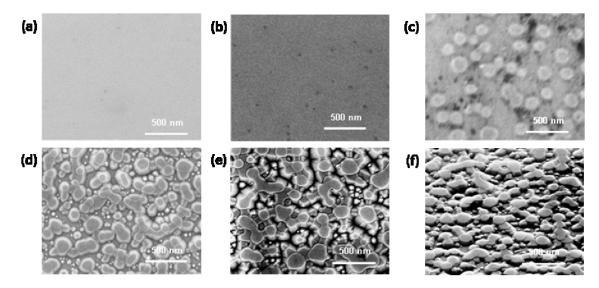

| Figure 4-4. SEM images showing the surface morphology of ISST-treated samples with different ISST times (a) 0 sec, (b) 60 sec, (c) 150 sec, (d) 300 sec, (e) 600 sec, and (f) the bird's eye view of the 300 sec sample |

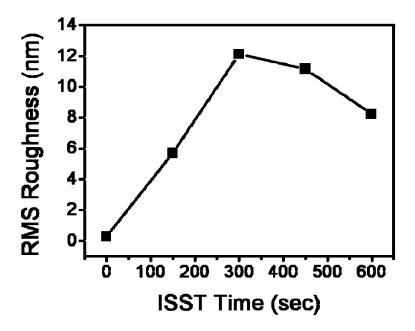

| Figure 4-5. RMS surface roughness versus ISST time. 50                                                                                                                                                                  |

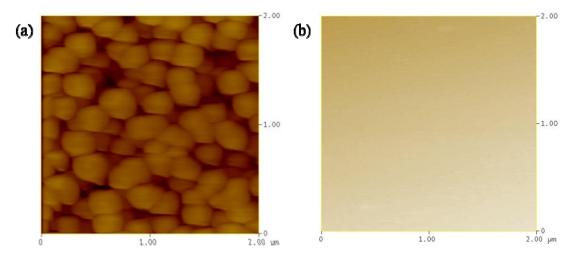

| Figure 4-6. AFM images of two samples: (a) ISST for 5 min and (b) ISST but no SiH <sub>4</sub> flow for 5 min                                                                                                           |

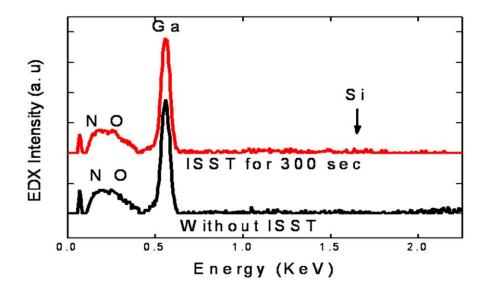

| Figure 4-7. EDX data of two samples, one with 5 min ISST and the other without ISST.                                                                                                                                    |

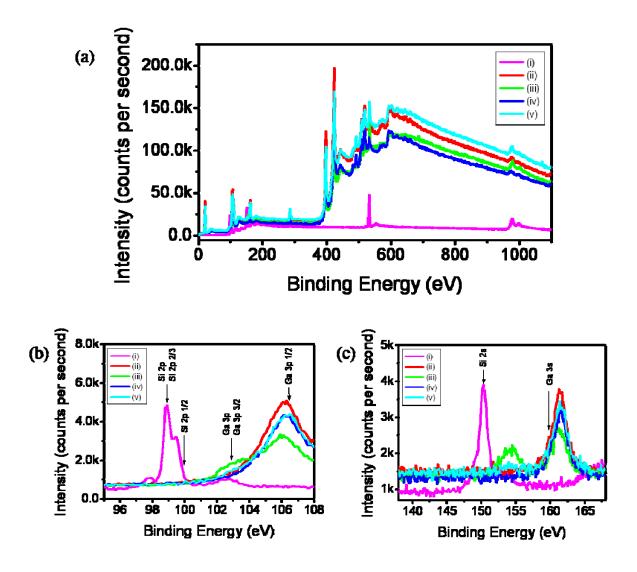

| Figure 4-8. XPS data of the samples: (i) Si (111) wafer, (ii) GaN template, (iii) 1.2 nm SiN <sub>x</sub> on GaN, (iv) 5 min ISST without SiH <sub>4</sub> flow, and (v) 5 min ISST on GaN 55                           |

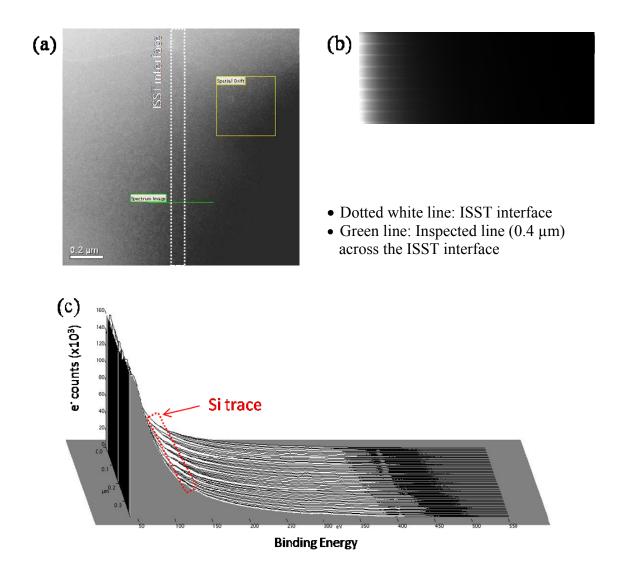

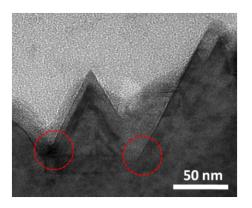

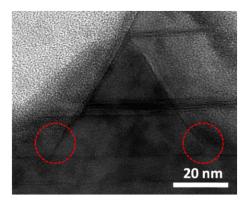

| Figure 4-9. EELS analysis: (a) TEM image of inspected region, (b) EELS spectrum, and (c) EELS data.                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

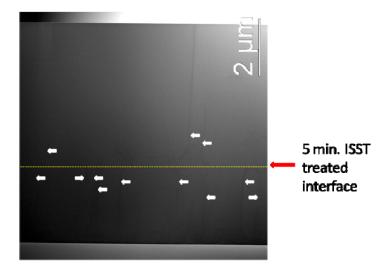

| Figure 4-10. TEM image showing TD density reduction above the ISST-treated interface.                                                                                                      |

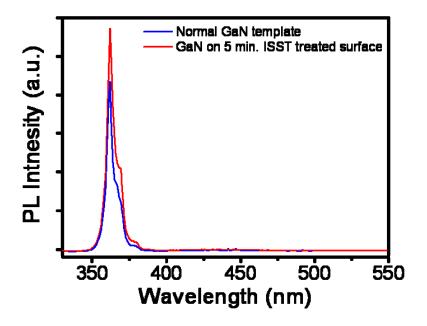

| Figure 4-11. Photoluminescence comparison of a normal GaN template to a GaN overlayer grown on a 5-minute ISST-treated surface.                                                            |

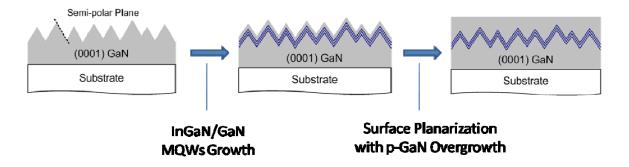

| Figure 4-12. Illustrations of the NSSP plane formation: surface morphologies after 5 min ISST and after HTO                                                                                |

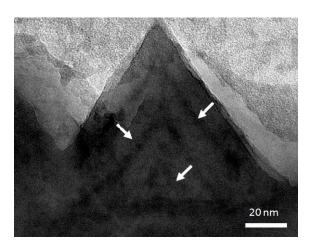

| Figure 4-13. TEM images showing the cross section of NSSP GaN template. Two crystal angles are observed: 62.5° and 57.2° which correspond to (10-11) and (11-22) <i>semi</i> -polar planes |

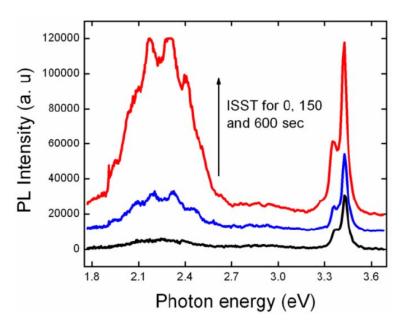

| Figure 4-14. Room temperature photoluminescence of ISST-treated GaN templates with different ISST times.                                                                                   |

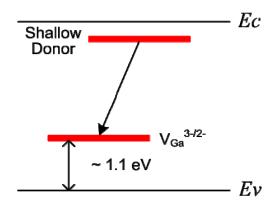

| Figure 4-15. Illustration of a possible origin for yellow band emission in GaN                                                                                                             |

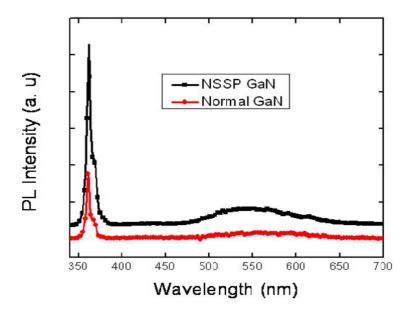

| Figure 4-16. Room temperature photoluminescence spectra of NSSP GaN template and normal <i>c</i> -plane GaN template                                                                       |

| Figure 5-1. Illustration of an NSSP InGaN LED fabricated on NSSP GaN template 68                                                                                                           |

| Figure 5-2. Cross-sectional TEM image showing NSSP MQWs                                                                                                                                    |

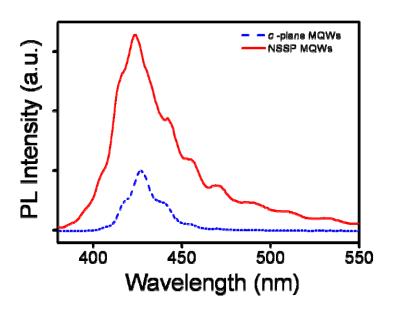

| Figure 5-3. Photoluminescence intensity comparison of NSSP and polar MQWs at room temperature                                                                                              |

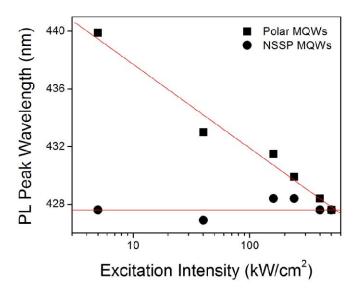

| Figure 5-4. Photoluminescence peak wavelength as a function of excitation intensity. The two straight lines are for guides only.                                                           |

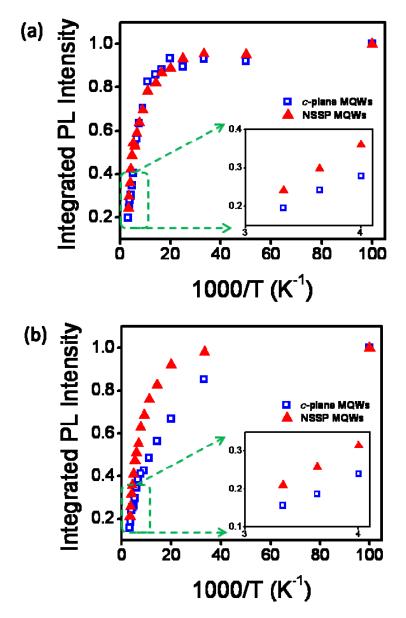

| Figure 5-5. Arrhenius plots obtained from temperature dependent PL for NSSP and polar samples with excitation intensity of (a) 5 kW/cm <sup>2</sup> and (b) 500 kW/cm <sup>2</sup>         |

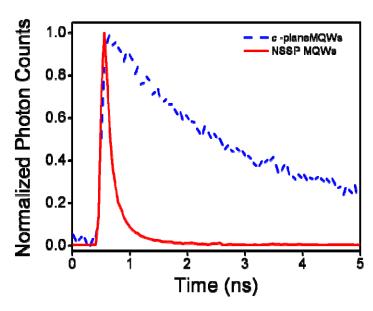

| Figure 5-6. Comparison of room temperature TRPL between NSSP and polar MQWs 75                                                                                                             |

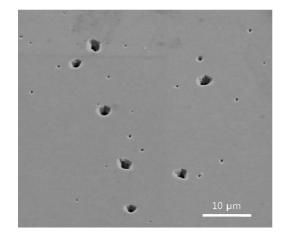

| Figure 5-7. SEM image to show the surface morphology after p-GaN planarization 76                                                                                                          |

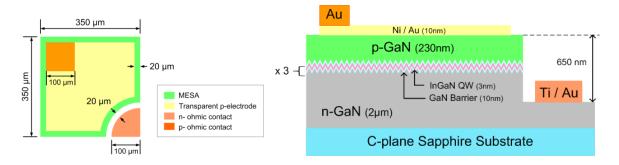

| Figure 5-8. Device structure of NSSP LED grown on <i>c</i> -plane sapphire substrate                                                                                                       |

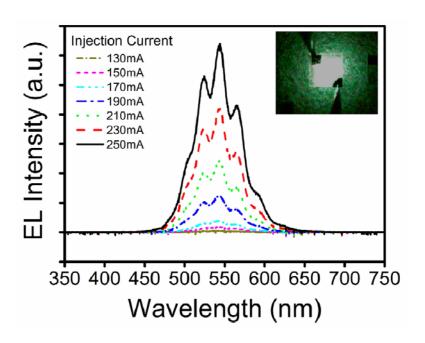

| Figure 5-9. Electroluminescence spectra of NSSP LED for different injection currents. 78                                                                                                   |

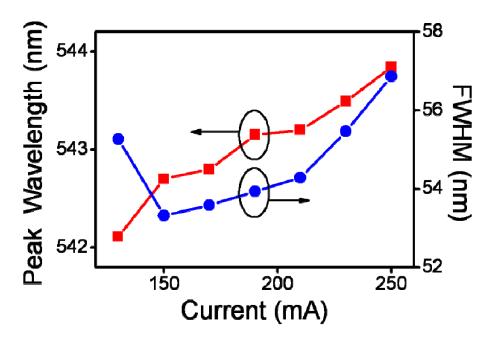

| Figure 5-10. Peak wavelength and FWHM linewidth of EL spectra in NSSP LED 79                                                                                                               |

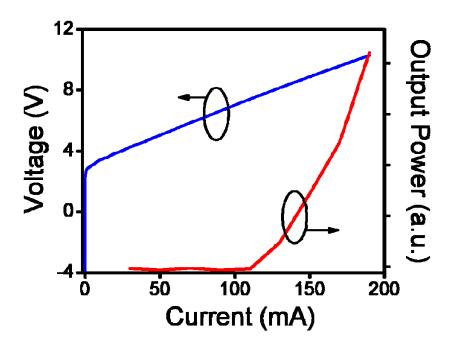

| Figure 5-11. L-I and I-V curves of NSSP LED.                                                                                                                                                                                                                                                                                   | 79  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

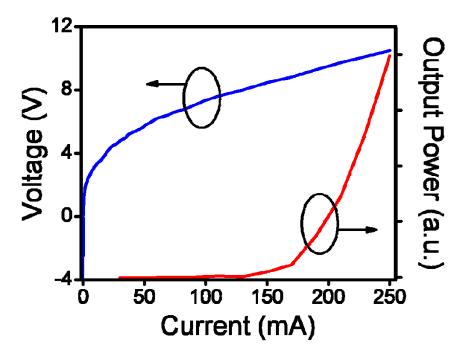

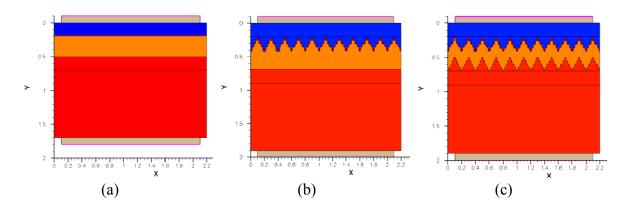

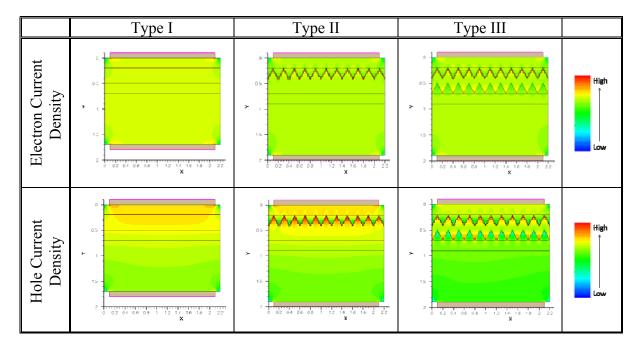

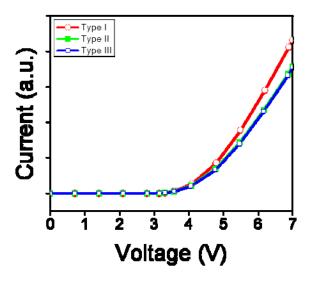

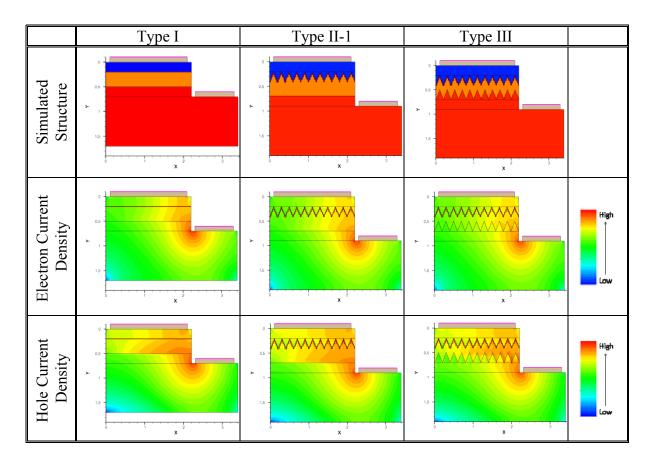

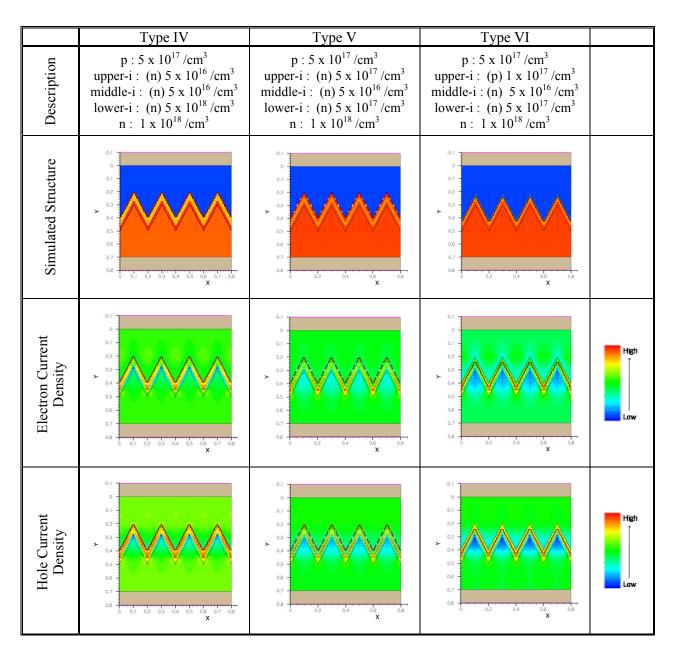

| Figure 6-1. Electrical characteristics simulated using Synopsys Sentaurus for three different p-i-n structures consisting of p-type GaN (blue), unintentionally-doped GaN (orange), and n-type GaN (red); (a) Type I: planar p-i-n, (b) Type II: p-i-n w NSSP interface between i and p, and (c) Type III: p-i-n on NSSP plane |     |

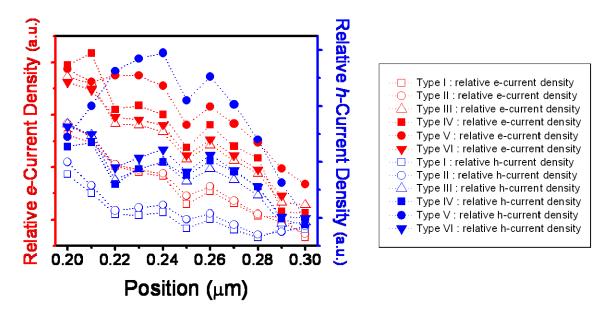

| Figure 6-2. The calculated electron and hole current densities for the three p-i-n structure.                                                                                                                                                                                                                                  |     |

| 1 iguic 0-2. The calculated electron and note current densities for the three p-1-ii struct                                                                                                                                                                                                                                    |     |

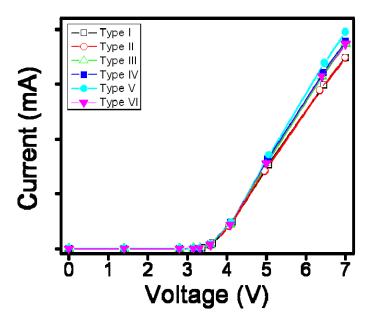

| Figure 6-3. Calculated IV curves for Type I, Type II, and Type III                                                                                                                                                                                                                                                             | 85  |

| Figure 6-4. Calculated p-i-n mesa structures, electron and hole current densities for the simulated structures, Type I, Type II, and Type III                                                                                                                                                                                  |     |

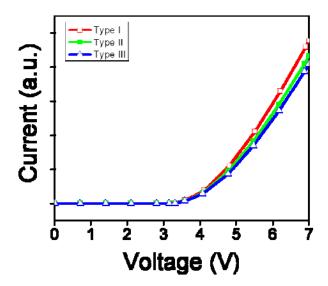

| Figure 6-5. Calculated IV curves for p-i-n mesa structures, Type I, Type II, and Type                                                                                                                                                                                                                                          |     |

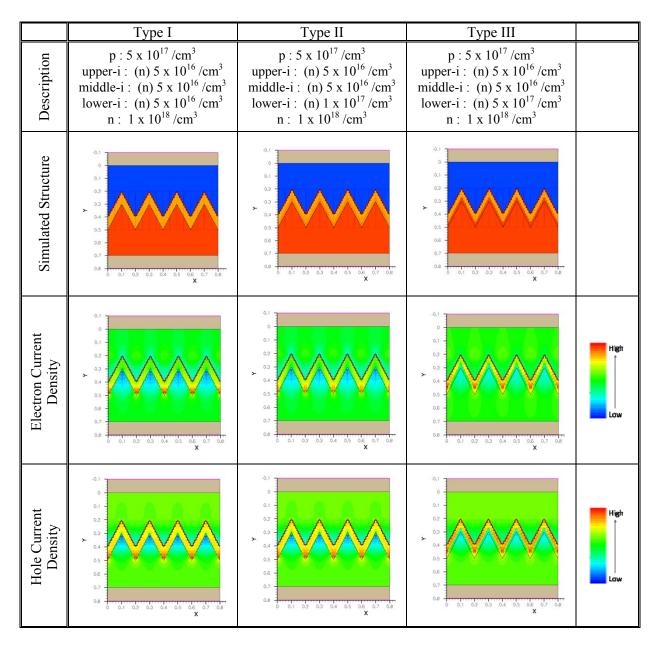

| Figure 6-6. Simulation for improving current uniformity in NSSP region with differen graded doping profiles in intrinsic region.                                                                                                                                                                                               |     |

| Figure 6-7. Simulation for improving current uniformity in NSSP region with differen graded doping profiles in intrinsic region.                                                                                                                                                                                               |     |

| Figure 6-8. Summarized electron and hole current densities along the center of intrinsic region for different graded doping profiles.                                                                                                                                                                                          |     |

| Figure 6-9. Simulated IV characteristics of different graded doping profiles in intrinsic region.                                                                                                                                                                                                                              |     |

| Figure 7-1. Surface texturing process using ISST.                                                                                                                                                                                                                                                                              | 94  |

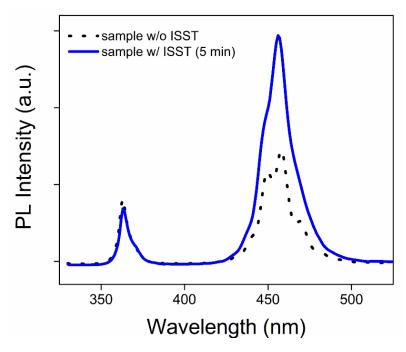

| Figure 7-2. Room temperature photoluminescence spectrum comparison of MQWs without ISST and with 5-minute ISST.                                                                                                                                                                                                                |     |

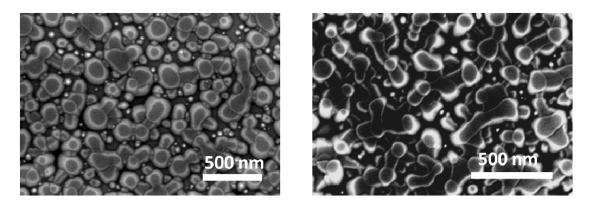

| Figure 7-3. Surface morphology comparison: (left) 5 min ISST at 1030 °C and (right) min ISST at 1000 °C.                                                                                                                                                                                                                       |     |

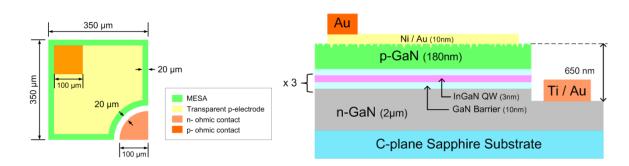

| Figure 7-4. Device structure of nano-structured LEDs grown on <i>c</i> -plane sapphire substrate: (left) top view and (right) side view                                                                                                                                                                                        | 98  |

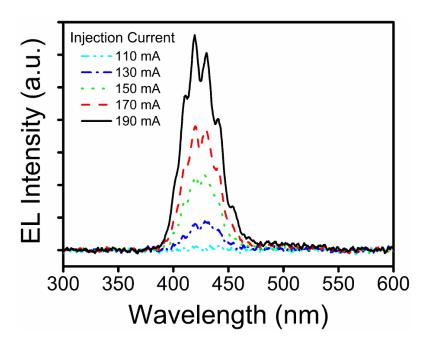

| Figure 7-5. Electroluminescence spectra of nano-structured LED under different inject current.                                                                                                                                                                                                                                 |     |

| Figure 7-6. L-I and I-V curves of nano-structured LED.                                                                                                                                                                                                                                                                         | 100 |

# LIST OF TABLES

| Table 2-1. Properties of III-nitride and various substrate materials                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2-2. Typical growth conditions for GaN templates used in this research                                                                                                |

| Table 2-3. Details of GaN epilayer growth                                                                                                                                   |

| Table 2-4. Summary of LT NL growth and LT NL annealing conditions for the three samples shown in Figure 2-7 and the comparison of HT GaN crystal quality through XRD and PL |

| Table 2-5. Summary of growth conditions for InGaN QW and GaN barrier and the results from the PL measurement                                                                |

| Table 4-1. Growth conditions for GaN template growth and ISST process                                                                                                       |

| Table 4-2. Summary of XRD measurements for GaN grown on an ISST-treated surface                                                                                             |

| Table 5-1. Summary of MQW growth condition                                                                                                                                  |

| Table 5-2. IQE comparison of NSSP MQWs and polar MQWs                                                                                                                       |

| Table 5-3. Summary of TR PL results                                                                                                                                         |

# LIST OF ABBREVIATIONS

2D 2 Dimensional

3D 3 Dimensional

AFM Atomic Force Microscopy

BHF Buffered Hydro-Fluoric acid

CCD Charge-Coupled Device

Cp<sub>2</sub>Mg Bis-cyclopentadienyl Magnesium

CRI Color Rendering Index

CW Continuous-Wave

EDX Energy Dispersive X-ray spectroscopy

EELS Electron Energy Loss Spectroscopy

EL Electroluminescence

ELOG Epitaxial Lateral Over-Growth

FF Fill Factor

FWHM Full Width Half Maximum

GaN Gallium Nitride

HEMT High Electron Mobility Transistor

HT High Temperature

HTO High Temperature Overgrowth

HVPE Hydride Vapor Phase Epitaxy

IEF Internal Electric Field

InGaN Indium Gallium Nitride

IQE Internal Quantum Efficiency

ISST In Situ Silane Treatment

LED Light-Emitting Diode

LEEBI Low Energy Electron Beam Irradiation

LT Low Temperature

MBE Molecular Beam Epitaxy

MOCVD Metal-Organic Chemical Vapor Deposition

MQWs Multiple Quantum Wells

NBE Near Band Edge

NH<sub>3</sub> Ammonia

NL Nucleation Layer

NSSP Nano-Structured Semi-Polar

PE *Pendeo-*Epitaxy

PEC Photo-Electro-Chemical

PECVD Plasma-Enhanced Chemical Vapor Deposition

PL Photoluminescence

QCSE Quantum Confined Stark Effect

QW Quantum Well

RIE Reactive Ion Etching

RMS Root-Mean Square

RT Room Temperature (300 K)

RTA Rapid Thermal Annealing

SAE Selective Area Epitaxy

SEM Scanning Electron Microscope

SiH<sub>4</sub> Silane

SIMS Secondary Ion Mass Spectroscopy

SiN<sub>x</sub> Silicon Nitride

SSL Solid-State Lighting

TIR Total Internal Reflection

TCAD Technology Computer Aided Design

TD Threading Dislocation

TEM Transmission Electron Microscopy

TMI Trimethyl-Indium

TMG Trimethyl-Gallium

TR PL Time-Resolved Photoluminescence

UID Unintentionally Doped

UTW Ultra Thin Window

XEDS X-Ray Energy Dispersive Spectroscopy

XPS X-ray Photoelectron Spectroscopy

XRD X-Ray Diffraction

YBE Yellow Band Emission

**ABSTRACT**

Nano-structured InGaN Light-Emitting Diodes

for Solid-State Lighting

by

**Taeil Jung**

Chair: P. C. Ku

Solid-state lighting can potentially reduce the electricity consumption by 25%. It

requires high efficiency light-emitting diodes across the visible spectrum. GaN and

related materials have direct bandgap across the entire visible spectrum and are ideal for

future solid-state lighting applications. However, materials defects, polarization charges,

and total internal reflection have thus far limited the efficiencies of InGaN LEDs, in

particular InGaN LEDs in the green/yellow wavelength range, which are critical in

achieving highly efficient LED luminaires with an excellent color-rendering index.

xvi

In this Thesis, we have developed and demonstrated that novel *in situ* nanostructured GaN processes in MOCVD are effective in improving the efficiencies of InGaN LEDs. InGaN LEDs grown on quasi-planar *semi*-polar GaN templates were proven to exhibit three times higher internal quantum efficiencies and negligible quantum confined Stark effect using selective area epitaxy. InGaN LEDs grown on nanostructured *semi*-polar GaN templates are also effective to improve the internal quantum efficiency by 31%. The same *in situ* processes are also effective in reducing the defect density by an order of magnitude and increasing the photon extraction efficiency as a factor of two.

The in situ processes include in situ silane treatment and high temperature overgrowth. Both processes require only standard MOCVD tools and hence are cost effective and suitable for mass-production. In situ silane treatment treats c-plane GaN samples with silane under ammonia environment, generating nano-scale truncated cone structures with up to 200 nm scale. These truncated cone structures can be subsequently transformed into pyramidal nanostructures comprising of only (10-11) and (11-22) semi-polar planes using high temperature overgrowth. These processes were applied to both InGaN active region and the LED surface to improve the internal quantum efficiency and the photon extraction efficiency, respectively. Extensive materials, device, and optical characterizations have been carried out in this research.

# **CHAPTER 1**

# **INTRODUCTION**

# 1.1 Gallium Nitride Materials for Optoelectronic Applications

Gallium nitride based materials, including GaN, AlN, InN, and their alloys, are excellent candidates for short-wavelength optoelectronic applications. Their direct bandgaps extend from ultraviolet to near-infrared. In addition, they exhibit high mechanical and thermal stabilities compared to other III-V *semi*-conductors, making them especially suitable for high-power and high-temperature operations. In recent years, breakthroughs in p-type doping and defect reduction have led to the commercialization of GaN based laser diodes, light-emitting diodes (LEDs), high electron mobility transistors (HEMT) and hydrogen detectors. Despite these advances, many technological challenges such as green gap and substrate growths still remain.

Perhaps one of the most important applications for GaN based materials is solid-state lighting (SSL). Worldwide, lighting constitutes 20% of electricity consumption while its efficiency is much lower than 25%. In contrast, efficiency of space heating has exceeded 90%. To this end, the development of highly efficient and reliable LEDs for

solid-state lighting has been very active in both industry and academia in the past few years. It is projected by the US Department of Energy that by 2015, if successful, solid-state lighting can reduce the overall electricity consumption by 25%.

Unlike GaAs and InP based *semi*-conductors, GaN based materials have suffered from a high density of defects due to very limited availability of lattice-matched GaN substrates. Up to now, most GaN based optoelectronic devices have been fabricated using hetero-epitaxy on foreign substrates such as sapphire (Al<sub>2</sub>O<sub>3</sub>), silicon carbide (SiC), and aluminum nitride (AlN), and in a very small percentage on silicon. Because of large lattice mismatch, GaN grown on these substrates often exhibits a high density of threading dislocations, typically on the order of 10<sup>8</sup> – 10<sup>10</sup> /cm<sup>2</sup>. These defects are still one of the major limiting factors for the performance of GaN based optoelectronic devices, acting as *non*-radiative recombination and scattering centers. Achievement of lower defect density would also improve device reliability, resulting in a longer lifetime. Various defect reduction approaches, such as epitaxial lateral over-growth (ELOG), have been demonstrated and some of the details will be discussed in Chap.1.3.1. As part of this thesis, we have explored a novel approach to using nano-structured GaN to effectively lower the threading dislocation density.

Among various epitaxial techniques that have been developed for GaN based materials, metal-organic chemical vapor deposition (MOCVD) is the leading technology. The typical growth temperature for GaN materials is around 1000 to 1200°C. This high growth temperature is necessary to improve the crystal quality and is a result of low cracking efficiency of the nitrogen source, ammonia (NH<sub>3</sub>), at a low temperature. In

Chapter 2, I will summarize my contributions to successfully ramp up an MOCVD tool for the epitaxial growth of GaN LEDs for this research.

# 1.2 InGaN LEDs for Solid-State Lighting

The basic component for SSL is a white-light LED. As shown in

Figure 1-1, it can be achieved by mixing various color components, which can be generated either from the direct output of individual LEDs or from color-conversion materials, such as phosphor. To date, commercially available white-light LEDs usually consist of a blue emitter and a yellow phosphor plate. It has been shown that InGaNbased blue LEDs could achieve external quantum efficiency in excess of 70% [1, 2]. However, this di-chromatic configuration typically has a poor color rendering index due to the lack of green and red components. The phosphor conversion process also limits the overall luminous efficiency due to energy loss during downconversion. To achieve luminous efficiency in excess of 200 lm/W and a color rendering index (CRI) in excess of 90, which is required for general illumination, a further improvement in blue LED efficiency and the use of tetra-chromatic configuration (blue + green + yellow + red) is necessary [3].\* Unfortunately, the efficiency of both InGaN and AlInGaP LEDs decreases significantly in the green-yellow (500 - 580 nm) range. This efficiency gap is also known as "green gap". Because AlInGaP materials have indirect bandgaps in this wavelength range, to achieve high-efficiency SSL, it is crucial to significantly improve the luminous

\* Note that a trichromatic (e.g. blue + green + red) source cannot achieve a CRI > 90.

3

efficiency of green and yellow InGaN LEDs. In this thesis, we will address these challenges using nano-structured GaN.

Figure 1-1. Illustration of various potential white-light LEDs configurations (after Ref. [4]).

# 1.3 Limiting Factors for InGaN LEDs Efficiency

To date, the efficiencies of InGaN LEDs are still limited by materials defects, polarization charges, and photon trapping. In this Section, we will briefly review the state of the art and overview how this research helps address these limitations.

#### **1.3.1** Materials Defects

As mentioned before, the high defect density in GaN based materials grown on foreign substrates increases the *non*-radiative recombination rate and lowers the radiative efficiency. To date, several techniques have been demonstrated to improve the crystal quality and reduce the threading dislocation (TD) density of the GaN layer. Substrate pretreatment at the growth temperature in an ammonia environment, also known as nitridation [5-7], has been shown to be critical for high quality GaN epilayers. The TD density of a typical GaN layer grown on *c*-plane sapphire substrate can be reduced to  $10^8/\text{cm}^2$  [8] by employing the combination of a low temperature (LT; 450 - 600 °C) nucleation layer (NL) and a short annealing at the growth temperature to change the phase of the as-grown NL from cubic to hexagonal [9-11]. As will be discussed in Chapter 2, careful optimization of these low temperature growth sequences can significantly alter the subsequent GaN template growth. To this end, a home-made optical *in situ* monitoring tool (reflectometry) was established and will be discussed extensively in Chapter 2.

In addition low temperature buffer growth, epitaxial lateral overgrowth (ELOG) which is a variation of selective area epitaxy (SAE) has been introduced [12, 13] to further lower the TD density by an order of magnitude to below 10<sup>7</sup>/cm<sup>2</sup>. Variations of ELOG including *pendeo*- (from the Latin: hang on or suspended from) epitaxy (PE) [14] and multi-step ELOG are also effective to further reduce the TD density. Additional techniques such as TiN nano-porous network [15] and anodic aluminum oxide nano-

mask [16] have also been proposed and demonstrated. All these methods, however, require *ex situ* processing and hence will add complexity and cost to the manufacturing. In this thesis, we will explore and generalize an *in situ* silane treatment approach to effectively lowering the TD density by an order of magnitude.

#### 1.3.2 Polarization Charges

Due to the *non*-cubic symmetry of GaN materials, compressively-strained active regions in InGaN LEDs exhibit both spontaneous and piezoelectric polarization charges. These polarization charges induce a strong internal electric field (IEF), typically on the order of MV/cm, in the active region, resulting in both efficiency droop at a high injection current density and the decrease of radiative efficiency with an increasing emission wavelength. The IEF can separate electrons from holes and increase electron leakage, resulting in low internal quantum efficiency (IQE) and efficiency droop [17], respectively. The suppression of the IEF, which is expected to increase IQE and the current density at which efficiency droop occurs, can be achieved by reducing the lattice mismatch in hetero-structures or growing them on *semi*-polar (e.g. {10-11} and {11-22}) and *non*-polar (e.g. *a*-plane and *m*-plane) surfaces. Because indium incorporation is more difficult on non-polar planes than on *semi*-polar planes, it is more advantageous to fabricate long-wavelength green-yellow LEDs on *semi*-polar planes to suppress the IEF.

At least three approaches to fabricating *semi*-polar InGaN LEDs have been reported thus far. These include the growth of a GaN epilayer on spinel substrates [18],

on bulk GaN substrates [19-27], and on the sidewalls of pyramidal or ridge GaN structures created on planar polar GaN surfaces using SAE [28-35]. GaN grown on spinel substrates have so far exhibited a high density of threading dislocations and stacking faults, thereby compromising the potential improvement of efficiency from the lowering of IEF. The use of bulk *semi*-polar GaN substrates has demonstrated the advantage of a lower IEF for the enhanced efficiency of green and yellow LEDs [25, 26]. However, limitations such as prohibitively high wafer cost and small substrate size need to be resolved before this approach can become more practical. On the other hand, the SAE technique can create *semi*-polar planes on polar GaN surfaces.

High quality polar GaN films have been fabricated from a variety of substrates including sapphire, 6H-SiC, and bulk GaN by MOCVD. Using growth rate anisotropy and three-dimensional growth, different *semi*-polar and *non*-polar GaN planes can be generated on *c*-plane GaN [13]. In Chapter 3, we will show that high quality InGaN multiple quantum wells (MQWs) which exhibit IQE as large as a factor of three compared to polar MQWs can be grown on pyramidal GaN microstructures. This approach, however, requires *ex situ* patterning processes and does not easily produce a planar structure for electrical contacts. In this thesis, a new *semi*-polar LED structure is investigated, which is enabled by a novel epitaxial nanostructure, namely the nanostructured *semi*-polar (NSSP) GaN, which can be fabricated directly on *c*-plane GaN but without the issues of the SAE technique mentioned above [36]. NSSP GaN also eliminates the issues of excessive defects for GaN grown on spinel substrates and lowers the cost of using bulk *semi*-polar GaN substrates. As we will show later, the surface of NSSP GaN consists of two different *semi*-polar planes: (10-11) and (11-22). Therefore it

is expected that InGaN active regions fabricated on NSSP GaN can exhibit a low IEF, and hence much improved IQE.

#### **1.3.3** Photon Extraction

After photons are generated from the active region in LEDs, they need to escape the device in order to be useful. When light travels from a medium with a higher refractive index to a medium with a lower refractive index, total internal reflection (TIR) occurs at the interface. In InGaN LEDs, photons experiencing TIR at LED surfaces can be re-absorbed by the active region or trapped in the device due to a waveguiding effect as shown in Figure 1-2. In a simple InGaN LED, only 4% of photons generated from the active region can escape from each device surface. It has been shown that surface textures on LED surfaces can greatly reduce TIR and improve photon extraction efficiency as illustrated in Figure 1-2. To date, many surface texturing techniques such as photonic crystal structures [37] and photo-electrochemical etching of GaN surfaces [38] have been introduced. Notably, the photo-electrochemical etching of nitrogen-terminated GaN surface has been successfully implemented into commercial blue LEDs [2]. However, these approaches all require additional ex situ patterning processes which add significant costs. In this thesis, we investigate an in situ process to fabricate nanostructured GaN surfaces on LEDs which effectively improves the photon extraction efficiency.

Figure 1-2. Light traveling within waveguides (left) with a smooth interface and (right) with a rough interface (after [39]).

# 1.4 Organization of the Thesis

The objective of this thesis is to investigate cost-effective nanofabrication techniques that can significantly improve the efficiency of the state-of-the-art InGaN LEDs in both blue and green/yellow ranges for high performance solid-state lighting. The organization of this thesis is as follows.

In Chapter 2, a summary of the MOCVD techniques for InGaN LEDs is given. In Chapter 3, we study the dependence of InGaN LED IQE on {10-11} semi-polar planes using SAE. In Chapter 4, fabrication and characterization of novel and cost-effective nano-structured GaN templates will be described. Using in situ silane treatment (ISST) and high temperature overgrowth (HTO), the formation of nano-scale inverted cone structures and nano-structured semi-polar (NSSP) templates has been obtained. In Chapter 5, we study InGaN semi-polar LEDs based on NSSP templates. An improvement of internal quantum efficiency is demonstrated. A green semi-polar InGaN LED grown on a c-plane substrate is also demonstrated. In Chapter 6, current spreading in NSSP

InGaN LEDs will be discussed. In Chapter 7, the application of ISST for the improvement of photon extraction efficiency of an InGaN LED will be discussed. In Chapter 8, we will summarize and make suggestions for future work.

# **CHAPTER 2**

# METAL-ORGANIC CHEMICAL VAPOR DEPOSITION FOR GALLIUM NITRIDE OPTOLECRONICS

#### 2.1 Gallium Nitride Growth

As mentioned in the Introduction, gallium nitride (GaN) and related alloys are excellent candidates for future solid-state lighting. To date, III-nitride epitaxial growth has been limited by the lack of sufficiently large single crystal substrate for homoepitaxial growth. Therefore, the growth of GaN and related materials has been largely based on hetero-epitaxy using hydride vapor phase epitaxy (HVPE), metal organic chemical vapor deposition (MOCVD), and molecular beam epitaxy (MBE). Among these techniques, MOCVD is the leading technology due to the advantages on material quality, scalability, and cost [40]. The material quality of GaN grown by MOCVD has been excellent owing to its relatively high growth temperature (1000 - 1200°C) [41, 42].

To date, various substrate materials including sapphire (Al<sub>2</sub>O<sub>3</sub>), silicon carbide (SiC), and silicon have been studied for GaN growth (Table 2-1). Although GaN substrates have been recently introduced in markets through bulk material growth on

foreign substrates using HVPE and laser cutting along specific crystal planes, the cost has been prohibitively high. On the other hand, GaN grown on *c*-plane (0001) sapphire substrate exhibits stable growth over a wide range of growth conditions despite high dislocation density at the interface between the substrate and epitaxial layer. In this research, I have helped ramping up an MOCVD system together with Dr. Hongbo Yu. In this Chapter, I will summarize the MOCVD technologies and defect reduction strategies for InGaN light-emitting diodes (LEDs) epitaxy that will be used throughout this Thesis.

| Ma          | terial                           | Crystal Structure /<br>Growth Plane | Lattice Const. (Å)                 | Lattice Mismatch<br>w/ GaN (%) | Thermal Expansion Coeff.(10 <sup>-6</sup> /K) |

|-------------|----------------------------------|-------------------------------------|------------------------------------|--------------------------------|-----------------------------------------------|

| III-Nitride | AlN                              | Wurtzite / (0001)                   | a = 3.112 / c = 4.982              | 2.5                            |                                               |

|             | GaN                              | Wurtzite / (0001)                   | a = 3.189 / c = 5.186              | 0                              | 5.6(a); 7.7(c)                                |

|             | InN                              | Wurtzite / (0001)                   | a = 3.548 / c = 5.703              | -10.1                          |                                               |

| Substrate   | Al <sub>2</sub> O <sub>3</sub>   | Rhonbohedral /<br>Rotated 30°       | a = 4.765 / c = 12.982             | 13.9                           |                                               |

|             | GaAs                             | Cubic / (111)                       | a = 5.653                          | -20.2                          |                                               |

|             | LiAlO <sub>2</sub>               | (100)                               | a = 5.169 / c = 6.267              | -6.3(b)<br>-1.4(c)             | 7.1(a); 7.5(c)                                |

|             | LiGaO <sub>2</sub>               | Orthorhombic / (001)                | a = 5.402<br>b =6.372<br>c = 5.007 | 0.1                            | 6(a); 9(b); 7(c)                              |

| Ø           | MgAl <sub>2</sub> O <sub>4</sub> | (111)                               | a = 8.083                          | -10.3                          | 7.45                                          |

|             | Si                               | Cubic / (111)                       | a = 5.431                          | -17.0                          |                                               |

|             | SiC                              | Wurtzite (6H) /<br>(0001)           | a = 3.081 / c = 15.117             | 3.5                            | 4.2(a); 4.0(c)                                |

|             | ZnO                              | Wurtzite / (0001)                   | a = 3.250 / c = 5.207              | 2.1                            | 2.9(a); 4.75(c)                               |

Table 2-1. Properties of III-nitride and various substrate materials (data after [41, 43]).

# 2.1.1 GaN Growth Using MOCVD

Due to a large lattice mismatch between GaN and sapphire, it is important to contain the defects near the GaN/sapphire interface such that the defect density can be minimized in the device region. Such optimization is achieved using *in situ* reflectometry [44, 45]. A home-made reflectometry system shown in Figure 2-1 was established in our 3 x 2" Thomas-Swan Close-Coupled Showerhead (CCS) MOCVD system. White light is reflected from the sample surface and monitored by a spectrometer during the growth. The reflectivity is sensitive to both the surface morphology and the epitaxial layer structure.

Figure 2-1. Illustration of a home-made *in situ* reflectometry system integrated into the MOCVD system.

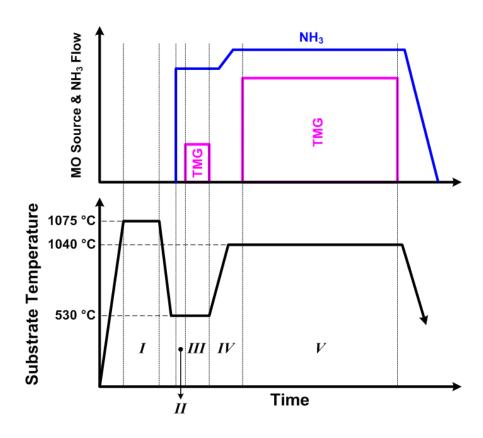

Figure 2-2. Typical growth conditions for GaN templates used in this research.

|     | Description                      | Temperature (°C)  | V/III Ratio |

|-----|----------------------------------|-------------------|-------------|

| I   | HT Cleaning                      | 1075              | N/A         |

| II  | Nitridation                      | 530               | N/A         |

| III | LT Nucleation                    | 530               | 9140        |

| IV  | Annealing of LT Nucleation Layer | 530 <b>→</b> 1040 | N/A         |

| V   | HT GaN                           | 1040              | 1230        |

Table 2-2. Typical growth conditions for GaN templates used in this research.

Typical growth conditions for GaN templates used in this research are summarized in Figure 2-2 and Table 2-2. Unless otherwise mentioned, *c*-plane sapphire substrates were used. The five steps outlined in Table 2-2, including high temperature (HT) cleaning, nitridation, low temperature (LT) nucleation, annealing of LT nucleation layer, and HT GaN growth, are crucial for high quality GaN epilayer.

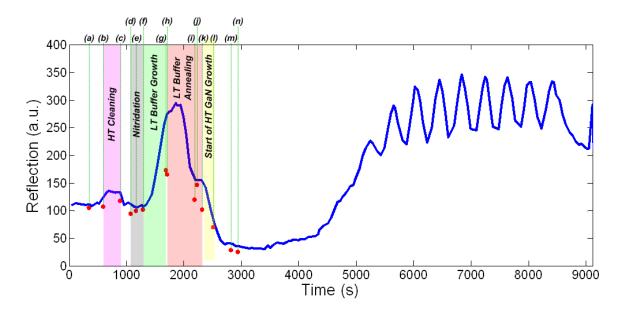

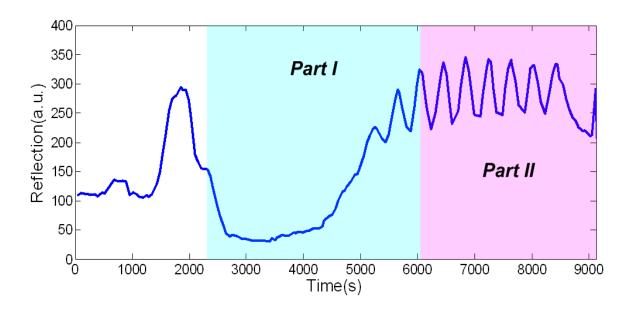

Figure 2-3 and Table 2-3 show the corresponding *in situ* reflectometry signal. In the following, we will describe how the reflectometry signal can be used to optimize the GaN template growth. Unless otherwise mentioned, we will refer to the reflectometry signal shown in Figure 2-3.

Figure 2-3. *In situ* reflectometry trace of GaN template growth (Sample ID : UM-S07-254). The highlighted areas correspond to important sub-steps during the epitaxy.

- (a) Beginning of temperature ramp-up for HT cleaning

- (b) Beginning of HT cleaning

- (c) End of HT cleaning

- (d) Beginning of NH<sub>3</sub> ramp-up (beginning of *nitridation*, NH<sub>3</sub> on)

- (e) Nitridation

- (f) Beginning of LT nucleation

- (g) End of LT nucleation

- (h) Beginning of temperature ramp-up for annealing of LT nucleation layer

- (i) End of temperature ramp-up for annealing of LT nucleation layer at 1020 °C

- (j) End of annealing at 1020 °C and beginning of HT GaN growth: TMG ramping (30  $\rightarrow$  60 s ccm), NH<sub>3</sub> (2000 sccm), i.e. V/III = 1524  $\rightarrow$  889

- (k) Beginning of TMG and NH<sub>3</sub> ramping (T = 1020 °C): TMG<sub>1</sub> ramping (60  $\rightarrow$  90 sccm), NH<sub>3</sub> (2000  $\rightarrow$  2650 sccm), i.e. V/III = 889  $\rightarrow$  628

- (1) Beginning of HT GaN growth ( $T = 1020 \, ^{\circ}\text{C}$ )

- (m) Beginning of HT GaN T ramp-up (T =  $1020 \rightarrow 1040 \,^{\circ}$ C)

Table 2-3. Details of GaN epilayer growth (based on the data for sample ID : UM-S07-254).

#### 2.1.1.1 High Temperature Cleaning

Initially, as the sample temperature is ramped up, the reflectivity increases due to the increase of the refractive index of the sample. Kim et al. has thoroughly studied the effect of initial thermal cleaning on the sapphire substrate and experimentally demonstrated that this thermal treatment can effectively reduce the surface roughness of the substrate [46]. Generally, the flat surface is preferred for the GaN nuclei to be formed uniformly, which is critical to the crystal quality of the final GaN epilayer. The specific condition for the HT cleaning should be optimized by examining the treatment temperature and time. In our GaN growth, the optimal treatment temperature and time were set to be 1075 °C and 5 minutes, respectively. Moreover, HT surface annealing can effectively eliminate surface moisture.

#### 2.1.1.2 Nitridation

Nitridation [5, 7] is the process of NH<sub>3</sub> preflow under hydrogen (H<sub>2</sub>) ambient to prepare the surface for growth. During nitridation, NH<sub>3</sub> reacts with the surface oxygen atoms on the sapphire substrate. Due to the replacement of the oxygen atoms by the nitrogen atoms and the diffusion of the nitrogen atoms into a certain depth, the exposed surface becomes a smooth amorphous state. Because this change of surface morphology is on the order of tens of angstrom, the corresponding reflectivity change is not significant. It has been shown that with a proper nitridation condition, GaN epilayers with lower dislocation density and better electrical and optical properties can be achieved [7]. However, as mentioned above, suitable combination of reactor conditions such as temperature, treatment time, and NH<sub>3</sub> flow rate must be considered. In our GaN growth, the nitridation was optimized at 530 °C for a total of 210 seconds under 3 slm of NH<sub>3</sub> flow.

### 2.1.1.3 Low Temperature Nucleation

As mentioned in Section 1.3.1, several approaches have been introduced to reduce the threading dislocation (TD) density in growing the GaN template. Specifically, the use of low temperature nucleation layer (LT NL) has been shown to be simple yet effective. A threading dislocation density as low as 10<sup>8</sup>/cm<sup>2</sup> has been reported [8].

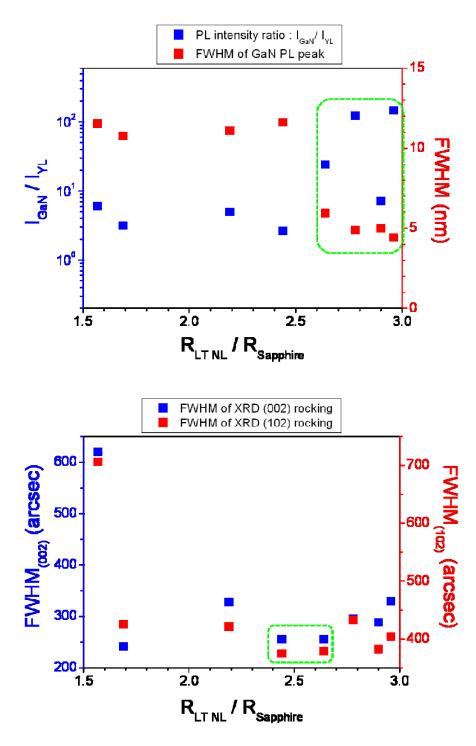

As GaN is nucleated on sapphire, the cubic phase islands are first formed at a temperature of 450 - 600 °C. These islands are subsequently transformed into the wurtzite phase [8]. The increase of the reflectivity during the LT NL growth is attributed to the increase of reflection from the flat top surfaces of nuclei. Basically, we know that the reflection from GaN is about twice stronger than that from sapphire due to the difference in refractive indices. As the islands become denser (i.e. the growth time of LT NL becomes longer), total reflection from the top surface of nuclei becomes up to 200% of reflection from sapphire substrate assuming that the entire surface is covered by GaN islands. Even though the islands are not coalesced completely to form a crystalline layer, this is still possible because the distances between the adjacent islands are too small compared to the optical wavelength. Once the reflectance exceeds twice that of the sapphire (as shown in Figure 2-3), the islands continue to coalesce further, which results in larger GaN grains and a thicker NL. Here, the size of the nucleation islands and the thickness of the NL are critical to obtain high quality GaN epilayer. To show that, we have compared a series of GaN templates with different NL conditions. All conditions were kept the same except the growth time of the LT NL was varied, resulting in different LT NL thicknesses. The thickness of the LT NL was extrapolated by analyzing the reflectometry data as the reflection ratio at the end of LT NL growth to the sapphire substrate  $(R_{LTNL} / R_{Sapphire})$ . The qualities of the GaN templates were characterized using photoluminescence (PL) and x-ray diffraction (XRD). From these results, the best GaN template quality can be obtained when  $R_{LTNL} / R_{Sapphire}$  is around 2.6 which corresponds to a 40nm thick NL, at the given growth conditions.

-

<sup>&</sup>lt;sup>†</sup> LT NL growth temperature = 530°C, V/III = 9140, LT NL annealing time = 420 seconds, HT GaN growth temperature = 1040°C, V/III = 1230, growth time = 4300 seconds.

Figure 2-4. The comparison of GaN template qualities with respect to the reflection ratio between the LT NL surface and the sapphire substrate.

## 2.1.1.4 Annealing of Low Temperature Nucleation Layer

In GaN hetero-epitaxy with a large lattice mismatch, the initial growth on the surface follows the Volmer Weber model [47], i.e. GaN island growth dominates. In order to obtain smooth GaN templates, these islands need to be transformed into the layer-by-layer growth mode using an NL annealing process. During annealing, the substrate temperature is gradually increased up to around 1030 - 1050 °C under NH<sub>3</sub> overpressure. Temperature ramping rate, reactor pressure, and NH<sub>3</sub> flow can control the NL decomposition rate, which determines the surface roughness at the end of the annealing process [48, 49]. In Figure 2-3, after point (h) at which LT NL annealing begins, slight increase of reflectance is normally observed. The increase continues until around 800 °C at which GaN decomposition process starts to occur. Once the reflection intensity peaks, it begins to drop due to the increase in surface roughness. Initially randomly distributed islands start to be transformed into relatively uniform islands due to the decomposition of the NL and the migration of the gallium ad-atoms.

Koleske et al. proposed that the NL decomposition rate is a function of the temperature, reactor pressure, NH<sub>3</sub> flow, and NL layer thickness [48, 49]. Because the decomposition rate follows the Arrhenius relation with the increase of temperature, a shorter annealing time is expected to achieve the same surface roughness using a higher temperature ramping rate. In addition, the decomposition rate in H<sub>2</sub> carrier gas increases with respect to the increase of reactor pressure and decreases with NH<sub>3</sub> flow. At a higher NH<sub>3</sub> flow, more nitrogen precursors will be delivered to the surface, lowering the decomposition rate. Concerning the NL thickness, it is known that a thicker NL exhibits a

higher decomposition rate. When the NL becomes thicker, GaN islands grow larger due to the coalescence of the adjacent islands, which increases the area where decomposition takes place. Hence, the optimization of the NL annealing process must be carried out carefully considering all possible effects of each parameter.

During the annealing process, the reflectivity first decreases due to the increase of surface roughness. Further annealing results in a slight increase of reflectivity because at a higher temperature, the surface morphology becomes smoother. However, if we anneal the surface even further, the surface roughness increases again, which results in the decrease of reflection intensity [48, 49]. This phenomenon can be explained by considering the volume of the GaN islands. At the transition point ((k) in Figure 2-3), the volume of the islands per unit area becomes the highest which is preferable for the subsequent HT GaN growth. As a rule of thumb, the position of this (reflectometry trace) shoulder is dominated by the highest temperature of the annealing process [50]. In summary, the goal of the low temperature nucleation and the subsequent annealing is to achieve a surface morphology with proper density and sizes of the islands for the following HT GaN growth.

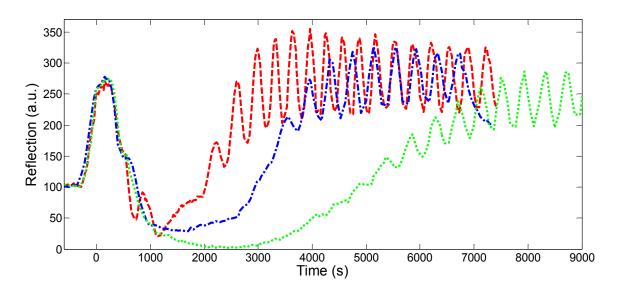

As shown in Figure 2-5, even a slight change of the island distribution caused by a slight difference of the NL thickness and temperature ramping rate (Table 2-4) can result in a significant difference in the following HT GaN growth under the same conditions. In general, it takes longer for an NL with a rougher surface and smaller islands to be transformed into the 2D growth mode. The conditions to achieve high crystal quality GaN on sapphire are mostly related to the growth and annealing of the LT NL.

### 2.1.1.5 HT GaN Growth

As soon as the sapphire surface is covered with suitable volume, uniformity, thickness, and density of GaN islands, HT GaN growth can be followed. This HT GaN itself can be divided into two parts (Figure 2-6). Part I corresponds to the initial stage of HT GaN growth when the growth mode is transitioned from 3D to 2D, which affects the crystal quality significantly. In part II, GaN epilayer becomes thicker because the growth mode as well as growth condition is stabilized for 2D mode. Several strategies to control the GaN growth in each regime will be briefly discussed in the following.

The growth in part I is a buffer step to prepare a surface suitable for HT GaN growth. During this step, the oscillation of the reflectometry signal becomes increasingly obvious. Initially, the reflectivity continues to drop due to the increase of surface roughness induced by the coagulations of the islands, i.e. 3D growth. As time goes by, the 3D growth mode is suppressed and the 2D growth mode is enhanced. Once the surface becomes flattened due to the enhanced 2D growth, layer by layer growth of GaN begins, which causes the reflectivity to increase. The duration of this part of growth can be optimized by tweaking the reactor pressure, V/III ratio, and growth rate [51, 52]. For example, in the case of a low V/III ratio, it takes longer to recover the reflection intensity, which implies that the change of the growth mode (3D  $\rightarrow$  2D) occurs more slowly. The reflectivity recovery time is critical to oscillation amplitude in part II. In general, a larger oscillation amplitude corresponds to a better crystal quality.

Figure 2-5. Comparison of reflectance data for three different samples: Red, Blue, and Green lines correspond to sample IDs UM-S07-223, UM-S07-254, and UM-S07-261, respectively.

|                    | Sample ID                    | UM-S07-223 | UM-S07-254 | UM-S07-261 |  |

|--------------------|------------------------------|------------|------------|------------|--|

| LT NL<br>Growth    | Temp. (°C)                   | 530        | 530        | 530        |  |

|                    | III/V                        | 9140       | 9140       | 9140       |  |

|                    | $R_1 / R_0$                  | 2.527      | 2.592      | 2.587      |  |

| LT NL<br>Annealing | Temp. ramping rate (°C/min.) | 70         | 63.1       | 63.1       |  |

|                    | Pressure (Torr)              | 200        | 200        | 200        |  |

|                    | NH <sub>3</sub> flow (sccm)  | 2500       | 2500       | 2500       |  |

|                    | $R_2 / R_0$                  | 1.574      | 1.459      | 1.512      |  |

| HT GaN             | Growth rate (nm/Hr)          | 1388.31    | 1148.28    | 1135.32    |  |

| XRD                | (002) (arcsec)               | 255.6      | 280.8      | 295.2      |  |

|                    | (102) (arcsec)               | 378        | 360        | 417        |  |

| PL                 | $I_{\rm GaN}$ / $I_{\rm YL}$ | 23.79      | 0.46       | 74.14      |  |

|                    | FWHM (nm)                    | 5.92       | 11.08      | 7.68       |  |

Table 2-4. Summary of LT NL growth and LT NL annealing conditions for the three samples shown in Figure 2-7 and the comparison of HT GaN crystal quality through XRD and PL ( $R_0 = R_{Sapphire}$ ,  $R_1 = R_{LT\,NL}$ , and  $R_2 = R_{NL\,Annealing}$ ).

Figure 2-6. Two different growth parts in HT GaN growth (reflectance trace of UM-S07-254).

The part II of the HT GaN growth is stable in a wide range of growth conditions because the growth occurs in a mass transfer limited region. Nevertheless, several key factors will still affect the crystalline structure, including the growth temperature, trimethyl-gallium (TMG) flow, NH<sub>3</sub> flow, V/III ratio, and reactor pressure. As shown in Figure 2-7, the growth rate increases as the group III flow increases but decreases as the V/III ratio and growth temperature increase. The growth rate is one of the key parameters to determine optical and electrical properties of GaN epilayer especially for p- or n- type doped cases. This will be discussed in more details in the next Section.

Figure 2-7. The dependence of the growth rate on (a) TMG flow, (b) NH<sub>3</sub> flow, and (c) V/III ratio at given TMG flow and NH<sub>3</sub> flow, and (d) growth temperature (fixed parameters: reactor pressure = 200 torr, rotation speed = 100 rpm).

# 2.1.2 GaN Doping

## 2.1.2.1 N-type Doping

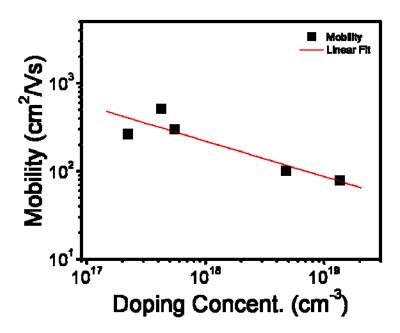

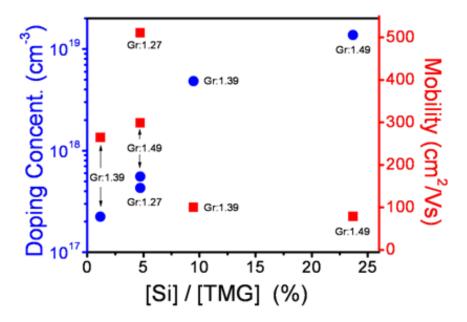

Usually, unintentionally doped (UID) GaN is n-type with a carrier concentration as low as  $10^{16}$ /cm<sup>3</sup>. The carrier concentration can be considerably increased by intentional silicon doping using silane (SiH<sub>4</sub>) [53]. The carrier concentration in an n-type GaN epilayer is closely related to the carrier mobility (Figure 2-8). The carrier mobility decreases exponentially as the doping concentration increases due to enhanced carrier scattering within the crystalline structure. Both the carrier concentration and mobility can be controlled by the growth rate and SiH<sub>4</sub> flow.

Figure 2-8. Relationship between the carrier mobility and the doping concentration in silicon doped n-type GaN (GaN:Si).

Figure 2-9. Doping concentration and carrier mobility with respect to the silane vaporphase mole fraction ([Si]/[TMG]) and the growth rate (Gr;  $\mu$ m/hour) in n-type GaN:Si.

## 2.1.2.2 P-type Doping

P-type doping has long been a show stopper for GaN based electronic and optoelectronic devices. In 1989, the first p-type GaN, doped with magnesium (Mg) and treated with low energy electron beam irradiation (LEEBI), was reported by Amano et al. [54]. However, the basic mechanism of the treatment had been unknown and as a result the experiment had not been reproducible until 1992 when Nakamura et al. experimentally demonstrated p-type Mg doped GaN (GaN:Mg) by post annealing treatment and ascertained the mechanism of hydrogen passivation of acceptors [55, 56]. Simply by adopting a thermal annealing step, p-type GaN could be obtained reliably, which made it possible for device applications.

Five samples were prepared with varying bis-cyclopentadienyl magnesium (Cp<sub>2</sub>Mg) flow (50, 100, 200, 250, and 375 sccm). All samples were thermally activated in MOCVD reactor at 720 °C for 20 minutes under N<sub>2</sub> ambient. Samples were characterized by Hall and photoluminescence (PL) measurements. The dependence of the carrier concentration and mobility on Cp<sub>2</sub>Mg flow is shown in Figure 2-10 and 2-11. The doping concentration increases but the carrier mobility decreases as Cp<sub>2</sub>Mg flow increases, similar to the n-type samples. The optical properties of the Mg-doped GaN epilayers with different carrier concentrations are presented in Figure 2-12. The shift of the PL peak position is attributed to the Mg acceptors with different concentrations [57, 58]. The transition energy decreases and is proportional to the acceptor concentration. The sample was also characterized by secondary ion mass spectroscopy (SIMS). About 7 % of total Mg atoms were activated through thermal annealing (Figure 2-13).

Figure 2-10. Measured doping concentration and carrier mobility of p-type GaN:Mg for different Cp<sub>2</sub>Mg flow.

Figure 2-11. Mobility vs. doping concentration of p-type GaN:Mg.

Figure 2-12. Optical properties of GaN:Mg with different carrier concentration; (a) room temperature PL spectra and (b) the Mg-related PL peak with respect to different doping concentrations.

Figure 2-13. As-grown PIN structure (left) and the corresponding SIMS analysis (right).

## 2.2 InGaN Quantum Wells

There are several control parameters to determine the characteristics of InGaN QWs. These parameters can be categorized into two parts, the structural control and the compositional control. These parameters are not independent.

Parameters for structural control include QW thickness, barrier thickness, the number of QWs, and the surface roughness of the underlying layer. Thinner QW and thicker barrier can reduce the quantum confined Stark effect (QCSE) for QWs grown on *c*-plane substrates. In general, QWs grown on a smooth surface tend to exhibit stronger photoluminescence. High temperature barrier growth, H<sub>2</sub> treatment during the barrier growth, and interruption between the QW and barrier growth can improve the surface morphology of the QW, resulting in better optical properties [59-62].

Parameters for compositional control include growth rate, growth temperature, trimethyl-indium (TMI) flow, and reactor pressure. For example, QWs with high indium contents require lower growth temperature and higher growth rate in order to reduce the indium desorption from the surface [63, 64]. However, for the growth of high indium content QWs, indium segregation and indium phase separation can occur. During post QW growth processes such as HT barrier growth and thermal annealing of p-type GaN, the indium atoms at the interface between the QW and the barrier can segregate into the barriers, eventually degrading the optical properties of the QWs [65, 66]. To minimize the indium segregation and improve the interface morphology, additional treatments such as H<sub>2</sub> interruption and TMI pretreatment, have been introduced [67-70]. TMI pretreatment is also beneficial to enhance the quantum efficiency of the QW.

### 2.2.1 InGaN Quantum Well Growth Optimization

In this Section, several examples will be discussed to demonstrate the optimization of InGaN QWs in our TS MOCVD. Table 2-5 shows the summary of the growth conditions in details.

| Sample ID  | Quantum Well Growth |                         |            |                     | GaN Barrier Growth |       |                         | PL Measurement          |         |             |           |

|------------|---------------------|-------------------------|------------|---------------------|--------------------|-------|-------------------------|-------------------------|---------|-------------|-----------|

|            | Temp.               | TMG <sub>2</sub> (sccm) | TMI (sccm) | [In]/[In+Ga]<br>(%) | V/III              | Temp. | TMG <sub>1</sub> (sccm) | TMG <sub>2</sub> (sccm) | V/III   | Peak λ (nm) | FWHM (nm) |

| UM-S07-138 | 780                 | 1.50                    | 200        | 80.5                | 8901.4             | 780   | 4.878                   | 1.50                    | 12652.2 | 397.3       | 11.3      |

| UM-S07-140 | 780                 | 1.00                    | 200        | 86.1                | 9519.1             | 780   | 5.500                   | 1.00                    | 12652.1 | 428.3       | 32.4      |

| UM-S07-141 | 780                 | 0.70                    | 200        | 89.9                | 9932.6             | 780   | 5.873                   | 0.70                    | 12652.4 | 453.6       | 46.8      |

| UM-S07-142 | 780                 | 1.10                    | 212.9      | 85.7                | 8901.1             | 780   | 5.500                   | 1.10                    | 12422.9 | 443.9       | 30.6      |

| UM-S07-143 | 780                 | 1.23                    | 208.6      | 84.0                | 8901.6             | 780   | 5.330                   | 1.23                    | 12427.6 | 442.5       | 27.2      |

| UM-S07-169 | 800                 | 1.39                    | 203.6      | 82.0                | 8901.8             | 800   | 5.140                   | 1.39                    | 12427.9 | 430.8       | 29.1      |

| UM-S07-172 | 800                 | 1.23                    | 208.6      | 84.0                | 8901.6             | 800   | 5.330                   | 1.23                    | 12427.6 | 440.9       | 38.5      |

| UM-S07-207 | 805                 | 1.23                    | 208.6      | 84.0                | 8901.6             | 805   | 5.330                   | 1.23                    | 12427.6 | 412.3       | 26.9      |

| UM-S07-209 | 773.7               | 1.23                    | 208.6      | 84.0                | 8901.6             | 773.7 | 5.330                   | 1.23                    | 12427.6 | 544.7       | 63.1      |

| UM-S07-212 | 800                 | 1.23                    | 208.6      | 84.0                | 8901.6             | 800   | 5.330                   | 1.23                    | 12427.6 | 434.0       | 30.8      |

Table 2-5. Summary of growth conditions for InGaN QW and GaN barrier and the results from the PL measurement (QW growth time = 3 minutes; GaN barrier growth time = 10 minutes; NH $_3$  flow for both QW and GaN barrier = 4 slm; reactor pressure = 400 torr; N $_2$  ambient condition).

## 2.2.1.1 Growth Temperature Optimization

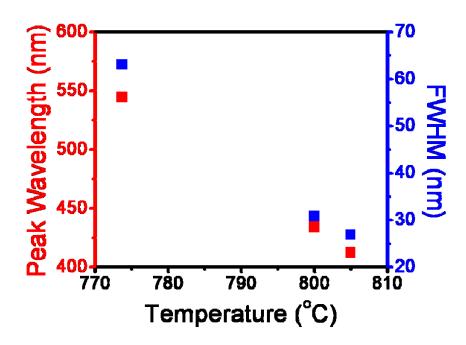

The growth temperatures of the QWs and barriers are perhaps the most critical parameter that will affect the emission wavelength and photoluminescence characteristics. In Figure 2-14, the comparison of samples UM-S07-207, UM-S07-209, and UM-S07-212 shows how the growth temperature affects the characteristics of the QW. The peak emission wavelength redshifts as the growth temperature decreases, which is attributed to a lower growth rate and reduced indium evaporation and hence a higher indium solid composition. However, the emission linewidth increases as the growth temperature decreases. Usually, a high growth temperature can improve the crystal quality and surface morphology of both the QWs and barriers. As discussed, smooth and dislocation-free underlayer is favorable to achieve a sharp interface between the InGaN QW and GaN barrier which results in a narrow emission linewidth. To obtain a longer emission wavelength, a lower growth temperature is required to achieve a high indium content but at the expense of a larger emission linewidth. To resolve this matter, techniques such as HT GaN barrier growth, growth interruption with H<sub>2</sub> treatment, and TMI pretreatment have been proposed in recent years [67, 70].

Figure 2-14. PL measurement data of the QWs grown at different growth temperatures (sample IDs: UM-S07-207, UM-207-209, UM-S07-212)

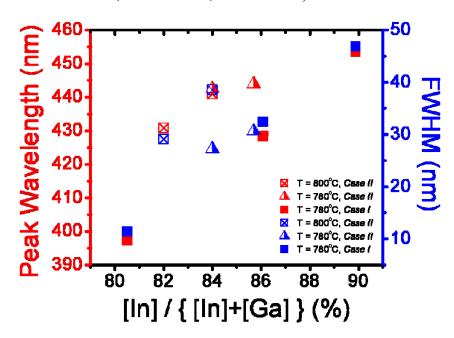

Figure 2-15. PL measurement data of the QWs grown with different indium vapor-phase mole fractions at two different growth temperatures; growth temperature =  $800 \,^{\circ}$ C with *Case II* (sample IDs: UM-S07-169, UM-S07-172), growth temperature =  $780 \,^{\circ}$ C with *Case II* (sample IDs: UM-S07-142, UM-S07-143), and growth temperature =  $780 \,^{\circ}$ C with *Case I* (sample IDs: UM-S07-138, UM-S07-140, UM-S07-141); *Case I* - TMGa flow control with varying V/III and *Case II* - both TMGa and TMI flow control with a constant V/III.

#### 2.2.1.2 Indium Mole Fraction Control

In addition to the growth temperature, it is also critical to control the indium vapor-phase mole fraction, i.e. the ratio of moles of indium flow to the total group III flow ([In] / {[In]+[Ga]}). Figure 2-15 shows how the indium mole fraction changes the emission wavelength, which unfortunately is not linear due to the increasing difficulty of incorporating indium. For all cases, both the emission wavelength and linewidth increase with the increase of indium mole fraction. The increase of the emission linewidth can be partially attributed to the indium phase separation. There is a limitation to accomplish high indium content by solely adjusting indium mole fraction. Therefore, a combination of the low growth temperature and high indium mole fraction is required for longer wavelength (green/yellow) InGaN QWs.

## 2.3 Summary

In this chapter, III-nitride growth using MOCVD was discussed. GaN epitaxy on c-plane sapphire substrate was reviewed and the optimization of the crystal quality was demonstrated. High temperature cleaning, nitridation, LT nucleation, annealing of LT nucleation layer, and HT GaN growth were performed successively to achieve high quality GaN epilayer. In particular, LT nucleation layer thickness is crucial to determine the subsequent decomposition rate of nuclei while optimized annealing of nucleation layer can allow us to achieve proper density and volume of nuclei for the following 3D growth mode. In the early stage of HT GaN growth, growth mode transformation from

3D into 2D occurs and techniques have been developed to enhance the growth mode evolution, such as growth rate modification. Once HT GaN growth becomes stabilized, GaN growth rate can be adjusted by V/III ratio and growth temperature. To achieve high crystal quality, it is essential to monitor and adjust the growth conditions using *in situ* reflectometry at each growth step.