# THE UNIVERSITY OF MICHIGAN COMPUTING RESEARCH LABORATORY<sup>1</sup>

### A CLASS OF CELLULAR COMPUTER ARCHITECTURES TO SUPPORT PHYSICAL DESIGN AUTOMATION

Robin Arthur Rutenbar

CRL-TR-35-84

September 1984

Room 1079, East Engineering Building Ann Arbor, Michigan 48109 USA Tel: (313) 763-8000

<sup>&</sup>lt;sup>1</sup>Any opinions, findings, and conclusions or recommendations expressed in this publication are those of the authors and do not necessarily reflect the views of the funding agency.

#### ABSTRACT

## A CLASS OF CELLULAR COMPUTER ARCHITECTURES TO SUPPORT PHYSICAL DESIGN AUTOMATION

by

#### Robin Arthur Rutenbar

Chairman: Daniel E. Atkins

Special computer architectures for design automation (DA) problems are a practical solution to manage the increasing complexity of designing large integrated systems. A class of cellular architectures is studied which is applicable to physical DA problems that are cellular in nature: problems well-represented on a cellular grid with strongly local functional dependencies. The Raster Pipeline Subarray (RPS) class is a systolic organization, the central features of which evolved historically in classical picture-processing applications. RPS-structured DA engines have several attractive engineering properties: transparent expansion of processing capacity with a linear pipeline, direct accommodation of large grids with the raster data format, and application to differing tasks with programmable pipeline stages.

This thesis studies routing and integrated circuit design rule checking in an RPS environment. An experimental hardware/software RPS environment is constructed around existing RPS hardware; tools are developed to support the design and debugging of large-scale RPS-based DA systems. Maze-routing is the major application of interest; a mapping of maze-routing algorithms onto an RPS pipeline is developed and its complexity analyzed. A progression of increasingly complex, fully functional routers is implemented in the prototype RPS environment to verify feasibility. Large-scale benchmarks and comparisons with software routers show significant speedups.

Design rule checking is considered from an algorithmic viewpoint: it is shown that a formalism derived from picture-processing tasks provides an elegant conceptual and notational tool for mapping rules checking onto an RPS pipeline. Hardware implementations of some specifications are analyzed. These studies prove that existing RPS engines can be improved incrementally and gracefully: additional pipeline stages improve execution times. Experiments over a range of pipeline lengths, and extrapolations based on experimental measurements support this claim. From these experiments, detailed performance models and cost/performance metrics are developed, treated analytically, and rigorously optimized. These results are employed to deduce the necessary functionality and tradeoffs to design optimal RPS-structured DA engines.

## A CLASS OF CELLULAR COMPUTER ARCHITECTURES TO SUPPORT PHYSICAL DESIGN AUTOMATION

## by

#### Robin Arthur Rutenbar

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer, Information and Control Engineering) in The University of Michigan 1984

#### **Doctoral Committee:**

Professor Daniel E. Atkins, Chairman Professor John P. Hayes Professor Ronald J. Lomax Associate Professor Trevor N. Mudge Professor Kensall D. Wise

© Robin Arthur Rutenbar 1984

## TABLE OF CONTENTS

| DEDICATION                                     | ii   |

|------------------------------------------------|------|

| ACKNOWLED GEMENTS                              | iii  |

| LIST OF TABLES                                 | vii  |

| LIST OF FIGURES                                | viii |

| LIST OF APPENDICES                             | x    |

| CHAPTER                                        |      |

| I. INTRODUCTION                                | 1    |

| 1.1 Problem Statement                          | 1    |

| 1.2 Research Overview                          | 3    |

| 1.3 Thesis Organization                        | 6    |

| II. BACKGROUND: CELLULAR ARCHITECTURES AND     |      |

| DA ENGINES                                     | 8    |

| 2.1 Introduction                               | 8    |

| 2.2 Cellular Architectures                     | 8    |

| 2.3 DA Architectures                           | 16   |

| 2.3.1 Design Issues for DA Hardware            | 16   |

| 2.3.2 Survey and Critique of DA Engines        | 20   |

| 2.3.2.1 Routing Engines                        | 22   |

| 2.3.2.2 DRC Engines                            | 24   |

| 2.3.2.3 Placement Engines                      | 26   |

| 2.3.2.4 Simulation Engines                     | 27   |

| 2.4 DA Architectures as Cellular Architectures | 30   |

| 2.5 Summary                                    | 33   |

| III. RPS ARCHITECTURES AS DA ENGINES           | 34   |

| 3.1 Introduction                               | 34   |

| 3.2 The RPS Class: Origins and Antecedents     | 34   |

| 3.2.1 Origins                                  | 35   |

| 3.2.2 Antecedents                              | 36   |

| 3.3 Design of RPS Systems                      | 42   |

| 3.3.1 Local and Global Concerns in RPS Systems | 49   |

|     | 3.3.2  | Basic Performance Analysis                    | 44  |

|-----|--------|-----------------------------------------------|-----|

|     | 3.3.3  | Metrics for DA Engines Revisited              | 50  |

|     | 3.3.4  |                                               | 53  |

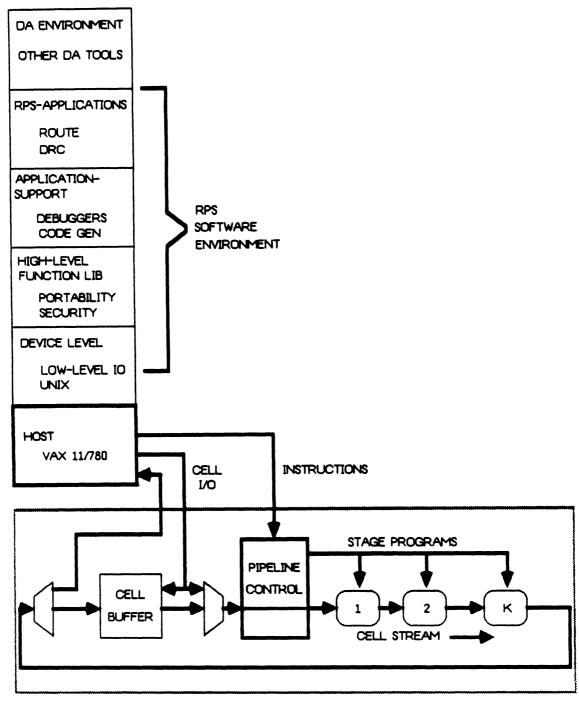

|     | 3.4 A  | n RPS Environment for DA Studies              | 63  |

|     | 3.4.1  | Hardware and Software                         | 64  |

|     | 3.4.2  | RPS Application Design                        | 68  |

|     | 3.5 S  | ummary                                        | 69  |

| IV. | ROUTI  | NG IN AN RPS ENVIRONMENT                      | 70  |

|     | 4.1 In | ntroduction                                   | 70  |

|     | 4.2 N  | Saze-Routing Reviewed                         | 70  |

|     | 4.3 E  | lementary RPS Maze-Routing                    | 74  |

|     | 4.4 C  | ne-Layer Routing                              | 79  |

|     | 4.4.   | l Local Design                                | 79  |

|     | 4.4.5  | 2 Global Design                               | 83  |

|     | 4.4.   | 3 Framing Experiment                          | 91  |

|     | 4.4.   | 4 Single-Net Experiments                      | 92  |

|     | 4.4.   | 5 PCB Experiments                             | 94  |

|     | 4.5 T  | Wo-Layer Routing                              | 96  |

|     | 4.5.   | 1 Local Design                                | 96  |

|     | 4.5.   | 2 Global Design                               | 99  |

|     | 4.5.   | 3 PCB and Gate Array Experiments              | 99  |

|     | 4.6    | Global Routing                                | 105 |

|     | 4.6.   | 1 Local and Global Design                     | 106 |

|     | 4.6.   | 2 Experiments                                 | 109 |

|     | 4.7    | Generic Concerns for RPS Routers              | 109 |

|     | 4.7.   | 1 The Effects of Statelessness                | 110 |

|     | 4.7.   | 2 Framing                                     | 112 |

|     | 4      | .7.2.1 An Approximate Model of Framing        | 113 |

|     | 4      | .7.2.2 Optimal Framing by Dynamic Programming | 115 |

|     | 4.8    | Connections to Picture-Processing Revisited   | 126 |

|     | 4.9    | Summary                                       | 126 |

| v.  | DESIG  | ON RULE CHECKING IN AN RPS ENVIRONMENT        | 128 |

|     | 5.1 I  | ntroduction                                   | 128 |

|     | 5.2 I  | ORC Reviewed                                  | 129 |

|     | 5.3 I  | Elementary DRC in an RPS Environment          | 132 |

|     | 5.4 I  | Local Design of Simple Tolerance Checks       | 134 |

|     | 5.5    | DRC Experiments                               | 138 |

|     | 5.6    | Extensions to Alternative Mask Operations     | 141 |

|     | 5.7    | Summary                                       | 145 |

| VI.    | DESIGN TRADEOFFS FOR RPS-STRUCTURED            |

|--------|------------------------------------------------|

|        | DA ENGINES                                     |

|        | 6.1 Introduction                               |

|        | 6.2 Local Design of RPS-Structured DA Engines  |

|        | 6.2.1 Buffering Scheme                         |

|        | 6.2.2 Subarray Storage                         |

|        | 6.2.3 Subarray Processor                       |

|        | 6.3 Global Design of RPS-Structured DA Engines |

|        | 6.4 Summary                                    |

| VII.   | CONCLUSIONS                                    |

|        | 7.1 Summary and Contributions                  |

|        | 7.2 Extensions and Future Research             |

| A PPEN | NDICES                                         |

| nini t |                                                |

| スロロしし  | OGRAPHY                                        |

## LIST OF TABLES

### TABLE

| 2.1        | Survey of Routing Engines                        | 23  |

|------------|--------------------------------------------------|-----|

| 2.2        | Survey of DRC Engines                            | 25  |

| 2.3        | Survey of Placement Engines                      | 26  |

| 2.4        | Survey of Simulation Engines                     | 28  |

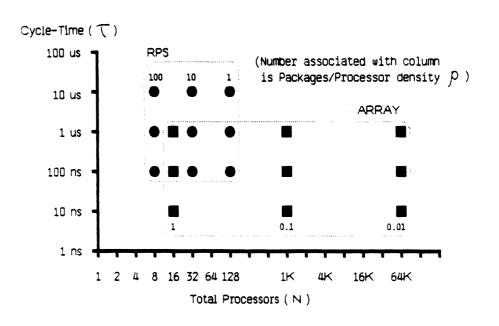

| 3.1        | Candidate RPS and Array Systems                  | 60  |

| 3.2        | RPS System Hardware                              | 66  |

| 4.1        | Local Design for One-Layer RPS Router            | 83  |

| 4.2        | Machines for RPS/Software Maze-Router Comparison | 94  |

| 4.3        | Local Design for Two-Layer RPS Router            | 99  |

| 4.4        | Local Design for RPS Global Router               | 109 |

| 4.5        | Predicting Optimal Frame Increment               | 115 |

| 4.6        | Comparison of DP Routing Times with One-Layer    |     |

|            | Benchmark                                        | 123 |

| 5.1        | DRC Strip Experiments                            | 140 |

| <b>5.2</b> | Estimated DRC Times for 4096 × 4096 Mask         | 140 |

## LIST OF FIGURES

## **FIGURE**

| 2.1  | A Taxonomy of Cellular Processors                    | 10  |

|------|------------------------------------------------------|-----|

| 2.2  | ICN Structure                                        | 11  |

| 2.3  | Full-Array Structure                                 | 12  |

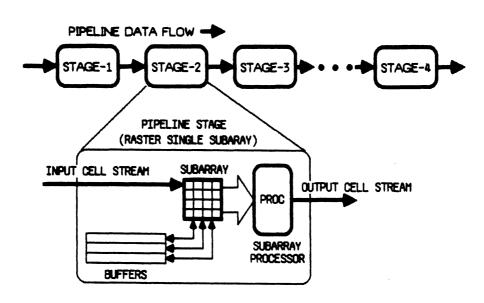

| 2.4  | Raster Single Subarray Structure                     | 13  |

| 2.5  | Raster Pipeline Structure                            | 14  |

| 2.6  | Non-Raster Multiple Subarray Structure               | 15  |

| 2.7  | Common Relationships between DA Hardware             |     |

|      | and DA Software                                      | 20  |

| 2.8  | Cellular Hardware Paradigms for DA                   | 33  |

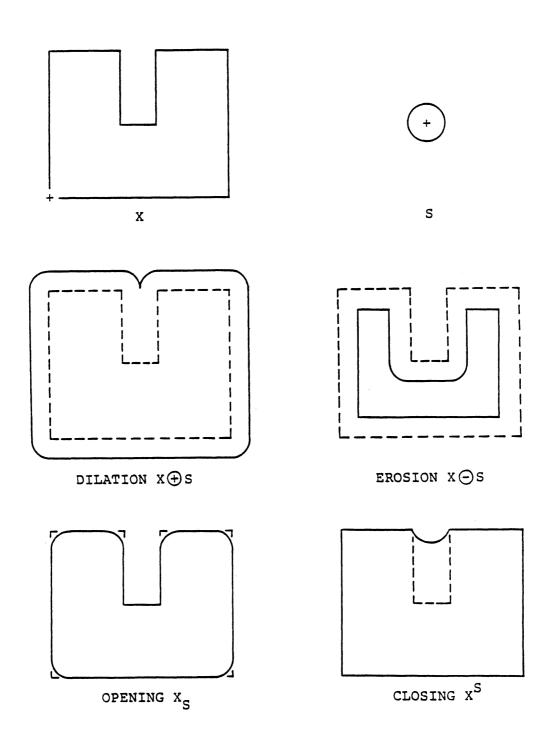

| 3.1  | Basic Morphological Operators                        | 39  |

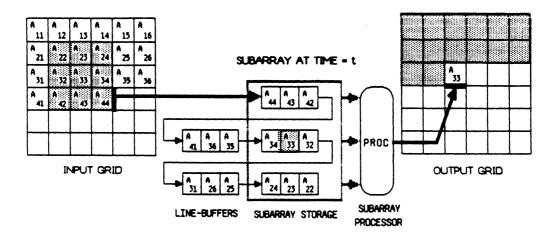

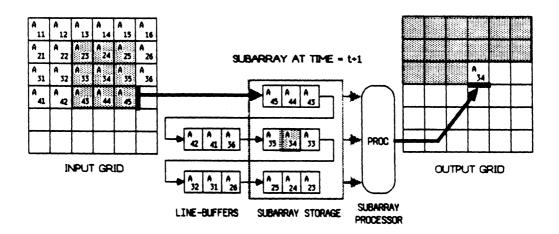

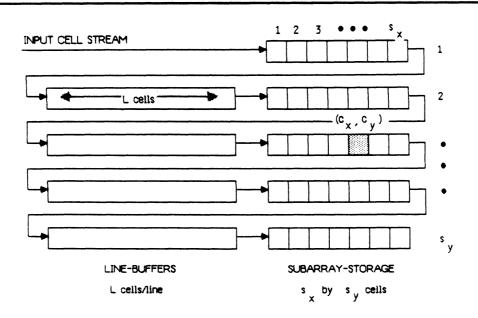

| 3.2  | Serial Flow through a 3 × 3 Stage                    | 45  |

| 3.3  | General Subarray Stage Structure                     | 46  |

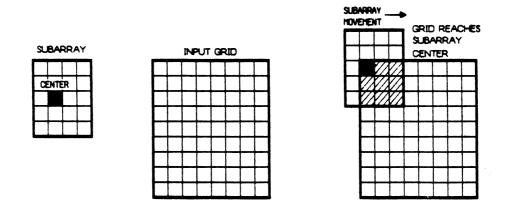

| 3.4  | Latency to Reach Subarray Center                     | 47  |

| 3.5  | Comparison of Candidate RPS and Array Systems        | 60  |

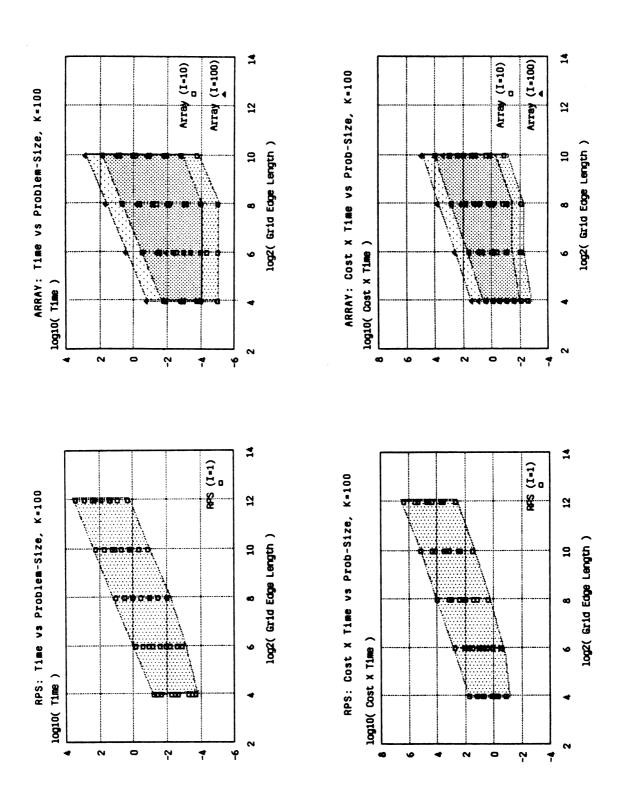

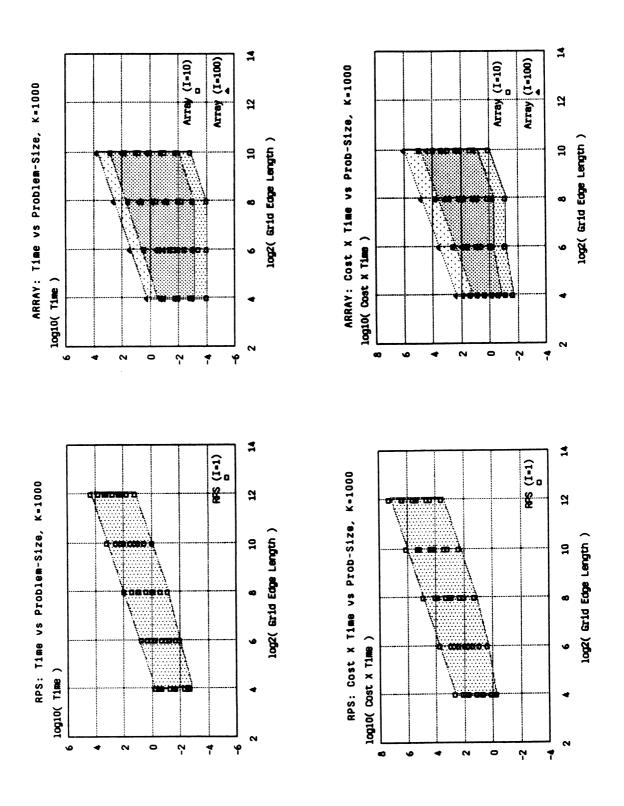

| 3.6  | RPS/Array Time, Cost X Time vs. Problem Size, K=100  | 61  |

| 3.7  | RPS/Array Time, Cost X Time vs. Problem Size, K=1000 | 62  |

| 3.8  | RPS System Configuration                             | 65  |

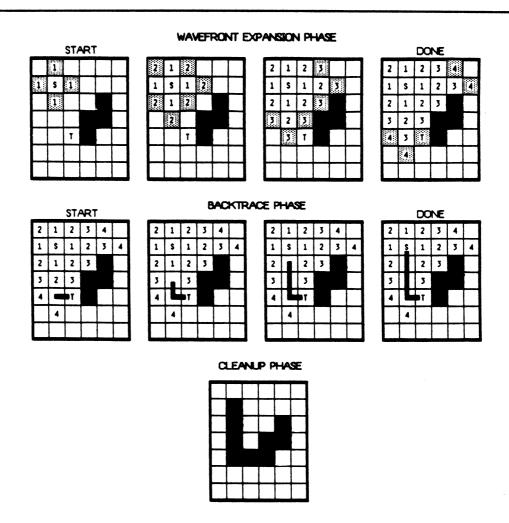

| 4.1  | Maze-Routing Phases                                  | 72  |

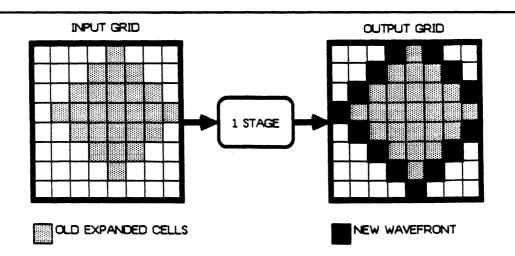

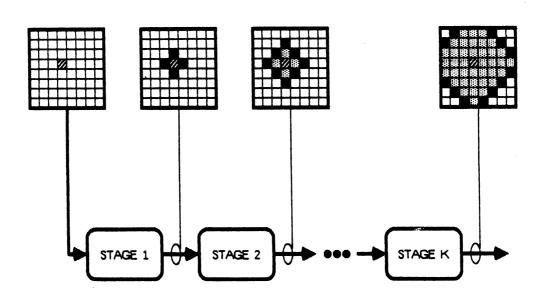

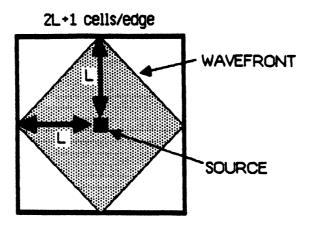

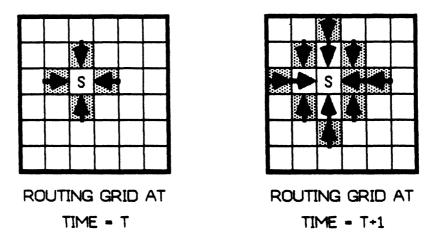

| 4.2  | Wavefront Expansion in One Subarray Stage            | 74  |

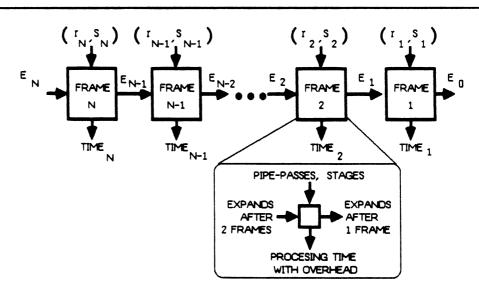

| 4.3  | Wavefront Expansion in an RPS Pipeline               | 75  |

| 4.4  | Wavefront Expansion Problem for Comparing            |     |

|      | Maze-Routers                                         | 77  |

| 4.5  | One-Layer Local Wavefront Expansion Algorithm        | 80  |

| 4.6  | One-Layer Local Backtrace Algorithm                  | 81  |

| 4.7  | One-Layer Local Cleanup Algorithms                   | 82  |

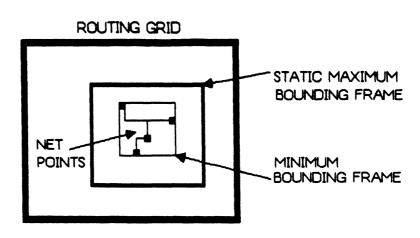

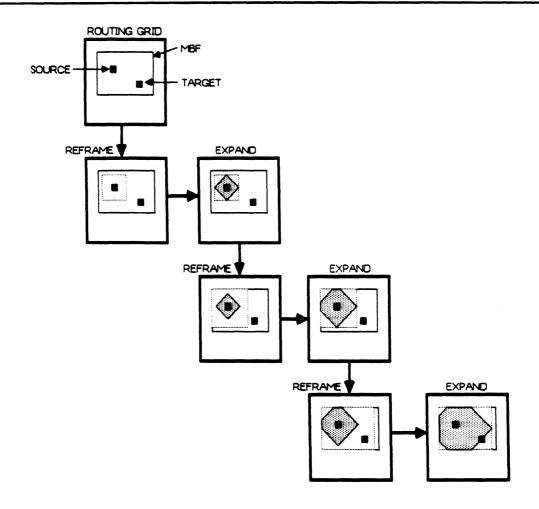

| 4.8  | Static Framing                                       | 84  |

| 4.9  | Incremental Framing                                  | 86  |

| 4.10 | One-Layer RPS Router Global Algorithm                | 89  |

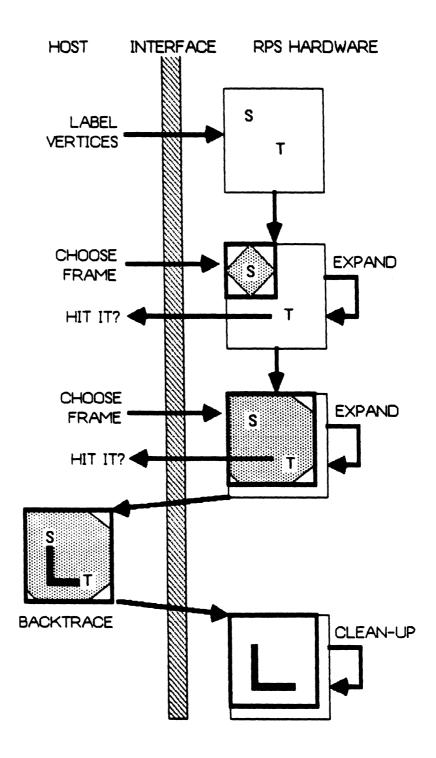

| 4.11 | Global Data Flow for One-Layer Router                | 90  |

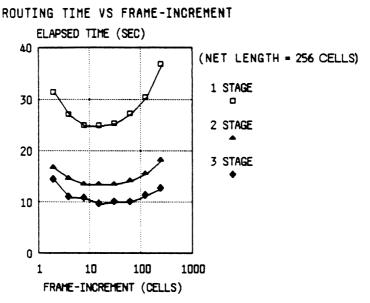

| 4.12 | Elapsed Routing Time vs. Frame-Increment,            |     |

|      | Pipeline Length                                      | 91  |

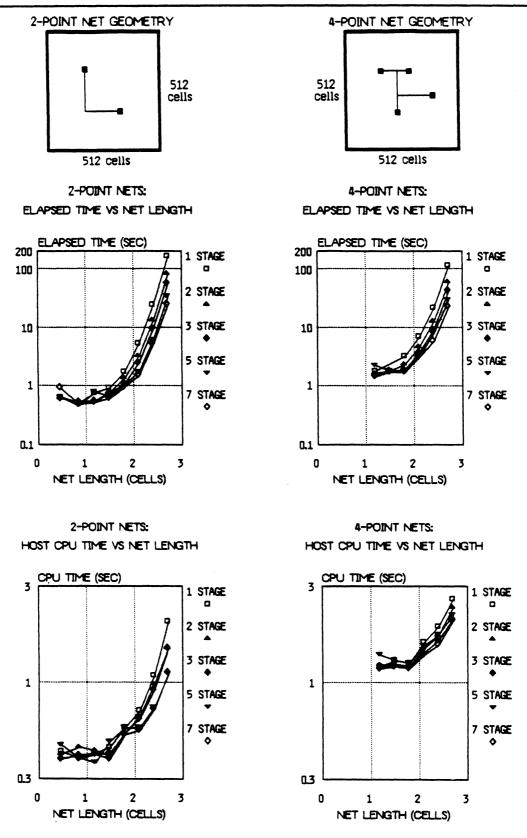

| 4.13 | One-Layer Single-Net Routing Benchmarks              | 93  |

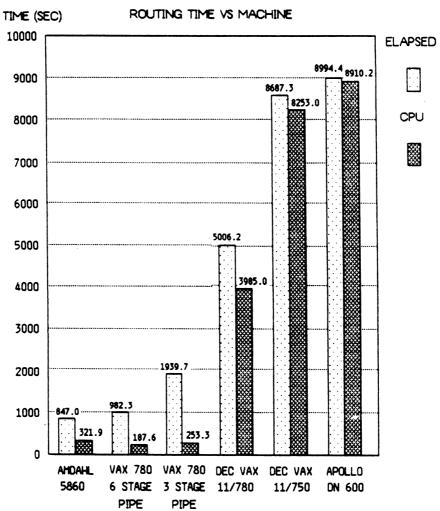

| 4.14 | RPS and Software Routers Compared for PCB Benchmark  | 95  |

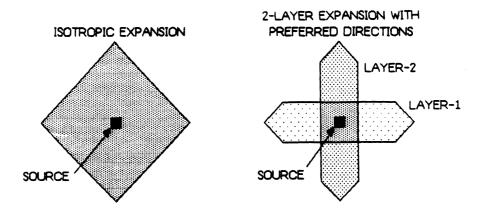

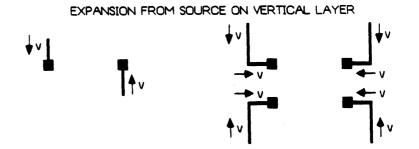

| 4.15 | Two-Layer Expansion with Preferred Directions, Jogs  | 98  |

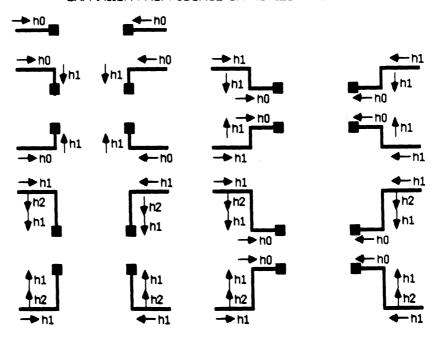

| 4.16 | Place and Route System Environment                   | 100 |

| 4.17       | Two-Layer PCB Experiment                               | 102 |

|------------|--------------------------------------------------------|-----|

| 4.18       | Two-Layer Gate Array Experiment                        | 103 |

| 4.19       | Estimated Gate Array Routing Times                     | 105 |

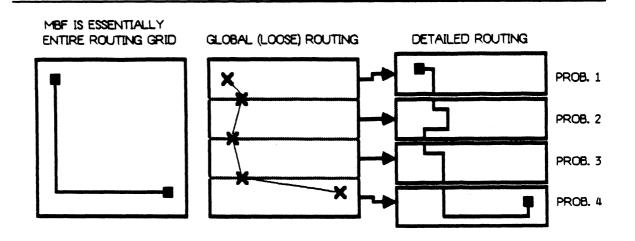

| 4.20       | RPS Global Routing Followed by RPS Detailed Routing    | 106 |

| 4.21       | Data Flow for RPS Global Router                        | 108 |

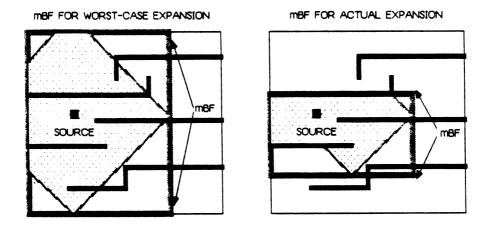

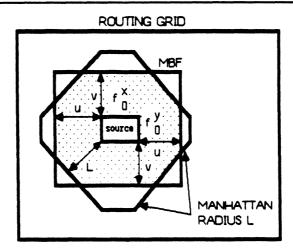

| 4.22       | Minimum Bounding Frame after Expansion                 |     |

|            | in Congested Region                                    | 111 |

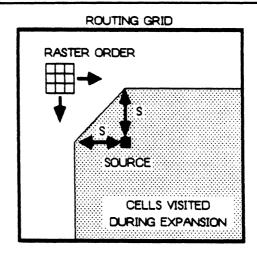

| 4.23       | Wavefront Expansion in S-Stage Non-Stateless Pipeline  | 112 |

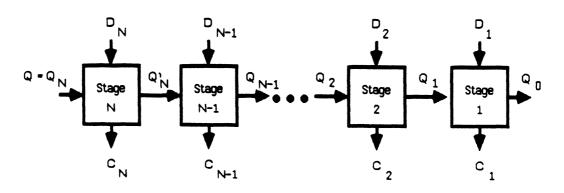

| 4.24       | Elementary Dynamic Programming Problem                 | 116 |

| 4.25       | Model of Framed Routing Problem for DP Solution        | 117 |

| 4.26       | DP Reformulation of Incremental Framing                | 118 |

| 4.27       | DP Algorithm to Obtain Optimal Framing Strategy        | 121 |

| 4.28       | Feasible Decision Variables                            | 122 |

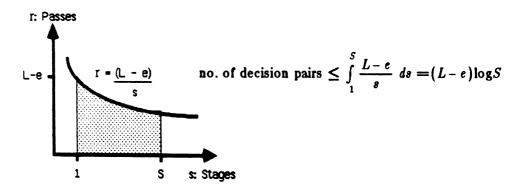

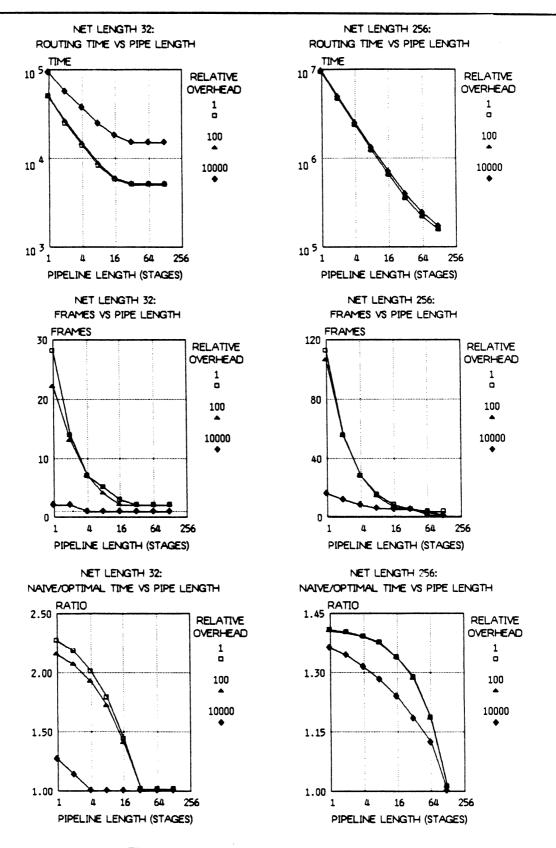

| 4.29       | Sensitivity Studies for RPS Routers                    | 125 |

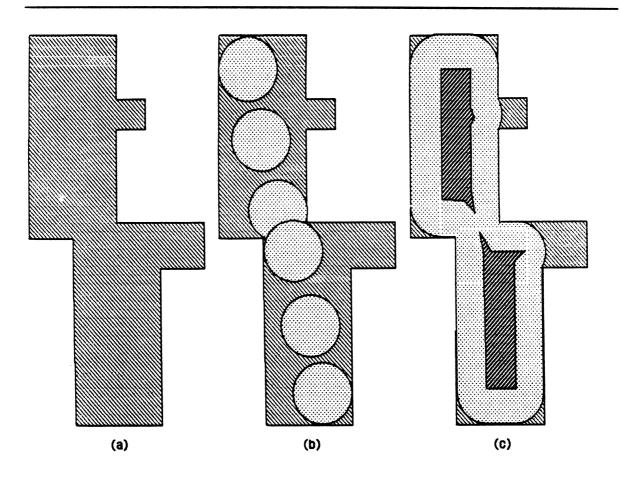

| 5.1        | Basis for Width Checking Algorithm                     | 135 |

| 5.2        | Geometric Figures for Width Check Algorithm            | 136 |

| 5.3        | Width Check Algorithm                                  | 137 |

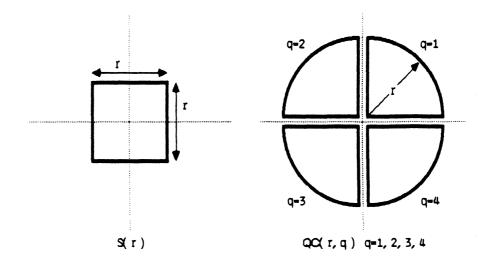

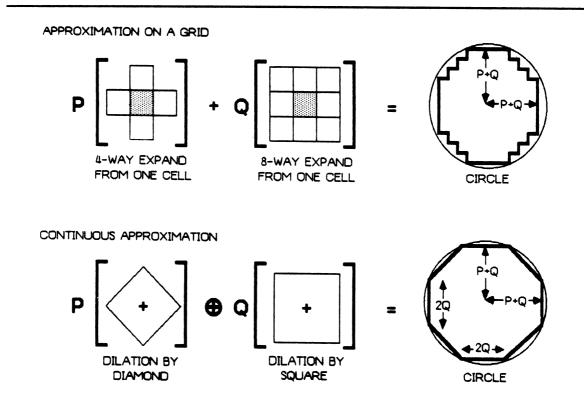

| 5.4        | Approximating Circles in a Grid                        | 138 |

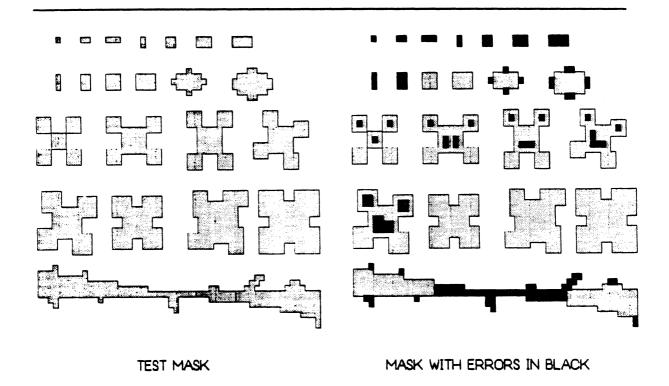

| 5.5        | 64 × 64 Test Cell and Width Checked Result             | 139 |

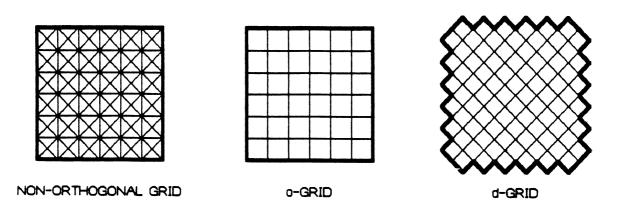

| <b>5.6</b> | Alternative Non-Orthogonal Grid Interpretation         | 141 |

| 5.7        | Example Representation on o-Grid/d-Grid                | 142 |

| 5.8        | Unrepresentable Oblique Notches                        | 143 |

| 5.9        | Attempt to Open X by S using Decoupled Computation     | 144 |

| 6.1        | Basic Subarray Stage Structure                         | 148 |

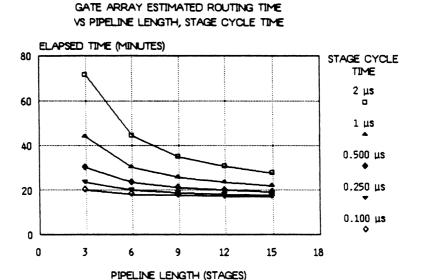

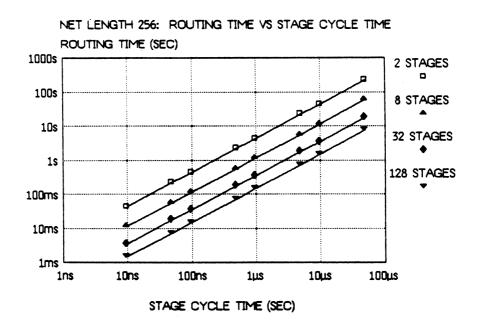

| 6.2        | Routing Time Variation with Stage Cycle Time           | 155 |

| 6.3        | Percent Time vs. Percent Nets Routed,                  |     |

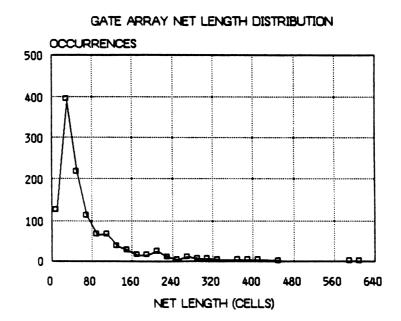

|            | Gate Array Benchmark                                   | 156 |

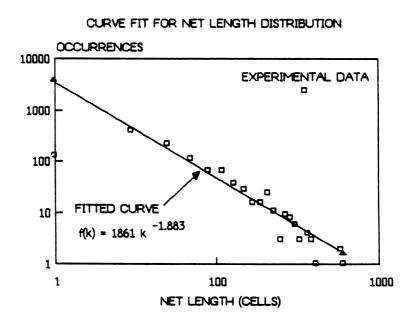

| 6.4        | Net Length Distribution and Curve Fit for              |     |

|            | Gate Array Benchmark                                   | 158 |

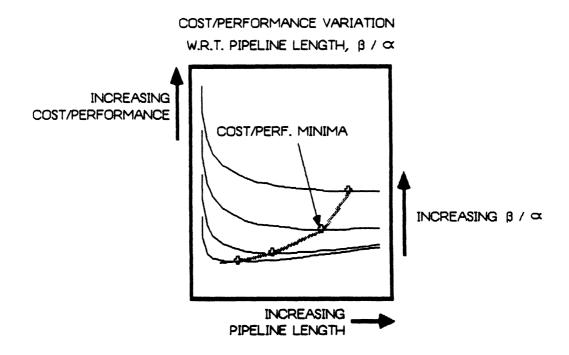

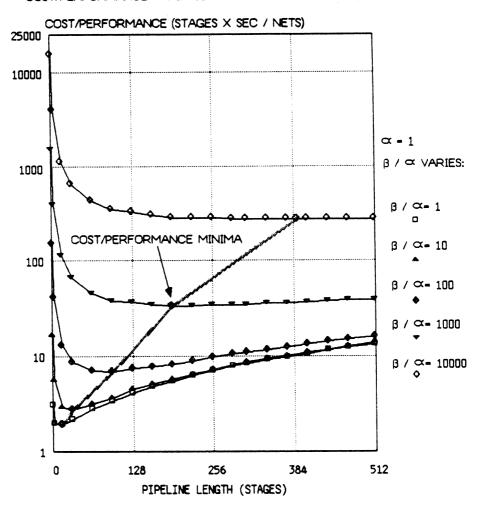

| 6.5        | Predicted Shape of Routing Cost/Performance Curves     | 161 |

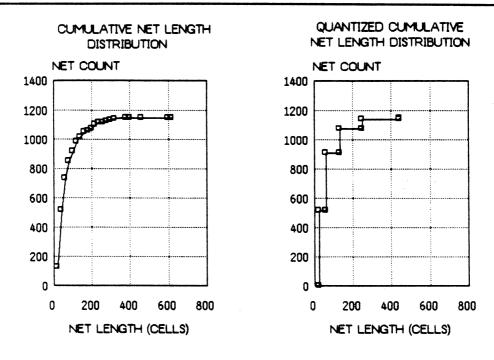

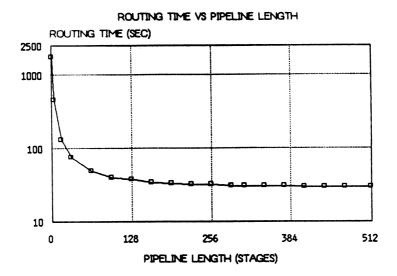

| 6.6        | Measured and Quantized Cumulative Length Distributions |     |

|            | for Gate Array Benchmark                               | 162 |

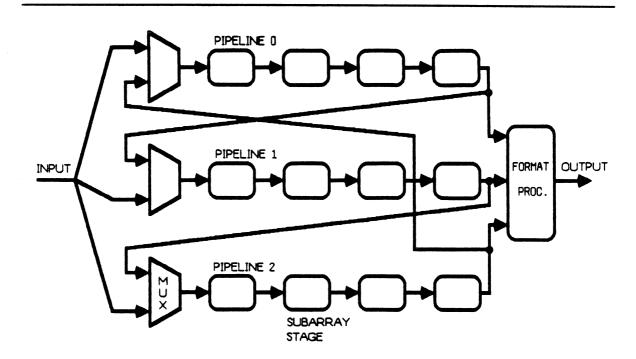

| 6.7        | Gate Array Routing Time, Cost/Performance Variation    | 163 |

| 6.8        | Parallel Pipeline Architecture                         | 165 |

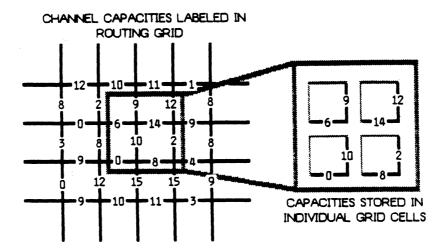

| R 1        | Basic Cell Representation for Global Routing           | 177 |

## LIST OF APPENDICES

## APPENDIX

| Α. | LOCAL ALGORITHMS FOR TWO-LAYER ROUTER | 173 |

|----|---------------------------------------|-----|

| B. | LOCAL ALGORITHMS FOR GLOBAL ROUTER    | 176 |

#### CHAPTER I

#### INTRODUCTION

#### 1.1. Problem Statement

The successful implementation of increasingly complex integrated systems demands the existence of increasingly sophisticated design automation tools. Traditional DA research--for example, mathematical analysis of DA algorithms and data-structures, application of software structuring techniques to mask layout, and use of databases to manage the design process--has produced software tools running on conventional serial computers. These tools are limited in three fundamental ways: by the inherent complexity of the problem, by the efficiency of the coded implementation, and by the resources of the machine on which the code runs. To overcome these three limitations recent attention has focused on special-purpose hardware for DA tasks. The strategy is to structure a machine architecture to exploit the task's inherent parallelism, replace software with hardware and firmware, and include precisely those resources critical to the task's solution.

The increasing cost of solving such DA problems can render general-purpose serial computers incapable of supporting a particular DA task. This application-dependent expense, measured in execution time or necessary machine resources, may arise because a problem is inherently too large, or because the preferred solution method requires complex or costly algorithms unaffordable when applied to a realistic problem. For example, a simple design rule check on the layout of a small mask is straightforward, but the same check performed on an entire microprocessor layout may be so expensive as to preclude performing the check as often as desired; the difficulty arises from the problem size. Similarly, maze-routers offer a wide

range of sophisticated performance, but may be unaffordable in practice due to the costly cell-by-cell processing of the grids representing the routing task; the difficulty here arises because the basic method is computationally demanding. Moreover, as technology advances permit the construction of more sophisticated systems, there is no guarantee that currently tractable design tools will accommodate these advanced designs, even on the enhanced general-purpose machines that will be built with such technologies. These concerns motivate research about special DA architectures.

This thesis examines a class of cellular architectures suitable for problems in physical design automation with respect to these concerns. A class of architectures called raster pipeline subarrays is examined; individual members of the class are called RPS machines. An RPS machine is a pipeline of subarray stages which processes a large grid as a serial, raster-order cell-stream. Machines in this class are appropriate for physical design tasks that are well represented on a fixed cellular grid and characterized by local functional dependencies among cell neighborhoods. In this framework, a large problem is one that must be represented on a large grid, and a complex solution method is one that requires computationally intensive processing of single grid cells or local cell groups. Tasks such as placement, routing, design rule checking, and device extraction have previously been solved by employing a grid representation and primarily local processing. This thesis concentrates on the design and analysis of routers in an RPS environment, and also examines briefly IC mask operations such as design rule checks in this environment.

Two central features of the RPS class address the difficulties that prohibit general-purpose machines from executing large DA tasks at an acceptable cost:

#### Serial Cell-Stream

Because RPS architectures process a grid in raster order--that is, as a serial stream of grid cells--the entire grid need never reside on an RPS machine. Thus, if extremely large grids can be generated they can be processed directly as they stream through an RPS-structured DA engine.

#### Pipeline Structure

Parallelism in the form of a pipeline enables RPS machines to perform several concurrent operations on grid cells streaming through the pipeline; it is this parallelism that enables RPS machines to be fast DA engines. Programmable pipeline stages provide the flexibility to accommodate a range of complex DA tasks adequately modeled in a cellular framework. Modular pipeline stages provide a practical mechanism to achieve precisely the performance required for the tasks at hand: small machines with short pipes can be upgraded to more powerful machines by the addition of pipeline stages.

Direct accommodation of a range of problem sizes and applications, and incremental expansion of processing power are the unique features that distinguish the RPS class as particularly cost-effective for DA tasks. This thesis examines in detail how these features affect the formal design, implementation, and analysis of RPS-structured DA engines.

#### 1.2. Research Overview

The research undertaken in this thesis can be partitioned into four broad, related areas:

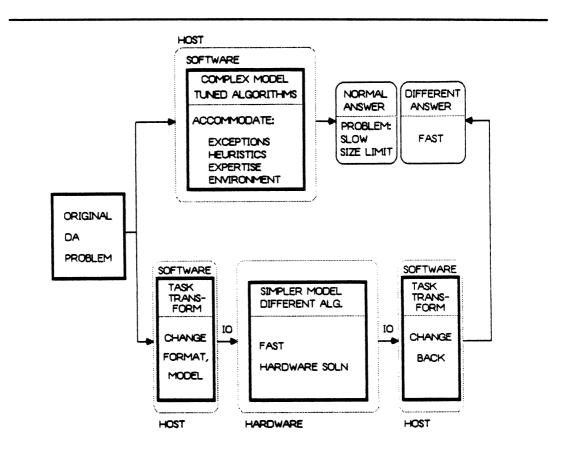

#### The Evolution of RPS Architectures as DA Architectures

As part of the overall goal to show how RPS-structured machines can function as DA engines, we survey and critique related architectures and applications. New machine architectures often appear as evolutions or generalizations of previous structures motivated by new applications. This is the case with the RPS class: in this thesis the RPS class is proposed as the appropriate abstraction of some of the novel features introduced by machines such as the cyto-computers in the field of cellular image processing [LoMS80, LoMc80]. Related cellular processors are reviewed and a taxonomy of these processors is constructed. This effort serves (1) to show how similar cellular problems have been approached with different machine structures, (2) to motivate the RPS organization, and (3) to delineate its relationship to and evolution from other cellular organizations. Similarly, DA architecture research is reviewed and critiqued in order (1) to show the range of DA problems being tackled, (2) to study how similar problems are handled on different DA machines, and (3) to motivate the typical metrics used to

evaluate DA hardware. Our cellular taxonomy is employed to categorize DA architectures intended for grid-based problems (those problems for which RPS machines are appropriate); several connections are made between such grid-based DA machines and general cellular architectures. The intent of this work to characterize the niche occupied by RPS-structured DA engines in the spectrum of DA hardware. We suggest the RPS structure as a new paradigm for DA machines, in precisely the sense that the standard parallel array has been the abstract model for several DA engines.

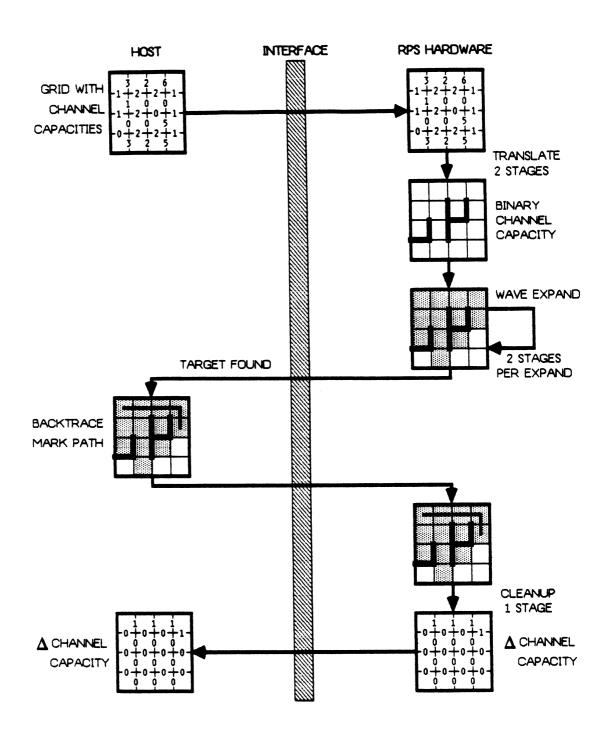

#### Experimental Studies of DA Tasks on RPS Machines

An existing family of RPS machines, the cytocomputers, is employed for experimental implementation of several DA tasks.<sup>1</sup> The experiments range from initial feasibility studies to mature, nearly complete systems. A new software environment is designed to support the development of these DA algorithms for this RPS hardware. Concrete implementations and performance statistics are examined for routing systems and DRC sub-systems functioning on the hardware. A principle goal of the experimental work is to identify performance bottlenecks, separating and abstracting those generic to RPS systems from those endemic to the current hardware.

#### Performance Evaluation and Optimization

The study of RPS architectures partitions naturally into local issues and global issues. Local issues involve the processing of individual grid cells or cell groups as a grid streams through a pipeline of subarray processors. Local concerns pertain primarily to the functional design of pipeline subarray stages and the algorithms that execute within these stages. Global issues concern strategies for handling complete grids in a pipeline environment; the design of such strategies must account for system parameters such as pipeline bandwidth and length, and host overhead. Given a specific task such as a routing problem, a solution for a specific RPS hardware environment comprises the encoding of the problem as a cellular grid, the design of algorithms to execute in the RPS pipeline stages and the design of algorithms to move the

<sup>&</sup>lt;sup>1</sup>By our definition, this family is a subset of the RPS class whose pipeline subarray stages are intended for picture-processing. These machines should not be regarded as DA engines because they are not designed to accommodate DA tasks. Despite a sub-optimal architecture for DA problems, these machines provide a useful research vehicle to realize basic variants of important DA tasks such as mase-routing and DRC.

necessary pieces of the grid through the pipeline. In this framework we examine how to achieve optimal performance for specific problems and solution techniques. Typically, solutions with minimum execution time are desired. It is shown that achieving such optimality mandates an accurate model of the basic performance of a solution method in an RPS environment. Such a model is parameterized by the values of the global constants for a specific machine realization. These models allow us to determine the best solution for a specific RPS realization. Moreover, they allow us to predict a good solution for our experimental systems, which is verified by measurement.

#### Architectures for RPS-Structured DA Engines

Given a specific DA task and a set of performance goals, for example, routing a particular class of layouts within fixed time and cost constraints, we study how to design an appropriate RPSstructured DA engine that meets these goals. Local issues are briefly addressed here because it is essential to match the functional capabilities of each RPS stage to the set of problems to be solved. RPS stage architectures with different performance characteristics are suggested for routing and IC mask operations; these proposed structures are based primarily on experience with experimental systems. Although local subarray stage functionality does impact the optimal global strategy for data movement, we concentrate on global design. Several stage architectures embodying radically different tradeoffs and, moreover, incurring radically different costs may each suffice to satisfy a set of performance constraints. We argue that it is naive to embark on a detailed stage design without knowledge of how to evaluate abstractly the alternatives and choose the best from among them. Hence, global design is addressed by employing the models previously developed to optimize the performance of specific algorithms. One goal is to evaluate the sensitivity of these algorithms to variations in global parameters, e.g., is a long, slow pipe the same as a short, fast pipe? Systematic variation of these parameters generates a set of candidate RPS systems; solving for the best performance achievable with each candidate effectively partitions the design space into classes of machines with equivalent performance. This analysis is used to evaluate the effects of cost/performance tradeoffs for different hardware configurations.

#### 1.3. Thesis Organization

The subsequent chapters of this thesis motivate our definition of the RPS class and focus on the solution of routing and DRC problems on RPS-structured DA engines.

Chapter II discusses the evolution of RPS architectures and provides the background necessary to evaluate their application as DA engines. Related cellular architectures are surveyed and a compact taxonomy is constructed to categorize them. DA architectures are likewise reviewed and critiqued, as are the metrics used to evaluate DA machines. Parallels are drawn between these cellular machines and DA engines intended for grid-based DA problems; the cellular taxonomy is employed to clarify the relationships among grid-based DA engines.

Chapter III defines and characterizes the RPS class. Important antecedents to the RPS organization, including cellular algorithms and machine implementations, are summarized. It is argued that the RPS class is the appropriate abstraction of the novel features introduced by these antecedent machines. Divorced from implementation details and application constraints, this definition is the appropriate level from which to proceed toward new areas such as DA engines. A design methodology for RPS structured systems is then suggested. The engineering tradeoffs implicit in the class are examined and compared with parallel array structures. The experimental hardware/software environment developed to support our RPS DA experiments is presented.

Chapter IV examines maze-routers in an RPS environment. A progression of increasingly complex routers implemented in our prototype RPS environment is presented. We discuss the essential local and global design issues for each router. These include the algorithms that execute in pipeline stages to mark cells in the routing grid, and algorithms to move the appropriate sections of the entire routing grid through the pipeline with the greatest economy. These experimental systems illustrate fundamental performance issues common to any RPS system. Analytical models are constructed to address these issues in the general case and optimal solutions are obtained. Solutions obtained by varying model parameters enable us to extrapolate the system configuration most suitable to meet any specific performance constraints. Further, these models are used to accurately predict the measured performance of empirically tuned experi-

mental systems.

Chapter V considers design rule checking in an RPS environment. In contrast to previous research on grid-based DRC, this work concentrates on the algorithmic specification of the individual checks comprised by a complete DRC. It is shown that a formalism originally developed for binary image analysis, suitably applied, provides an elegant and precise tool for the specification of DRCs. An experimental implementation of an example specification is constructed and its performance analyzed. Other IC mask operations are briefly addressed.

Chapter VI investigates the design of RPS-structured engines intended specifically to support DA tasks. The fundamental restrictions and bottlenecks discovered in the experimental systems are reviewed briefly. Alternative RPS stage architectures embodying different tradeoffs in functionality are suggested. We concentrate on global issues such as the design of system-level parameters which must be adequately characterized before informed decisions can be made about detailed stage architectures. The sensitivity of performance metrics is examined with respect to variations in global system parameters. The models developed in earlier chapters are employed to generate candidate RPS systems embodying different hardware tradeoffs to satisfy a set of inflexible performance constraints.

Chapter VII presents concluding remarks, summarizes the basic contributions of this research, and suggests some areas for further study related to the RPS organization.

#### CHAPTER II

BACKGROUND: CELLULAR ARCHITECTURES AND DA ENGINES

#### 2.1. Introduction

This chapter connects research in the fields of cellular architecture—RPS architecture specifically—and DA architecture. A central theme of this thesis is that the RPS class represents a new approach to grid-based DA problems. To support this assertion, we survey related cellular architectures because the RPS structure is itself a cellular architecture. An extensive survey of DA engines is also presented, along with an analysis of the goals and metrics by which such machines are typically evaluated. Parallels are then drawn between architectures for cellular processing and for grid-based physical DA: each is characterized by how storage and processing power are allocated to cells in the problem. It is shown that several DA engines intended for grid-based applications can be well-regarded as instances of more general cellular structures, and hence, that architectures for general cellular problems are potential solutions for grid-based DA problems.

#### 2.2. Cellular Architectures

It is important first to be specific about the notion of a cellular architecture. For our purposes, a cellular architecture is simply one which supports a cellular grid as the primary data structure. This definition includes special hardware designed specifically for grid-based tasks, and excludes machines such as conventional mainframes that, while certainly applicable, are not strictly intended for these tasks. Note also that machines composed primarily of replicated components, that is, of replicated cells, are not necessarily cellular machines by this definition,

8

unless they are applicable to grid-based tasks. Similarly, machines need not be composed of replicated elements (cells) to be suited to cellular problems.

Research in special-purpose hardware for cellular applications spans more than two decades and has accelerated with recent advances in technology. An immediate candidate for such problems is a cellular array, and indeed, advances in technology have heralded a renaissance for arrays in many applications, including DA. However, classical two-dimensional arrays are not the only machine organization capable of efficient solution of grid-based DA problems. Architectures for solving grid-based problems have been studied extensively in fields such as image processing, pattern recognition, and mesh-based numerical analysis.

This section focuses on machines that support image-processing and pattern-recognition [PDLN79, DaLe81, DuLe81, PrUh82, Kido83, Pres83]. Discussion is restricted to these machines for three reasons. First, much of the work on cellular architectures has been in the picture-processing area because of the precise match between problem and architecture; many of the cellular machines actually constructed are intended for picture-processing activities. Second, this thesis is concerned with those DA tasks that can loosely be regarded as symbolic processing, for example mask layout operations, which more resemble picture-processing applications like pattern-recognition than they resemble numerical-computation. Third, most of the antecedents to the RPS class arose from tasks related to picture-processing; it is from solutions to some of these concrete problems that we later abstract the central features of the RPS organization. From the narrow perspective of grid-based DA we construct a taxonomy of these cellular processors emphasizing:

- how storage is allocated to the cells of a grid being processed,

- how processing power is applied to individual cells or groups of cells,

- how processing elements and storage elements are interconnected.

The place of RPS architectures is described in this scheme. It will be shown later that many grid-based DA architectures fit naturally into this scheme.

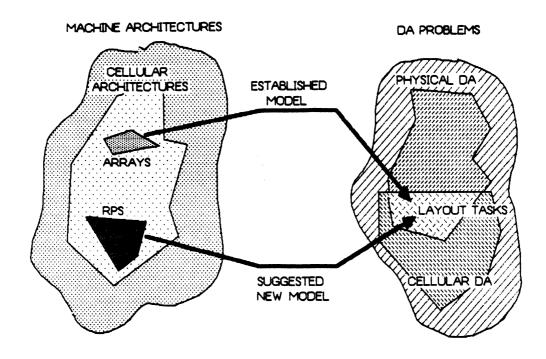

A central problem for a cellular architecture that manipulates large grids is how to distribute all grid cells over a numerically smaller set of processors. In image-processor architecture this problem has been referred to as windowing [Pres83]. Because the grids representing real images span the range 10<sup>2</sup> to 10<sup>5</sup> cells on a side, it is generally impossible to allocate a unique physical processor to each cell. Instead, the grid must be manipulated in subsections or windows. For our purposes, the shapes of these discrete sections, their acquisition, their path to and from processing elements, and the amount of parallelism in data-movement and data-manipulation define the architecture.

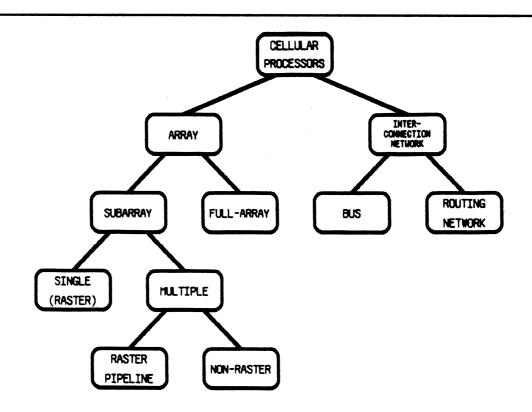

Fig. 2.1 shows a taxonomy emphasizing these features. It has three salient points. First, because the ultimate goal here is to illuminate DA architectures, this scheme is just large enough to contain most of the interesting grid-based DA architectures of which we are aware; cellular architectures that have no close analogue in current DA machines (e.g., pyramid machines) are simply omitted. Accordingly, it is not intended to be formal in the sense that the categories within the taxonomy are rigid, definitive partitions. Second, it is explicitly a

Figure 2.1 A Taxonomy of Cellular Processors

hierarchical classification in contrast to other schemes [DaLe81, Pres83]. Specifying a machine by its parents in the hierarchy gives its concise relationship to other machines, emphasizing critical similarities and differences. Third, it places RPS machines in this scheme to show their natural relationship with other array organizations.

At the first level the hierarchy divides into two basic machine organizations. As noted in [DaLe81] there are machines whose architectures are dominated by a central bus structure or, more generally, by an Interconnection-Network (ICN) structure. The other basic organization is, as expected, the array structure. By array structure we mean specifically the existence of one or more spatially distributed matrices of locally connected processor/storage elements and the machinery to move data through these elements. The critical distinction between ICN and array structures is that arrays are primarily locally connected--processing elements can be considered to be embedded in a grid or lattice--whereas ICN systems admit more general, global connectivity. Each of these two basic organizations is subdivided into two classes.

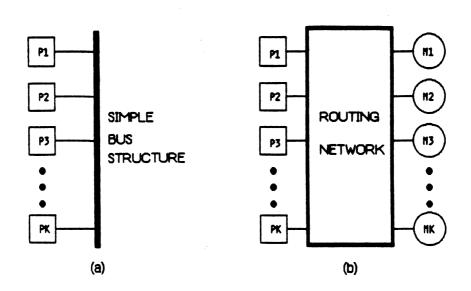

Figure 2.2 ICN Structure

(a) Bus-based structure. (b) Network-based structure.

ICN-structured machines are classified as using either a bus or a routing-network, as shown in Fig. 2.2. Although bus-based structures can be considered as a degenerate form of a network, we prefer to view them as a separate category. The label bus-structured is taken to imply systems which have few physical communication paths and in which most data transfers are multiplexed in time. Routing networks, on the other hand, imply more complex physical connectivity and more concurrent data transfers. For example, the PICAP II machine [Anto82] is centered around a single high-speed bus connecting image memories, a neighborhood processor, and a filter processor. In contrast, the proposed PASM architecture [Sieg81] employs multi-path routing-networks to connect a set of processor/memory subsystems.

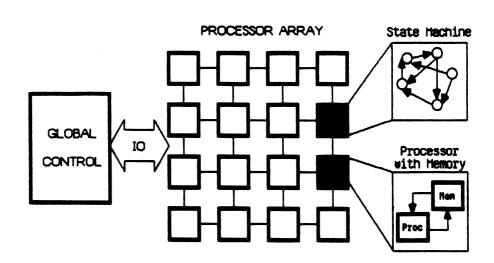

The class of array-structured machines is also divided into two subclasses. Adopting the terminology of [Pres83], array-structured machines are classified as being subarrays or full-arrays. The distinction here requires clarification, as it depends not only on structural differences, but also on the size of the array involved. The full-array would be labeled a traditional cellular array: a matrix of processor/memory pairs each connected locally to its neighbors (Fig. 2.3). Early arrays include SOLOMON [SIBM62], and the Illiac machines [McCo63, Barn68]. Modern machines in this class are typically large square arrays of simple bit-

Figure 2.3 Full-Array Structure

processors with storage at each node. Examples include CLIP4, a 96 × 96 array with 32 bits/node [Duff78]; the Distributed Array Processor (DAP), a 64 × 64 array with 4K-bits/node [Ilif82]; the Massively Parallel Processor (MPP), a 128 × 128 array with 1K-bit/node [Batc80]; and the Adaptive Array Processor (AAP), whose basic building block is a single chip 8 × 8 array with 96 bits/node [Aoki82]. Some machines with large memories at each node, e.g., MPP and DAP, incorporate a notion of grid-folding: grids larger than the physical array are folded into several planes and mapped onto the storage available at each node. Some also provide for limited global communication, e.g., DAP includes an additional bus for each row and column, enabling complete row-vectors and column-vectors to be moved around the array.

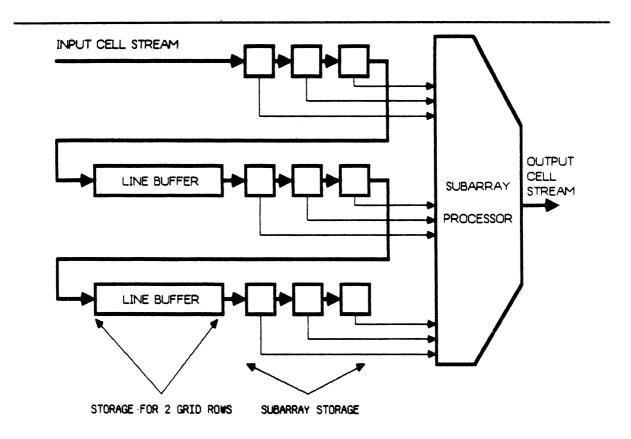

The subarray class is further subdivided, and is characterized by the range of subarray sizes and the connections between distinct subarrays. A subarray is an array much smaller than the entire grid to be processed; it is simply a processing window. The smallest subarray is a sin-

Figure 2.4 Raster Single Subarray Structure

gle neighborhood, 3 × 3 on a square lattice, while the largest is generally between 16 × 16 and 32×32. The simplest subarray organization is the class of raster, single-subarrays shown in Fig. 2.4. The idea is to process the entire cell grid in a serial stream (raster order) as it passes by a subarray processor. To do this, shift-registers are introduced as buffers for a few rows of the grid. As the stream passes through the buffers and the processor, enough of the grid is present to insure that each subarray of cells eventually arrives at the subarray processor to be processed. The GLOPR machine [PrNo72] is an early example of this using a hexagonal subarray and operating on a single bit-plane; the Texture Analyzer machine [KISe72] is a similar contemporary. Although single-subarray systems need not employ a raster structure as in Fig. 2.4, it turns out that subsequent non-raster machines generally use more than one subarray. Hence, this category actually implies a raster organization.

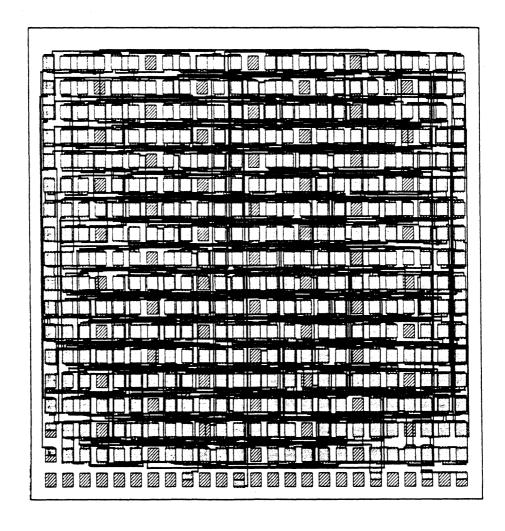

The subarray class is not restricted to a single subarray processing element. The second subclass contains the multiple-subarray machines and is itself subdivided. Because the single subarrays just discussed output a data stream with format identical to the input stream, it is possible to connect several in a pipeline. Here the individual processors are called stages, and the entire machine is a raster pipeline subarray (see Fig. 2.5). This is the organization of the

Figure 2.5 Raster Pipeline Subarray Structure

cytocomputer family [LoMc80, LoMS80]. The RPS organization and its antecedents are treated more fully in Chapter III.

Multiple subarrays are not restricted to a raster input format. Non-raster organizations use several interconnected subarray memories and subarray processors to concurrently process several pieces of a complete grid (see Fig 2.6). The major difference between these machines and the apparently similar ICN-based machines is a matter of emphasis. Of primary interest in multiple subarrays is the physical design of the subarray buffers and processors, with their interconnections of secondary interest. In ICN structures much of the architecture is subordinated to the interconnection scheme. This is perhaps the most general subarray structure, since we define it basically in terms of the structure it lacks. An early example is the diff3 machine [PDLN79] with four fixed-size binary image memories connected to eight table-driven subarray processors. A modern example is the Preston-Herron Processor (PHP) [HFPS82], in which three cell memories communicate with sixteen table-driven processors.

From this brief survey, some important points emerge. As claimed earlier, not all machines intended for cellular problems have a full-array structure. These alternative structures can be considered to be engineering responses to the problem of constructing an *ideal* full-array-one processor per cell. The engineering constraint is the inability to construct such a

Figure 2.6 Non-Raster Multiple Subarray Structure

large array economically. Thus, the raster single-subarray structure of GLOPR is a very early answer to the problem, conceived at a time when only one subarray processor was technologically feasible. The raster pipeline subarray structure of the cytocomputer family is a subsequent answer, derivable from this earlier structure, conceived at a time when multiple processors became feasible. Non-raster multiple subarrays such as the PHP illustrate another non-array direction made possible when multiple processors became feasible. Hence, we argue that the development of the RPS structure appears as a natural evolution from earlier subarray forms. This is in contrast to other classification schemes [DaLe81, Pres83] in which the RPS cytocomputers are inappropriately categorized as completely disjoint from all other cellular organizations.

#### 2.3. DA Architectures

We turn now from general cellular structures to DA machine structures. This section examines design issues for DA engines and surveys proposed and constructed DA engines. This will provide background necessary for a later evaluation of RPS-structured DA engines.

#### 2.3.1. Design Issues for DA Hardware

This section reviews key issues related to the design of special purpose DA engines. Issues common to the design of standard computing machines are not stressed. Rather, we review the consequences of dedicating hardware to DA tasks.

Adshead [Adsh82a], and Abramovici et al. [AbLM82] briefly suggest several positive attributes of successful DA hardware, and some potential drawbacks. Our discussion expands on this theme. We identify seven relevant design issues: task model and architecture, speed and cost-effectiveness, range of application, task representation and limitations, hardware/software boundaries, modularity, and host environment. Although these will be treated separately, the partition is somewhat artificial; design choices in one area force tradeoffs in another. These seven areas can be considered metrics by which to evaluate the performance of a specific DA engine.

#### Task Model and Architecture

A task model comprises the data representation and processing steps necessary to solve a problem. For example, switch-level networks and gate-level networks are models for logic simulation; local-area cellular grids, discrete polygons and hierarchical cells are models for DRC. Choice of task model is intimately bound together with choice of DA machine architecture: some models admit more parallelism or concurrency, or permit cleaner data movement, or incur less overhead than others. Trading model complexity (substituting simpler models) for speed is common; specific model/architecture tradeoffs are examined in the subsequent survey section.

#### • Speed, Cost-Effectiveness

The central motivation for migration of DA tasks into hardware is to decrease execution time: moderately large problems become cheap, perhaps interactive; previously intractable problems become manageable; more passes through the design cycle are feasible, permitting a more thorough search of the design space, and yielding a higher chance of success before an irrevocable commitment to physical implementation. Nevertheless, improvement upon the best available (affordable) software time is not the sole motivation. From an engineering standpoint, these systems must also be cost-effective to be practical. For example, a hardware system offering significantly more performance than a mainframe computer for the same cost as a mainframe should be considered cost-effective, as should a system offering mainframe performance for the cost of a workstation. Almost any DA algorithm can be accelerated by hardware; we argue that the imposed constraint of cost-effectiveness drastically reduces the number of alternative hardware approaches that will compete successfully.

#### • Range of Application

The issue of whether to build a machine that handles one problem or a range of problems involves tradeoffs between speed and flexibility. A single-purpose machine can be optimized more fully than a multi-purpose machine. A single purpose machine may need to achieve significantly more performance than the multi-purpose machine if it is to be as cost-effective.

#### • Task Representation, Task Limitations

A hardware solution may require that the common representation of a DA task (i.e., the software representation) be transformed into something suitable for the hardware. Likewise, the result may require a transformation back into the common representation. These processes must be accounted for if they are time-intensive and can degrade overall performance. There may also exist hard limits on the allowable size of the task that can be processed in hardware, limits imposed by the physical structure of the DA engine. Practical hardware must accommodate both the complexity of current systems and the foreseeable growth of VLSI systems.

#### Hardware/Software Boundaries

A common view of design is one of descent through decreasingly abstract, increasingly physical levels in a hierarchy, a progression from behavior toward implementation. In such a model, a DA task is typically a transition between levels of the hierarchy. We might suppose that special DA hardware replaces entire steps in the descent, but such a view is an overly restrictive simplification. In a real system it will be necessary to address during design the location of the boundaries between the DA engine and its environment, which we assume is mostly software. This is of concern for three reasons. First, not all phases of any DA task necessarily have a structure that justifies hardware implementation. Some phases may have little parallelism or concurrency (e.g., book-keeping operations) and no reasonable fit onto the rest of the DA engine; these may be adequately performed in the host environment. Second, the engine itself may be programmable and require software support from the host environment. Third, the DA engine will in any event need to communicate with other levels in the hierarchy, which are likely to be implemented in software.

#### Modularity

Modularity is closely related to questions of range-of-application and task-limitations. A modular system can be expanded or augmented, without complete redesign, to accommodate larger or different tasks. This implies some tradeoff against speed: modular systems may incur more overhead than tightly integrated systems that satisfy critical time

constraints for a select set of problems. However, modular systems may be more costeffective: they need not be redesigned to accommodate increasingly complex problems.

Note that modularity applies both to the hardware and software components of a DA

engine. If we assume that the primary competitor to a DA engine is a large software

package running on mainframe computer, then any software component of the engine

must be at least as maintainable as the competing software package. This becomes clearer

while reflecting upon the fact that the hardware engine may require arcane and subtle programs (managing parallelism, scheduling, transformation, IO, etc) to succeed.

#### • Host Environment

Given that DA hardware replaces only portions of a descent-through-levels design, it is clear that a practical DA engine must interact with the rest of the design process. This interaction is loosely what we call the host environment and includes: IO overhead required to move problems or results to and from the hardware, programming overhead, and task representation transformation. For example, IO bandwidth between the hardware and its surrounding environment (assume configuration as a peripheral processor) is an important design issue. The advantages of a fast engine may be negated by an inappropriate interface.

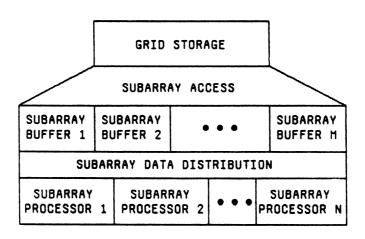

Design choices in these seven areas define the engineering of a DA engine--they determine its practical application. Fig. 2.7 illustrates common relationships among these issues, showing a simplified comparison between software and hardware approaches to one DA task. Notice the possible need for representation changes, IO overhead, and an explicit tradeoff of model complexity for speed, yielding a faster solution to a perhaps simplified form of the problem.

Figure 2.7 Common Relationships between DA Hardware and DA Software

#### 2.3.2. Survey and Critique of DA Engines

This section surveys research on DA hardware and serves two purposes. First, it provides background for a later evaluation of RPS-structured DA engines. Second, it makes concrete the evaluation metrics just discussed by providing examples of the consequences of different design tradeoffs chosen for DA engines.

Considerable DA architecture research has appeared recently, e.g., [AbLM82, Adsh82a, Adsh82b, BaST80, Blan82, BlSv81, BrSh81, Carr81, DaGe82, Dunn84, HoMW83, HoNa83, HoNS81, IoKB83, Iosu80, KaSa83, MRLA82, MuLT81a, MuLT81b, Pfis82, RuMA83a, RuMA83b, RuMA84, Seil82, SKOT83, UeKH83, vanA71, vanB83]. For clarity, we partition this body of work in two ways: level of abstraction, and intended application.

To define levels of abstraction, we observe that not all DA hardware research pertains to concrete system building activities. Rather, a survey of the literature yields a clear pattern to the evolution of DA architectures, starting from abstract notions of parallelism and algorithm restructuring, and proceeding toward concrete mappings onto machine structures and system integration. Hence, the first partition categorizes research by where it falls in this evolution from idea to system. Three phases are identified:

#### • Problem Restructuring Studies

By restructuring we mean the mapping of a standard DA task onto new hardware. This typically begins with identification of intrinsic parallelism in a DA problem or a critical performance bottleneck in an algorithm. The next step is a suggested architectural solution, for example: a machine organization, instruction set, or technology enhancement to an existing structure. The final step is a demonstration that this solution is feasible, usually by simulation of small, well-structured DA tasks running on an idealized machine.

#### Machine Feasibility Studies

Engineering issues are considered in this phase. A machine feasibility study implies either a new prototype hardware system, or a retrofit of an existing special-purpose machine that demonstrates the viability of the machine organization for DA tasks.

#### System Integration Studies

In this final phase appear full-scale hardware systems interfaced with a complete DA host environment and intended to solve real-world DA problems.

The second partition categorizes DA machines by intended application. Those machines intended for a range of tasks thus appear more than once. This organization permits close comparison of differing architectures solving similar problems.

Each of the following sections reviews research directed toward one DA task. A tabular format is employed which emphasizes the central features of each contribution. Each table gives relevant references for a particular study, summarizes the DA task modeled and any assumptions about its structure, describes the architecture of the DA engine suggested for this task, gives the status of any real implementation efforts, and classifies the entire study by its

level or levels of abstraction. Important examples of design tradeoffs categorized earlier in this chapter are clarified by reference to concrete systems. We defer detailed discussion of the cellular aspects of these DA engines to a later section.

#### 2.3.2.1. Routing Engines

Table 2.1 describes research on routing hardware. The important shared characteristic of all these systems is that each implements a maze-router. Maze-routing is attractive for hardware because of the potential for parallelism in the search for paths in a cellular routing grid. All these systems are cellular by our earlier definition.

Moreover, all but two - [DaGe82] and the system examined in this thesis [RuMA84] -- are full-array organizations.

The L-machine [BrSh81] and the Wire Routing Machine (WRM) [HoNS81] are illustrative examples of different directions for model/architecture tradeoffs. Each is a full-array organization. The L-machine trades model complexity for speed: one-layer unit-cost routing is implemented as a very large array (1024 × 1024) of simple state-machines for marking the grid. This is an elegant approach, fully exploiting the parallelism of maze-routing. Practical utility, however, does not necessarily follow. Production-quality maze-routing software often employs complex path-functions and heuristics [Souk81]--techniques not easily captured in this simple model--to achieve acceptable performance. On the other hand, the WRM implements a global maze-routing algorithm of greater complexity than common software approaches, and uses special hardware to accelerate the execution speed. The algorithm [NHLV82] requires general processing elements in the array, in this case microprocessors, and uses a small, virtual array onto which is folded a larger routing grid. However, the performance improvements on the small 8 × 8 WRM prototype were at best modest: basic problems required roughly 1 minute to execute on either the WRM or a mainframe computer. Assuming that a few minutes of mainframe computer time is easily obtained and is not a burdensome delay, the added complexity of managing special hardware can detract from its acceptance, despite the hardware's obvious cost-effectiveness.

|                                                             | Model and                                                                                                                                                   |                                                                                                                                                      | Engineering                                                         | Level of                                     |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------|

| References                                                  | Assumptions                                                                                                                                                 | Architecture                                                                                                                                         | Status                                                              | Abstraction                                  |

| [BISv81],<br>[Blan82]                                       | Mase-routing for detailed wiring. Unit-cost grid; 1-2 layers. BMP has fixed size; large Virtual grids folded onto physical array of VBMP.                   | Bit Map Proc (BMP): Fixed 1024×1024 array of bit-serial proc's + mem. Each array node addressable.  Virtual BMP (VBMP): 32×32 array of               | BMP: Proposed  VBMP: 4×4 nodes under construction at Stanford Univ. | BMP:<br>Prob. Restr.<br>VBMP:<br>Mach. Feas. |

|                                                             |                                                                                                                                                             | bit-serial proc + mem. Support for folding large grids onto physical array. Each array node addressable.                                             |                                                                     |                                              |

| [HoNS81],<br>  [NHLV82],<br>  [HoNa83]<br>  (also [Bald83]) | Maze routing for global wiring. Weighted grid with expected wiring cost/demand; 2 layers. Detailed wiring proposed. Large grids folded onto physical array. | Wire Routing Machine (WRM):  32×32 array (max)  of \( \mu\) proc with mem.  Support for folding large grid onto array.  Each array node addressable. | Functional:  8×8 array  with Z80 µproc,  15Kb mem/node              | Mach. Feas.,<br>Sys. Integ.                  |

| [Adsh82a],<br>[Adsh82b]                                     | Mase routing for detailed wiring. Unit cost grid, 2 layers. Large grids folded onto physical array.                                                         | Distributed Array Processor (DAP): 64×64 array of bit-serial proc + mem. Global row/col busses for global movement. Minicomp. host.                  | DAP is commercial machine                                           | Mach. Feas.<br>Sys. Integ.                   |

| [Carr81]                                                    | Mase routing for detailed<br>wiring.<br>Unit cost grid, 2 layers.<br>Fixed grid.                                                                            | Smart Memory Array Processor: memory array with logic on one chip.                                                                                   | Chips designed                                                      | Prob. Restr.<br>Mach. Feas.                  |

Table 2.1 Survey of Routing Engines

| References                                        | Model and                                                                            | Architecture                                                                                                                      | Engineering                                         | Level of                   |

|---------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------|

|                                                   | Assumptions                                                                          |                                                                                                                                   | Status                                              | Abstraction                |

| [BrSh81]                                          | Mase routing for detailed<br>wiring.<br>Unit cost grid, 1 layer.<br>Fixed size grid. | L-Machine: 1024×1024 fixed full-array of L-cells; L-cell is state auto- maton for marking grid.                                   | Proposed                                            | Prob. Restr.               |

| [Iosu80]                                          | Mare-routing for detailed wiring. Unit cost grid, 1 layer.                           | Modular L-Machine: Partition full-array of [BrSh81] into smaller subarray chips which com- municate serially to reduce pin count. | Proposed                                            | Prob. Restr.               |

| [DaGe82]                                          | Maze routing for detailed<br>wiring.<br>Weighted grid, 2 layer PWB's.                | CAD-CALAY: Minicomp. plus: Routing-Kernel in hardware Extra µcode Cell memory Extra busses                                        | Functional:<br>LSI 11/23 +<br>Hardware kernel       | Mach. Feas.                |

| [RuMA84],<br>[RuMA83a],<br>[RuMA83b],<br>[MRLA82] | Mase routing for detailed/global wiring. Unit cost grid, 1-2 layers. Fixed grid.     | Raster Pipeline Subarray Cytocomputer: pipeline of 3×3 subarray stages, minicomputer host.                                        | Functional: employ prototype for commercial machine | Mach. Feas.<br>Sys. Integ. |

Table 2.1 continued

# 2.3.2.2. DRC Engines

Table 2.2 describes research on design rule checking hardware.

All except one system [KaSa83] employ a local-area cellular model: masks are represented as bit-planes on a large uniform grid. Design rules are local in extent, usually checked inside a small processing window. This trades complexity for speed: no electrical parameters are extracted; some incorrect errors are flagged due to connectivity problems; arbitrary obliques are not permitted. But the flattened, uniform mask representation is conducive to rapid local processing of cells.

| References                                                      | Model and<br>Assumptions                                                                                                                                                                                                                                                       | Architecture                                                                                                                                                                                        | Engineering<br>Status                                               | Level of<br>Abstraction                       |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------|

| [BISv81],<br>[Blan82]                                           | Local area DRC: mask represented as cellular grid, Manhattan geometry only. Large grid folded onto processor array; rectangles can be loaded into array by indivi- dually addressing rows/cols in array. Errors marked in grid.                                                | BMP/VBMP:<br>see routing entries                                                                                                                                                                    | BMP: Proposed  VBMP: 4×4 nodes under construction at Stanford Univ. | BMP:<br>Prob. Restr.<br>VBMP:<br>Mach. Feas., |

| [Seil82]                                                        | Local area DRC: mask represented as cellular grid, Manhattan and some 45-degree geometry. Large grid streamed through proces- sor in raster order; rasteriza- tion done elsewhere; error lo- cations sent back to host. Width, edge, boolean mask ops are hardware primitives. | Hardware Assisted DRC: Raster single subarray organization. Line buffers and custom chips for: Width-check Edge-check Derived mask check (Boolean ops) Rasterizer  µcomp. controller Minicomp. host | Functional:<br>Custom NMOS<br>chips                                 | Mach. Feas.,<br>Sys. Integ.                   |

| [RuMA84],<br>[RuMA83a],<br>[MRLA82],<br>[MuLT81a],<br>[MuLT81b] | Local area DRC: mask represented as cellular grid, Manhattan geometry only. Large grid streamed through pipeline in raster ord- er, rasterization done else- where; errors marked in grid. Implements tolerance checks on shapes in parallel in pipe- line stages.             | Raster Pipeline Subarray cytocomputer: pipeline of 3×3 subarray stages, minicomputer host                                                                                                           | Functional: employ prototype for commercial machine                 | Mach. Feas.,                                  |

| [KaSa83]                                                        | Mask represented by edges of<br>features. Width/space checks<br>on well-formed polygons with<br>Manhattan geometry.                                                                                                                                                            | Systolic DRC (SDRC): 2 systolic sort arrays (SAX, SAY) for horis, vert. edges. Linear systolic DRC array for width/space checks                                                                     | Proposed                                                            | Prob. Restr.                                  |

|                                                                 |                                                                                                                                                                                                                                                                                | in 1 dimension (hor-<br>iz or vert).                                                                                                                                                                |                                                                     |                                               |

Table 2.2 Survey of DRC Engines

# 2.3.2.3. Placement Engines

Table 2.3 describes research on placement hardware.

All these systems attempt to minimize the (possibly weighted) sum of wiring lengths between connected modules. Although this is a common model for placement, experience with large problems [Souk81] has recognized that minimum wiring length alone is insufficient to guarantee wirability, and that more complex complex metrics, e.g., weighted sum of wire lengths and maximum channel congestion, produce better results. Hence, these machines also trade some model complexity for speed.

Moreover, the similar problem restructuring for a full-array suggested by [UeKH83] and [ChBr83] presents several difficult engineering problems. The model is based on parallel inter-

| References | Model and Assumptions                                                                                                                                                                                                      | Architecture                                                                                                                                                                                                                | Engineering<br>Status          | Level of<br>Abstraction |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------|

| [UeKH83]   | Parallel pairwise interchange placement of connected modules to minimise total wiring length. Modules are vertices of graph to be embedded in a grid. Fixed size grid.                                                     | Full-array of processors with memory. Global bus connects all nodes. Global controller.                                                                                                                                     | Proposed                       | Prob. Restr.            |

| [ChBr83]   | Parallel pairwise interchange placement of connected modules to minimise total wiring length. Modules are vertices of graph to be embedded in a grid. Fixed size grid.                                                     | Full-array of processors.  Processors have a  Content Addressable Mem to store connected modules; tally-circuit to count modules in CAM connected to module in cell.  Global bus connects to all nodes.  Global controller. | Proposed                       | Prob. Restr.            |

| [IoKB83]   | Pairwise interchange of con-<br>nected modules to minimise<br>total wiring length. Solve<br>quadratic assignment problem<br>(min sum of module distances<br>over weighted nets) incremen-<br>tally after each interchange. | Module Interchange Placement Machine: 4-stage arith. pipe (solve QAP) Connections table (Mem nets/mods) µcomp controller Minicomp. host                                                                                     | Functional:<br>256 modules max | Mach. Feas.,            |

Table 2.3 Survey of Placement Engines

change of adjacent modules in a grid. [ChBr83] suggests a Content Addressable Memory (CAM) in each array-node to store module connectivity information. This presents problems for highly interconnected modules such as those on busses or clock-lines: a small CAM will not accommodate dense connectivity; a large CAM will be expensive and sparsely occupied over most array nodes. Questions of how to address realistically large problems—the problems that may justify special hardware—on a physically small array have yet to be addressed. Indeed, simulations that verify the technique for such large problems (10<sup>8</sup> to 10<sup>4</sup> modules) have yet to appear in the literature. This work is an example of the difficulty in transforming elegant ideas about restructuring into practical engineering systems.

# 2.3.2.4. Simulation Engines

Table 2.4 describes research on simulation hardware.

This has been the most active area of research in special DA hardware due to demonstrated large performance-gains achieved with special hardware. Two approaches have been investigated: event-driven simulation, in which time is quantized and components are only updated when they are scheduled to change, and compiled-code simulation, in which the network to be simulated is compiled into an executable description that is independent of network inputs. Table 2.4 shows that event-driven systems have been more numerous.

The evolving family of compiled-code simulators developed at IBM--LSM, YSE, EVE-illustrates serious, large-scale issues in system-integration. For example, the YSE is currently

constrained by the IO bandwidth of its host connection [BHST84]. Capturing simulation trace

data thus takes place at the slower host speeds, rather than native YSE speed, and the overhead

makes the YSE slower than a mainframe when applied to modest problems, despite its superior

performance on large problems [Dunn84]. [PfKr82] and [KMMN83, HKMR83] discuss the

task-transformation software and user-interface software necessary to support the compiled-code

model on the YSE and LSM respectively. This work also exemplifies some range-of-application

tradeoffs. Although easily regarded as a gate-level simulator, [BHST84] shows how MOS pass-

<sup>&</sup>lt;sup>1</sup>See [WeLF82] for a discussion of CAMs in array structures.

| References                                      | Model and Assumptions                                                                                                                                                                                        | Architecture                                                                                                                                                                                                                      | Engineering<br>Status                                  | Level of<br>Abstraction     |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-----------------------------|

| [vanA71]                                        | Event driven gate simulation                                                                                                                                                                                 | Boeing Computer<br>Simulator                                                                                                                                                                                                      | Functional:<br>48K gates max                           | Mach. Feas.,<br>Sys. Integ. |

| [HoMW83],<br>[BLMR83],<br>[KMMN83],<br>[HKMR83] | Compiled gate simulation (non-event driven); every gate evaluated every cycle:  Variable gate delay; a gate is a 6-input 1-output function over 2-bit values. Software schedules processing over a crossbar. | Logic Simulation Machine (LSM): 1 control proc. logic proc's (eval. logic expr) array proc's (sim. memory) 64×64 crossbar (communication) mini. interface mainframe host                                                          | Functional:<br>64512 gates max                         | Mach. Feas.,<br>Sys. Integ. |

| [Pfis82],<br>[Denn82],<br>[PfKr82]              | Same as LSM, except: unit gate delay and rank-order simulation (~ zero gate-delay); a gate is a 4-input 1-output function over 2-bit values.                                                                 | Yorktown Simulat. Engine (YSE): 1 control proc. logic proc's (eval. logic expr) 16×16 crossbar (communication) bus bus-controller (comm. all proc)  µcomp. interface mainframe host                                               | Functional: 16 logic proc. 0 array proc. 64K gates max | Sys. Integ.                 |

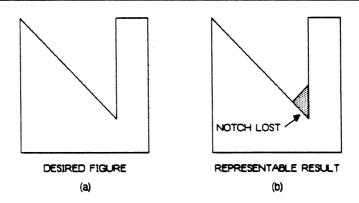

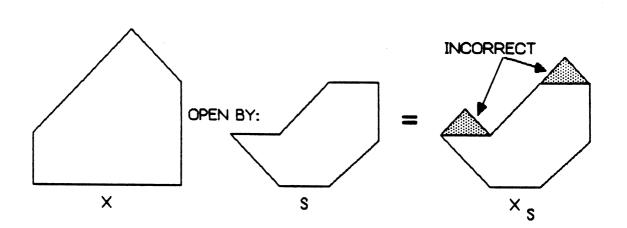

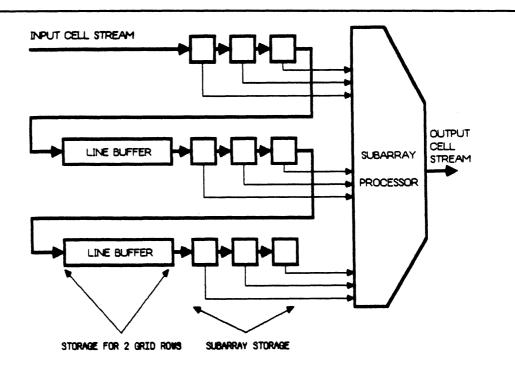

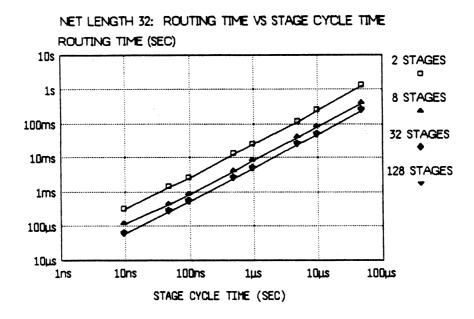

| [Dunn84]                                        | Same as YSE                                                                                                                                                                                                  | Engin. Verification Engine (EVE): same as YSE but 256×256 crossbar, 2.0M gates max, 12.8Mb array memory.                                                                                                                          | Under construction<br>at IBM                           | Sys. Integ.                 |