# **Amorphous In-Ga-Zn-O Thin Film Transistor for Future Optoelectronics**

by

Tze-Ching Fung

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2010

#### **Doctoral Committee:**

Professor Jerzy Kanicki, Chair Professor Kensall D. Wise Associate Professor Cagliyan Kurdak Associate Professor Jamie D. Phillips © Tze-Ching Fung 2010 To Dad, for teaching me the value of work.

To Mom, for encouraging me to complete the degree.

And to My Younger Brother, for sharing with me all the joy in life.

# Acknowledgements

I think I am very fortunate to have Professor Jerzy Kanicki as an advisor. I sincerely appreciate his constant support and advice that led me to a researcher during the course of my graduate study. I also heartily thank my doctoral committee members: Professor Kensall Wise, Professor Cagliyan Kurdak and Professor Jamie Phillips for their time and effort in helping me complete this thesis work. Many thanks also go to Professor Yogesh Gianchandani and Dr. Jack East for their support and guidance during my early years in master's program.

Much of the work in this thesis could not have been completed without the efforts of other individuals and their help is greatly appreciated. I am very grateful to Professor Hideo Hosono and Dr. Kenji Nomura from the Tokyo Institute of Technology for their generous help in preparing the PLD a-IGZO samples and for introducing us to the exciting a-IGZO research. I am also eternally grateful to Dr. Hideya Kumomi and Mr. Katsumi Abe from Canon Research Center for their assistant in preparing the a-IGZO TFT samples and for many valuable scientific discussions. Thanks to the guidance from Mr. Robert Cottle and Mr. Mark Townsend from Silvaco Inc., the ATLAS 2D numerical simulation was able to conduct smoothly. I would like to show them my appreciation. I am also thankful for the advice on noise measurement and system setup from Dr. James Ma and Mr. Yeong-Gil Kim of ProPlus Design Solutions Inc.

I also would like to thank DARPA/MTO HARDI program (Dr. Devanand K. Shenoy) and EECS department for their financial supports. Much appreciation is also due to LNF staffs. Of course, it is the unselfish support and friendship from my current and previous group members: Dr. Alex Kuo, Charlene Chen, Geonwook Yoo, Gwanghyeon Back, Dennis Feng, Dr. Chiao-Shun Chuang and Dr. Patrick Shea, that get me through one obstacle after another during the course of my graduate study. Thus, I sincerely thank them. In addition, I want to extend my devout appreciation to all my friends for their continuous care and help.

Lastly and most importantly, my wholehearted gratitude goes to my family in Taiwan for their everlasting support and encouragement.

# **Table of Contents**

| Dedication          | ••••••                                                           | ii     |

|---------------------|------------------------------------------------------------------|--------|

| Acknowled           | lgements                                                         | iii    |

| List of Figu        | ıres                                                             | . viii |

| List of Tab         | les                                                              | XV     |

| Chapter 1. Introduc | etion                                                            | 1      |

| 1.1 (               | Overview / Background                                            | 1      |

| 1.1.1               | Current status and limitation of a-Si:H TFT backplane technology | 1      |

| 1.1.2               | a-Si:H TFT backplane in photo-imager                             | 4      |

| 1.1.3               | High performance amorphous In-Ga-Zn-O TFTs                       | 6      |

| 1.2 I               | Dissertation Organization                                        | 13     |

| 2. Electrica        | al Properties of the a-IGZO TFTs                                 | 14     |

| 2.1                 | FFT Fabrication and Structure                                    | 14     |

| 2.1.1               | Common gate, pulse-laser deposition (PLD) a-IGZO TFT             | 14     |

| 2.1.2               | Common gate, radio frequency (RF) sputter a-IGZO TFT             | 16     |

| 2.1.3               | Defined gate, radio frequency (RF) sputter a-IGZO TFT            | 17     |

| 2.2 I               | Basic TFT Electrical Properties                                  | 19     |

| 2.2.1               | Common gate, PLD a-IGZO TFT electrical properties                | 19     |

| 2.2.2               | Common gate, RF sputter a-IGZO TFT electrical properties         | 23     |

| 2.2.3               | Defined gate, RF sputter a-IGZO TFT electrical properties        | 27     |

| 3. Advance          | ed Analysis of the a-IGZO TFT Electrical Properties              | 33     |

| <b>3.1</b> a        | -IGZO TFT Source/Drain Series Resistances                        | 33     |

| 3.1.1               | Transmission line analysis of a-IGZO TFT                         | 33     |

| 3.1.2               | Gate voltage dependent series resistance (R <sub>S/D</sub> )     | 39     |

|             | 3.2    | Field-Effect Mobility of the a-IGZO TFT                               | 46   |

|-------------|--------|-----------------------------------------------------------------------|------|

|             | 3.2.   | 1 Mathematical model for gate-voltage dependent filed-effect mobility | 46   |

|             | 3.2.   | 2 Parameter extraction: simultaneous method                           | 48   |

|             | 3.2.   | Parameter extraction: two-steps method                                | 50   |

|             | 3.2.   | The effect of $\mu_{eff}(V_{GS})$ on transmission line analysis       | 55   |

| 4. I        | Photof | ield-Effect Study of the a-IGZO TFTs                                  | 57   |

|             | 4.1    | Introduction                                                          | 57   |

|             | 4.2    | Experimental                                                          | 58   |

|             | 4.2.   | Common gate, inverted-staggered a-IGZO TFT                            | 58   |

|             | 4.2.   | 2 Experimental conditions and setup                                   | 60   |

|             | 4.3    | Optical Properties of a-IGZO Thin-Film                                | 61   |

|             | 4.4    | Dark a-IGZO TFT Electrical Properties                                 | 63   |

|             | 4.5    | a-IGZO TFT Electrical Properties under Illumination                   | 66   |

|             | 4.5.   | 1 Wavelength dependent a-IGZO TFT photo-response                      | 66   |

|             | 4.5.   | 2 Intensity dependent a-IGZO TFT photo-response                       | 69   |

|             | 4.6    | Photofield-Effect Analysis                                            | 72   |

| <b>5.</b> T | wo D   | imensional Numerical Simulation of the a-IGZO TFT                     | 78   |

|             | 5.1    | A Brief Review of Earlier Works                                       | 78   |

|             | 5.2    | Two Dimensional (2D) Numerical Simulation                             | 81   |

|             | 5.2.   | a-IGZO TFT structure used in simulation                               | 81   |

|             | 5.2.   | 2 Source/drain contacts, electronic affinity and band mobility of the |      |

|             |        | a-IGZO                                                                | 83   |

|             | 5.2.   | 3 a-IGZO TFT density-of-states (DOS) model                            | 85   |

|             | 5.3    | Simulation Results and Discussion                                     | 89   |

| 6.          | Impa   | ct of Defect States and Contact Resistances on a-IGZO TFT             |      |

| Ele         | ctrica | l Properties                                                          | 95   |

|             | 6.1    | The Impact of Conduction Band-Tail Slope (Ea)                         | 95   |

|             | 6.2    | The Impact of Source/Drain Contact Resistance (rc)                    | 104  |

|             | 6.3    | The Impact of Oxygen Vacancy (OV) States                              | 107  |

| 7. a        | -IGZ   | O TFT Electrical Instability                                          | 115  |

|             | 7.1    | Introduction                                                          | .115 |

|             | 7.2    | Experimental                                                          | .116 |

|             | 7.2    | 1 Rias-temperature stress (RTS) measurement                           | 116  |

| 7.2       | .2 Methodology for parameter extraction                   | 117 |

|-----------|-----------------------------------------------------------|-----|

| 7.3       | DC-BTS Electrical Instability of a-IGZO TFT               | 118 |

| 7.4       | Stretched-Exponential Model                               | 124 |

| 8. Electi | onic Noise in a-IGZO TFTs                                 | 131 |

| 8.1       | Common Low Frequency Noise Sources in TFTs                | 131 |

| 8.2       | .1 Thermal noise                                          | 132 |

| 8.2       | .2 Flicker (1/f) noise                                    | 133 |

| 8.2       | Experimental                                              | 138 |

| 8.2       | .1 Noise measurement setup                                | 138 |

| 8.2       | .2 System calibration – thermal noise measurement         | 141 |

| 8.3       | Noise Properties of the a-IGZO TFTs                       | 144 |

| 8.3       | .1 Example of the a-IGZO TFT drain current noise spectrum | 144 |

| 8.3       | .2 Noise as a function of channel area                    | 146 |

| 8.3       | .3 Noise as a function of gate voltage                    | 150 |

| 8.3       | .4 Noise from different device structures                 | 154 |

| 9. Concl  | usions and Future Work                                    | 158 |

| 9.1       | Conclusions                                               | 158 |

| 9.2       | Recommendations for Future Work                           |     |

| Append    | x – List of Publications                                  | 162 |

| Bibliogr  | anhv                                                      | 163 |

# **List of Figures**

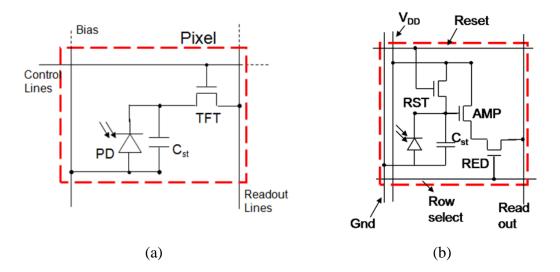

| Figure 1 | .1 Circuit schematics for (a) passive pixel sensor (PPS) and (b) active pixel sensor (APS).                                                                                                                                                                                                                             |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

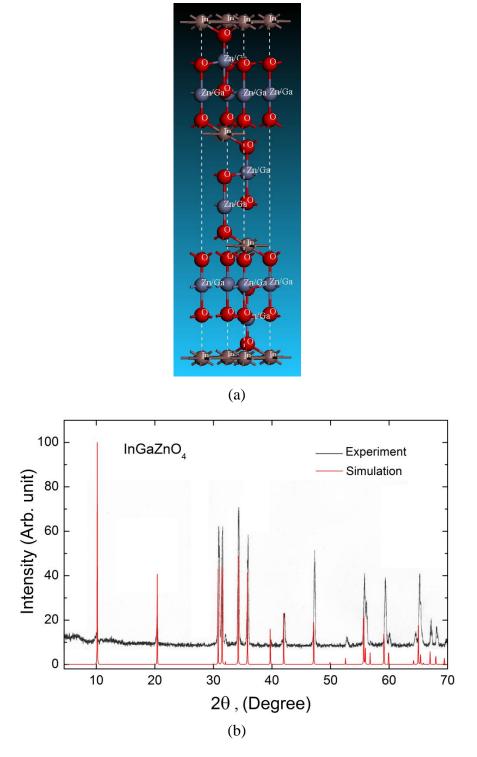

| Figure 1 | .2 (a) (Color) Structure of the InGaZnO <sub>4</sub> crystal. The brown, blue and red balls represent In, Zn/Ga and O atoms, respectively. (b) (Color) XRD rocking curves of the InGaZnO <sub>4</sub> .                                                                                                                 |

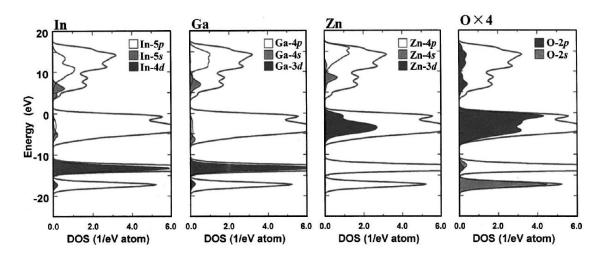

| Figure 1 | .3 Partial density-of-states (DOS) curves for InGaZnO <sub>4</sub> crystal structures 10                                                                                                                                                                                                                                |

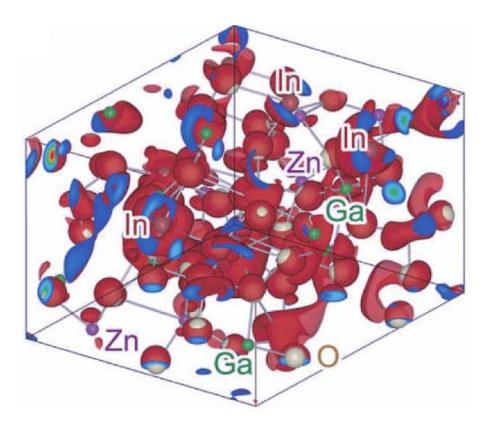

| Figure 1 | <b>.4</b> (Color) The red surfaces represent the conduction band minimum (CBM) wave function $( \psi ^2)$ in a-IGZO structure.                                                                                                                                                                                          |

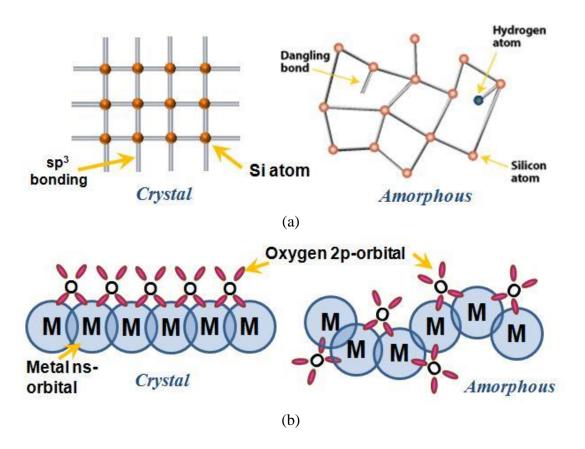

| Figure 1 | .5 Schematic orbital drawing of electron conducting pathway (conduction band bottom) in (a) conventional covalent bond semiconductors (e.g. Si) and (b) ionic oxide semiconductors.                                                                                                                                     |

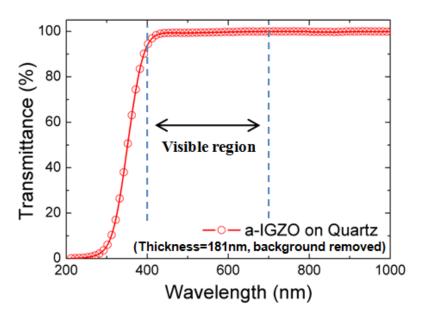

| Figure 1 | <b>.6</b> Absorption spectrum of the a-IGZO thin film                                                                                                                                                                                                                                                                   |

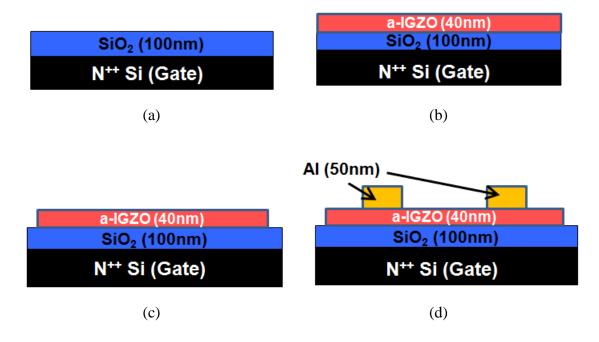

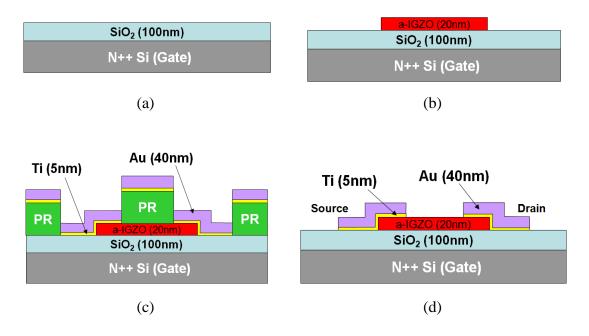

| Figure 2 | 2.1 Process flow for making the common gate, inverted-staggered PLD a-IGZO TFT                                                                                                                                                                                                                                          |

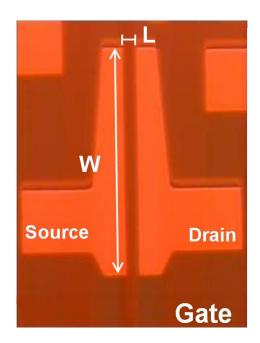

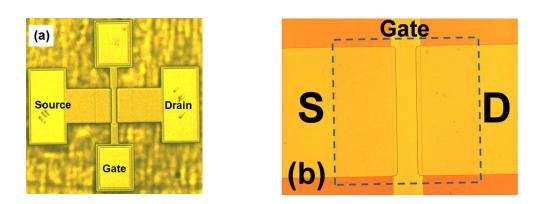

| Figure 2 | .2 Top view of the common gate, inverted-staggered PLD a-IGZO TFT 15                                                                                                                                                                                                                                                    |

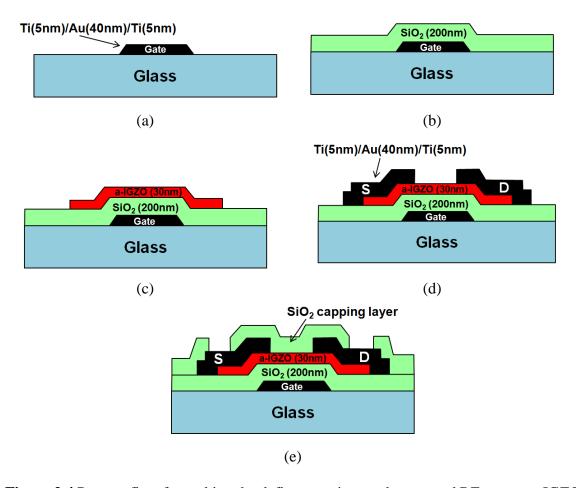

| Figure 2 | 2.3 Process flow for making the common gate, inverted-staggered RF sputter a-IGZO TFT                                                                                                                                                                                                                                   |

| Figure 2 | .4 Process flow for making the define gate, inverted-staggered RF sputter a-IGZO TFT                                                                                                                                                                                                                                    |

| Figure 2 | .5 (a) Top view of the defined gate, RF sputter a-IGZO TFT. (b) A zoom-in view of the TFT channel area.                                                                                                                                                                                                                 |

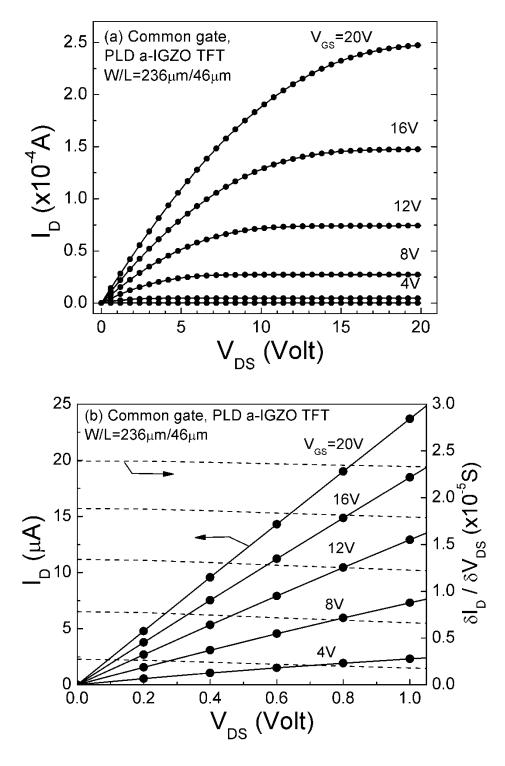

| Figure 2 | .6 (a) Output characteristics of the common gate, PLD a-IGZO TFT (with Al S/D electrodes). (b) A zoom-in plot of the output characteristics (solid curves with symbols) near the origin ( $V_{DS}$ =0~1V); derivatives of $I_D$ vs. $V_{DS}$ characteristics ( $\delta I_D/\delta V_{DS}$ , dash curves) are also shown |

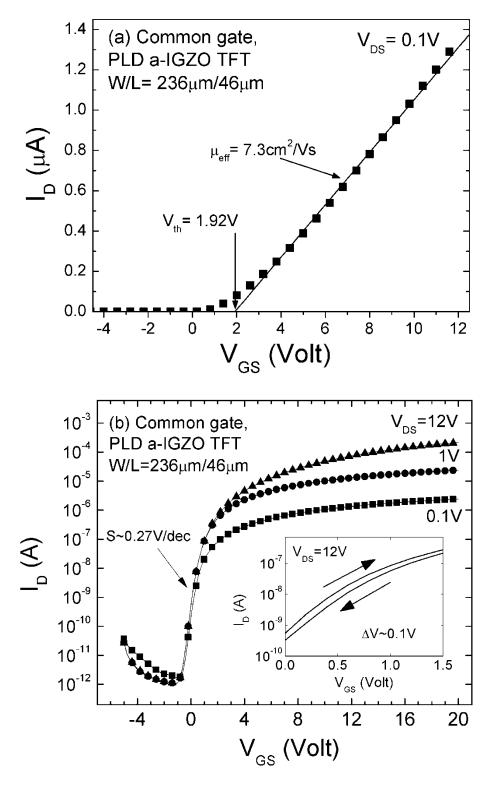

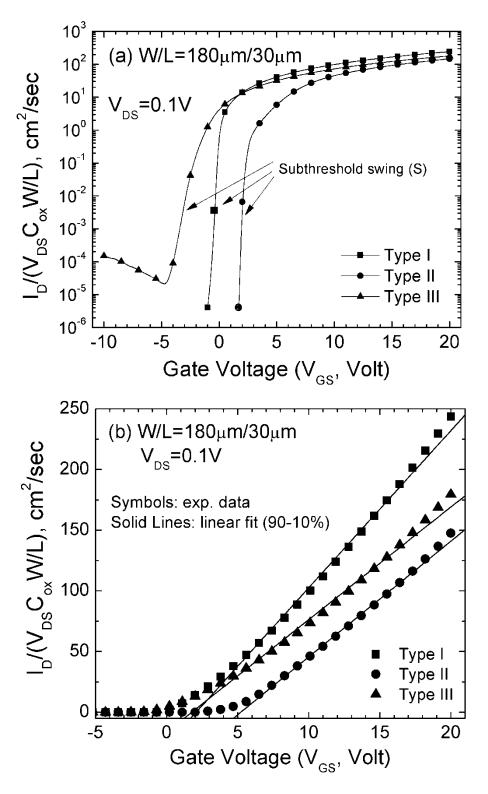

| Figure 2.7 Transfer characteristics of common gate, PLD a-IGZO TFT in (a) linear plot and (b) semi-log plots                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

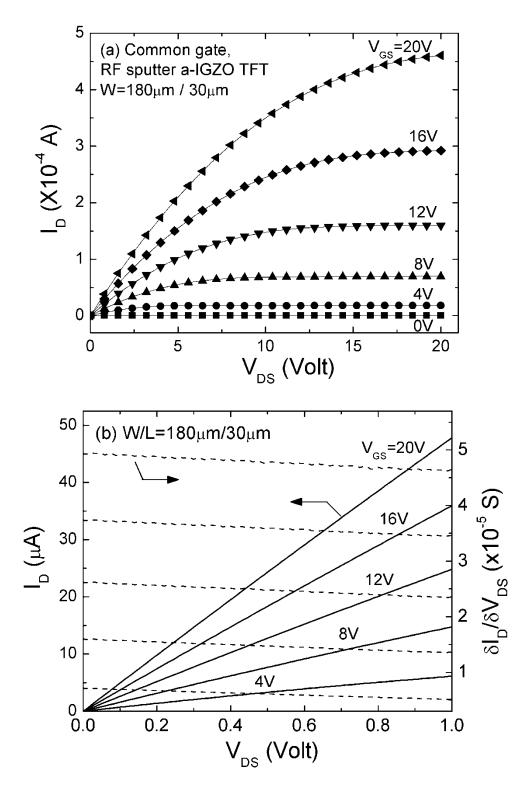

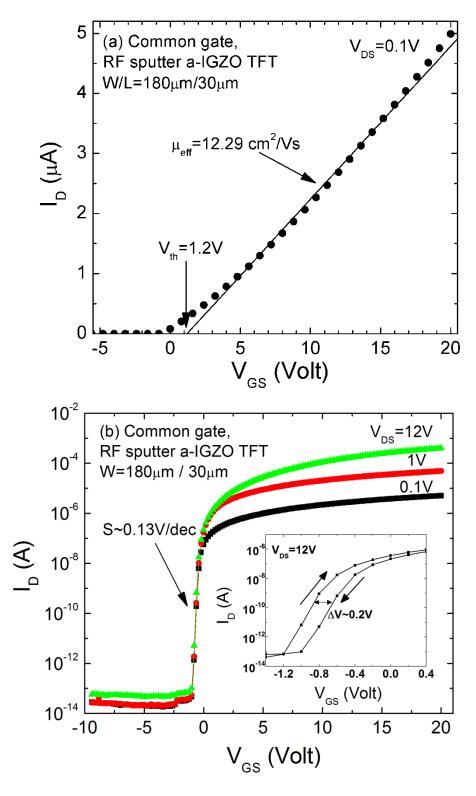

| <b>Figure 2.8</b> (a) Output characteristics of the common gate, RF sputter a-IGZO TFT. (b) A zoom-in plot of the output characteristics (solid curves) near the origin ( $V_{DS}$ =0~1V); derivatives of $I_D$ vs. $V_{DS}$ characteristics ( $\delta I_D / \delta V_{DS}$ , dash curves) are also shown. |

| <b>Figure 2.9</b> Transfer characteristics of common gate, RF sputter a-IGZO TFT in (a) linear plot and (b) semi-log plots                                                                                                                                                                                 |

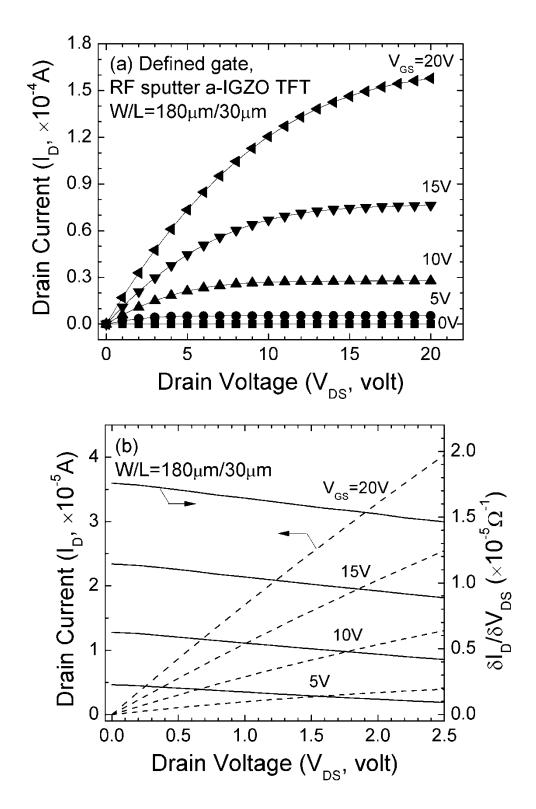

| Figure 2.10 (a) Output characteristics of the defined gate, RF sputter a-IGZO TFT. (b) A zoom-in plot of the output characteristics (solid curves) near the origin ( $V_{DS}$ =0~2.5V); derivatives of $I_D$ vs. $V_{DS}$ characteristics ( $\delta I_D / \delta V_{DS}$ , dash curves) are also shown.    |

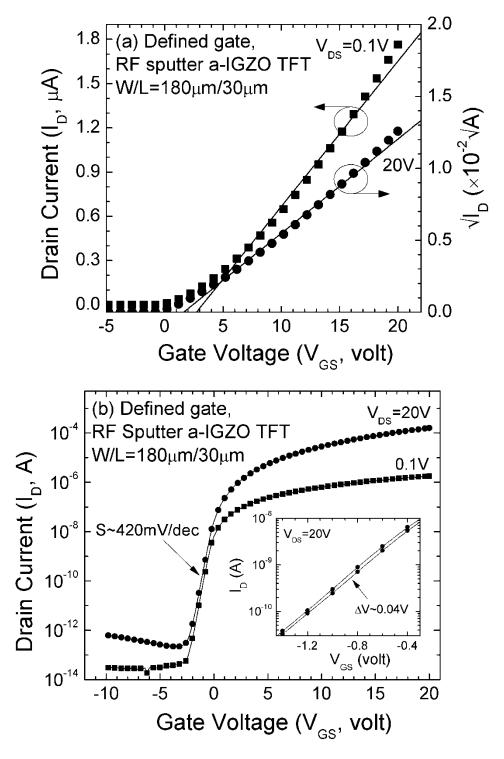

| <b>Figure 2.11</b> Transfer curves of defined gate, RF sputter a-IGZO TFT in (a) linear and (b) semi-log scales                                                                                                                                                                                            |

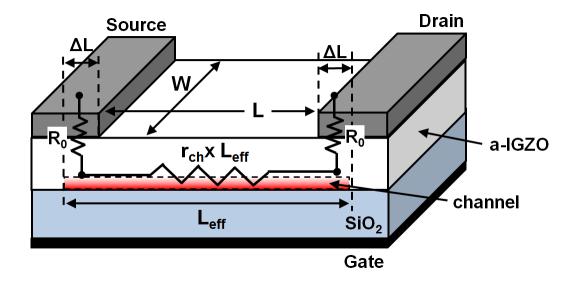

| <b>Figure 3.1</b> Physical origin of the resistance components in equation (3-1)                                                                                                                                                                                                                           |

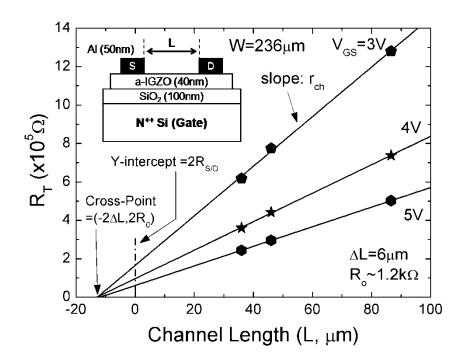

| <b>Figure 3.2</b> Illustration of the transmission line method (TLM)                                                                                                                                                                                                                                       |

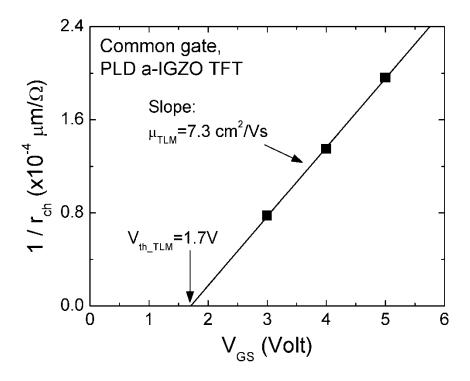

| Figure 3.3 The evolution of $1/r_{ch}$ with TFT gate voltage ( $V_{GS}$ )                                                                                                                                                                                                                                  |

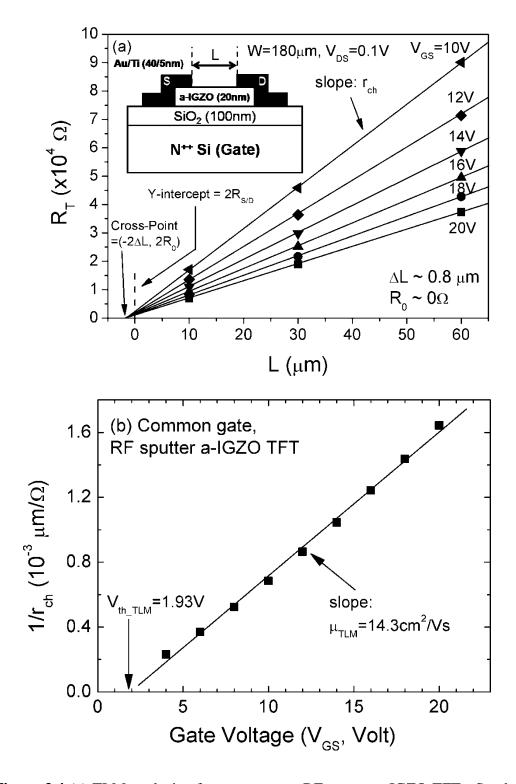

| Figure 3.4 (a) TLM analysis of common gate, RF sputter a-IGZO TFTs. Symbol: experimental data, solid line: linear fit to the (3-4) or (3-5). (b) The evolution of $1/r_{ch}$ with $V_{GS}$ .                                                                                                               |

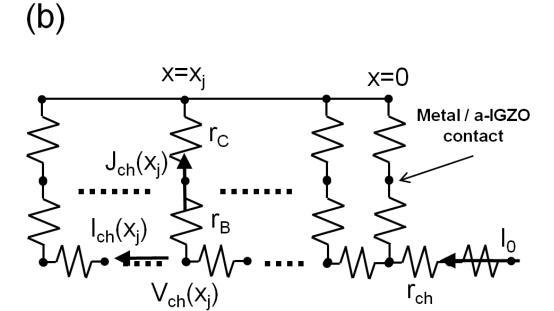

| Figure 3.5 (a) Graphical representation of the transfer length $(L_T)$ (adapted from [59]). (b) Equivalent circuit near the a-IGZO TFT source electrode (adapted from [54]). A distributed resistance network is chosen to model the current distribution under source electrode                           |

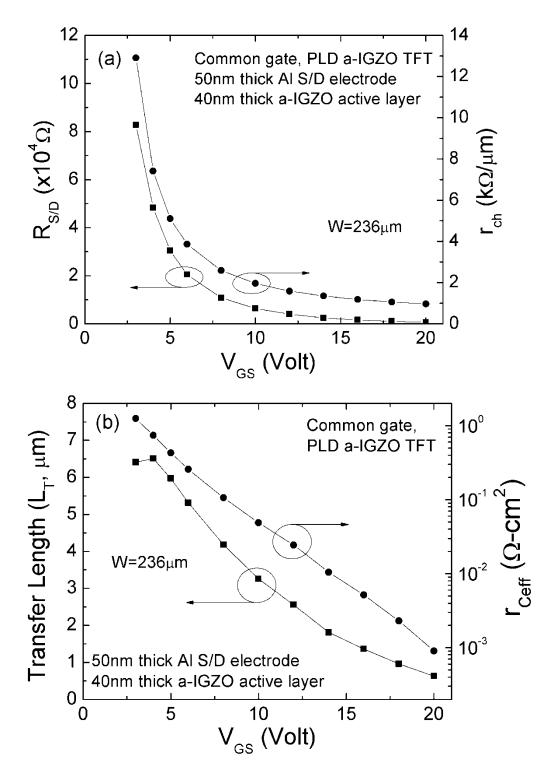

| $ \begin{tabular}{ll} \textbf{Figure 3.6 (a) Common gate, PLD a-IGZO TFT S/D series resistance $(R_{S/D})$ and channel resistance per unit length $(r_{ch})$ as a function of $V_{GS}$. (b) Calculated transfer length $(L_T)$ and effective contact resistance $(r_{Ceff})$ as a function of $V_{GS}$$    |

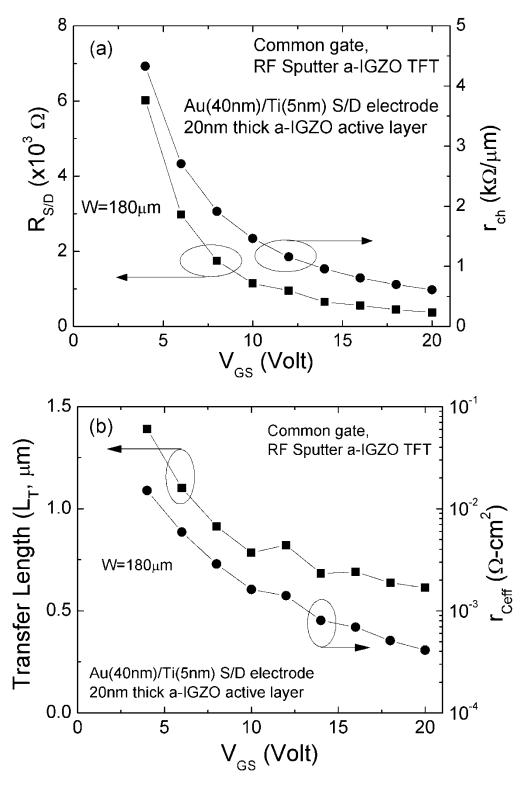

| $ \begin{tabular}{ll} \textbf{Figure 3.7} (a) Common gate, RF sputter a-IGZO TFT $R_{S/D}$ and $r_{ch}$ as a function of $V_{GS}$. (b) \\ Calculated $L_T$ and $r_{Ceff}$ as a function of $V_{GS}$$                                                                                                       |

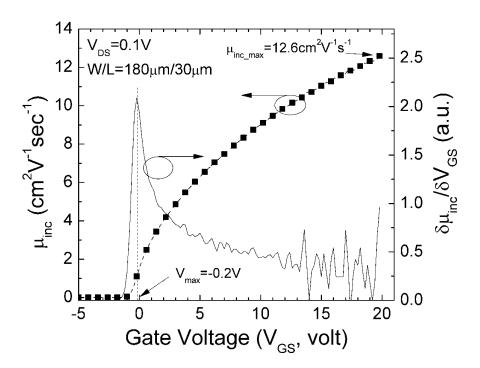

| <b>Figure 3.8</b> Symbol( $\blacksquare$ ): Incremental field-effect mobility ( $\mu_{inc}$ ) of the defined gate, RF sputter a-IGZO TFT extracted by using (3-19). The differentiation of $\mu_{inc}$ ( $\delta\mu_{inc}/\delta V_{GS}$ , solid line) is also shown.                                      |

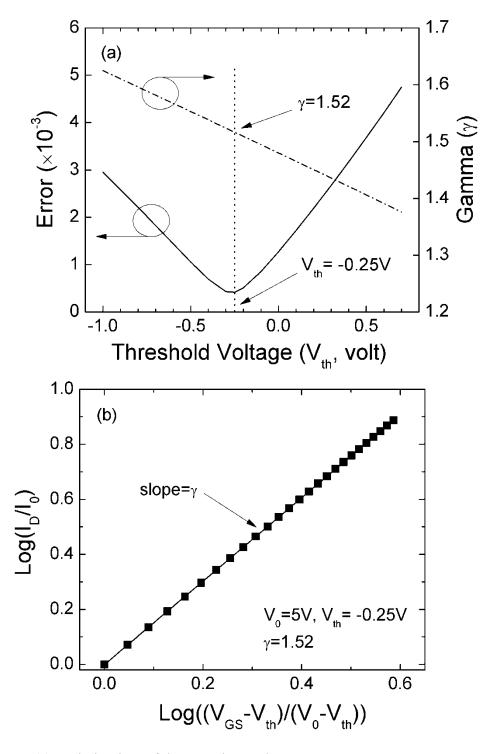

| Figure 3.9 (a) Variation in $\gamma$ of the experimental I-V data (collected from defined gate, RF                                                                                                                                                                                                         |

| sputter a-IGZO TFT) in above threshold region as a function of $V_{th}$ . A reference gate voltage $V_0$ of 5V is used for parameter extraction. Also shown is the RMS error of the least-square fit to the log of drain current ratio (Log( $I_D/I_0$ )). (b) Example of the actual linear fitting plot to (3-27) at $V_{th}$ with minimum error (-0.25V).   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

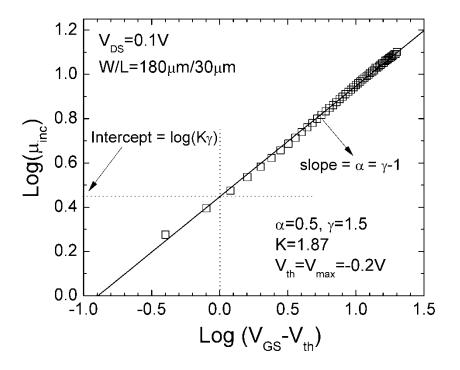

| Figure 3.10 The log-log plot of the incremental field-effect mobility ( $\mu_{inc}$ ) as a function of the effective gate voltage ( $V_{GS}$ - $V_{th}$ ). Data are collected from defined gate, RF sputter a-IGZO TFT.                                                                                                                                       |

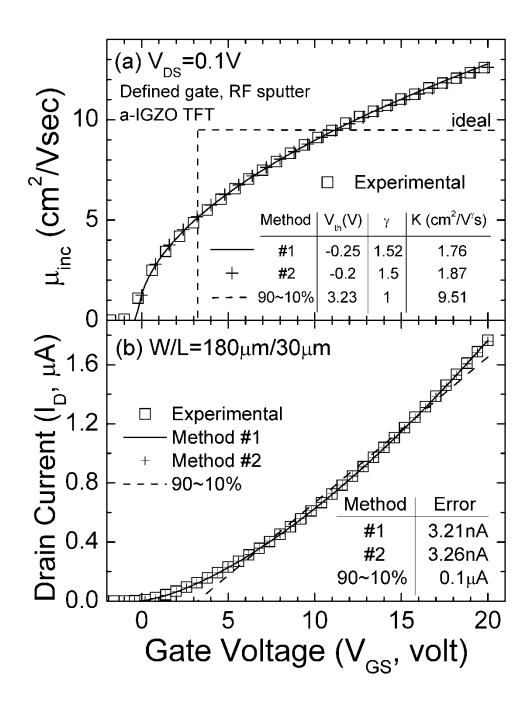

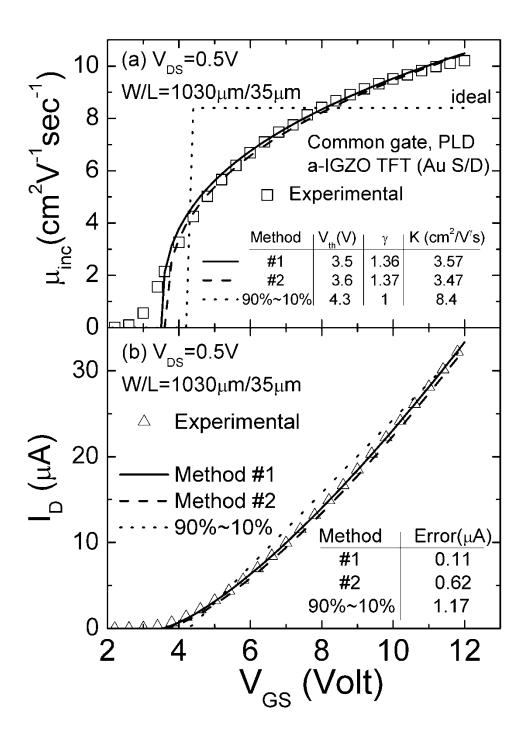

| Figure 3.11 The calculation of (a) $\mu_{inc}$ and (b) $I_D$ based on different models/extraction methods used in this study.                                                                                                                                                                                                                                 |

| Figure 3.12 (a) $\mu_{inc}$ and (b) $I_D$ of common gate, PLD a-IGZO TFT with gold (Au) S/D electrodes [47]. Both experimental and simulated data are shown                                                                                                                                                                                                   |

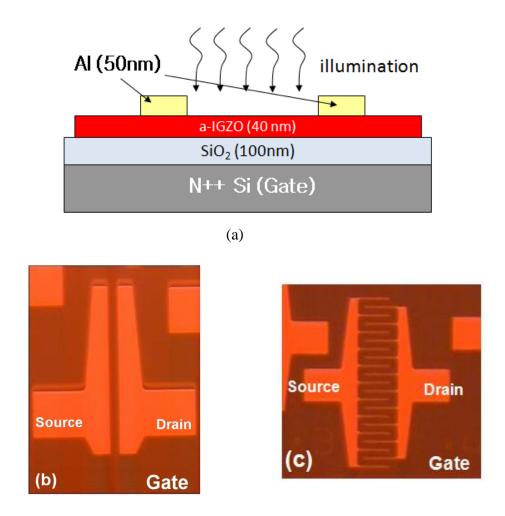

| <b>Figure 4.1</b> (a) Cross-sectional view of the common gate, PLD a-IGZO TFT device used in photo field effect study. (b) and (c) are die photos of regular and finger type (interdigitated) TFTs, respectively.                                                                                                                                             |

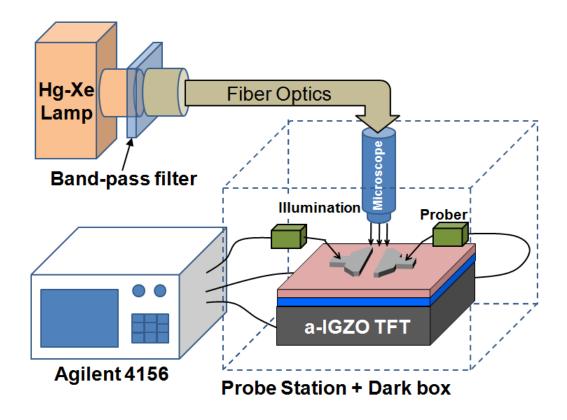

| <b>Figure 4.2</b> The schematic of experimental setup used in photofield-effect study 61                                                                                                                                                                                                                                                                      |

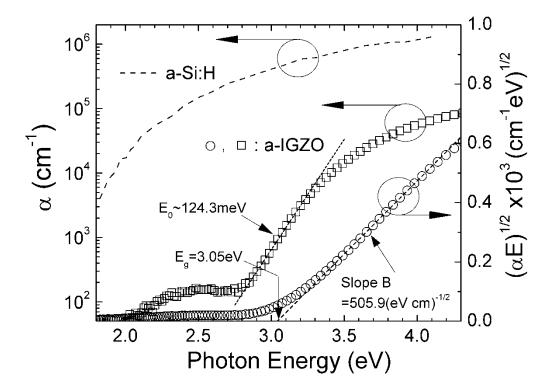

| <b>Figure 4.3</b> Optical absorption spectrum of PLD a-IGZO (○, □) [74] and a-Si:H (dash line) [72] thin film.                                                                                                                                                                                                                                                |

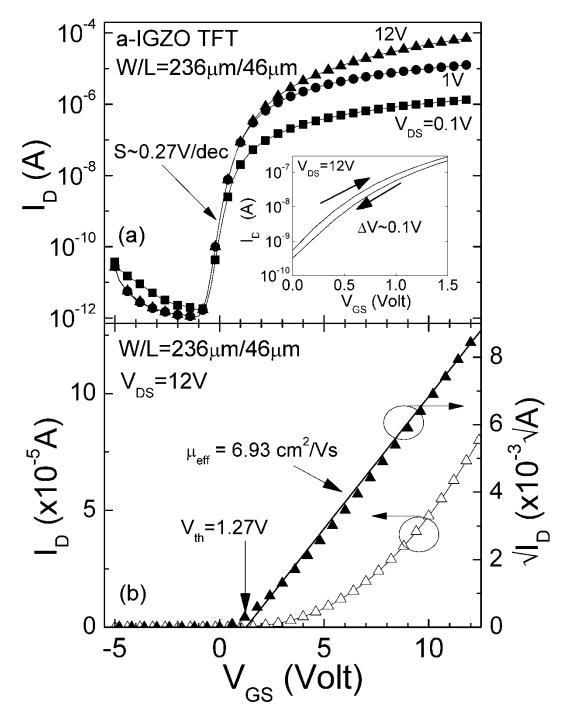

| <b>Figure 4.4</b> Transfer characteristic of PLD a-IGZO TFT in (a) semi-log plot and (b) linear plot. (Inset, a) The TFT hysteresis measured at $V_{DS}$ =12V; $\Delta V$ is the shift (hysteresis) in sub-threshold properties.                                                                                                                              |

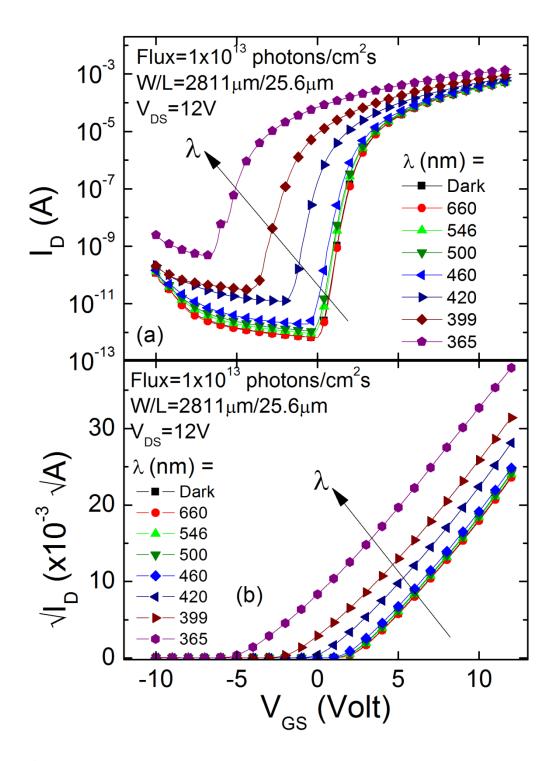

| <b>Figure 4.5</b> (Color) PLD a-IGZO TFT transfer characteristics for constant photon flux with the varying illumination wavelengths. ((a): semi-log plot, (b): linear plot) 67                                                                                                                                                                               |

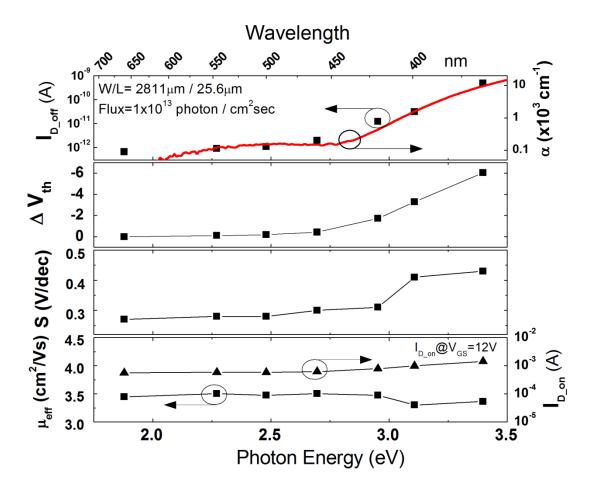

| Figure 4.6 (Color) Dependence of PLD a-IGZO TFT minimum off-state drain current ( $I_{D\_off}$ ), on-state drain current ( $I_{D\_on}$ ), threshold voltage shift ( $\Delta V_{th}$ ), sub-threshold swing (S), and field-effect mobility ( $\mu_{eff}$ ) on incident photon energy (or equivalent wavelength). Red curve: absorption spectrum of the a-IGZO. |

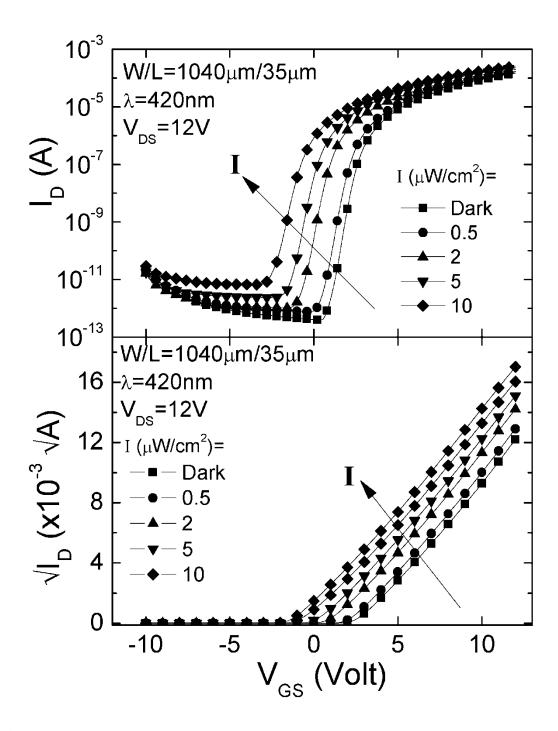

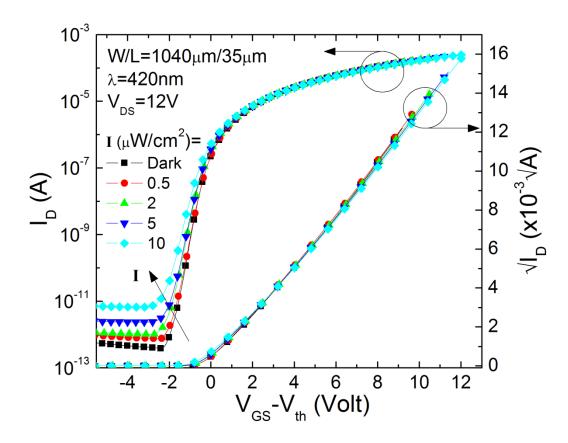

| <b>Figure 4.7</b> PLD a-IGZO TFT transfer characteristics for dark and different irradiance levels (I) in (a): semi-log plot and (b) linear plot. UV illumination wavelength (λ) 420nm.                                                                                                                                                                       |

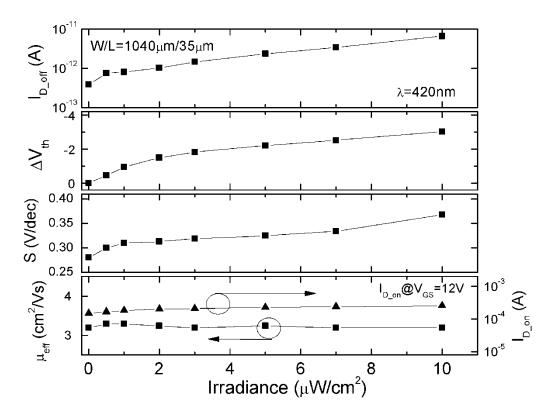

| Figure 4.8 Dependence of PLD a-IGZO TFT off state drain current ( $I_{D\_off}$ ), on-state drain current ( $I_{D\_on}$ ), threshold voltage shift ( $\Delta V_{th}$ ), subthreshold swing (S), and field-effect mobility ( $\mu_{eff}$ ) on irradiance level. UV illumination wavelength ( $\lambda$ ):                                                       |

| 420nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 4.9</b> (Color) Threshold voltage normalized (I <sub>D</sub> is plotted as a function of effective gate voltage, V <sub>GS</sub> -V <sub>th</sub> ) PLD a-IGZO TFT transfer properties for dark and different irradiance levels (I).                                                                                                                                                                                                                                                                |

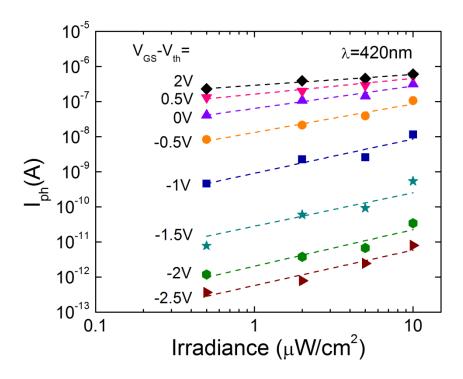

| <b>Figure 4.10</b> (Color) Dependence of photocurrent (I <sub>ph</sub> ) on irradiance at various V <sub>GS</sub> -V <sub>th</sub> voltages.                                                                                                                                                                                                                                                                                                                                                                  |

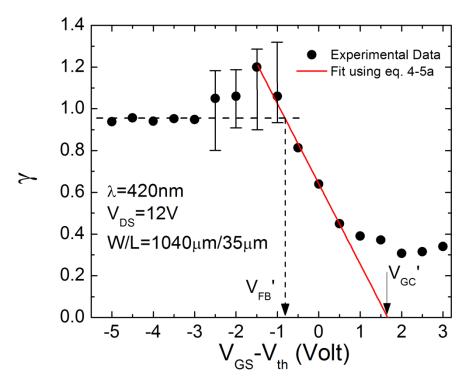

| <b>Figure 4.11</b> (Color) Gamma factor $(\gamma)$ of PLD a-IGZO TFT versus $V_{GS}$ - $V_{th}$ at a wavelength of 420nm.                                                                                                                                                                                                                                                                                                                                                                                     |

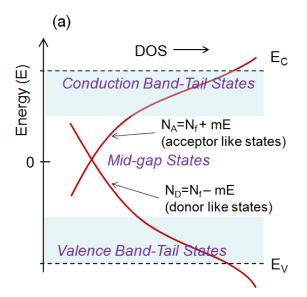

| <b>Figure 4.12</b> (a) Schematic of the simplified mid-gap DOS model used in photofield-effect analysis. (b) Extracted DOS parameters for a-Si:H [82] and a-IGZO (this study).                                                                                                                                                                                                                                                                                                                                |

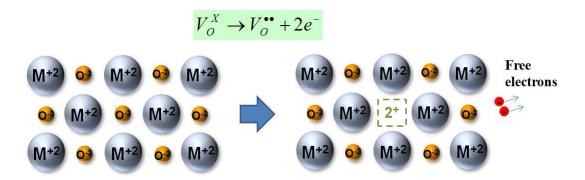

| Figure 5.1 Schematic representation of the oxygen vacancy                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

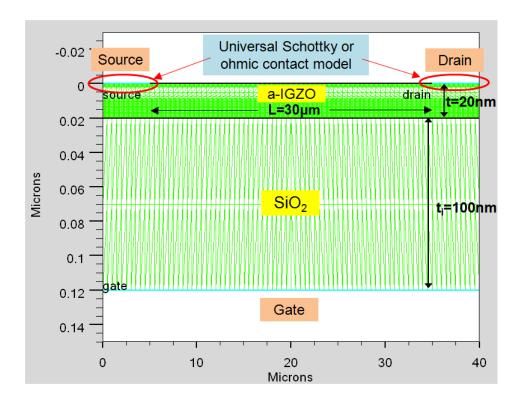

| <b>Figure 5.2</b> (Color) The cross section of inverted-staggered a-IGZO TFT structure used in the numerical simulation.                                                                                                                                                                                                                                                                                                                                                                                      |

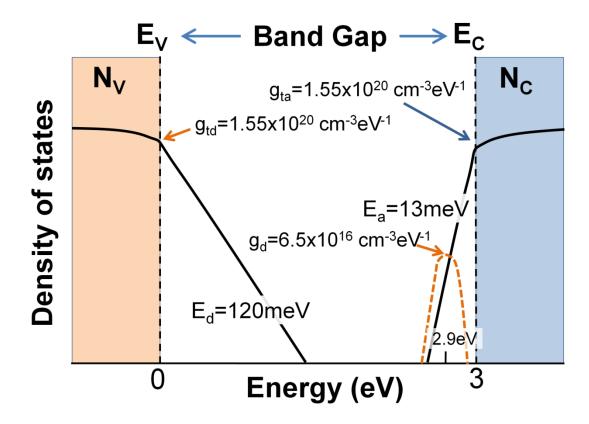

| Figure 5.3 (Color) Proposed DOS model for a-IGZO.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

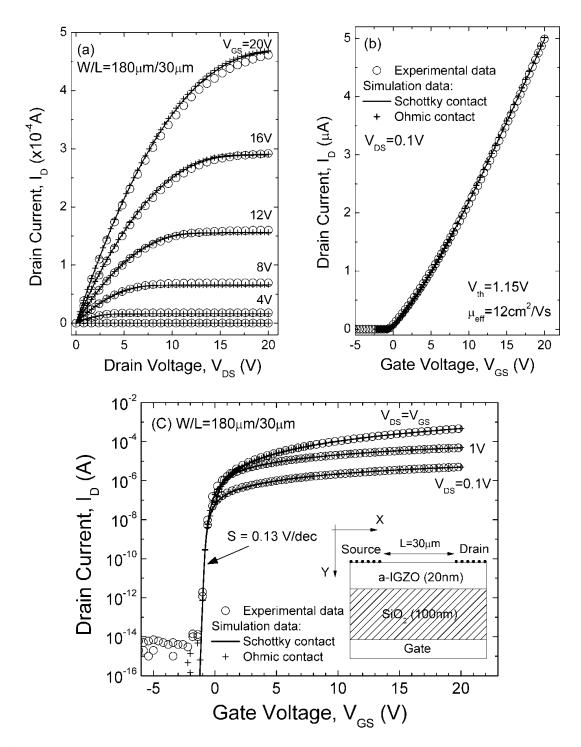

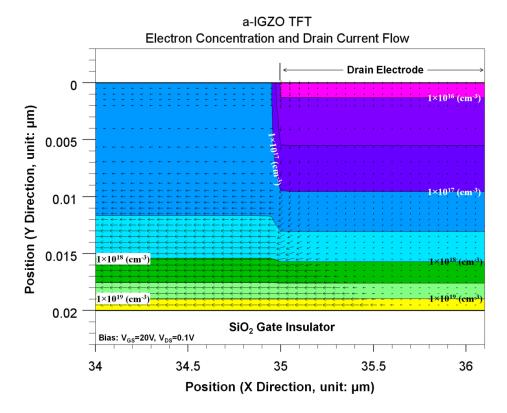

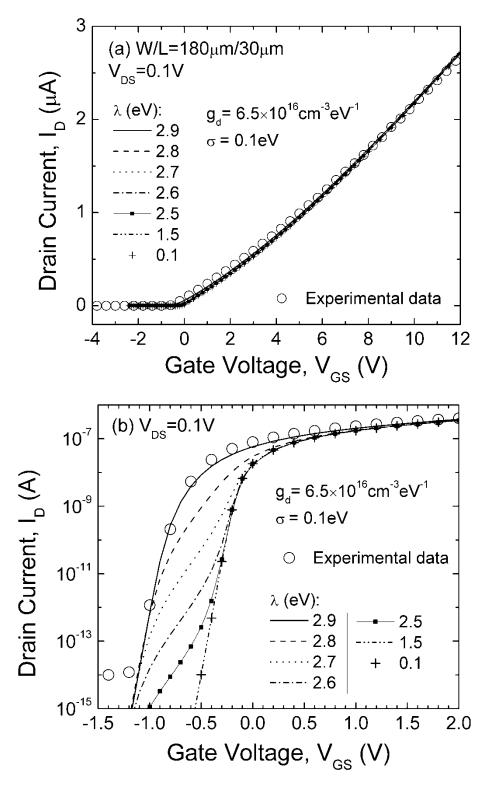

| <b>Figure 5.4</b> a-IGZO TFT: (a) output and [(b) and (c)] transfer characteristics (W/L=180/30μm). Both experimental (○) and simulation data (solid line: Schottky contact; +: Ohmic contact) are shown.                                                                                                                                                                                                                                                                                                     |

| Figure 5.5 (Color) A zoom-in view of the simulated TFT structure near the drain electrode.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

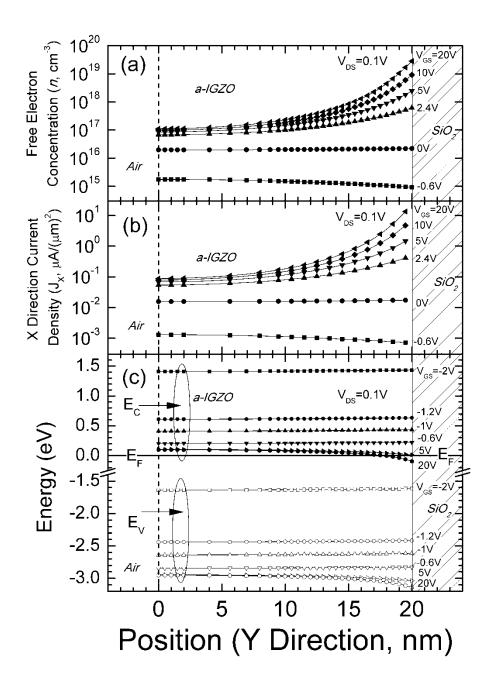

| <b>Figure 5.6</b> Simulated distribution of (a) free electron density (n) and (b) <i>X</i> -direction current density (J <sub>x</sub> ) at the center of the a-IGZO TFT structure. Gate voltage was changed from -0.6 up to 20 V. The film thickness of a-IGZO is 20nm. Position <i>Y</i> =0 represents the back channel surface while <i>Y</i> =20 nm represents the interface between a-IGZO and SiO <sub>2</sub> gate insulator. (c) Simulated energy band bending diagram at the center of TFT structure. |

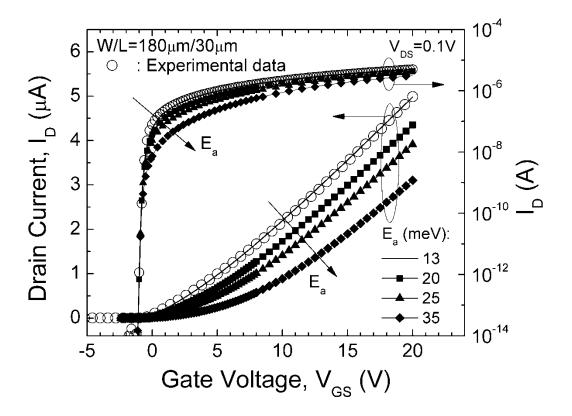

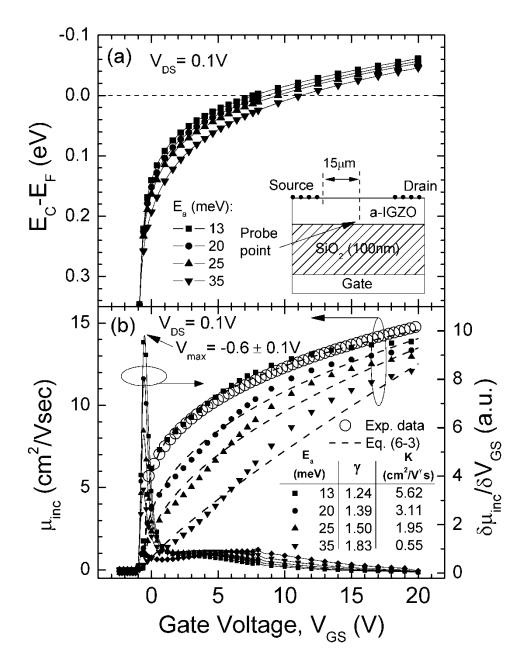

| <b>Figure 6.1</b> Simulated a-IGZO TFT linear region transfer curves for both linear and semilogarithm scales for various E <sub>a</sub> values are shown                                                                                                                                                                                                                                                                                                                                                     |

| <b>Figure 6.2</b> (a) Simulated a-IGZO Fermi-level position vs. gate voltage ( $V_{GS}$ ). The Fermi-level position is represented as $E_C - E_F$ , where $E_C$ and $E_F$ are energies for conduction band-edge and Fermi level, respectively. The inset indicates the probe point for this data and it is located at the center of the TFT, near (0.5nm away from) the a-IGZO/SiO <sub>2</sub> interface. The slight off-set is to avoid the                                                                 |

| calculation discontinuity which might occur at the interface. (b) The $\mu_{inc}$ as $\delta\mu_{inc}/\delta V_{GS}$ extracted from simulated a-IGZO TFT transfer characteristics for various $E_a$ values.                                                  | or |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

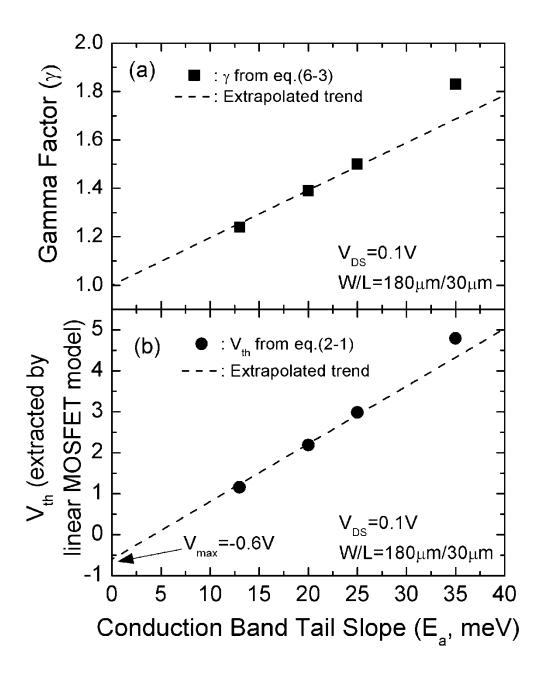

| Figure 6.3 Simulated evolution of (a) gamma factor $(\gamma)$ and (b) threshold voltage $(V_{th})$ as function of conduction band-tail slope $(E_a)$ .                                                                                                       |    |

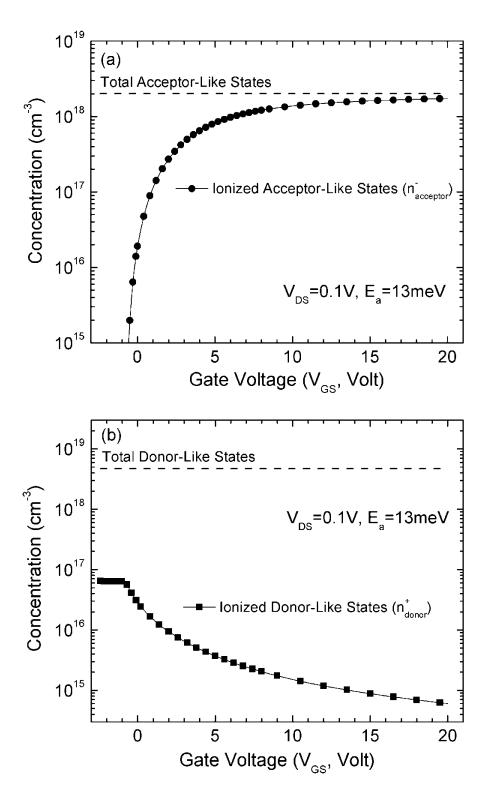

| <b>Figure 6.4</b> Simulated evolution of ionized (a) acceptor-like and (b) donor-like states as function of $V_{GS}$ . The simulation is done with $E_a$ =13meV                                                                                              |    |

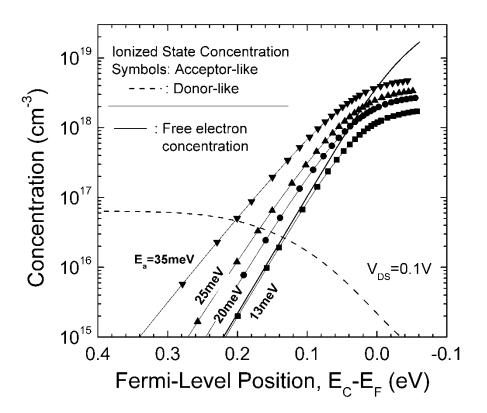

| <b>Figure 6.5</b> Simulated free electron concentration $(n)$ , ionized acceptor-like states $(n_{acceptor}^-)$ and ionized donor-like states $(n_{donor}^+)$ as a function of $E_C$ - $E_F$                                                                 |    |

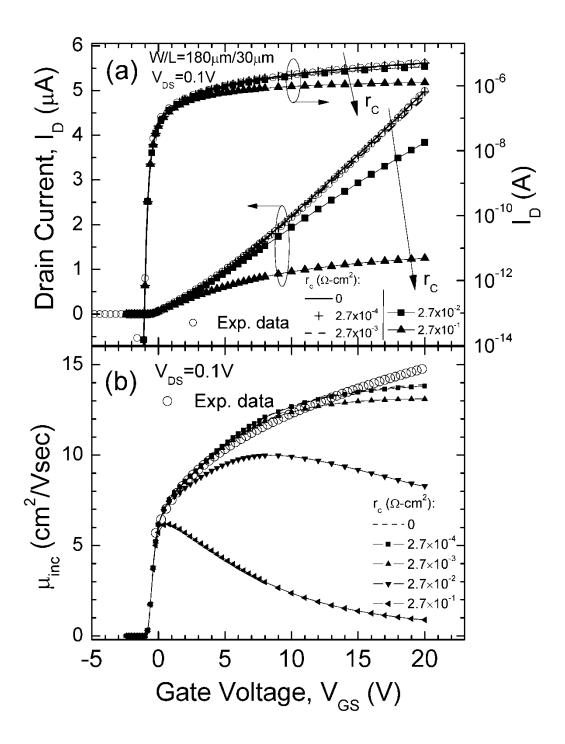

| Figure 6.6 Simulated a-IGZO TFT (a) linear region transfer curves and (b) $\mu_{inc}$ extract from TFT transfer characteristics for various $r_c$ values.                                                                                                    |    |

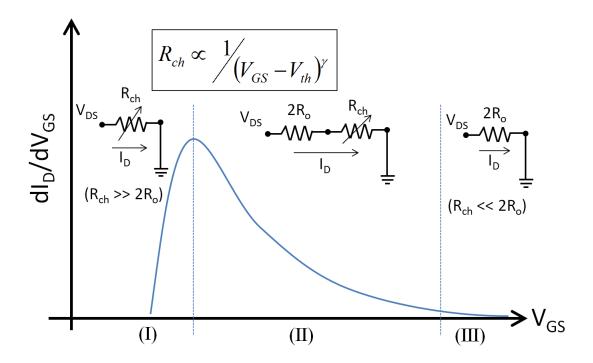

| <b>Figure 6.7</b> Illustration of the S/D contact resistance effect                                                                                                                                                                                          | 06 |

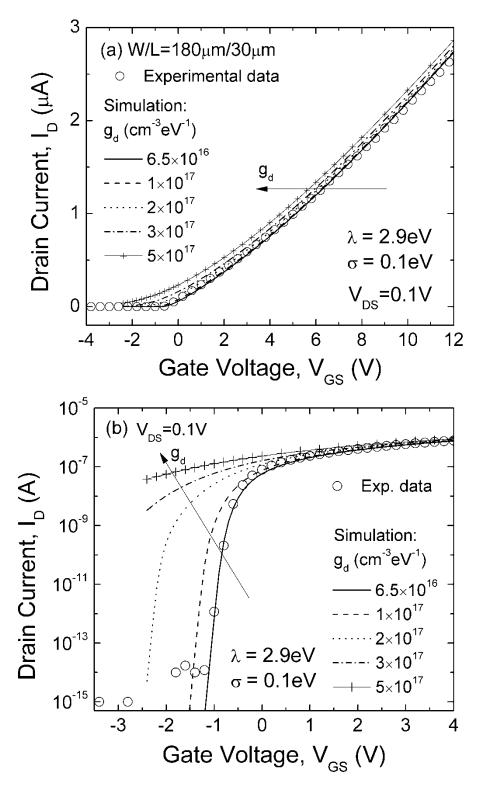

| <b>Figure 6.8</b> a-IGZO TFT simulated linear region $I_D$ - $V_{GS}$ curves in (a) linear scale and (semi-logarithm scale for various OV states peak value ( $g_d$ )                                                                                        |    |

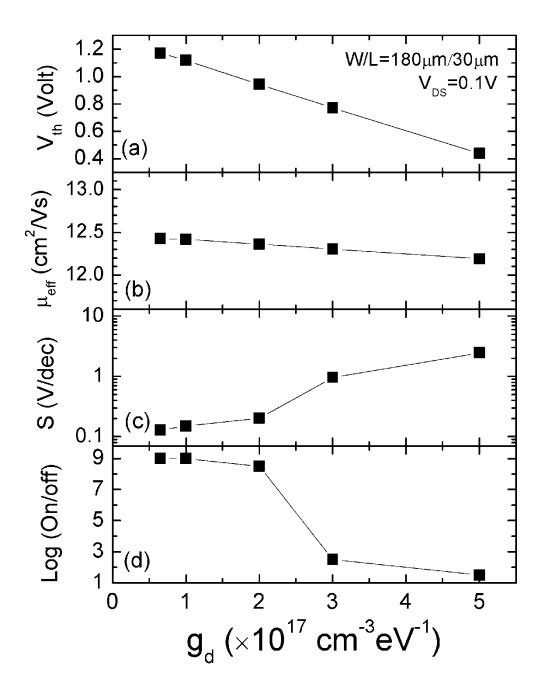

| Figure 6.9 Simulated TFT (a) $V_{th}$ , (b) $\mu_{eff}$ , (c) S and (d) on/off ratio as a function of $g$                                                                                                                                                    |    |

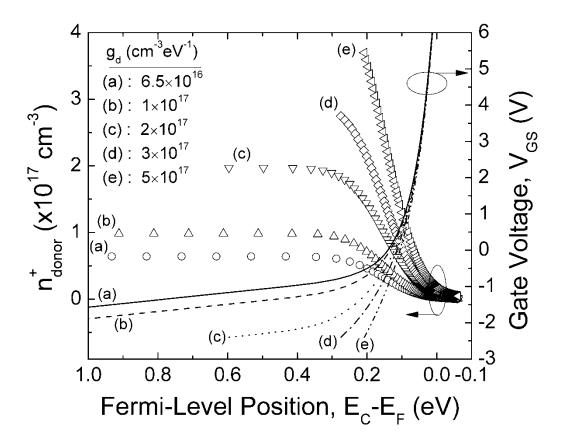

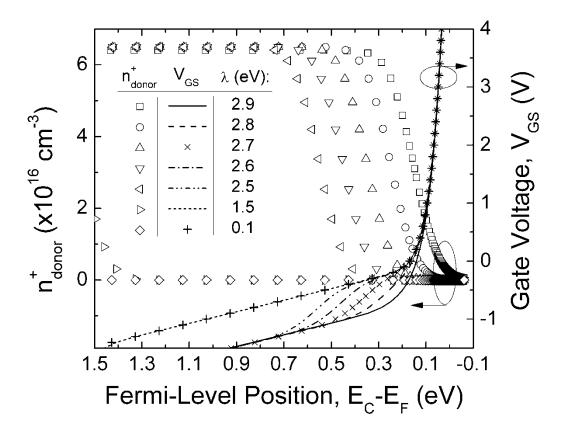

| <b>Figure 6.10</b> Simulated ionized donor-like states concentration $(n_{donor}^+)$ and gate voltage $(V_{GS})$ as a function of Fermi-level position $(E_C - E_V)$ for various OV states per value $(g_d)$ .                                               | ak |

| <b>Figure 6.11</b> a-IGZO TFT simulated linear region $I_D$ - $V_{GS}$ curves in (a) linear scale and (semi-logarithm scale for various OV states mean energy ( $\lambda$ )                                                                                  |    |

| <b>Figure 6.12</b> Simulated ionized donor-like states concentration $(n_{donor}^+)$ and gate voltage $(V_{GS})$ as a function of Fermi-level position $(E_C - E_V)$ for various OV states meaning $(\lambda)$ .                                             | an |

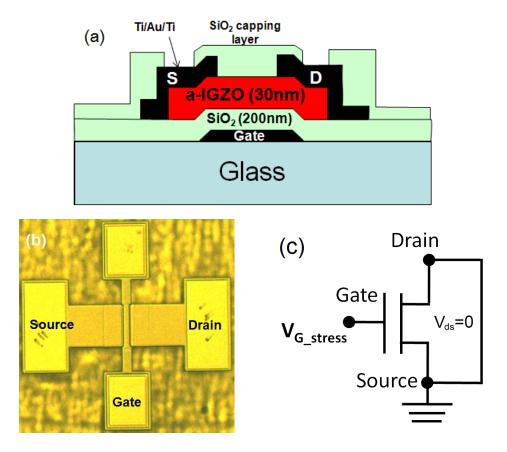

| <b>Figure 7.1</b> (a) Cross-sectional and (b) top view of the RF sputter a-IGZO TFT device use in this study. (c) The schematic of the circuit setup used for steady state BT experiments.                                                                   | ΓS |

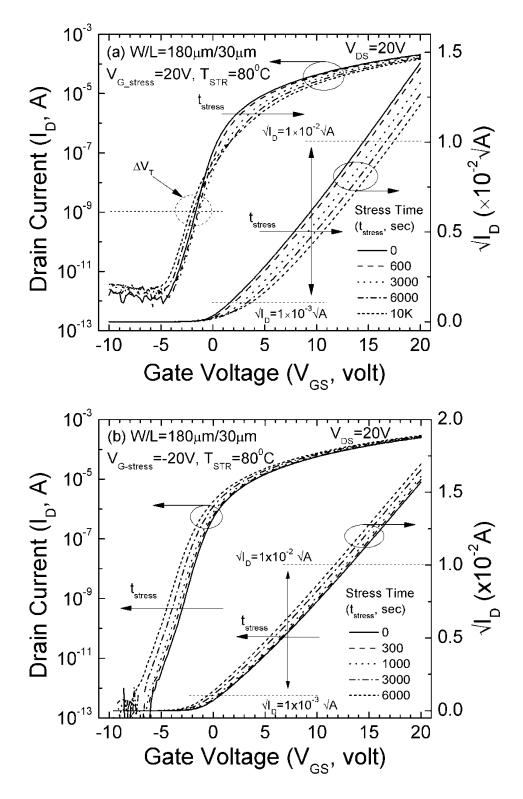

| <b>Figure 7.2</b> The evolution of RF sputter a-IGZO TFT transfer characteristics for (a) positive BTS ( $V_{G\_stress}$ = 20V) and (b) negative BTS ( $V_{G\_stress}$ = -20V). For both experiments, the stress temperature, $T_{STR}$ , is $80^{\circ}$ C. | th |

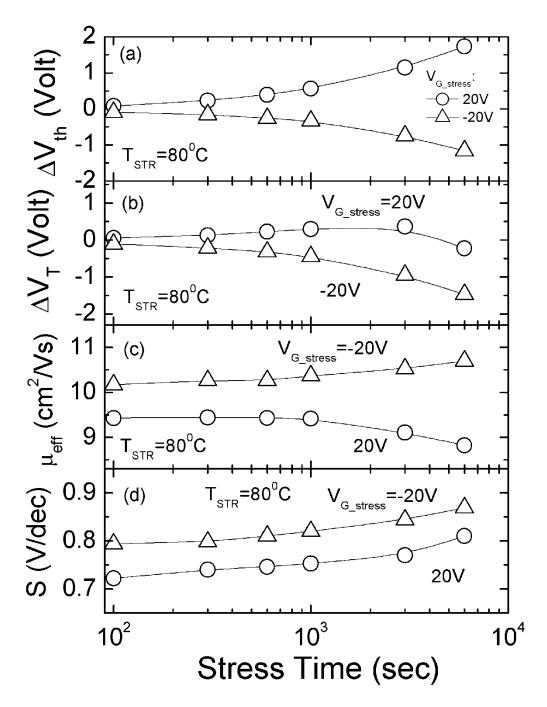

| <b>Figure 7.3</b> (a) $\Delta V_{th}$ , (b) $\Delta V_{T}$ , (c) $\mu_{eff}$ and (d) S as a function of stress time ( $t_{stress}$ ) for bo positive ( $V_{G\_stress}$ =20V) and negative (-20V) BTS                                                         |    |

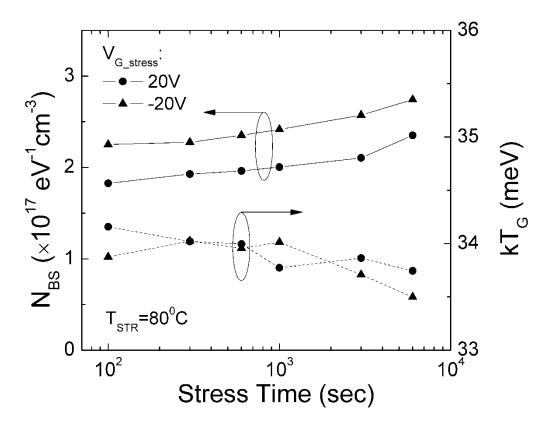

| Figure 7.4 Density of bulk-states ( $N_{BS}$ ) and characteristic temperature of conduction band tail states ( $T_G$ ) as a function of stress time ( $t_{stress}$ ) for both positive ( $V_{G\_stress}$ =20V) and negative (-20V) BTS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

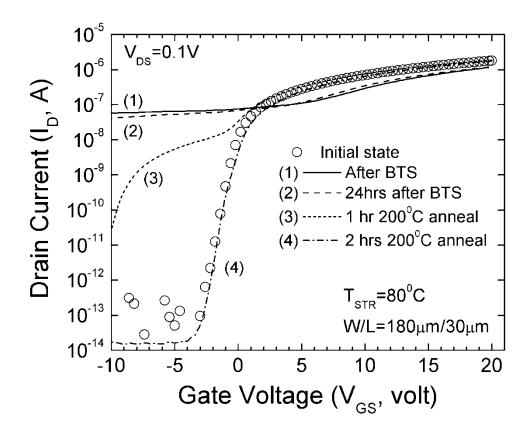

| <b>Figure 7.5</b> Recovery of the a-IGZO TFT electrical instability after thermal annealing. 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

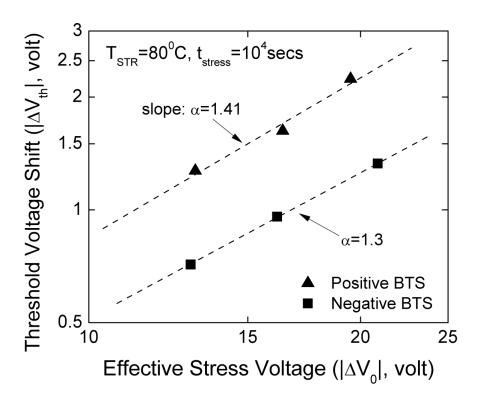

| Figure 7.6 $\Delta V_{th}$ as a function of effective stress voltage ( $\Delta V_0$ ) for positive (symbol: $\blacktriangle$ ) and negative ( $\blacksquare$ ) BTS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

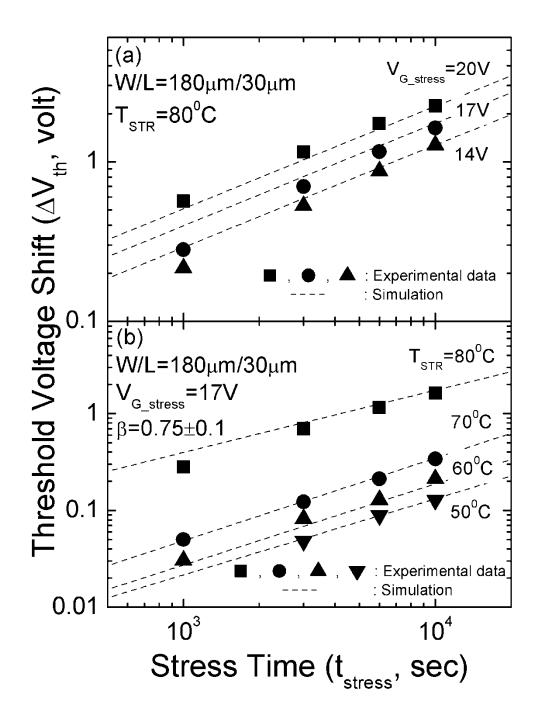

| <b>Figure 7.7</b> $\Delta V_{th}$ vs. stress time (t <sub>stress</sub> ) for various (a) positive stress voltages ( $V_{G\_stress}$ =20 $V_{th}$ ) and 14 $V_{th}$ , $V_{th}$ and 15 $V_{th}$ and 16 $V_{th}$ and |

| <b>Figure 7.8</b> $\Delta V_{th}$ vs. stress time (t <sub>stress</sub> ) for various (a) negative stress voltages ( $V_{G\_stress} = -20V$ , -15V and -12V, $T_{STR} = 80^{0}C$ ) and (b) temperature ( $T_{STR} = 50^{0}C \sim 80^{0}C$ , $V_{G\_stress} = -20V$ ). Symbols represent the experimental data while dashed lines are the simulation fits to stretched-exponential model (7-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

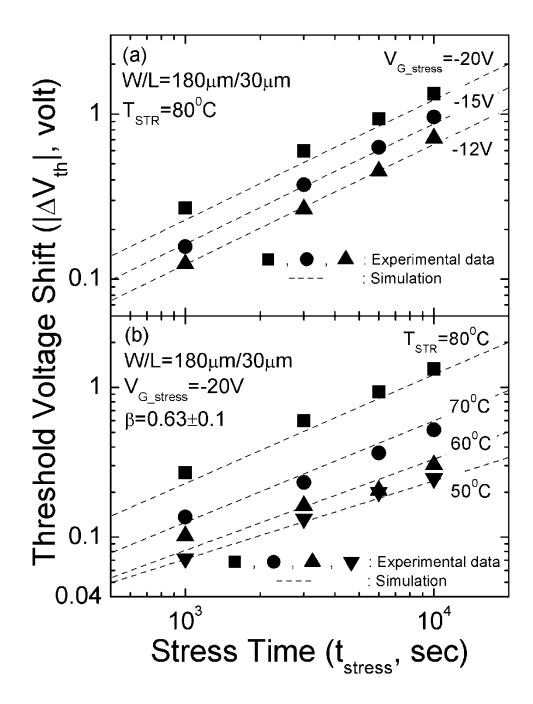

| Figure 7.9 The characteristic trapping time $\tau$ for positive (symbol: $\blacktriangle$ ) and negative ( $\blacksquare$ ) BTS as a function of $1/T_{STR}$ . ( $T_{STR}$ range: $50^{0}$ C $\sim 80^{0}$ C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

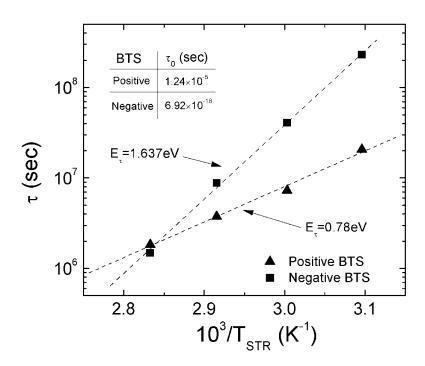

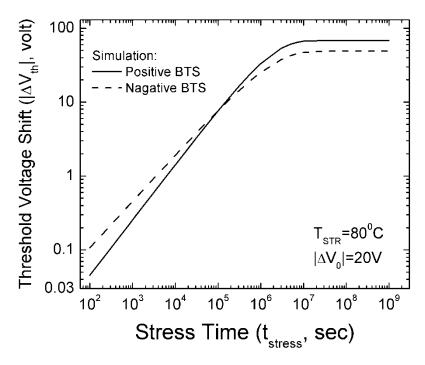

| Figure 7.10 Simulated $\Delta V_{th}$ vs. stress time ( $t_{stress}$ ) for (solid line) positive and (dash line) negative BTS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

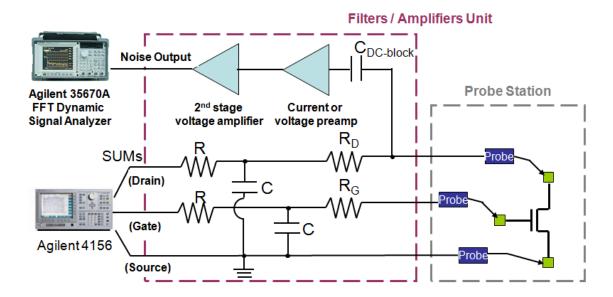

| <b>Figure 8.1</b> (Color) Circuit diagram of the experimental setup used for measuring the TFT drain current noise. The filter / amplifier unit is also known as 9812B noise analyzer. (Adapted from [153])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <b>Figure 8.2</b> (Color) Photo of the noise measurement system. Device is placed inside the light-tight probe station, which also serves as a Faraday cage for electrical shielding.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

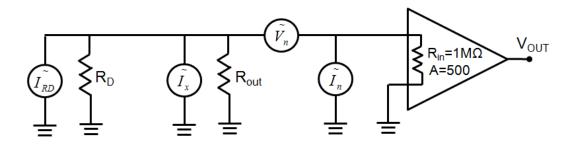

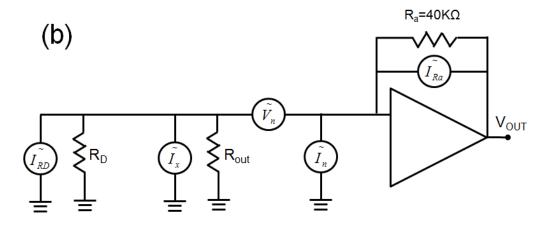

| <b>Figure 8.3</b> The equivalent circuits for noise measurements with (a) voltage and (b) current amplifiers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

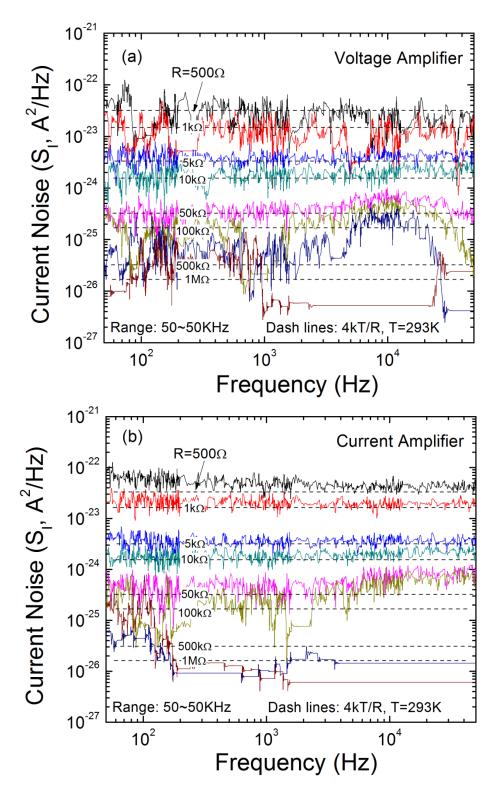

| <b>Figure 8.4</b> (Color) Thermal noise spectrums measured from high quality metal film resistors. Both (a) voltage and (b) current amplifier are used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

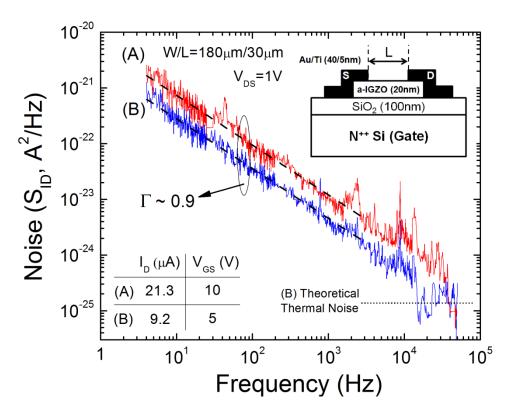

| <b>Figure 8.5</b> (Color) Example of a-IGZO TFT drain current noise spectrum ( $S_{\rm ID}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

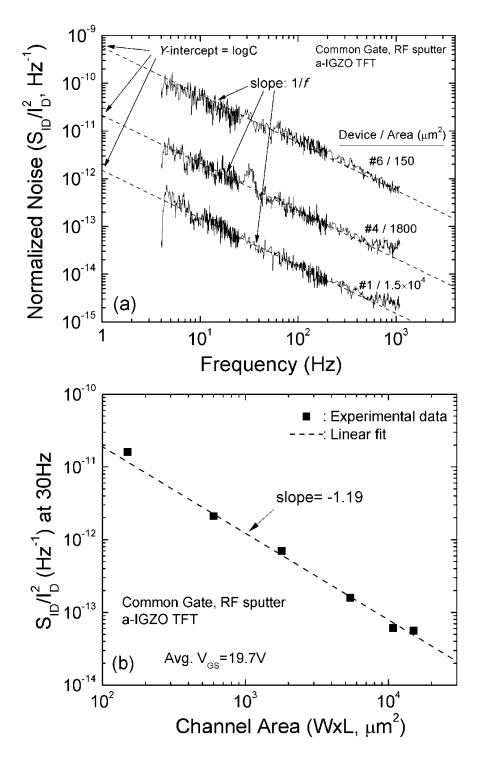

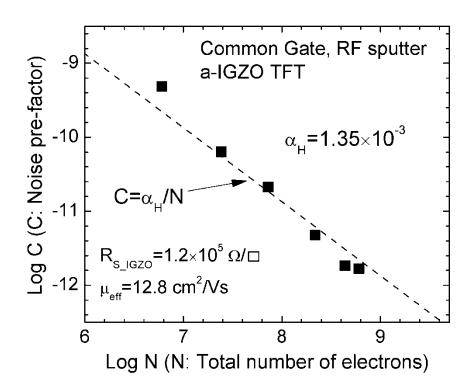

| <b>Figure 8.6</b> (a) Examples of the normalized noise spectrums collected from three TFTs with different channel areas (150, 1800 and $1.5\times10^4~\mu\text{m}^2$ ). Dash lines are the best linear fits to equation (8-26). (b) Normalized a-IGZO TFT drain current noise $(S_{\text{ID}}/I_{\text{D}}^{2})$ versus channel area.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>Figure 8.7</b> Illustration of $\alpha_H$ extraction based on area-dependent noise data                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

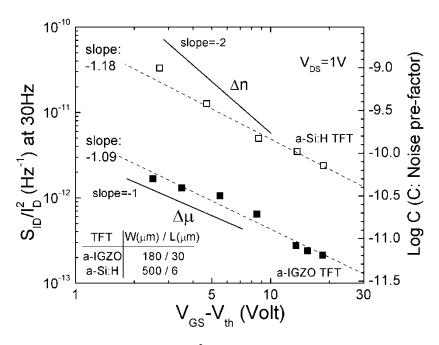

| <b>Figure 8.8</b> Linear region ( $V_{DS}$ =1V) $S_{ID}/I_D^2$ (at 30Hz) and noise pre-factor C as a function of $V_{GS}$ - $V_{th}$ .                    |

| <b>Figure 8.9</b> Saturation region ( $V_{DS}$ =12V) $S_{ID}/I_D^2$ (at 30Hz) and pre-factor C as a function of $V_{GS}$ - $V_{th}$ .                     |

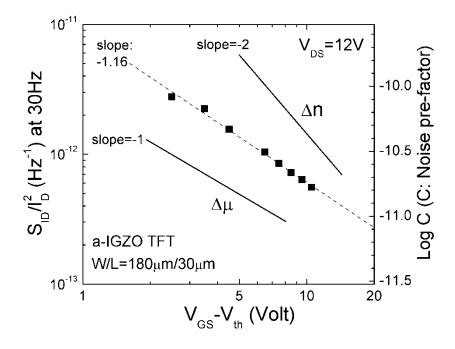

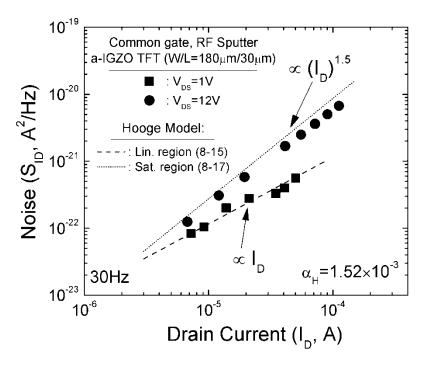

| Figure 8.10 Hooge's parameters ( $\alpha_H$ ) versus $V_{GS}$ - $V_{th}$ .                                                                                |

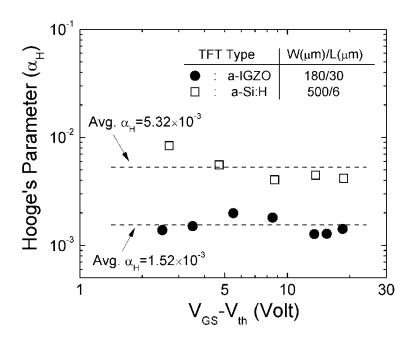

| <b>Figure 8.11</b> Drain current noise power density (S <sub>ID</sub> , sampling at 30Hz) of a-IGZO TFT as a function of drain current (I <sub>D</sub> ). |

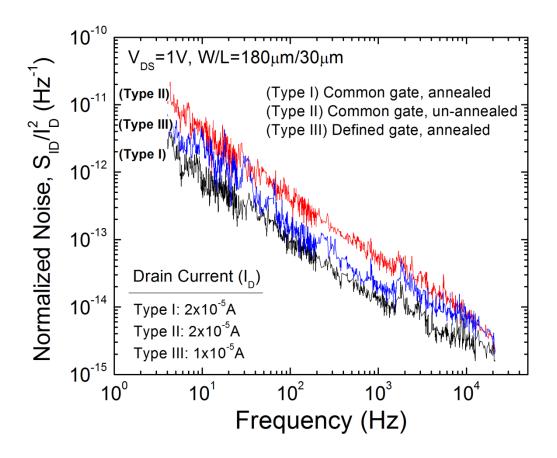

| <b>Figure 8.12</b> Normalized linear region transfer properties of various RF sputter a-IGZO TFTs in (a) semi-log and (b) linear plots                    |

| <b>Figure 8.13</b> Normalized noise spectrums collected from various RF sputter a-IGZO TFTs.                                                              |

# **List of Tables**

| <b>Table 1.1</b> Challenges of TFT backplanes for next generation optoelectronics.    5                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Table 1.2</b> Comparison of different TFT technologies.    6                                                                                                                                                                                |

| <b>Table 2.1</b> Typical electrical properties of common gate a-IGZO TFTs                                                                                                                                                                      |

| Table 2.2 Electrical properties of defined gate, RF sputter a-IGZO TFT                                                                                                                                                                         |

| <b>Table 4.1</b> Experimental conditions for photofield-effect study.    60                                                                                                                                                                    |

| Table 4.2 Key electrical properties of PLD a-IGZO TFTs with 50nm Al S/D electrodes used in this study.       65                                                                                                                                |

| <b>Table 5.1</b> Key simulation parameters and properties of common gate, inverted-staggered a-IGZO TFT.       90                                                                                                                              |

| <b>Table 6.1</b> Simulated a-IGZO TFT electrical properties for various r <sub>c</sub> values 106                                                                                                                                              |

| <b>Table 7.1</b> Fitting parameters for stretched-exponential model used in this study 130                                                                                                                                                     |

| <b>Table 8.1</b> Normalized flicker noise spectral density $(S_{ID}/I_D^2)$ for $\Delta n$ and $\Delta \mu$ in MOSFET or TFT. $C_{ox}$ is the gate insulator capacitance per unit area; W and L are TFT channel length and width, respectively |

| Table 8.2 Optimized amplifier noise parameters $(I_n \text{ and } V_n)$ for the measurement system used in this study.       142                                                                                                               |

| Table 8.3 Normalized measurement conditions for studying the channel area dependent noise properties.       146                                                                                                                                |

| <b>Table 8.4</b> Structures and electrical properties of various RF sputter a-IGZO TFTs 156                                                                                                                                                    |

# Chapter 1

### Introduction

## 1.1 Overview / Background

#### 1.1.1 Current status and limitation of a-Si:H TFT backplane technology

The Hydrogenated amorphous silicon (a-Si:H) thin-film transistor (TFT) has long been the workhorse in the active-matrix liquid crystal display (AM-LCD) industry. As the most critical element of the entire AM-LCD, the active-matrix backplane commonly consists of a array of a-Si:H TFT pixel electrode circuits, which directly drive each individual liquid crystal cell pixel [1, 2]. This approach significantly reduces the pixel crosstalk and allows the LCD display to have a high resolution. Thanks to the growing need for large area displays for home entertainment and the full adoption of digital broadcasting, the active-matrix flat panel display (AM-FPD) industry experienced a strong growth during the past few years. It has taken over the dominate role in TV market from the old, bulky cathode ray tube (CRT) technology and is predicted to reach a 96% market penetration during year 2009 [3]. Although there are many different technologies available for AM-FPD, active-matrix liquid crystal display (AM-LCD) is by far the dominant one and is expected to occupy more than 70% of the entire AM-FPD market [3].

Just like the microelectronics industry pursues the miniaturization of transistors dic-

tated by Moore's law for lower production cost and enhanced functionality, scientists and engineers continuously investigates new material and processing technologies to fabricate TFT backplane over even larger substrate areas. Because of this unique technological road map, the TFT backplane has also frequently been called "macroelectronic" device [4]. During the past decades, the plasma enhanced chemical vapor deposition (PECVD) has been proven to be the ideal technique to deposit highly uniform a-Si:H thin film while keeping up the trend of substrate size scaling [5]. Today, the state-of-art Gen-8 facility is able to process glass substrate approximately 2160 × 2460 mm in size [6], which can produced up to six 52-inch flat panel TV screens from one single substrate!

The typical PECVD a-Si:H TFT has field effect mobility ( $\mu_{eff}$ ) of 0.6 ~ 0.8cm²/Vs, sub-threshold swing of 0.3 ~ 0.4V/dec, off-state drain current ( $I_{D\_off}$ ) below  $10^{-13}A$  and on-to-off ratio about  $10^7$  [7]. These properties are suitable for liquid crystal cell switching but the  $\mu_{eff}$  could become insufficient for the new requirements of next generation displays. For example, the future trend for AM-LCD is toward large area (e.g. 82-inch) with QFHD (3840×2160 pixels) resolutions [8, 9]. To suppress the display motion blur effect in QFHD, high frequency (120~240Hz or even higher) display driving circuits will be inevitable [10]. The driving scheme of the 120Hz (or higher) QFHD display only allows the pixel charging time to be less than 4 $\mu$ sec [9]. Conventional a-Si:H TFT backplane configuration doesn't work well in such short time and the pulse / clock signal can be distorted. To address this issue, proposed solutions are focused on reducing the gate bus-line RC propagation delay, such as adding gate planarization layer [11], adopting buried bus-line structure [12] or using low resistance Cu interconnection [13]. Nonetheless, the low  $\mu_{eff}$  (< 1cm²/Vs) of a-Si:H TFT itself can still fundamentally restrict the high frequency response of backplane. A TFT LCD pixel charging time ( $t_{charge}$ ) is about five RC time constants ( $t_{charge}$  ~ 5RonCpix),

where  $C_{pix}$  is the pixel capacitance and  $R_{on}$  is the TFT channel resistance.  $R_{on}$  can be estimated as follows:

$$R_{on} \approx \frac{L}{W\mu_{eff} (V_{GS} - V_{th}) C_{SiNx}}, \tag{1-1}$$

where W and L are channel width and length, respectively;  $V_{GS}$  and  $V_{th}$  are gate voltage and TFT threshold voltage, respectively; and  $C_{SiNx}$  is the gate insulator capacitance. For a typical a-Si:H TFT pixel,  $C_{pix}$  is ~0.5pF, and  $R_{on}$  is ~1.67M $\Omega$  (W/L=3,  $\mu_{eff}$  ~ 0.6cm<sup>2</sup>/Vs,  $(V_{GS}-V_{th})$ ~10V and  $C_{SiNx}$  ~3.32×10<sup>-8</sup> F/cm<sup>2</sup>). This combination results in a  $t_{charge}$  of 4.2 $\mu$ sec. Thus, the  $t_{charge}$  required for a-Si:H TFT is too long, and driving large size, high rate/ resolution display with a-Si:H TFT backplane will be either impractical or complicated [9]. As indicated in (1-1), a high-mobility material is desired, since it can reduce  $R_{on}$  and  $t_{charge}$ .

The other emerging area in AM-FPD is the emissive display such as active-matrix organic light-emitting display (AM-OLED), where the organic light emitting diode (OLED) is directly integrated with the TFT pixel electrode circuit. AM-OLED avoids the need of backlight and the dynamic range of the AM-OLED brightness can be controlled at the pixel level, which is ideal for TV applications [14]. In addition, it can have an extremely high contrast ratio and delivers much better picture quality than the AM-LCD [15]. Despite all these attractive properties, AM-OLED actually poses more stringent requirement on TFT backplane. Unlike liquid crystal which only required external electrical field to change its phase, OLED takes significant amount of current to produce light. The  $\mu_{eff}$  of a-Si:H TFT, unfortunately, is not high enough to drive a large area AM-OLED [16]. Because the TFT may constantly operate under high bias, a long term electrical instability is another concern [17] and can also make the pixel electrode circuit design more complicated (e.g. additional compensation circuits are needed) [18].

**Figure 1.1** Circuit schematics for (a) passive pixel sensor (PPS) and (b) active pixel sensor (APS). Both pixel circuits contain photodiode (PD) and storage capacitor ( $C_{st}$ ). RED, AMP and RST represent read, amplifier and reset TFTs, respectively, in APS design.

#### 1.1.2 a-Si:H TFT backplane in photo-imager

The application of a-Si:H TFT backplane is not limited to AM-FPD. By integrating the photodiode or radiation sensitive layer with the backplane, a-Si:H TFT can also be used for sensor signal readout [19]. One important example is the flat panel X-ray imager used for medical imaging [20-22]. Traditionally, a single TFT pixel electrode circuits is used to passively (no amplification) control the signal current transfer from sensor (Figure 1.1(a)). This restricts the sensor signal-to-noise ratio and also lengthens the imager response time. Recently, a more advanced approach, or so called "active pixel sensor (APS)" is proposed. By adding a transconductance amplifier stage in the a-Si:H TFT pixel electrode circuit, the APS is able to achieve a higher signal-to-noise ratio and a high operating speed [23]. Such circuit is expected to be more suitable for a low-noise, a high speed imaging like X-ray fluoroscopy [24].

As one of the key metrics for photo-imager performance, the sensor resolution can be

| Applications | Technological Requirements on TFT Backplane | Enabling Material Properties |

|--------------|---------------------------------------------|------------------------------|

|              | Large area                                  | Uniform amorphous phase      |

| AM-LCD       | High aperture ratio                         | Visible light transparency / |

| AM-LCD       |                                             | High mobility                |

|              | Fast response                               | High mobility                |

|              | Good current driving capability             | High mobility                |

| AM-OLED      | Good stability                              | Low defect and weak          |

|              |                                             | bonding density              |

|              | Large dynamic range                         | High mobility                |

| Photo-imager | Small pixel size                            | High mobility                |

|              | (high resolution)                           | High mobility                |

**Table 1.1** Challenges of TFT backplanes for next generation optoelectronics.

more demanding than what is needed for display and it is directly dictated by the TFT backplane design. As shown in Figure 1.1(b), typical APS has three TFTs (read, amplifier and reset TFTs) in one single pixel [24]. In order to achieve desirable APS signal gain for signal readout, both amplifier and readout TFT can have a width-over-length ratio (W/L) of  $150\mu\text{m}/25\mu\text{m}$  when using a-Si:H as the semiconductor material [23]. These transistors take a significant amount of pixel area ( $\sim 50\%$  for  $250\mu\text{m}^2$  pixel size) resulting in a low imager resolution (<200dpi) [25], which is considered as one drawback for a-Si:H TFT APS. To better understand the design constrain, we approximate the small signal current gain of AMP TFT ( $g_{\text{m}\_AMP}$ ) by its saturation region transconductance:

$$g_{m\_AMP} \cong \mu_{eff} C_{ox} \frac{W}{I} \left( V_{GS\_AMP} - V_{th} \right) , \qquad (1-2)$$

where  $V_{GS\_AMP}$  is the difference of AMP TFT gate and source voltage;  $V_{th}$  is the threshold voltage. Equation 1-2 suggests that the  $g_{m\_AMP}$  is proportional to the product of  $\mu_{eff}$  and W/L ratio. For a low mobility semiconductor like a-Si:H, designing a TFT with a large W/L ratio to achieve a high gain is necessary. Therefore, for a definite gate length, adopting TFT

| Technology | Mobility (cm <sup>2</sup> /Vs) | Visible Light<br>Transparency | Large Area<br>Uniformity | Comments                   |

|------------|--------------------------------|-------------------------------|--------------------------|----------------------------|