# MANAGING VARIABILITY IN VLSI CIRCUITS

by

## Brian T. Cline

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2010

#### **Doctoral Committee:**

Professor David Blaauw, Chair Professor Marios Papaefthymiou Associate Professor Joanna Mirecki-Millunchick Associate Professor Dennis M. Sylvester

© Brian T. Cline All Rights Reserved 2010

# **DEDICATION**

# To my Family & Friends...

This dissertation is dedicated to my family and friends that supported, encouraged, and inspired me throughout my education. I'd especially like to thank my wife, Cecilia, my parents, Kevin and Barbara, and my sisters Kelly and Caitlin. I love you all.

#### **ACKNOWLEDGEMENTS**

Aside from the people that I dedicate my dissertation to, I would also like to offer my most sincere gratitude to a number of people. First, I would like to thank the following people for their support: my advisor, David Blaauw, Dennis Sylvester, and the rest of my dissertation committee: Professor Papaefthymiou and Professor Mirecki-Millunchick. I would also like to especially acknowledge my colleague Vivek Joshi for his collaboration on Chapter 4. I also express my deepest thanks to all of my colleagues that worked under Professors Blaauw and Sylvester during my years at the University of Michigan. Finally, I would like to acknowledge the Semiconductor Research Corporation, Freescale Semiconductor, and Mentor Graphics for their support throughout my doctoral studies.

# TABLE OF CONTENTS

| Dedication                                                        | ii   |

|-------------------------------------------------------------------|------|

| Acknowledgements                                                  | iii  |

| List of Figures                                                   | viii |

| List of Tables                                                    | x    |

| Abstract                                                          | xi   |

| CHAPTER 1: INTRODUCTION                                           | 1    |

| 1.1. Gate Length Variation                                        | 3    |

| 1.2. Threshold Voltage Variation                                  | 6    |

| 1.3. Oxide and Inter-Layer Dielectric Thickness Variation         | 8    |

| 1.4. Sub-100nm Induced Variation and Mobility Degradation         | 9    |

| 1.5. Managing Variability in VLSI Designs                         | 11   |

| 1.6. Contribution of Dissertation                                 | 14   |

| 1.7. Organization of Dissertation                                 | 15   |

| CHAPTER 2: CD VARIATION ANALYSIS AND CORRELATION MODELING IN SSTA | 17   |

| 2.1. Types of Gate Length Variation                               | 20   |

| 2.1.1. Independent                                                | 20   |

| 2.1.2. Die-to-Die                                                 | 20   |

| 2.1.3. Spatially Correlated                                       | 21   |

| 2.2. Correlation Models                                           | 21   |

| 2.2.1. D2D, Random, and D2D + Random                              | 22   |

| 2.2.2. PCA                                                        | 23   |

| 2.2.3. Quad-Tree                                                  | 24   |

| 2.3. Experimental Data and Analysis                                         | . 26 |

|-----------------------------------------------------------------------------|------|

| 2.4. Variation Modeling and SSTA Results                                    | .30  |

| 2.4.1. Model Accuracy vs. Die Size                                          | .35  |

| 2.4.2. Grid Model Behavior                                                  | .36  |

| 2.5. Summary                                                                | .38  |

| CHAPTER 3: MODELING CD VARIATION IN SSTA                                    | .39  |

| 3.1. Prior Work and Previous Approach                                       | .42  |

| 3.1.1. Delay Model                                                          | .43  |

| 3.1.2. CD Model                                                             | . 44 |

| 3.2. Proposed Transistor-Specific Model                                     | .45  |

| 3.2.1. Transistor-Specific CD and Delay Models                              | .48  |

| 3.2.2. Transistor-Specific Characterization                                 | .49  |

| 3.2.3. Litho-Aware Simulation                                               | .51  |

| 3.3. Results                                                                | . 52 |

| 3.3.1. Experimental Setup                                                   | . 53 |

| 3.3.2. CD and Delay Distributions                                           | . 55 |

| 3.3.3. Model Comparison                                                     | . 56 |

| 3.4. Summary                                                                | . 58 |

| CHAPTER 4: MECHANICAL STRESS AWARE OPTIMIZATION FOR LEAKAGE POWER REDUCTION |      |

| 4.1. Prior Work                                                             | . 62 |

| 4.2. Contributions                                                          | . 63 |

| 4.3. Background                                                             | . 64 |

| 4.3.1. Mechanical Stress Sources and their Layout Dependence                | . 65 |

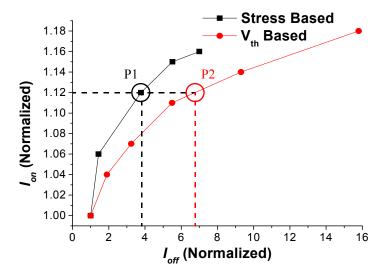

| 4.3.2. Drain Current Dependence on Stress and Vth                           | . 67 |

| 4.4. Layout Dependence of Stress-Based Performance Enhancement              | . 70 |

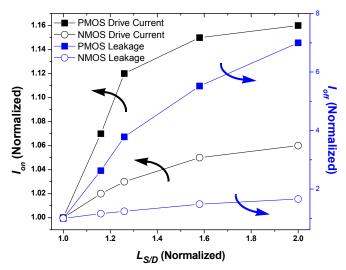

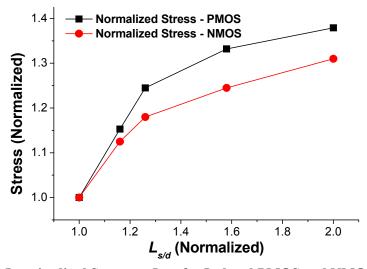

| 4.5. Layout Properties that Impact Mechanical Stress and Performance        | .75  |

| 4.6. Modifying 65nm Standard Cell Layouts                                   | .81  |

| 4.7. Optimization Methodology                                               | . 87 |

| 4.8. Experimental Setup and Results                                            | 90  |

|--------------------------------------------------------------------------------|-----|

| 4.8.1. Library Characterization                                                | 90  |

| 4.8.2. Experimental Results                                                    | 92  |

| 4.9. Summary                                                                   | 100 |

| CHAPTER 5: STEEL: A TECHNIQUE FOR STRESS-ENHANCED STANDARD CELL LIBRARY DESIGN | 102 |

| 5.1. A Technique for Enhancing Stress in Standard Cell Layouts                 | 103 |

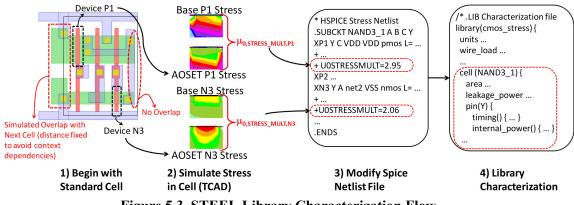

| 5.2. Implementation of STEEL in Standard Cell Design                           | 106 |

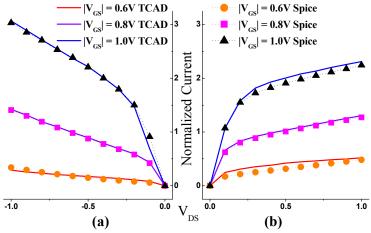

| 5.2.1. Tsuprem4 and Davinci Device Simulation                                  | 107 |

| 5.2.2. Stress-Enhanced BSIM4 Hspice Model                                      | 108 |

| 5.2.3. Standard Cell Library Characterization                                  | 109 |

| 5.2.4. Implementation Decisions in STEEL                                       | 109 |

| 5.3. Experimental Results                                                      | 112 |

| 5.3.1. APR using STEEL Libraries                                               | 112 |

| 5.3.2. STEEL versus Regular-Vth Results                                        | 113 |

| 5.3.3. STEEL versus Dual-Vth Results                                           | 117 |

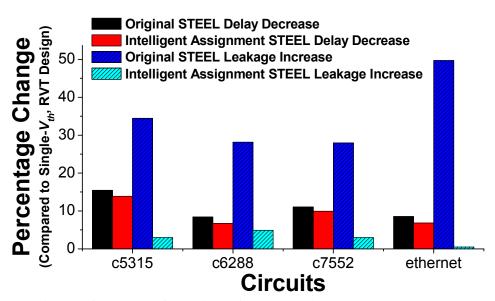

| 5.3.4. Intelligent STEEL-Cell Assignment                                       | 119 |

| 5.4. Summary                                                                   | 122 |

| CHAPTER 6: COMBINING STRESS ENHANCEMENT WITH GATE LENGTH BIASING               | 124 |

| 6.1. Stress Enhancement and Gate-Length Biasing                                | 127 |

| 6.2. STLB Standard Cell Library Implementation                                 | 130 |

| 6.2.1. Combining Stress-Enhancement and Gate-Length Biasing                    | 130 |

| 6.2.2. The STLB 65nm Library                                                   | 131 |

| 6.3. Dual Performance Optimizer for DVT and STLB Libraries                     | 135 |

| 6.4. Experimental Results                                                      | 137 |

| 6.5. Summary                                                                   | 140 |

| CHAPTER 7: CONCLUSION AND FUTURE WORK                                          | 141 |

| 7.1. Conclusion – Summarizing Our Contributions                                | 142 |

| RELATED PUBLICATIONS |                                                               | 148  |

|----------------------|---------------------------------------------------------------|------|

| DE                   | 7.2.3. Further Exploration of Mechanical Stress               |      |

|                      | 7.2.2 Eurther Exploration of Machanical Stress                | 1.47 |

|                      | 7.2.2. Library Characterization, Automation, and Optimization | 146  |

|                      | 7.2.1. CD Modeling at Advanced Process Nodes                  | 145  |

| ,                    | 7.2. Future Work                                              | 145  |

# LIST OF FIGURES

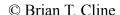

| Figure 1.1  | Supply Voltage vs. Process Node and Gate Length.                   | 2  |

|-------------|--------------------------------------------------------------------|----|

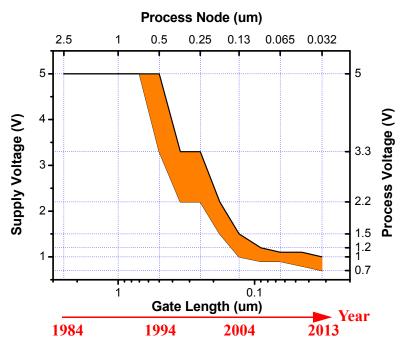

| Figure 1.2  | Simple Polysilicon SRAF and OPC Example.                           |    |

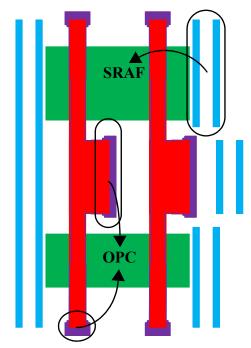

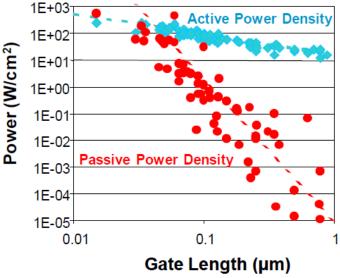

| Figure 1.3  | Dynamic and Static Power Density vs. Technology [19]               | 8  |

| Figure 1.4  | Preferred CMOS Device Stress Types.                                |    |

| Figure 2.1  | PCA Grid Example.                                                  | 23 |

| Figure 2.2  | Quad-tree Model Example.                                           | 24 |

| Figure 2.3  | Wafer CD Measurement Contour Plot.                                 | 27 |

| Figure 2.4  | (a) Mean CD Values for Die (2x2 reticle dice)                      |    |

|             | (b) Standard Deviation/Mean for Die (2x2 reticle dice)             | 28 |

| Figure 2.5  | (a) Mean CD Values for Die (4x4 reticle dice)                      |    |

|             | (b) Standard Deviation/Mean for Die (4x4 reticle dice)             |    |

| Figure 2.6  | Average Correlation vs. Distance (2x2 reticle)                     | 30 |

| Figure 2.7  | Average Correlation vs. Distance (1-dimension only)                |    |

| Figure 2.8  | PDF Plot for ELM Measured CD.                                      | 31 |

| Figure 2.9  | Timing Analyses Flow.                                              |    |

| Figure 2.10 | Probability Density Plots for 3 Models (Enumeration-Based, PCA Mo  |    |

|             | Based Monte Carlo, and PCA Probabilistic).                         |    |

| Figure 2.11 | Mean and Standard Deviation vs. Number of Principal Components     | 37 |

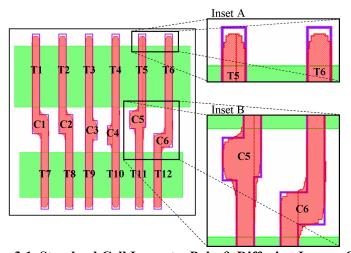

| Figure 3.1  | Standard Cell Layout – Poly & Diffusion Layers Only                |    |

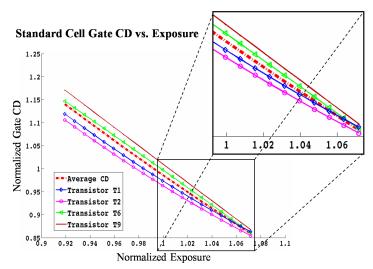

| Figure 3.2  | Standard Cell Gate CD vs. Exposure.                                |    |

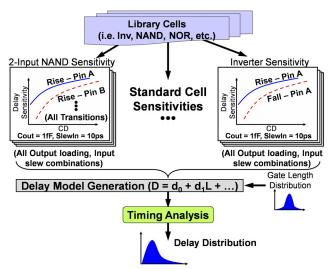

| Figure 3.3  | Delay Model Characterization.                                      | 44 |

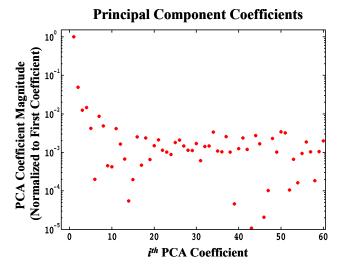

| Figure 3.4  | Normalized CD Distribution PCA Coefficients.                       | 47 |

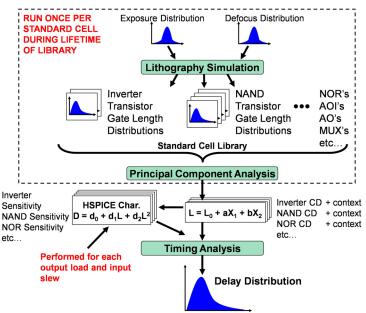

| Figure 3.5  | Proposed Transistor-Specific Delay Model Flow.                     | 50 |

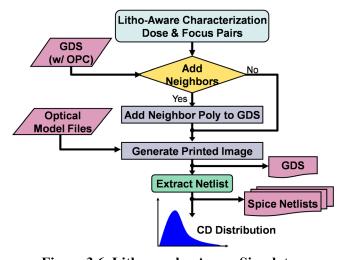

| Figure 3.6  | Lithography-Aware Simulator                                        | 51 |

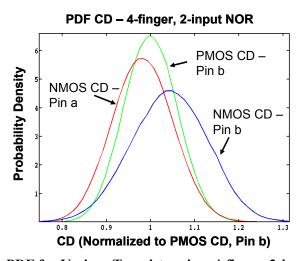

| Figure 3.7  | PDF for Various Transistors in a 4-finger, 2-input NOR gate        | 55 |

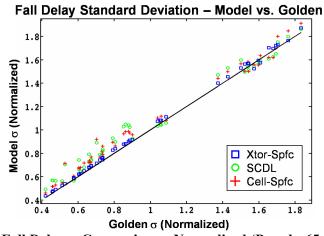

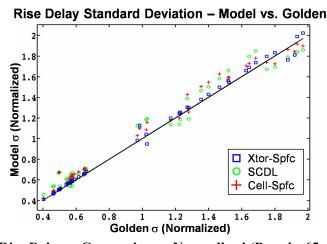

| Figure 3.8  | Fall Delay s Comparison – Normalized (Pseudo-65nm Variation)       | 57 |

| Figure 3.9  | Rise Delay s Comparison – Normalized (Pseudo-65nm Variation)       | 57 |

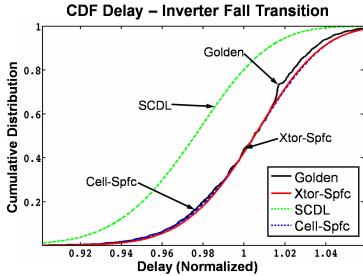

| Figure 3.10 | Minimum-sized Inverter Fall Delay Transition CDF (90nm Variation). | 59 |

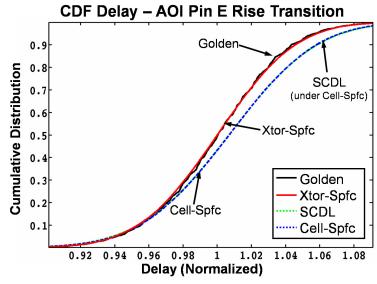

| Figure 3.11 | AND/OR Invert Rise Delay Transition CDF (90nm Variation)           | 59 |

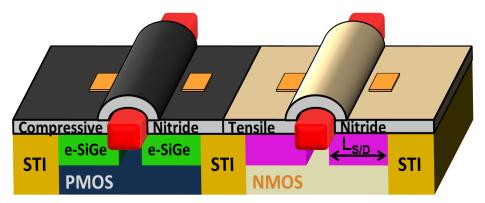

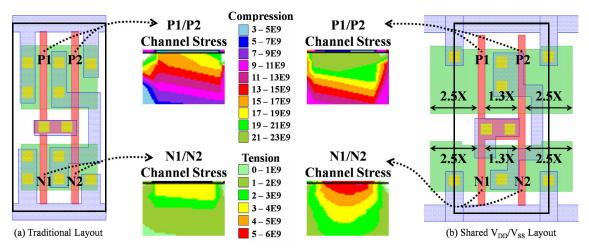

| Figure 4.1  | Sources of Stress for NMOS and PMOS Devices.                       | 65 |

| Figure 4.2  | 65nm PMOS Ion vs. Ioff for Vth-based and Stress-based              |    |

|             | Enhancement                                                        | 69 |

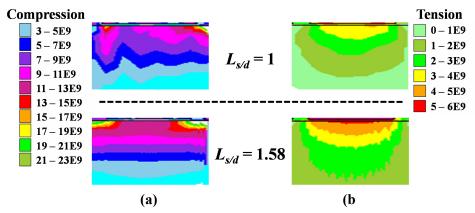

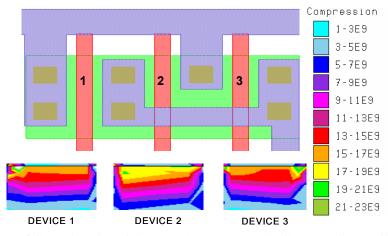

| Figure 4.3  | Longitudinal Stress, Sxx (Pa), for Normalized LS/D of 1 and 1.58                                                 | 72    |

|-------------|------------------------------------------------------------------------------------------------------------------|-------|

| Figure 4.4  | Ioff and Ion vs. LS/D for Stress-based Enhancement in Isolated PMOS NMOS Devices.                                |       |

| Figure 4.5  | Longitudinal Stress vs. LS/D for Isolated PMOS and NMOS Devices                                                  |       |

| Figure 4.6  | PMOS Devices in a 3-input NAND and their Channel Stress Contours (Pa)                                            |       |

| Figure 4.7  | Application of Layout Property #1 to PMOS Stack in 3-input NOR                                                   |       |

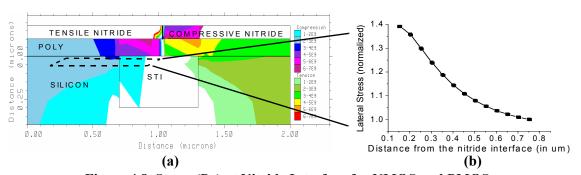

| Figure 4.8  | Stress (Pa) at Nitride Interface for NMOS and PMOS                                                               | 78    |

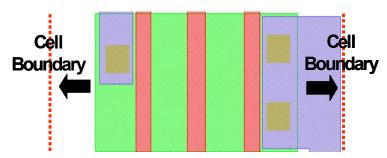

| Figure 4.9  | Two Layouts Illustrating Scope for Layout-based Stress Improvement.                                              | 82    |

| Figure 4.10 | Basic Domino Gate and Two Possible Layouts for the PMOS Devices.                                                 | 86    |

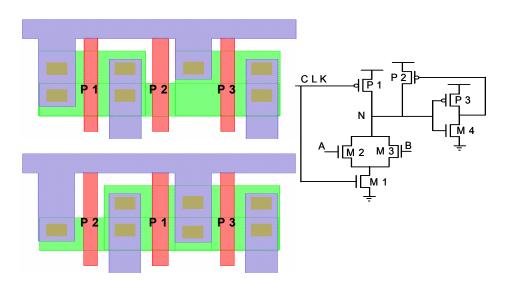

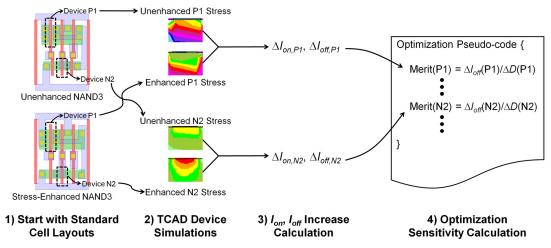

| Figure 4.11 | Leakage and Switching Delays for Various Combinations of Vth and Stress-based Optimization for 3-input NOR Gate. | 87    |

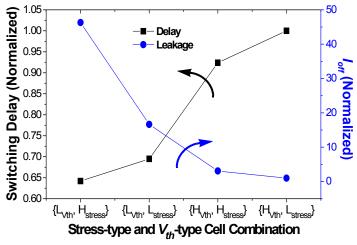

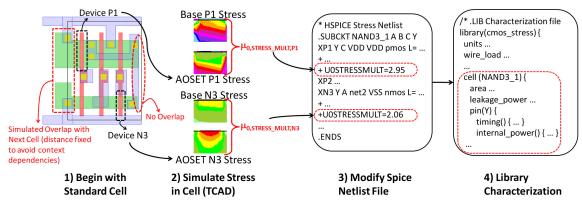

| Figure 4.12 | Custom Library Characterization Flow for Stress-aware Optimization.                                              | 91    |

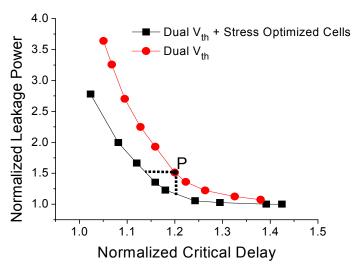

| Figure 4.13 | Pleak vs. Delay for Dual-Vth and Proposed Approach for Benchmark c7552                                           | 94    |

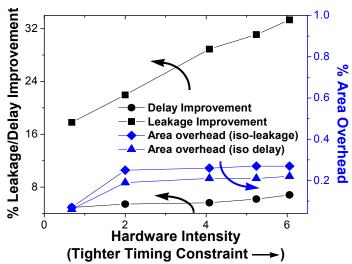

| Figure 4.14 | Delay, Pleak, and Area Overhead vs. Hardware Intensity                                                           |       |

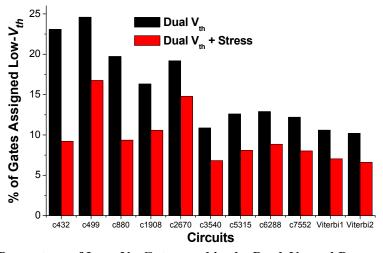

| Figure 4.15 | Percentage of Low-Vth Gates used in the Dual-Vth and Proposed Approach                                           | 98    |

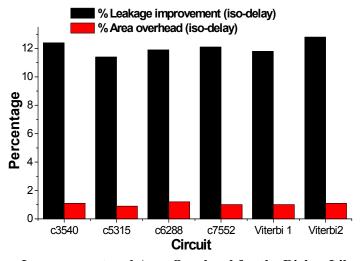

| Figure 4.16 | Pleak Improvement and Area Overhead for the Richer Library vs.  Original                                         | 99    |

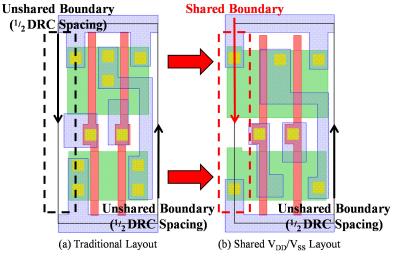

| Figure 5.1  | Traditional Standard Cell Layout vs. Proposed Shared Source/Drain Layout for a 2-input NAND                      |       |

| Figure 5.2  | Impact of Shared VDD/VSS Approach on Stress (Pa) in a Two-Finger Inverter.                                       |       |

| Figure 5.3  | STEEL Library Characterization Flow.                                                                             | . 106 |

| Figure 5.4  | Davinci vs. Hspice I-V plots                                                                                     | . 108 |

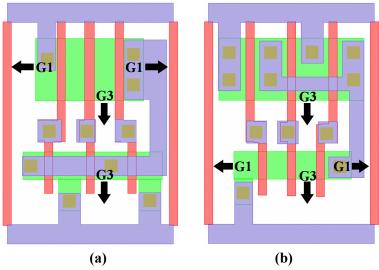

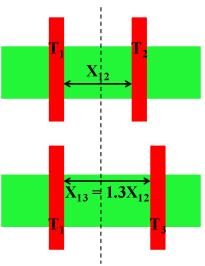

| Figure 5.5  | Context Dependency within STEEL Designs.                                                                         | . 111 |

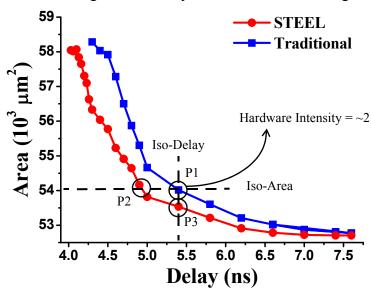

| Figure 5.6  | Viterbi Decoder Area vs. Delay (Single-Vth)                                                                      | . 114 |

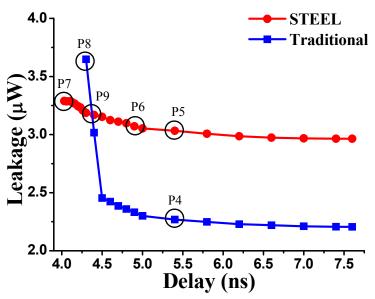

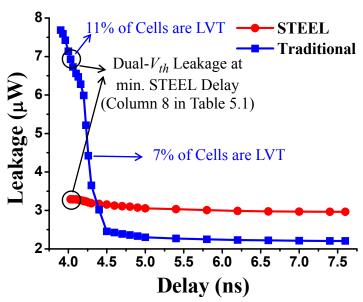

| Figure 5.7  | Viterbi Decoder Leakage Power vs. Delay (Single-Vth)                                                             | . 115 |

| Figure 5.8  | Viterbi Decoder Pleak vs. Delay Plot comparing Dual-Vth and                                                      |       |

|             | STEEL.                                                                                                           |       |

| Figure 5.9  | Impact of Intelligent STEEL Assignment on Delay and Pleak                                                        |       |

| Figure 6.1  | Dynamic and Static Power Density vs. Technology [19]                                                             |       |

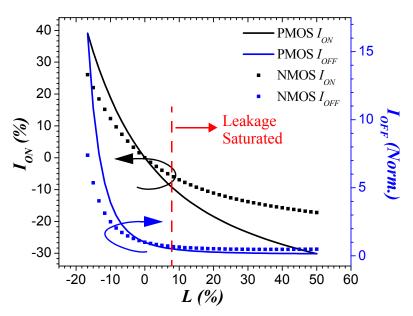

| Figure 6.2  | Normalized Ion and Ioff vs. L for PMOS and NMOS devices                                                          |       |

| Figure 6.3  | STLB characterization flow.                                                                                      | . 132 |

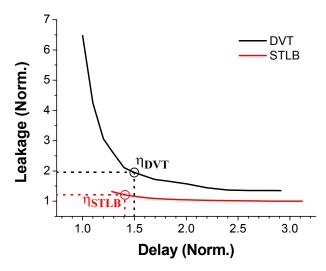

| Figure 6.4  | Normalized Leakage Power vs. Delay for Benchmark Viterbi Decoder 1                                               | . 138 |

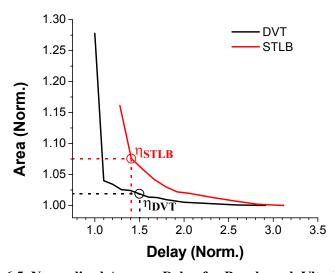

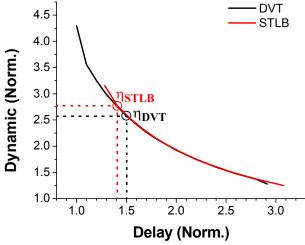

| Figure 6.5  | Normalized Area vs. Delay for Benchmark Viterbi Decoder 1                                                        | .138  |

| Figure 6.6  | Normalized Dynamic Power vs. Delay for Benchmark Viterbi Decoder 1                                               | . 138 |

# LIST OF TABLES

| Table 2.1 | Enumeration-Based, Model-Based, and Probabilistic TA Results          | 33  |

|-----------|-----------------------------------------------------------------------|-----|

| Table 2.2 | Model vs. Die Size.                                                   | 36  |

| Table 3.1 | Percentage Deviation from Max CD.                                     | 46  |

| Table 3.2 | Absolute Error in Standard Deviation.                                 | 56  |

| Table 4.1 | Percentage Contribution of Layout Properties 1–3 to the Overall Drive |     |

|           | Current Improvement for PMOS/NMOS Stacks                              | 83  |

| Table 4.2 | Summary of Stress-Aware Layout Optimization Drive Current             |     |

|           | Improvement and Tradeoffs in 65nm Standard Cells                      | 84  |

| Table 4.3 | Stress and Vth Combinations.                                          | 95  |

| Table 4.4 | Improvement in Leakage and Delay Compared to Dual-Vth based           |     |

|           | Assignment.                                                           | 96  |

| Table 5.1 | Design Improvement Obtained using STEEL.                              | 116 |

| Table 6.1 | Methods for Increasing PMOS and NMOS Mobility in Standard             |     |

|           | Cells.                                                                | 128 |

| Table 6.2 | DVT vs. STLB Library Comparison.                                      | 134 |

| Table 6.3 | STLB Performance Directly Compared to DVT.                            | 139 |

|           |                                                                       |     |

#### **ABSTRACT**

Over the last two decades, Design for Manufacturing (DFM) has emerged as an essential field within the semiconductor industry. The main objective of DFM is to reduce and, if possible, eliminate variability in integrated circuits (ICs). Numerous techniques for managing variation have emerged throughout IC design: manufacturers design instruments with minute tolerances, process engineers calibrate and characterize a given process throughout its lifetime, and IC designers strive to model and characterize variability within their devices, libraries, and circuits. This dissertation focuses on the last of these three techniques and presents material relevant to managing variability within IC design. Since characterization and modeling are essential to the analysis and reduction of variation in modern-day designs, this dissertation begins by studying various correlation models used within Statistical Static Timing Analysis (SSTA). In the end, the study shows that using complex correlation models does not necessarily result in significant error reduction within SSTA, and that simple models (which only include die-to-die and random variation) can therefore be used to achieve similar accuracy with reduced overhead and run-time. Next, the variation models, themselves, are explored and a new critical dimension (CD) model is proposed which reduces standard deviation error in SSTA by ~3X. Finally, the focus changes from the timing analysis level and moves lower in the design hierarchy to the libraries and devices that comprise the backbone of IC

design. The final three chapters study mechanical stress enhancement and discuss how to fully exploit the layout dependencies of mechanically stressed silicon. The first of these three chapters presents an optimization scheme that uses the layout dependencies of stress in conjunction with dual-threshold-voltage ( $V_{th}$ ) assignment to decrease leakage power consumption by ~24%. Next, the second of the three chapters proposes a new standard cell library design methodology, called "STEEL." STEEL provides average delay improvements of 11% over equivalent single- $V_{th}$  implementations, while consuming 2.5X less leakage than the dual- $V_{th}$  alternative. Finally, the stress enhanced studies (and this document) are concluded by a new optimization scheme that combines stress enhancement with gate length biasing to achieve 2.9X leakage power savings in IC designs without modifying  $V_{th}$ .

#### CHAPTER 1

#### Introduction

For the past forty years, the driving force behind the semiconductor industry has been device scaling and the ability to manufacture smaller geometries. Traditionally, in order to maintain electric fields of the same magnitude within these scaled devices, process engineers would also scale the device voltages (e.g., supply voltage and threshold voltage). Since the creation of the first microprocessors in the 1970's, supply voltage and gate length have decreased from ~15V and 10µm [1], respectively, to 0.9V and 32nm [2] in state-of-the-art technologies. In other words, over the past three decades geometries have scaled by  $\sim 1000$ X while supply voltage has only scaled by  $\sim 10$ X. This difference is partially illustrated in Figure 1.1, which shows supply voltage versus gate length over the last 25 years [3-4]. Voltage scaling has significantly lagged behind geometry scaling in modern-day technology nodes (starting around the 90nm process node in Figure 1.1) because process engineers can no longer scale the supply voltage,  $V_{DD}$ , or the threshold voltage,  $V_{th}$ , without significantly degrading reliability and exponentially increasing leakage power consumption. Consequently, devices manufactured in the latest technology nodes have higher effective electric fields than their predecessors. These increased electric fields can lead to a number of parasitic effects such as drain-induced barrier lowering (DIBL), gate-induced drain leakage (GIDL), mobility degradation, and hot carrier

Figure 1.1. Supply Voltage vs. Process Node and Gate Length. Voltage is shown as a range between high-performance and low-power voltages.

degradation. However, electric-field-related parasitics are merely one subset of a larger collection of issues that the semiconductor industry is faced with today.

Of all the pressing semiconductor issues, one of the most fundamental concerns is, simply, how to manufacture these nanoscale devices and fabricate features that are 32nm or smaller. Since state-of-the-art devices are currently made using photolithography techniques that use 193nm wavelength light, printing sub-193nm features on a wafer is difficult, due to optical effects that occur. To further complicate matters, manufacturing issues such as linewidth variation, random dopant fluctuation, and dielectric thickness variation have complex dependencies and are statistical in nature. This means that the traditional semiconductor device can no longer be handled in a deterministic manner and modern-day integrated circuits (ICs) have to be designed to tolerate variation in certain device parameters such as threshold voltage, gate length, and oxide thickness, in addition

to tolerating variation in interconnect properties like resistance and capacitance. In the last ten years variability in semiconductor devices has become such a large concern that an entirely new technology field has emerged – Design for Manufacturability (DFM).

The concept of designing with manufacturability in mind is somewhat of a departure from traditional semiconductor design practices since IC design and IC fabrication were two distinct entities for the first 30 years of the semiconductor industry. DFM, therefore, attempts to "bridge the gap" between these two fields and make engineers on both sides aware of the others' difficulties, challenges, and pitfalls. While linking IC design with semiconductor manufacturing, the ultimate objective is to improve IC yield by either reducing a circuit's susceptibility to variation or by reducing variation altogether. DFM from a "Very Large-Scale Integration" (VLSI) perspective typically involves reducing and tolerating certain amounts of variation in gate length (L), threshold voltage ( $V_{th}$ ), oxide thickness ( $t_{ox}$ ), and inter-layer dielectric (ILD) thickness.\(^1\) Since the underlying mechanisms that cause variation in these parameters are different, each parameter requires its own set of solutions and design rules.

# 1.1 Gate Length Variation

Fabricated geometries in today's semiconductor processes vary from transistor to transistor, die to die, reticle to reticle, and wafer to wafer. Since digital ICs typically utilize the minimum gate length allowed for a device, gate length is especially susceptible to variation and can dramatically affect performance (in terms of both delay and power). Gate length variation is often included within a more liberal classification of variation,

<sup>&</sup>lt;sup>1</sup> Inter-layer dielectric thickness is a measure of the dielectric height between metal layers in an IC.

called critical dimension (CD) variation.<sup>2</sup> CD variation has proven to be an interesting and difficult research problem on a variety of VLSI fronts. A significant number of publications have been dedicated to characterizing, modeling, analyzing, managing, and reducing CD variation [5-10]. CD variability is particularly formidable because it contains both a probabilistic component that is independent of other components, as well as a spatially correlated (systematic) component that is dependent on device context.<sup>3</sup> The probabilistic components of variation manifest themselves with either a low spatial frequency (e.g., shifts in CD) or high spatial frequency (e.g., line-edge roughness). The underlying causes of CD variation are numerous and include stepper imperfections (lens aberrations, variations in exposure and defocus, etc.), reticle defects, and photoresist variations (non-uniformity and thickness variation, post-exposure bake time variation, etc.), among others [7,11]. In fact, CD variability and its causes have become such a large concern that manufacturers have had to add mask correction techniques such as subresolution assist features (SRAFs) and optical proximity corrections (OPCs) to try and compensate for known imperfections during fabrication.

Process engineers rely on SRAF's and OPC's to ensure that the devices and interconnect print with minimum placement error (often referred to as EPE, or edge placement error). A simple example of what these features look like in a typical layout is included in Figure 1.2. In addition to improving printability, these features and corrections also strive to reduce variability. Other techniques that are being researched to reduce CD variability are regularity [8-9] and logic-brick/fabric design [10]. Since regularity makes

<sup>&</sup>lt;sup>2</sup> Critical dimension refers to the smallest feature size that can be manufactured/printed in a particular technology.

The context of a particular device involves both the distance between a device and its neighbors, as well as the size and orientation of the neighbors.

Figure 1.2. Simple Polysilicon SRAF and OPC Example.

Drawn poly is shown in red, while the OPC's and SRAF's are purple and blue.

context dependency more predictable (because features are placed at fixed intervals), it typically reduces the systematic CD variability. With reduced systematic variation, the complex OPC rules and resolution enhancement techniques (RETs) can be relaxed and become less computationally expensive.

Variations in CD affect VLSI designs in numerous ways and can dramatically alter an IC's performance. For example, gate length, or L, variation (one type of CD variation) affects a number of metal-oxide-semiconductor field-effect transistor (MOSFET) characteristics. Variation in L changes the drain current ( $I_D$ ) in all operating regimes (subthreshold, triode, and saturation); the  $V_{th}$  through DIBL; and the gate-to-channel capacitance ( $C_{gc}$ ), which loads the previous logic stage (modulating the previous stage's delay and dynamic power consumption). This means that for a given device, gate length variation will alter its propagation and rise/fall delays, its leakage power consumption, and

the delays and power consumption of its fanin cone.<sup>4</sup> Another example of CD variation is interconnect variation. Variation in the interconnect geometries modifies the capacitance and resistance of a given net. Variable interconnect capacitance affects both the coupling between nets, as well as the dynamic power consumption and delay of the gates driving those nets.

Given that CD variation affects so many circuit and device characteristics, accurately capturing this variability and developing techniques to handle it are essential to modern-day VLSI design. Typically in research, creating accurate models first involves characterizing the variability itself. In the case of CD variation, this requires capturing variations across dies, reticles, wafers, and lots. Additionally, since CD variation has a systematic component, it will also contain a certain amount of die-to-die, reticle-to-reticle, wafer-to-wafer, and lot-to-lot correlation. Characterizing this correlation and modeling it is another important aspect of capturing CD variability. Once the characteristics of CD variation are understood, accurate and efficient models can be extracted and used in timing analysis tools (discussed later in Section 1.5).

# 1.2 Threshold Voltage Variation

Another type of variation that impacts fundamental MOSFET device behavior is threshold voltage, or  $V_{th}$ , variation. The main cause of  $V_{th}$  variation is a purely probabilistic phenomenon (which is independent of other types of variation) known as random dopant fluctuation (RDF). Random dopant fluctuations occur in MOSFET devices because of the random nature of ion implantation [12-13]. However, with process scaling,

<sup>&</sup>lt;sup>4</sup> The fanin cone of a net, N, is defined as the collection of gate(s) that have net N as an output.

the number of dopants located in a MOSFET's depletion region has decreased dramatically and is only on the order of hundreds in modern-day devices [14]. This fluctuation in channel dopants typically results in ~50mV of  $V_{th}$  variation in today's MOSFETs [14-15]. Similar to gate length and CD variation, threshold voltage variation has also been studied in detail and many people have proposed variation models [14-16]. On the other hand,  $V_{th}$  variation differs significantly from CD variation in that its main component is probabilistic and random in nature (aside from its dependency on gate length, itself). Therefore,  $V_{th}$  variation due to RDF is typically modeled as a Gaussian random variable that is characterized by its mean,  $\mu$ , and standard deviation,  $\sigma$  [14-15].

Similar to CD, threshold voltage variation also influences a number of MOSFET device parameters. Both delay and leakage power are affected by changing  $V_{th}$  since drain current is dependent on threshold voltage. Delay is usually a linear or slightly super-linear function of  $V_{th}$  [17] while leakage power, on the other hand, is exponentially dependent on threshold voltage [18]. This exponential relationship between subthreshold current (and hence, leakage power) and  $V_{th}$  has become a major concern for contemporary VLSI designers. With billions of transistors in one design, leakage power consumption is now on the same order as dynamic power consumption (as illustrated in Figure 1.3), so any variation in leakage power can lead to significant variation in total circuit power. Additionally,  $V_{th}$  is often used as an optimization lever in VLSI circuits to achieve savings in either leakage power or delay [20-22]. However, with the amount of variability in  $V_{th}$  in sub-65nm devices, designers are becoming increasingly wary of using threshold voltage for optimization.

Figure 1.3. Dynamic and Static Power Density vs. Technology [19].

# 1.3 Oxide and Inter-Layer Dielectric Thickness Variation

In state-of-the-art process nodes, the equivalent gate oxide thickness,  $t_{ox}$ , is on the order of 1nm [23]. To put this in perspective, the silicon atom is ~0.2nm in diameter, which means that sub-65nm transistors have a gate oxide thickness that is *less than five silicon atoms thick*. Thus, atomic scale roughness introduced at the gate-to-oxide and oxide-to-silicon interfaces can cause significant amounts of oxide thickness variation (OTV) [24]. These variations are probabilistic in nature and can lead to variability in mobility, gate tunneling leakage current, and threshold voltage, among other parameters [24].

Aside from the gate oxide in today's devices, another type of dielectric material that experiences thickness variation is the dielectric between each metal layer in a process's metal stack. This material is often referred to as the inter-layer dielectric, or ILD. Inter-layer dielectric thickness variation is a spatially correlated (systematic) variation that is created during the Chemical-Mechanical Polishing (CMP) manufacturing step used to

planarize dielectric material. With CMP, the resulting ILD thickness is dependent on topology because regions with higher interconnect density polish slower than sparse regions. Therefore, ILD thicknesses are spatially correlated with interconnect density and the variation can be predicted [25]. Due to this fact, numerous publications have provided techniques to improve metal density uniformity and, therefore, reduce the systematic variation in ILD due to CMP [26-27].

# 1.4 Sub-100nm Induced Variation and Mobility Degradation

As the semiconductor industry continues to scale below 100nm and approaches the fundamental limits of a number of parameters (e.g., CD size using 193nm wavelength light,  $t_{ox}$ ,  $V_{th}$ ,  $V_{dd}$ , etc.), process engineering becomes increasingly complicated. Effects like well proximity and mechanical stress due to shallow trench isolation (STI) have emerged in the last decade and now contribute to device variability. Furthermore, with the decline of voltage scaling, higher effective fields are causing increasing amounts of device parameter degradation due to phenomena like hot carriers and impact ionization. In recent process nodes, the amount of mobility degradation (due to the higher effective fields) has become so high that it has motivated the semiconductor industry to explore techniques like mobility enhancement. Currently, mobility enhancement is typically achieved by adding manufacturing steps to the process which induce mechanical stress in all MOSFET channels [28-31]. In the last five years, mechanical-stress-based enhancement has rapidly emerged across the semiconductor industry and many companies are employing one or more stress-enhancement techniques in their processes [28-32]. These techniques typically involve mechanical stress sources such as embedded-SiGe (in PMOS

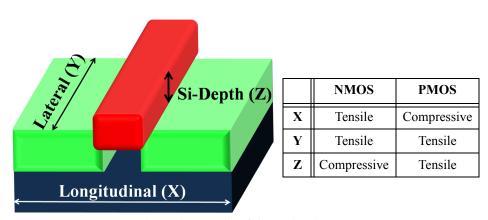

source/drain regions) [28-29,31]; compressive/tensile (dual) nitride liners [28-30]; the Stress Memorization Technique (in NMOS transistors) [30]; and PMOS/NMOS hybrid orientation [32]. By inducing the correct type of stress in a MOSFET device, as shown in Figure 1.4, the effective mass and band scattering rates of the valence and conduction bands can be modified. These changes in effective mass and band scattering can result in increased mobility, which enhances transistor performance but increases leakage current.

While stress-based mobility enhancement does reduce the performance loss due to mobility degradation, it can also be a source of variation in today's devices because the sources of mechanical stress depend on layout properties like length of diffusion (LOD), contact placement, STI width, and well proximity [33-34]. In fact, experimental results show that MOSFET saturation current can vary by as much as 15% if stress dependencies are ignored. To date, researchers have mainly taken two different approaches regarding the layout dependency of stress: they either attempt to eliminate the dependency (using manufacturing techniques) [28,35] or they attempt to exploit the dependency (using layout techniques) [36].

Figure 1.4. Preferred CMOS Device Stress Types.

# 1.5 Managing Variability in VLSI Designs

While process engineers constantly strive to mitigate the sources of variability discussed in the previous sections, the reality is that these sources are inherent to modern-day semiconductor manufacturing, so an intrinsic amount of variability is always present in manufactured IC's. Like any semi-automated manufacturing process, semiconductor manufacturing relies heavily on a number of different tools and instruments, and most of these instruments have to be calibrated frequently throughout the lifetime of a process in order to meet tolerance specifications for given parameters. It is the imperfections and non-zero tolerances of these tools that cause variability. Properties like stepper/scanner dosage and defocus, mask alignment, etch rate, etc., vary from wafer-lot to wafer-lot, wafer to wafer, reticle to reticle, and die to die. Since these tool imperfections typically affect specific stages of the manufacturing process, they are usually identified and classified by their region of impact: lot-to-lot, wafer-to-wafer, reticle-to-reticle, die-to-die, or within-die.

Furthermore, the semiconductor industry is continuing to scale device parameters, but the statistical mean of these parameters is decreasing more rapidly than the standard deviation (due to the intrinsic, probabilistic sources that cannot be eliminated or reduced). This means that the variation of a particular parameter is actually increasing with respect to its mean. Thus, over the last 10 to 20 years, IC designers have had to develop various methods of analysis and characterization which allow them to capture and reduce the variability of their designs.

Since static timing analysis (STA) [37] became the dominant timing verification method in modern VLSI design, the first techniques for managing variability involved identifying design corners and using STA to characterize circuits across various combinations of supply voltage, temperature, and process variation. At this point in semiconductor history, design corners were generally very simple since global/inter-die variations (types of variation that occurred from die to die; e.g., lot-to-lot, wafer-to-wafer, reticle-to-reticle, and within-reticle die-to-die) were more prevalent than local variations (also called intra-die or within-die variations). Therefore, circuit variation could be adequately captured by running characterization at the nominal-, best-, and worst-case process corners. At each corner, process variation for all devices in a circuit would be grouped into one category (e.g., worst-case process variation) and the STA program would then analyze the circuit given that all of its devices (and their parameters) were affected uniformly by this variation. For instance, in the worst-case design corner all device gate lengths and threshold voltages would be increased to their maximum possible value (under process variation), and then STA would characterize the circuit and report the decrease in performance.

In the last 20 years, however, local variations have grown in importance and were identified in the early 21<sup>st</sup> century as the dominant component [38-39]. During this time, corner-based analysis was labeled as "pessimistic" since the likelihood that *all* devices within a die would *all* be best- or worst-case at the same time was very small. The initial solutions to this criticism were to either run more corners or perform thousands of Monte Carlo STA analyses to determine the actual path distributions. The increased complexity incurred by these solutions was unattractive to the VLSI design community and

consequently spawned an entirely new area of research that explored propagating *statistical* distributions through a circuit graph, rather than *deterministic* delay values. This type of analysis was quickly labeled "Statistical Static Timing Analysis", or SSTA, and researchers sought to obtain more accurate, statistical representations of circuit performance [38-42].

In its simplest form, SSTA represents path delay as a weighted function of independent components [38-42]. However, since path delay is dependent on a number of varying parameters (L,  $t_{ox}$ , and  $V_{th}$ ), modeling path delay as a function of these parameters and determining the sensitivity of delay to changes in each of these parameters is an essential component of SSTA. Thus, SSTA research is not only composed of proposed algorithms and related improvements, but it also includes modeling studies on various device parameters. The models typically used within SSTA for L,  $t_{ox}$ , and  $V_{th}$  variation were briefly mentioned in Sections 1.1 through 1.3.

While SSTA, in theory, produces a more accurate representation of delay than STA and corner-based analysis, actual implementations of SSTA algorithms have not distanced themselves from STA-based techniques, due to the simplistic underlying models and the approximations involved (e.g., the approximation that the maximum of two Gaussian variables is also Gaussian). Thus, additional research and improvements in both the underlying statistical process variation models, as well as the algorithm itself are needed to warrant the replacement of current deterministic timing analysis (STA-based) flows with their statistical counterpart.

#### 1.6 Contribution of Dissertation

This dissertation focuses on two topics that are essential to the Design for Manufacturing space of integrated circuit design: CD variation and mechanical stress in silicon. Capturing, analyzing, and modeling CD variation is an important but difficult problem, as alluded to in Section 1.1. CD variation is different from  $V_{th}$ ,  $t_{ox}$ , and ILD variation because it contains *both* a systematic component that is spatially correlated, and a probabilistic (random) component that is independent of other components. Variations in the other three parameters ( $V_{th}$ ,  $t_{ox}$ , and ILD) originate from sources that are *either* probabilistic *or* systematic. This makes capturing and modeling their variability more manageable and straightforward. The CD variation research included in this dissertation began by analyzing raw CD data and characterizing the variations seen (die-to-die, reticle-to-reticle, wafer-to-wafer, etc.). Next, we used the data to compare a number of CD correlation models that had been proposed over the last decade. Prior to this work, the correlation models were presented from a conceptual perspective, but the actual implementation and accuracy in manufactured designs were not discussed.

Once the tradeoffs between correlation models were understood, we studied CD variation modeling within Statistical Static Timing Analysis (SSTA). Present-day CD models for timing analysis are error-prone because they do not capture the underlying sources of CD variability accurately. In fact, the models prior to this work grouped all CD variation (from various optical sources) across an entire standard cell library into one variable, essentially masking important, context-dependent effects that occur between transistors in a standard cell library. The CD variability research culminated in a new SSTA model that was more accurate than its predecessors.

The final DFM topic discussed in this dissertation is mechanical-stress-based mobility enhancement and its impact on circuit design. In modern processes, gate width (W), L,  $V_{th}$ , and  $t_{ox}$  are no longer the only parameters that affect a device's drain current (which impacts both performance and power consumption). The materials that process engineers now use to enhance MOSFET channel stress have their own dependence on layout (as discussed in Section 1.4), which results in device mobility variation. In order to characterize this mobility variation, this document concludes with a study that simulated, analyzed, and modeled the layout dependence of mechanical stress in silicon. After understanding the properties of mechanical stress, we proposed a novel standard cell library methodology, as well as a new timing optimization framework that combined mechanical-stress-enhancement with gate length biasing to achieve leakage power savings.

# 1.7 Organization of Dissertation

The remainder of this dissertation is organized as follows. Chapter 2 focuses on critical dimension variation. It begins by analyzing electrical linewidth measurement (ELM) data obtained from fabricated 0.13µm technology device structures. This ELM data is then used to characterize and validate a number of correlation models that have been proposed over the last decade to accurately capture CD variation. At the end of the chapter, the results show that the basic correlation models provide a simpler solution than the complex models (in terms of overhead and run-time) and only increase error by a few percent. A discussion on modeling CD in SSTA follows in Chapter 3, which concludes by proposing a new SSTA model that accurately captures CD variation and reduces the

average error in standard deviation by  $\sim$ 3X. In Chapter 4, the variability focus shifts from CD to mechanical stress. It begins with a general discussion on mechanical stress in silicon and culminates in a technique that uses stress-enhancement in conjunction with dual- $V_{th}$  assignment to reduce leakage by  $\sim$ 24%. Chapter 5 continues the discussion on mechanical stress, but deviates from the work in Chapter 4 in that it proposes a novel standard cell library technique and methodology for exploiting stress enhancement. This library methodology is used to improve delay (on average) by 11% over equivalent single- $V_{th}$  implementations, while consuming 2.5X less leakage than the dual- $V_{th}$  alternative. In Chapter 6, the stress-enhancement study is completed and a new optimization scheme that combines stress-enhancement with gate length biasing is presented. Results show that the proposed approach (stress plus gate length biasing) can optimize a single- $V_{th}$  circuit to consume 2.5X less leakage than the dual- $V_{th}$  approach with an average delay increase of only  $\sim$ 4%. Finally, Chapter 7 concludes the dissertation with a summary of the DFM work and a brief discussion of future work.

## **CHAPTER 2**

# CD VARIATION ANALYSIS AND CORRELATION MODELING IN SSTA

Static timing analysis (STA) has become a key method in the performance verification of modern chip designs and is the primary technique that abstractly incorporates manufacturing variation into design. Recently, the shortcomings of STA have become apparent with its inability to efficiently include within-die (or intra-die) variation in process parameters such as gate length, oxide thickness, and doping levels. STA, in its most common form, is a case-based analysis: designers perform simulations given best-, nominal-, and worst-case conditions and all devices are assigned the same process parameter value. However, with continued process scaling past 65nm, within-die variation has become more prominent and exhibited considerable spatial correlation. Unlike interdie variation, within-die variation tends to average out over the length of a circuit path, which reduces the variance of a circuit's delay distribution. On the other hand, the presence of significant intra-die delay variation in two converging paths increases the "maximum" (typically Clark-based) delay distribution variance. With a case-based STA analysis, it is therefore difficult to construct a guaranteed bound on the actual timing distribution of a circuit without being overly conservative.

To address this issue, "Statistical Static Timing Analysis" (SSTA) was developed and it has received considerable attention in the CAD research community in recent years [38-41]. SSTA models process parameters, such as gate length and doping concentration, as random variables and propagates these random variables through the circuit in topological fashion, analogous to the propagation in its deterministic counterpart (STA).

The first efforts in SSTA modeled all process parameter variations, as well as the propagated arrival times, as independent random variables [42]. This assumption significantly simplified the analysis but compromised accuracy. In [40,43], process parameter variations were still considered independent, but correlations between arrival times due to reconvergence in the circuit were accounted for. In the latest generation of SSTA tools [38-39,41], correlations between the process parameters of different gates in the circuit are also considered.

Of the device parameters discussed in Chapter 1, typically only gate length (or more generally, CD) and inter-layer dielectric (ILD) thickness exhibit spatial correlations. Specifically, CD variation exhibits both a die-to-die component (causing all CD in a die to vary by some common amount) and a within-die component (where devices with close proximity are more likely to have similar CD). While die-to-die correlations can be incorporated relatively easily by enumerating a small number of die conditions, the within-die (spatial) correlations increase the complexity of SSTA substantially. Accounting for these correlations requires both a model which expresses the correlations in an amenable form, as well as an accompanying SSTA algorithm that can operate on that model. Over the past decade, a number of spatial correlation models have been proposed [38-39]. The spatial correlation model proposed in [39] used a grid-based approach where

the process parameters of all gates that fell within the same grid square were assumed to be identical. The correlation between different grid squares was decomposed using "Principal Component Analysis" (PCA), and then modeled as a weighted sum of independent random variables (the principal components). A different grid-based model was developed in [38]. Here, the authors combined multiple grids with varying granularity in a tree-like fashion, where each grid square was assigned an independent random variable and each gate was associated with every grid square in which it resided. While the Quad-tree used a larger total number of random variables than the PCA approach (given the same grid granularity), less information was associated with each individual gate. One important item addressed in this chapter that was not included in [38] is a method for fitting the Quad-tree model to measured data.

In this chapter, critical dimension (CD) data obtained through electrical linewidth measurements (ELM's) of a 0.13µm test chip design is used to analyze the accuracy of a number of proposed SSTA correlation models. The test chip consists of 8 different test structures (various densities and orientations of polysilicon lines) repeated at 308 sites per field over 23 fields and 5 wafers for a total of 35,420 measurements [44]. The ELM data is used to study both the correlation characteristics of actual CD variation as well as the effectiveness of different SSTA correlation models.

The remainder of the chapter is divided as follows. Section 2.1 discusses the types of gate length variation while Section 2.2 explains the spatial correlation models in more detail. Next, Section 2.3 demonstrates our experimental data and the results obtained while characterizing the raw ELM CD data. Section 2.4 implements the spatial correlation

models using the ELM data, discusses the observed model accuracy and, finally, Section 2.5 provides a brief summary of the results.

# 2.1 Types of Gate Length Variation

Within the random component of gate length variation, we can further distinguish three types of variation: independent, die-to-die, and spatially correlated. For this section, all variables –  $\Delta L_x$  – are assumed to be zero-mean, unit-variance random variables.

#### 2.1.1 Independent

In this type of variation, each device in the design has process parameter variations that are independent from the variations in other devices. Independent variations can be modeled using independent random variables. If the gate lengths in a die are completely specified by independent variations, the length of gate i can be expressed as follows:

$$L_{g,i} = L_{nom,i} + \sigma_{ri} \Delta L_{rnd,i}, \qquad (2-1)$$

where  $L_{nom,i}$  is the nominal value of gate length for that gate,  $\Delta L_{rnd,i}$  is the random device length variation for gate i, and  $\sigma_{ri}$  is the sensitivity of gate i to changes in  $\Delta L_{rnd,i}$ .

#### 2.1.2 Die-to-Die

Die-to-die variation, on the other hand, describes variation that is common for all devices on a particular die. When only inter-die variation is considered, all gate lengths within a particular die become perfectly correlated. Therefore, the gate length of gate *i*, only considering die-to-die variation, can be expressed as:

$$L_{g,i} = L_{nom,i} + \sigma_{dd} \Delta L_{die-to-die}, \qquad (2-2)$$

where  $L_{nom,i}$  is the nominal value for gate i,  $\Delta L_{die\text{-}to\text{-}die}$  is a single random variable that is applied to all gates in the circuit, and  $\sigma_{dd}$  is the global gate sensitivity to changes in  $\Delta L_{die\text{-}to\text{-}die}$ .

### 2.1.3 Spatially Correlated

The last type of variation that we consider is spatially correlated variation. Most process variation within a single die is spatially correlated, and generally, correlation decays as a function of the distance between two points. Generally, in statistical timing analysis, the desire is to express correlation using a weighted sum of independent random variables, as shown below,

$$L_{g,i} = L_{nom,i} + \alpha_1 \Delta L_1 + \alpha_2 \Delta L_2 + \alpha_3 \Delta L_3 + \dots,$$

(2-3)

where  $\Delta L_k$  is the variation of the  $k^{th}$  component and  $\alpha_k$  is the sensitivity of the gate length to changes in the  $k^{th}$  component. By maintaining this form throughout the timing analysis, correlation information between the arrival times can be maintained. The specific values of the sensitivities and the number of components will vary between the different correlation models, which are discussed in the following subsection.

#### 2.2 Correlation Models

The five correlation models analyzed in our experiments are die-to-die (D2D), independent (also referred to as "random," which we will use for the remainder of this chapter), D2D + random, PCA, and Quad-tree.

#### 2.2.1 D2D, Random, and D2D + Random

The equations used to express the length variation of a particular gate for the random and die-to-die cases were shown in (2-1) and (2-2). Therefore, the "D2D + random" variation is a combination of (2-1) and (2-2):

$$L_{g,i} = L_{nom,i} + \sigma_{dd} \Delta L_{die-to-die} + \sigma_{ri} \Delta L_{rnd,i}, \qquad (2-4)$$

Once we understand the forms of these gate length equations, it is simple to develop sensitivity matrices, which are the input to our statistical timing tool. For instance, the sensitivity matrices for D2D, random, and D2D + random are shown in (2–5) as D, R, and DR, respectively.

$$R = \begin{bmatrix} \sigma_{r1} & 0 & 0 & \cdots & 0 \\ 0 & \sigma_{r2} & 0 & \cdots & 0 \\ 0 & 0 & \sigma_{r3} & \cdots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \cdots & \sigma_{rn} \end{bmatrix} \qquad D = \begin{bmatrix} \sigma_{dd} & \sigma_{dd} & \sigma_{dd} & \cdots & \sigma_{dd} \\ 0 & 0 & 0 & \cdots & 0 \\ 0 & 0 & 0 & \cdots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \cdots & 0 \end{bmatrix}$$

$$DR = \begin{bmatrix} \sigma_{dd} & \sigma_{dd} & \sigma_{dd} & \cdots & \sigma_{dd} \\ \sigma_{r1} & 0 & 0 & \cdots & 0 \\ 0 & \sigma_{r2} & 0 & \cdots & 0 \\ 0 & 0 & \sigma_{r3} & \cdots & 0 \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 0 & 0 & 0 & \cdots & \sigma_{rn} \end{bmatrix}$$

$$(2-5)$$

where  $\sigma_{dd}$  is the standard deviation of only the die-to-die component,  $\sigma_{ri}$  is the standard deviation of the  $i^{th}$  random component, and  $\sigma_{ri}$  is the standard deviation of the  $i^{th}$  random component when the die-to-die component has been removed.

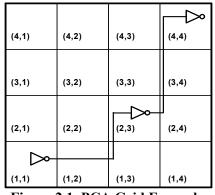

#### 2.2.2 PCA

The PCA model is a grid-based model (shown in Figure 2.1) that separates the die into n grids. Each grid is associated with a principal component, and all n principal components are independent, normal random variables with zero mean and unit variance. Because PCA deals with spatially correlated distributions, its gate length equation is based on (2-3). Thus, for some gate i, its length can be expressed as:

$$L_{g,i} = L_{nom,i} + \sum_{j} \alpha_{ij} \Delta L_{j}$$

, where  $\alpha_{ij} = \sigma_{i} v_{ij} \sqrt{\lambda_{j}}$ , (2-6)

where  $\Delta L_j$  is the  $j^{th}$  principal component and  $\alpha_{ij}$  is calculated as stated in (2–6);  $\sigma_i$  is the standard deviation associated with grid i,  $v_{ij}$  is the  $i^{th}$  element in the  $j^{th}$  eigenvector of the correlation matrix, and  $\lambda_j$  is the  $j^{th}$  eigenvalue of the correlation matrix [39]. Therefore, the sensitivity matrix, P, for the PCA model will be of the form,

$$P = \begin{bmatrix} \alpha_{1,1} & \alpha_{1,2} & \alpha_{1,3} & \dots & \alpha_{1,m} \\ \alpha_{2,1} & \alpha_{2,2} & \alpha_{2,3} & \dots & \alpha_{2,m} \\ \alpha_{3,1} & \alpha_{3,2} & \alpha_{3,3} & \dots & \alpha_{3,m} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ \alpha_{n,1} & \alpha_{n,2} & \alpha_{n,3} & \dots & \alpha_{n,m} \end{bmatrix},$$

(2-7)

where each grid is associated with one column and one row (and  $m \le n$ ).

Figure 2.1. PCA Grid Example.

#### 2.2.3 Quad-Tree

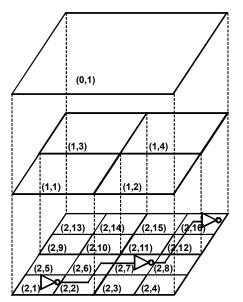

Quad-tree is another grid model that utilizes various grid levels combined in a tree-like structure – shown in Figure 2.2 – to include spatial correlation. The Quad-tree has l+1 levels, and each level, k, contains  $2^k$ -by- $2^k$  squares [38]. Levels are numbered where "level 0" represents the top level and l is bottommost level. Level 0 only has one grid, while level k has  $4^k$  grids. All of the regions at different levels of the tree are associated with an independent random variable that includes part of the total intra-die variation. For a gate located within bottommost region r, the associated variation is a sum of all the intra-die variation components that intersect region r as you progress up the tree (e.g., in Figure 2.2 grid (2,13) intersects grids (1,3) and (0,1)). For example, the equation for gate length for the gate that lies in grid (2,7) is,

$$L_{g,(2,7)} = L_{nom,(2,7)} + \Delta L_{(2,7)} + \Delta L_{(1,2)} + \Delta L_{(0,1)}.$$

(2-8)

Thus, the sensitivity matrix is similar to the PCA matrix in (2–7), where all grids (including all levels of the tree) are given one row in the sensitivity matrix, but, in the

Figure 2.2. Quad-tree Model Example.

Quad-tree matrix, only the bottommost grids are assigned to individual columns. All grids that do not intersect with a particular bottommost grid (assigned column i in the matrix) will have a zero-sensitivity value at its row j in the matrix (i.e., element [j,i] equals zero). Equation (2–9) below contains the general form for a 3-level (l=2) Quad-tree sensitivity matrix. Specific grids are shown in parentheses and there are a total of 16 ( $4^l=16$ ) columns and 21 rows (1 "level 0" row + 4 "level 1" rows + 16 "level 2" rows). It is interesting to note that while this matrix has a larger number of elements compared to the equivalent PCA matrix ( $16 \times 21 = 336$  compared to  $16 \times 16 = 256$ ), the majority of the 336 elements are 0, making the Quad-tree version a sparse matrix.

$$Q = \begin{bmatrix} \alpha_{(0,1)} & \alpha_{(0,1)} \\ \alpha_{(1,1)} & \alpha_{(1,1)} & 0 & 0 & \dots & 0 & 0 & 0 & 0 \\ 0 & 0 & \alpha_{(1,2)} & \alpha_{(1,2)} & \dots & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & \dots & \alpha_{(1,3)} & \alpha_{(1,3)} & 0 & 0 \\ 0 & 0 & 0 & 0 & \dots & 0 & 0 & \alpha_{(1,4)} & \alpha_{(1,4)} \\ \alpha_{(2,1)} & 0 & 0 & 0 & \dots & 0 & 0 & 0 & 0 \\ 0 & \alpha_{(2,2)} & 0 & 0 & \dots & 0 & 0 & 0 & 0 \\ 0 & 0 & \alpha_{(2,3)} & 0 & \dots & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & \alpha_{(2,4)} & \dots & 0 & 0 & 0 & 0 \\ \vdots & \vdots & \vdots & \vdots & \ddots & \vdots & \vdots & \vdots & \vdots \\ 0 & 0 & 0 & 0 & \dots & \alpha_{(2,13)} & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & \dots & 0 & \alpha_{(2,14)} & 0 & 0 \\ 0 & 0 & 0 & 0 & \dots & 0 & 0 & \alpha_{(2,15)} & 0 \\ 0 & 0 & 0 & 0 & \dots & 0 & 0 & 0 & \alpha_{(2,16)} \end{bmatrix}$$

As stated in the introduction, the authors in [38] did not explain how to fit actual data to the Quad-tree model. After examining several different algorithms, we derived a Quad-tree fit that was efficient, simple and provided good accuracy. Prior to fitting, we

discovered that closely matching the die-to-die component was very important to the overall accuracy. Therefore, this fitting method was designed to accurately capture the die-to-die component first with zero error. The pseudo-code for the fitting algorithm is as follows:

| Algorithm 2–1                | QUADTREE_FIT( $L$ ) // Correlation fit for quad-tree                      |  |  |  |  |

|------------------------------|---------------------------------------------------------------------------|--|--|--|--|

|                              | //L = number of levels                                                    |  |  |  |  |

| 1: $i_L = 0$                 | $//i_L$ = index of level in quad-tree                                     |  |  |  |  |

| 2: while $(i_L \cdot$        | < L)                                                                      |  |  |  |  |

| 3: $i_G = 1$                 | $//i_G = $ current grid number                                            |  |  |  |  |

| 4: <b>while</b> ( <i>i</i> , | $_G$ < $4^{i_L}$ )                                                        |  |  |  |  |

| 5: Comp                      | oute grid mean, $\mu_i$                                                   |  |  |  |  |

| 6: Comp                      | Computer the standard deviation, $\sigma_{u,i}$ , of $\mu_i$ for all dies |  |  |  |  |

| 7: Enter                     | Enter $\sigma_{u,i}$ into sensitivity matrix                              |  |  |  |  |

| 8: end whi                   | le                                                                        |  |  |  |  |

| 9: end while                 |                                                                           |  |  |  |  |

Essentially, the fitting method starts at level 0 and traverses down the tree. The method stops at each level,  $i_L$ , and determines the number of grids that comprise it  $(4^{i_L})$  for grid level  $i_L$ ). Next, every grid on the particular level (all  $i_G$ ,  $i_G < 4^{i_L}$ ) is parsed and the grid mean,  $\mu_i$ , is calculated. This procedure is repeated across all dies, reticles, and wafers. Finally, the standard deviation of grid mean,  $\sigma_{\mu,i}$ , is calculated for each grid and then entered into the corresponding row of the sensitivity matrix (as in equation 2–9).

### 2.3 Experimental Data and Analysis

As stated earlier, our analysis is based on 0.13µm ELM data taken from horizontal polysilicon lines (which were manufactured with typical resolution enhancement techniques such as optical proximity correction) [44]. We investigated 5 different wafers that each contained 23 fields, and each field included 308 measurement points – 14 points

in the horizontal direction and 22 points in the vertical direction. Individual measurement points were spaced horizontally by 2.19mm and vertically by 1.14mm.

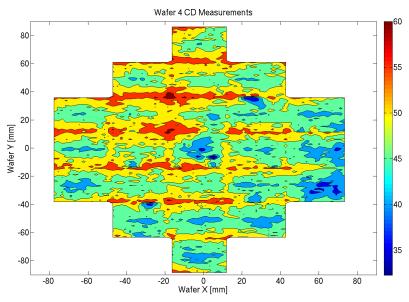

An example of one wafer of ELM CD measurements is illustrated in Figure 2.3. As shown, not only do the measurements vary across the wafer (the lower right corner has smaller CD values than the upper right corner), but specific patterns occur within the reticles (the upper and lower boundaries of the field have a higher CD than the center points). For these 5 wafers, we divided the reticles into various die sizes in order to investigate the effect that die size had on CD variation. Initially, we diced a reticle into 4 die, (a 2-die x 2-die configuration where each die was approximately 15mm x 13mm). Then, we examined a number of characteristics including the mean, standard deviation, and correlation of all the dies.

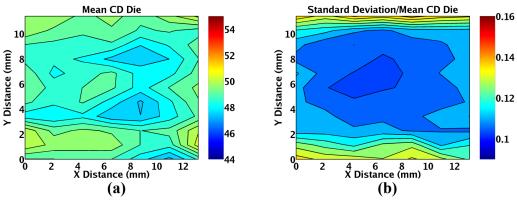

The mean values for each data point in a die from the 2x2 reticle configuration are shown in Figure 2.4 (a). From this type of figure, certain trends became clear. For example, in Figure 2.4 (a) the typical die had lower values in the center of the die, and the

Figure 2.3. Wafer CD Measurement Contour Plot.

CD values increased toward the edges of the die. In Figure 2.4 (b), the standard deviation over mean is plotted for the same reticle configuration. Again, the figure shows the edge effects in the die. To contrast the 2x2 diced reticle, we have also included the equivalent plots for the 4x4 reticle configuration in Figure 2.5.

On average, the 4x4 dicing merely divided the 2x2 case into two-by-two grids of its own. Thus, it can be seen that the 4x4 mean plot is a quarter of the 2x2 plot, with the spot effect seen in the 2x2 case lying on the inner portion of the 4x4 die. Similarly, the standard-deviation-over-mean plot also resembles a quarter of the 2x2 case, with the lower deviation occurring at the top edge of the typical 4x4 die. It should be noted,

Figure 2.4. (a) Mean CD Values for Die (2x2 reticle dice) (b) Standard Deviation/Mean for Die (2x2 reticle dice).

Figure 2.5. (a) Mean CD Values for Die (4x4 reticle dice) (b) Standard Deviation/Mean for Die (4x4 reticle dice).

however, that the variation structure is quite different between the 2x2 and 4x4 diced cases.

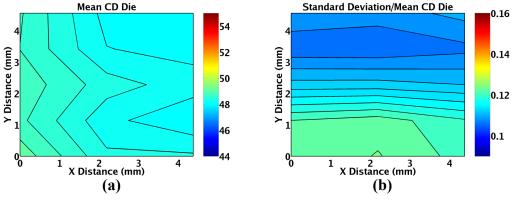

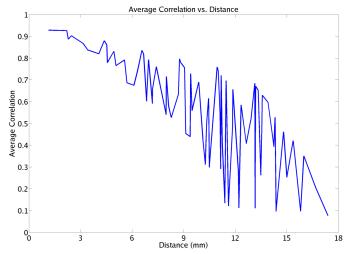

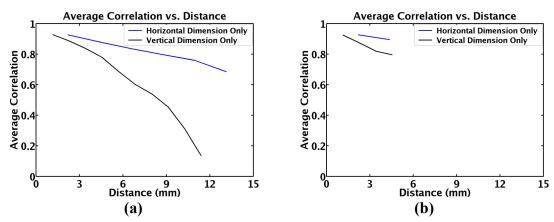

In addition to the mean and standard deviation, the correlation was also extracted for different size die. Plotted in Figure 2.6 is the average correlation versus separation distance. It is easily identifiable that this function was not monotonically decreasing with distance, x. On the contrary, we saw many distinctive peaks where correlation fell and then rose again, sharply, at a particular distance. From this investigation, it became clear that correlation versus horizontal distance was different than the correlation versus vertical distance (i.e., correlation was typically stronger along a particular axis). This is confirmed in Figure 2.7 (a) where correlation versus distance is plotted separately for the horizontal and vertical directions.

As shown in Figure 2.7, correlation in the x-direction was actually stronger than correlation in the y-direction. We hypothesized that the reason behind this phenomenon was that during fabrication, the lithographic stepper scanned across the reticle and only printed a narrow slit in the x-direction while the entire y-dimension was printed. Thus, vertically, the reticle saw all of the variation in the lithographic system (particularly lens aberrations) but as the stepper scanned across x, the variation did not change significantly (e.g., the same part of the lens exposed all x-locations in a field), creating higher correlation in x. Figure 2.7 (b) also shows similar behavior for the smaller die size.

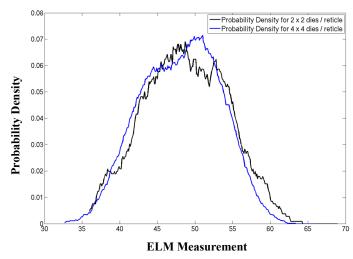

Lastly, we plotted probability density functions for each point within a die. One example is shown in Figure 2.8, which is a plot of point 76 within the 15mm x 13mm die (2x2 reticle) and point 14 within the 8mm x 6mm die (4x4 reticle).

Figure 2.6. Average Correlation vs. Distance (2x2 reticle).

Figure 2.7. Average Correlation vs. Distance (1-dimension only).

(a) 2x2 reticle dice (b) 4x4 reticle dice

### 2.4 Variation Modeling and SSTA Results

After analysis of the experimental data, we used the data to test the accuracy of different correlation models and their associated SSTA runs. For our test circuit, we utilized the behavioral Verilog from an industrial 15,000 gate implementation of a Viterbi decoding circuit. Then Synopsys's *Design Compiler* was used to synthesize the design and balance the paths. Lastly, the test circuit was placed and routed using Cadence's *Silicon Ensemble*, in order to generate the placement information needed by the SSTA tool. The

Figure 2.8. PDF Plot for ELM Measured CD.

authors would like to note that we did not actually layout the Viterbi decoder. It was merely used as a simulation benchmark to test the accuracy of our spatial correlation models.

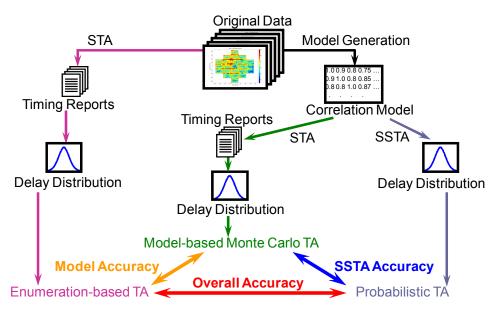

The general flow of our analyses is illustrated in Figure 2.9. There are effectively three branches in the flow. All branches start with the same wafer data. Then, in the first case (the left branch), we perform static timing analysis on all *N* die, where,

$$N = X \times Y \times 23 \times 5, \tag{2-10}$$

X is the number of die per reticle in the horizontal direction, and Y is the number of die per reticle in the vertical direction (23 represents the number of reticles and 5 represents the number of wafers). From deterministic STA, we obtain N timing reports from which we can extract a final distribution for critical path delay of the circuit. We consider this the golden analysis of circuit delay (since it is based directly on the underlying measured data) and refer to it as the "Enumeration-based Timing Analysis" for the remainder of the chapter.

Figure 2.9. Timing Analyses Flow.

The two paths on the right both begin with a model generation step which involves fitting one of the 5 discussed CD models to the data. The two paths then diverge. The center path (referred to as "Model-based Monte Carlo") essentially follows a flow similar to the "Enumeration-based" timing analysis (TA). The only difference between the two paths is that the STA in the Model-based Monte Carlo TA is performed on random samples that were generated using the fitted correlation models, whereas the Enumeration-based TA uses the measured ELM data, directly. Finally, the right-most path, called "Probabilistic TA," performs SSTA on the fitted correlation model.

In the end, implementing this TA flow gave us three outputs available for comparison. By comparing the Enumeration-based TA with the Model-based Monte Carlo TA, we were able to determine the inherent accuracy of each correlation model. Similarly, by comparing the Probabilistic TA distribution to the Model-based Monte Carlo TA, the accuracy of SSTA, itself, was determined. Lastly, we computed the overall accuracy of

Table 2.1. Enumeration-Based, Model-Based, and Probabilistic TA Results.

| Analysis Method               |                   | μ (ns) | % Error from Enum. | σ (ns) | % Error from Enum. |

|-------------------------------|-------------------|--------|--------------------|--------|--------------------|

| Enumeration-based TA          |                   | 2.049  | _                  | 0.152  | _                  |

| Model-based<br>Monte Carlo TA | Die-to-Die        | 1.934  | 5.623%             | 0.139  | 8.326%             |

|                               | Random            | 2.087  | 1.849%             | 0.058  | 62.12%             |

|                               | D2D + Random      | 2.006  | 2.117%             | 0.146  | 3.784%             |

|                               | PCA               | 2.033  | 0.800%             | 0.151  | 0.428%             |

|                               | 2-level Quad-tree | 2.006  | 2.111%             | 0.159  | 4.556%             |

| Probabilistic TA              | Die-to-Die        | 1.945  | 5.108%             | 0.146  | 3.789%             |

|                               | Random            | 2.130  | 3.934%             | 0.040  | 73.70%             |

|                               | D2D + Random      | 2.006  | 0.769%             | 0.146  | 3.793%             |

|                               | PCA               | 2.071  | 1.043%             | 0.148  | 2.694%             |

|                               | 2-level Quad-tree | 2.061  | 0.577%             | 0.157  | 3.198%             |

using each correlation model within SSTA by directly comparing the Enumeration-based TA to the Probabilistic TA.

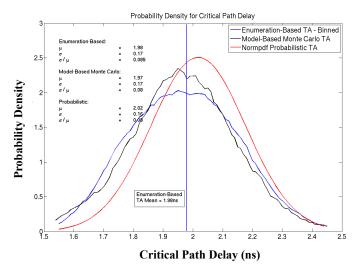

Table 2.1 includes the results of our TA verification flow. All three TA flow outputs are reported. Additionally, Figure 2.10 shows sample probability density plots for three of the models, including the Enumeration-based and two PCA models (Model-based and Probabilistic). All of the curves in Figure 2.10 are from the 4x4 reticle dice experiment.

When examining the Model-based Monte Carlo TA results in Table 2.1, it was clear that even the simple die-to-die models only deviated from the Enumeration-based results by less than 10%. The random model was more accurate than die-to-die with regards to the mean, but it produced considerable amounts of error in standard deviation. This was due to the fact that die-to-die variations tend to produce circuit delay variation (increasing σ) whereas random and/or spatially correlated variations tend to average out over circuit paths and, consequently, shift the mean value of circuit delay. Since the random correlation model did not model die-to-die variation, it incurred a significant error in the standard deviation of circuit delay. The "Die-to-die + random" correlation model,

Figure 2.10. Probability Density Plots for 3 Models (Enumeration-Based, PCA Model-Based Monte Carlo, and PCA Probabilistic).

however, improved on both die-to-die and random because it modeled both components. Overall, after analyzing the simple models, it was apparent that both random and die-to-die variation were the two most important components of total variation and, of the two, die-to-die was substantially more significant.

Table 2.1 also shows the two complex spatial correlation models for Model-based Monte Carlo TA. The error in PCA was found to be negligible (falling below 1%) while the Quad-tree error was somewhat higher. The fact that the PCA correlation model outperformed the Quad-tree for Model-based Monte Carlo TA was not surprising since it utilized a much larger number of principal components to fit the measured data.

One of the more surprising results was that when we examined the error of the Probabilistic TA for the 5 models, PCA and Quad-tree reported very comparable accuracy, despite the fact that PCA reported better results for Model-based Monte Carlo TA. Both were less than 1% away from the mean of the Enumeration-based run, and both had  $\sim 3\%$  error in standard deviation. Hence, the PCA model may have been more accurate than the

Quad-tree model, but the execution of the PCA-based SSTA incurred more error than the Quad-tree-based SSTA, making the final results approximately equal. We saw this behavior consistently across a number of different tests and postulate that this behavior was the result of the large number of independent components associated with each gate in PCA. The large number of independent components allowed PCA to obtain a better fit of the data, but also made SSTA's task more difficult and introduced a higher error in the Clark-based "MAX" function that was performed inside the SSTA tool. Finally, perhaps the most noteworthy fact gleaned from this data was that the simple "D2D + random" model performed nearly as well on the Probabilistic TA flow as the more complex models.

### 2.4.1 Model Accuracy vs. Die Size

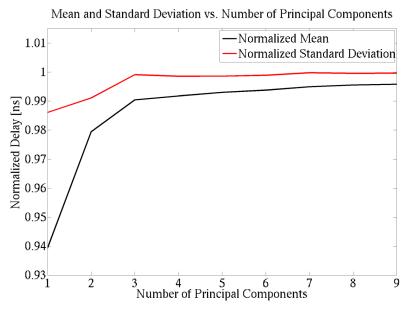

Next, we studied the affect that die size had on the models and SSTA accuracies. The results are shown in Table 2.2. The cells in the first row contain the Enumeration-based results for mean and standard deviation, while the rest of the table displays the percent deviation from the Enumeration-based TA. In general the D2D, D2D + random, and Quad-tree models became more accurate (in terms of overall accuracy) as the dies decreased in size. From a D2D perspective, this was intuitive because by shrinking the die, more of the variation became inter-die variation. Furthermore, since we fit the Quad-tree to the die-to-die variation first, it followed the same trend. The random model, on the other hand, became less accurate as die size decreased because it modeled all within-die variation as uncorrelated, which was incorrect since the dies actually became more strongly correlated after shrinking, due to the inverse relationship between correlation and distance. The last model, PCA, showed a non-monotonic accuracy trend with decreasing

Table 2.2. Model vs. Die Size.

| Run Type                   |                      | 23mmx19mm<br>(1.2x1.2 reticle dice) |         | 15mmx13mm<br>(2x2 reticle dice) |         | 8mmx6mm<br>(4x4 reticle dice) |         |

|----------------------------|----------------------|-------------------------------------|---------|---------------------------------|---------|-------------------------------|---------|

|                            |                      | μ (ns)                              | σ (ns)  | μ (ns)                          | σ (ns)  | μ (ns)                        | σ (ns)  |

| Enumeration                | Enumeration-based TA |                                     | 0.156   | 2.049                           | 0.152   | 1.975                         | 0.167   |

|                            | Die-to-Die<br>(D2D)  | 4.176%                              | 6.733%  | 5.281%                          | 2.138%  | 2.407%                        | 2.405%  |

|                            | Random               | 2.136%                              | 68.176% | 1.772%                          | 62.396% | 4.545%                        | 51.130% |