# Low Power, Integrated, Thermoelectric Micro-coolers for Microsystems Applications

By

#### Andrew John Gross

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2010

#### **Doctoral Committee:**

Professor Khalil Najafi, Chair Professor Massoud Kaviany Professor Ctirad Uher Professor Kensall D. Wise Assistant Research Scientist Rebecca L Peterson

## **Dedication**

To Kelsey,

Thank you for all your love, help and support.

### **Table of Contents**

| Dedicatio   | on                                            | . ii |

|-------------|-----------------------------------------------|------|

| List of Fig | guresv                                        | iii  |

| List of Ta  | bles                                          | xi   |

| Chapter 1   | l Introduction                                | . 1  |

| 1.1 Ap      | oplications for micro cooling                 | 3    |

| 1.1.1       | Analog Electronics                            | 4    |

| 1.1.2       | Infrared (IR) Detectors                       | 5    |

| 1.1.3       | Resonant MEMS and gyroscopes                  | 6    |

| 1.1.4       | Other Applications                            | 7    |

| 1.1.5       | Summary of Applications                       | 8    |

| 1.2 Co      | omparison of Cooling Methods                  | 8    |

| 1.2.1       | Macro-scale coolers and refrigerators         | 9    |

| 1.2.2       | Previous work in Micro-coolers                | 13   |

| 1.3 Sc      | ope of Research                               | 16   |

| 1.4 Co      | ontributions                                  | 18   |

| 1.5 Th      | nesis organization                            | 18   |

| Chapter 2   | 2 Thermoelectric Materials                    | 20   |

| 2.1 In      | troduction                                    | 20   |

| 2.2 Th      | nermal and Thermoelectric Material Properties | 20   |

| 2      | 2.1  | Thermal conductivity                                         | 20 |

|--------|------|--------------------------------------------------------------|----|

| 2      | 2.2  | Joule heating                                                | 22 |

| 2.     | 2.3  | The Peltier Effect                                           | 22 |

| 2      | 2.4  | The Seebeck effect                                           | 23 |

| 2      | 2.5  | Thomson                                                      | 24 |

| 2      | 2.6  | Thermoelectric Figure of Merit                               | 25 |

| 2.3    | Bu   | lk Thermoelectric Materials                                  | 26 |

| 2      | 3.1  | Metals                                                       | 26 |

| 2      | 3.2  | Semiconductors                                               | 27 |

| 2.4    | Th   | in-film Materials                                            | 32 |

| 2.     | 4.1  | Poly-silicon                                                 | 32 |

| 2.     | 4.2  | Bismuth Telluride and Antimony Telluride                     | 33 |

| 2.     | 4.3  | Super-lattice Thermoelectrics                                | 37 |

| 2.5    | Ma   | iterials Produced at the University of Michigan              | 37 |

| 2.     | 5.1  | Co-evaporation Process and System                            | 38 |

| 2.     | 5.2  | Material Properties and characterization                     | 43 |

| 2.6    | Su   | mmary                                                        | 49 |

| Chapte | er 3 | Modeling Thermoelectric Coolers                              | 51 |

| 3.1    | Th   | e Ideal Thermocouple                                         | 53 |

| 3.2    |      | n-Ideal Thermocouple                                         |    |

| 3.3    |      | ıltistage Cooling                                            |    |

| 3.3    | 3.1  | Ideal 2-Stage Cooler                                         |    |

| 3.:    | 3.2  | Sequential Current Optimization (Fixed Stage-1 Current)      |    |

|        | 3.3  | Simultaneous Current Optimization (Variable Stage-1 Current) |    |

|        | 3.4  | Single Current Optimization                                  |    |

|        |      | =                                                            |    |

| 3.3      | 3.5  | Parasitic Effects                                                 | 80   |

|----------|------|-------------------------------------------------------------------|------|

| 3.3      | 3.6  | Ultimate Cooling Limits                                           | 85   |

| 3.4      | Pre  | ediction and Comparison to 2-D FEM                                | 86   |

| 3.4      | 4.1  | 1-D Model Performance Predictions                                 | 87   |

| 3.4      | 4.2  | 2-D FEM Model                                                     | 89   |

| 3.5      | Su   | mmary                                                             | 91   |

| Chapte   | er 4 | Fabrication Process 1 – Designs and Results                       | 93   |

| 4.1      | Int  | roduction                                                         | 93   |

| 4.2      | Str  | ructure                                                           | 93   |

| 4.2      | 2.1  | Planar vs. Vertical Design                                        | 93   |

| 4.2      | 2.2  | Satisfying Thermal Requirements (cite other planar coolers fabric | ated |

| on membr | rane | s)                                                                | 97   |

| 4.2      | 2.3  | Satisfying Structural Requirements                                | 101  |

| 4.3      | Fal  | brication Process                                                 | 103  |

| 4.3      | 3.1  | Processing Challenges                                             | 106  |

| 4.3      | 3.2  | Detailed Fabrication Process                                      | 114  |

| 4.4      | 5-8  | Stage Coolers                                                     | 118  |

| 4.4      | 4.1  | Specifications                                                    | 118  |

| 4.4      | 4.2  | Results and Discussion                                            | 121  |

| 4.5      | 6-5  | Stage Coolers                                                     | 126  |

| 4.5      | 5.1  | Results and analysis                                              | 128  |

| 4.5      | 5.2  | Modified 6-Stage Cooler (Version 2)                               | 130  |

| 4.5      | 5.3  | Test Results                                                      | 134  |

| 4.6      | 1-5  | Stage cooler                                                      | 136  |

| 4.7      | Pro  | ocess and Design Shortcomings                                     | 142  |

| 4.7.1     | Parasitic Thermal Conduction                    | 142 |

|-----------|-------------------------------------------------|-----|

| 4.7.2     | Contact Resistance                              | 143 |

| 4.7.3     | Die Attachment and support                      | 144 |

| 4.8 Su    | mmary                                           | 144 |

| Chapter 5 | Single Wafer Process                            | 145 |

| 5.1 In    | troduction                                      | 145 |

| 5.2 De    | evice Overview                                  | 147 |

| 5.3 Pr    | ocess description                               | 151 |

| 5.3.1     | Process-related challenges and design decisions | 153 |

| 5.3.2     | Full Process Flow                               | 154 |

| 5.4 Th    | ne 4 stage device                               | 160 |

| 5.4.1     | Current drive mechanism                         | 161 |

| 5.4.2     | Structure and process simplification            | 165 |

| 5.4.3     | Device parameters                               | 166 |

| 5.4.4     | Performance                                     | 168 |

| 5.5 1,    | 2, 3, and 5-Stage coolers                       | 173 |

| 5.5.1     | Parameters                                      | 173 |

| 5.5.2     | Simulated Performance                           | 175 |

| 5.5.3     | Fabrication issues                              | 179 |

| 5.5.4     | Measured Performance and Material Analysis.     | 180 |

| 5.5.5     | Revised performance predictions                 | 181 |

| 5.6 Di    | e attachment                                    | 182 |

| 5.6.1     | TLP bonding                                     | 184 |

| 5.6.2     | Target device alignment and transfer            | 186 |

| 5.6.3     | Proof of Concept                                | 186 |

| 5.7    | Packaging                       | 188 |

|--------|---------------------------------|-----|

| 5.8    | Summary                         | 189 |

| Chapto | er 6 Conclusion and Future Work | 190 |

| 6.1    | Conclusion                      | 190 |

| 6.2    | Future work                     | 193 |

| 6.2    | 2.1 Thermoelectric Materials    | 193 |

| 6.2    | 2.2 Structure and Process       | 194 |

| 6.3    | Projected Long Term Results     | 195 |

| Refere | ences                           | 196 |

# **List of Figures**

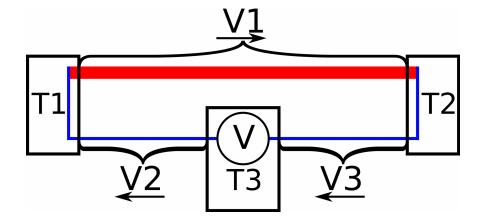

| Figure 2.1: The material being measured (red) generates voltage V1= $\alpha_1$ (T1-T2).                                             |

|-------------------------------------------------------------------------------------------------------------------------------------|

| However this cannot be directly measured because the test leads produce voltages                                                    |

| $V_2 = \alpha_2 (T_3 - T_1)$ and $V_3 = \alpha_2 (T_2 - T_3)$ . The total measured voltage is $V = V1 + V2 + V3$ .                  |

| Where $\alpha_1$ is the Seebeck coefficient of the material being investigated, and $\alpha_2$ is the                               |

| the Seebeck coefficient of the test leads. $\alpha_1$ can only be determined if $\alpha_2$ is known.                                |

|                                                                                                                                     |

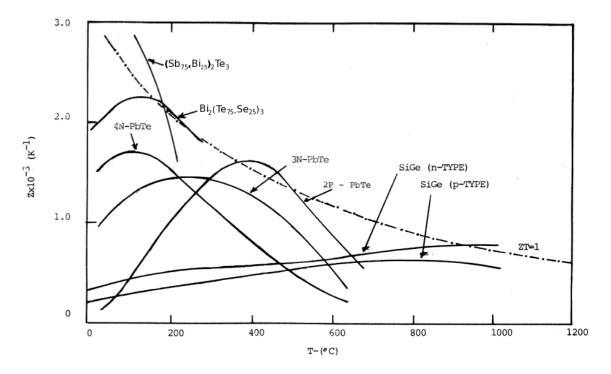

| Figure 2.2: A comparison TE material figures of merit between 0 C and 1200 C. It is                                                 |

| important to note that most materials do not have a high enough Z to exceed ZT=1                                                    |

| over a wide temperature range, if at all. Below 200 C tertiary compounds of                                                         |

| (Bi,Sb) <sub>2</sub> Te <sub>3</sub> and Bi <sub>2</sub> (Te,Se) <sub>3</sub> provide the highest figures of merit. Reproduced from |

| [48] (annotations edited for readability)                                                                                           |

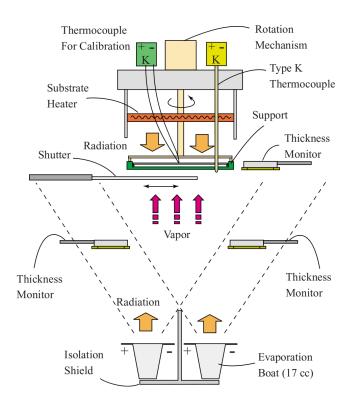

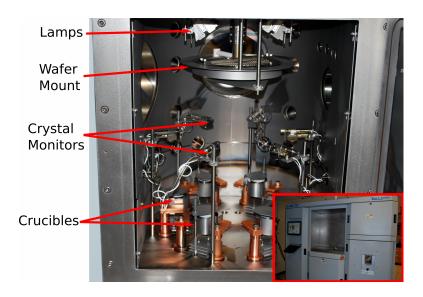

| Figure 2.3: Schematic of a two-source co-evaporation system. They system is housed in                                               |

| a high vacuum chamber and includes two crucibles, a crystal thickness monitor for                                                   |

| each of the crucibles, and a third monitor near the wafer surface. The temperature of                                               |

| the substrate can be controlled and the substrate can be rotated (graphic reproduced                                                |

| from Huang et al [74])                                                                                                              |

| Figure 2.4: The original TE deposition system                                                                                       |

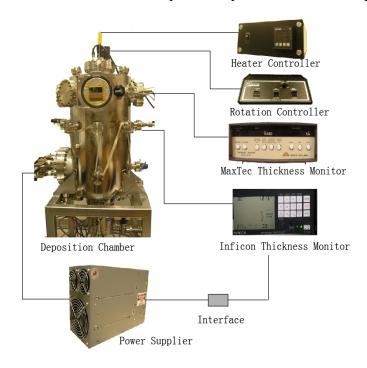

| Figure 2.5: TE deposition system from Kurt J. Lesker Company. The main picture shows                                                |

| the interior of the deposition chamber. The inset shows the exterior of the tool 41                                                 |

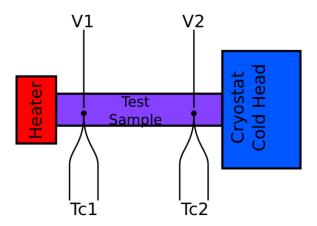

| Figure 2.6: Schematic of a Seebeck measurement apparatus                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------|

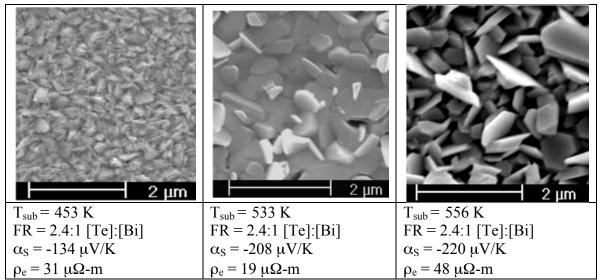

| Figure 2.7: Bismuth telluride films deposited at 453 K, 533 K, and 556 K, using a flux                                                     |

| ratio of 2.4:1 along with measured thermoelectric properties. Images were                                                                  |

| reproduced from [74]                                                                                                                       |

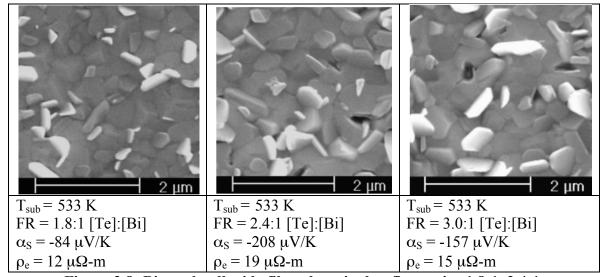

| Figure 2.8: Bismuth telluride films deposited at flux ratios 1.8:1, 2.4:1, and 3.0:1 at a                                                  |

| temperature of 533 K, along with measured thermoelectric properties of the films.                                                          |

| Images were reproduced from [74]                                                                                                           |

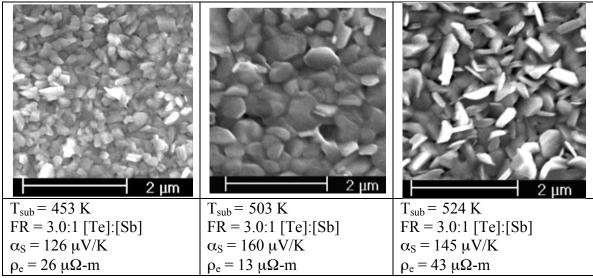

| Figure 2.9: Antimony telluride Films deposited at 453 K, 503 K, and 524 K, using a flux                                                    |

| ratio of 2.4:1 along with measured thermoelectric properties. Images were                                                                  |

| reproduced from [74]47                                                                                                                     |

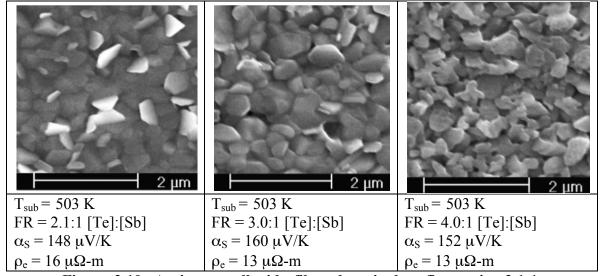

| Figure 2.10: Antimony telluride films deposited at flux ratios 2.1:1, 3.0:1, and 4.0:1 at a                                                |

| temperature of 503 K, along with measured thermoelectric properties of the films.                                                          |

| Images were reproduced from [74]                                                                                                           |

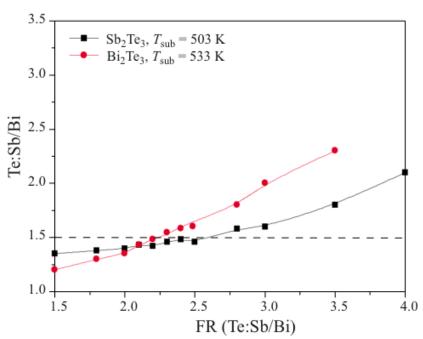

| Figure 2.11: Atomic ratio of Te:Bi and Te:Sb vs. the flux ratio used during deposition.                                                    |

| Image reproduced from [74]                                                                                                                 |

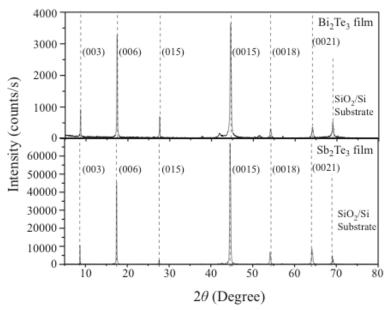

| Figure 2.12: X-ray diffraction spectra for Bi <sub>2</sub> Te <sub>3</sub> and Sb <sub>2</sub> Te <sub>3</sub> . The dashed lines are from |

| the spectra of powdered, single-crystal Bi <sub>2</sub> Te <sub>3</sub> and Sb <sub>2</sub> Te <sub>3</sub> . Image reproduced from        |

| [74]49                                                                                                                                     |

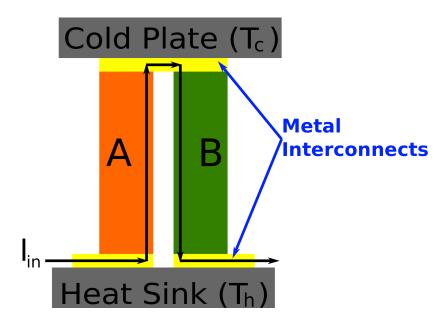

| Figure 3.1: Illustration of a basic thermocouple arrangement for cooling                                                                   |

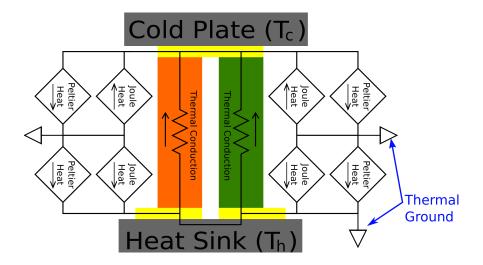

| Figure 3.2: Heat flow in an ideal thermocouple, when it is used as a cooler. The heat                                                      |

| flows are shown as an electrical equivalent thermal circuit, over a diagram of the                                                         |

| thermocouple                                                                                                                               |

| Figure 3.3: The generalized cooling curve of an ideal thermocouple with fixed T <sub>c</sub> . The                    |

|-----------------------------------------------------------------------------------------------------------------------|

| graph is plotted from Eqn. 3.10 and shows $\Delta T/\Delta T_{max}$ plotted versus $I/I_{opt}$                        |

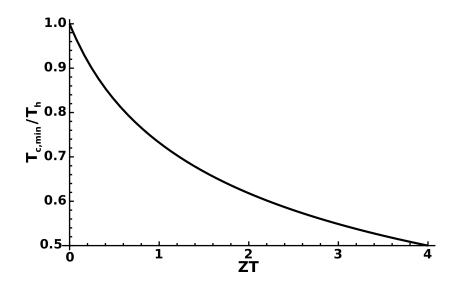

| Figure 3.4: The effect of ZT on cooling. The graph is plotted from Eqn. 3.14 and shows                                |

| the normalized minimum temperature of a single, ideal thermocouple plotted versus                                     |

| ZT59                                                                                                                  |

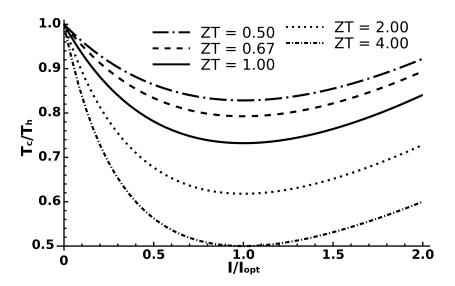

| Figure 3.5: The effect of current input on the cold side temperature of a single, ideal                               |

| thermocouple. The graph is plotted from Eqn. 3.11 and shows normalized                                                |

| temperature of a single thermocouple plotted versus normalized current input for                                      |

| several values of ZT                                                                                                  |

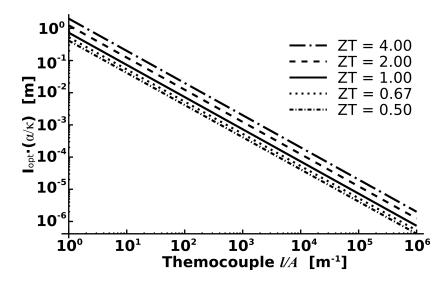

| Figure 3.6: The effect of aspect ratio on the optimum current of a single, ideal                                      |

| thermocouple. The optimum current, normalized with respect to material properties                                     |

| is plotted from Eqn. 3.15 versus aspect ratio for several values of ZT61                                              |

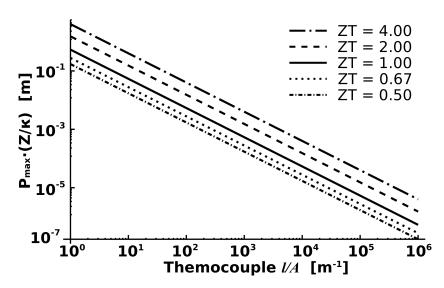

| Figure 3.7: The effect of aspect ratio on power consumption of single, ideal                                          |

| thermocouple. Power dissipation, normalized with respect to specific material                                         |

| properties, is plotted from Eqn. 3.17 versus aspect ratio for several different values                                |

| of ZT62                                                                                                               |

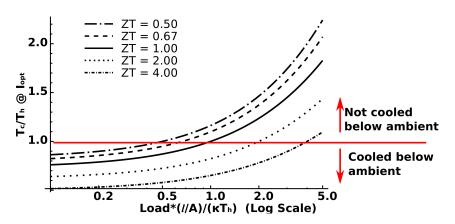

| Figure 3.8: The effect of a load on the cooling of a single, ideal thermocouple. The                                  |

| normalized minimum temperature is plotted versus load, normalized with respect to                                     |

| aspect ratio, specific material properties, and $T_h$ (see Eqn. 3.19). Several different                              |

| values of ZT are plotted64                                                                                            |

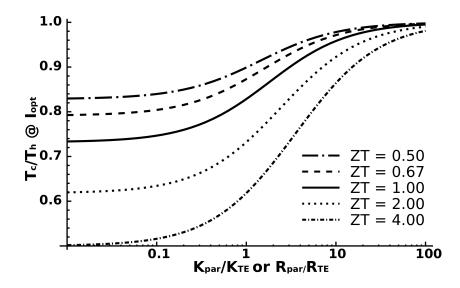

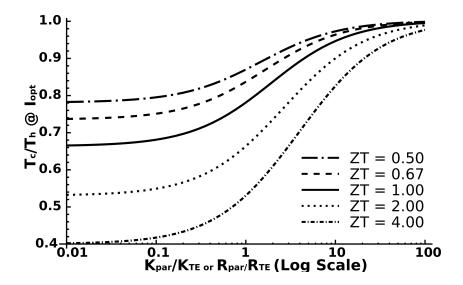

| Figure 3.9: The effect of parasitic thermal conductance on cooling for a single, ideal                                |

| thermocouple. The normalized minimum temperature is plotted versus the $K_{\mbox{\tiny par}}\!/\!K_{\mbox{\tiny TE}}$ |

| or $R_{\text{TE}}/R_{\text{TE}}$ (see Eqn. 3.25) where $K_{\text{TE}}=\kappa A/l$ and $R_{\text{TE}}=\rho l/A$        |

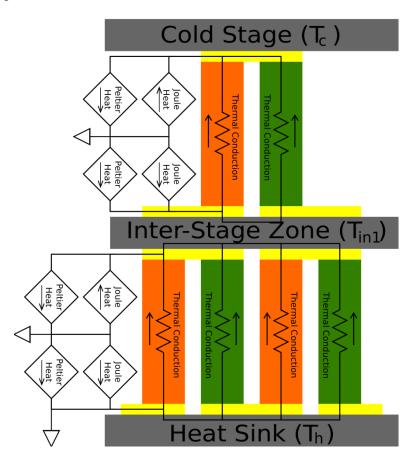

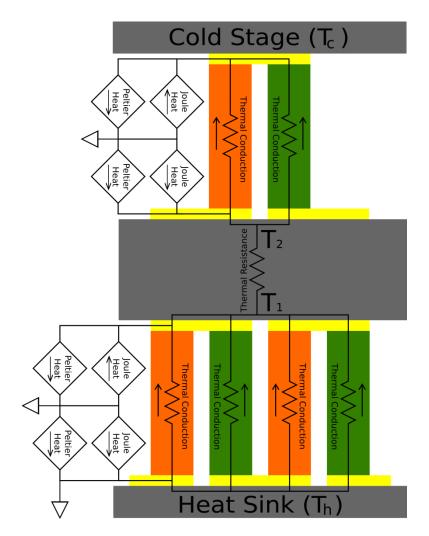

| Figure 3.10: Heat flow schematic for a 2-stage cooler                                                     |

|-----------------------------------------------------------------------------------------------------------|

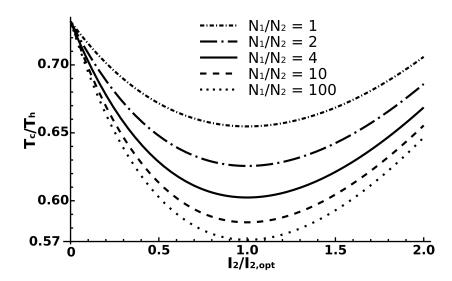

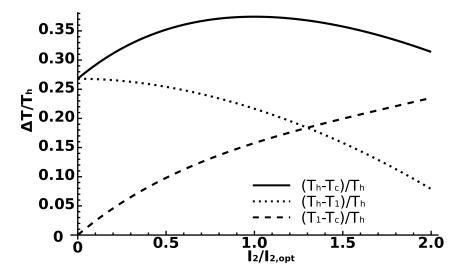

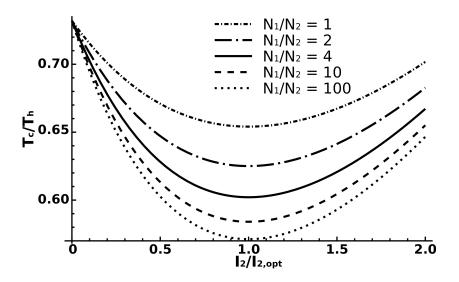

| Figure 3.11: The effect of the second-stage current on the temperature of a 2-stage                       |

| cooler, when the currents are set by sequential optimization. Normalized                                  |

| temperature is plotted versus $I_2$ , normalized with respect to $I_{2,opt}$ for several different        |

| values of $N_1/N_2$ . All curves are for ZT=1                                                             |

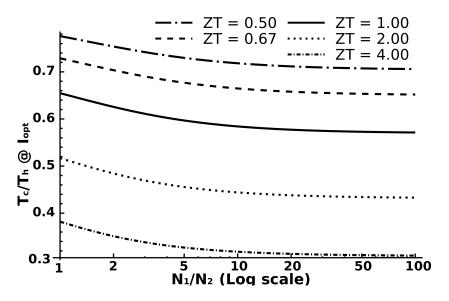

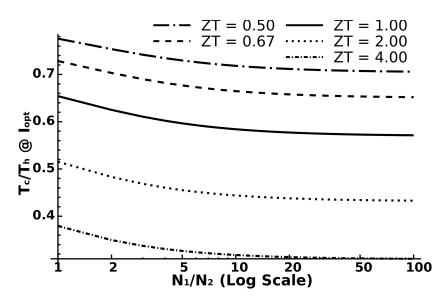

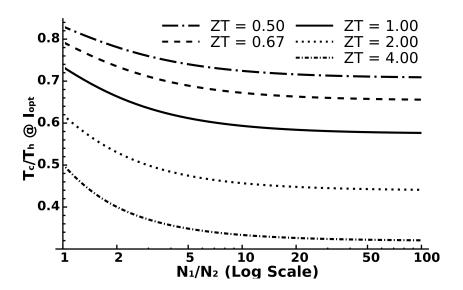

| Figure 3.12: The effect of $N_1/N_2$ on the temperature of a 2-stage cooler, when the                     |

| currents are set by sequential optimization. Normalized minimum is plotted versus                         |

| $N_1/N_2$ at several values of ZT                                                                         |

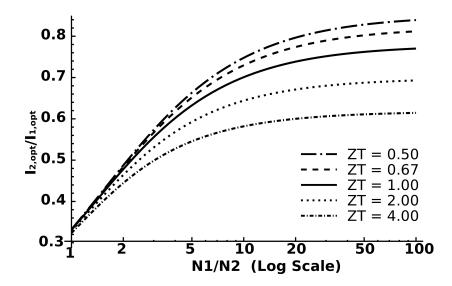

| Figure 3.13: The effect of $N_1/N_2$ on $I_{2,opt}$ for a 2-stage cooler, when the currents are set by    |

| sequential optimization. The ratio of $I_{2,opt}$ : $I_{1,opt}$ is plotted versus the $N_1/N_2$ , showing |

| that $I_{2,opt}$ remains lower than $I_{1,opt}$ , even at high values of $N_1/N_2$                        |

| Figure 3.14: The effect of the second-stage current on the temperature across each stage                  |

| of a 2-stage cooler, when the currents are set by sequential optimization. The                            |

| normalized temperature difference is shown across the first-stage, the second stage,                      |

| and both stages plotted versus $I_2$ . $ZT=1$ , and $N_1/N_2=2$                                           |

| Figure 3.15: The effect of the second-stage current on the temperature of a 2-stage                       |

| cooler, when the currents are set by simultaneous optimization. Normalized                                |

| temperature is plotted versus $I_2$ , normalized with respect to $I_{2,opt}$ for several different        |

| values of $N_1/N_2$ shown. All curves are for ZT=1. This method shows almost no gain                      |

| in performance compared to the sequential optimization process used for Figure                            |

| 3.11. 76                                                                                                  |

| Figure 3.16: The effect of $N_1/N_2$ on the temperature of a 2-stage cooler, when the                     |

currents are set by simultaneous optimization. Normalized minimum is plotted

| versus $N_1/N_2$ at several values of ZT. This method shows almost no difference                    |

|-----------------------------------------------------------------------------------------------------|

| compared to the sequential optimization process used for Figure 3.1277                              |

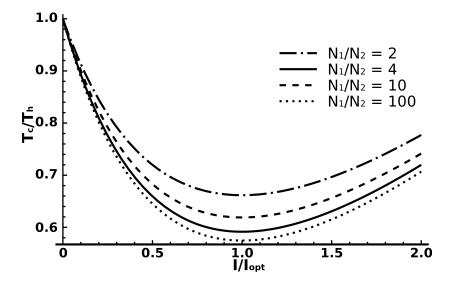

| Figure 3.17: The effect of current on the temperature of a 2-stage cooler, when $I_1=I_2$ .         |

| Normalized temperature is plotted versus $I_2$ , normalized with respect to $I_{2,\text{opt}}$ for  |

| several different values of $N_1/N_2$ . All curves are for ZT=1                                     |

| Figure 3.18: The effect of $N_1/N_2$ on the temperature of a 2-stage cooler, when $I_1=I_2$ .       |

| Normalized minimum is plotted versus N <sub>1</sub> /N <sub>2</sub> at several values of ZT79       |

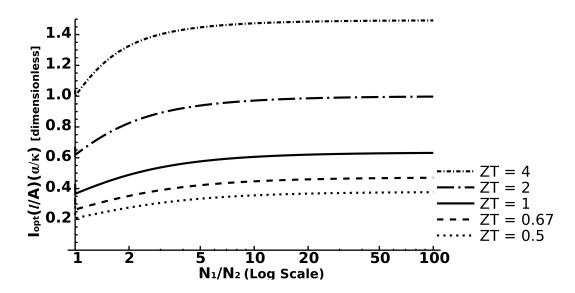

| Figure 3.19: The effect of $N_1/N_2$ on the $I_{opt}$ of a 2-stage cooler, when $I_1=I_2$ . Optimum |

| input current, normalized with respect to geometry and material properties, is plotted              |

| versus the $N_1/N_2$ for several values of ZT                                                       |

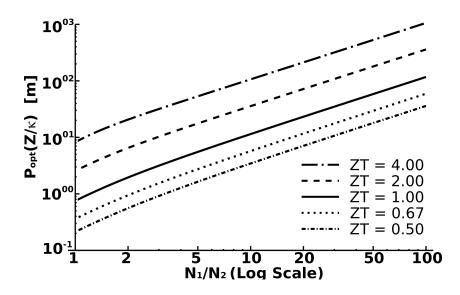

| Figure 3.20: The effect of $N_1/N_2$ on the power consumption of a 2-stage cooler, when             |

| $I_1=I_2$ . Power consumption at the optimum input current, normalized with respect to              |

| geometry and material properties, is plotted versus the $N_1/N_2$ for several values of             |

| ZT80                                                                                                |

| Figure 3.21: The effect of parasitic thermal conductance on cooling for a 2-stage cooler            |

| where $I_1=I_2$ . The normalized minimum temperature is plotted versus the ratio                    |

| between the parasitic thermal conductance per thermocouple and the thermal                          |

| conductance of one thermocouple. $N_1/N_2=2$ for all the curves                                     |

| Figure 3.22: Heat flows in a 2-stage cooler, including an intermediate region with a finite         |

| thermal conductance82                                                                               |

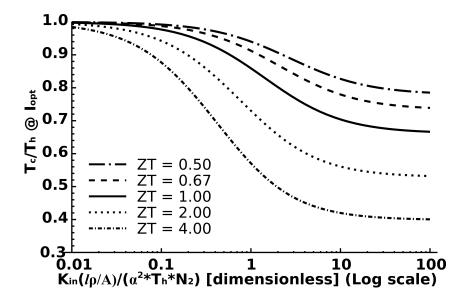

| Figure 3.23: The effect of inter-stage thermal conductance on minimum temperature of a              |

| 2-stage cooler. Normalized minimum temperature is plotted versus K. normalized                      |

| over temperature, material properties, geometry and the number of TCs in the                 |

|----------------------------------------------------------------------------------------------|

| second stage. $N_1/N_2=2$ and a single drive current is used for both stages                 |

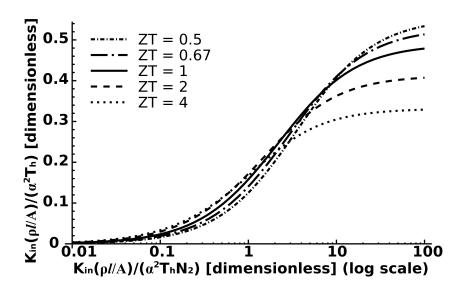

| Figure 3.24: The effect of inter-stage thermal conductance on the optimum current of a 2-    |

| stage cooler for various values of ZT. Optimum current normalized with respect to            |

| temperature, geometry, and material properties versus $K_{\mbox{\tiny in}}$ normalized over  |

| temperature, geometry, material properties, and the number of TCs in the second              |

| stage are shown. $N_1/N_2=2$ and a single drive current is used for both stages 84           |

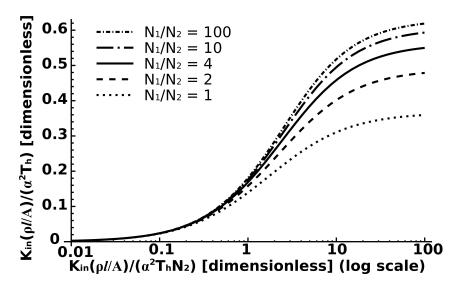

| Figure 3.25: The effect of inter-stage thermal conductance on the optimum current of a 2-    |

| stage cooler for various values of $N_1/N_2$ . Optimum current normalized with respect       |

| temperature, geometry, and material properties, versus $K_{\text{in}}$ normalized over       |

| temperature, geometry, material properties, and the number of TCs in the second              |

| stage are shown. ZT=1 and a single drive current is used for both stages                     |

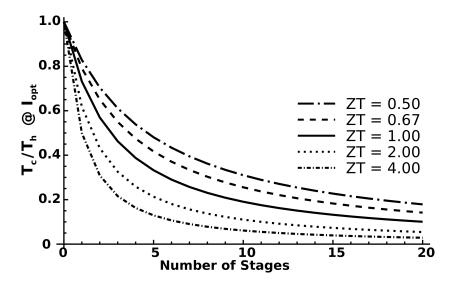

| Figure 3.26: The effect of the number of stages on the normalized minimum temperature        |

| for several values of ZT. The ratio $N_1/N_2$ is set to infinity                             |

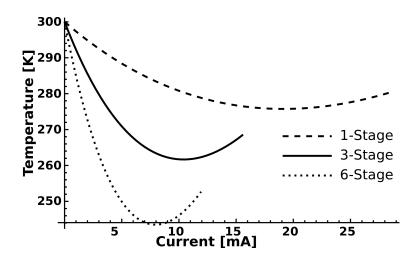

| Figure 3.27: Simulated performance of 1-stage, 3-stage, and 6-stage coolers vs. current      |

| input. The coolers use the material properties for the Michigan TE thin films, and a         |

| contact resistivity of 1.45 $\mu\Omega$ -m.                                                  |

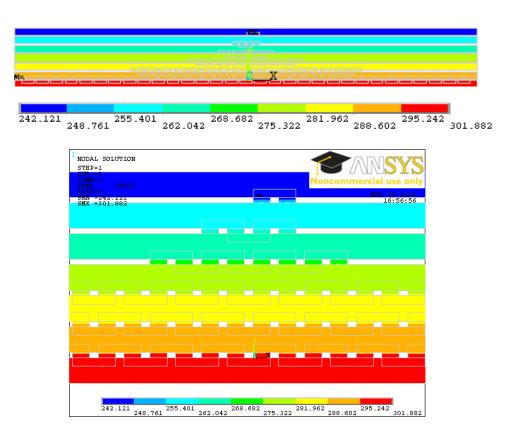

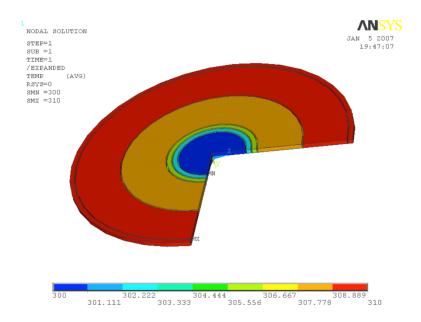

| Figure 3.28: (a) The FEM model of a 6-stage cooler showing the temperature profile at        |

| the optimum current input. (b) The same model, enlarged to make the TCs more                 |

| visible90                                                                                    |

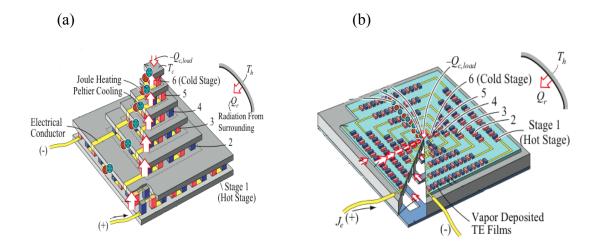

| Figure 4.1: Pyramid to planar design transitions. (a) A traditional pyramid structure. (b) A |

| planar cooler with the stages arranged as concentric rings96                                 |

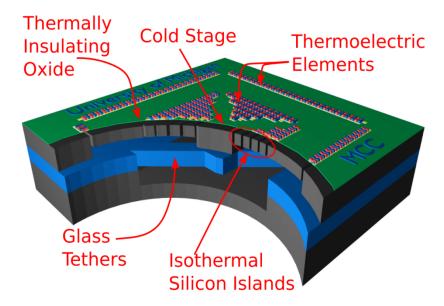

| Figure 4.2: A 3-D rendering of a planar multi-stage thermoelectric cooler. The coldest          |

|-------------------------------------------------------------------------------------------------|

| region is in the center of the device, with 6-stages arranged in concentric squares             |

| around the center. A glass tether supports the cold region to give some additional              |

| strength to the system                                                                          |

| Figure 4.3: Cross sectional diagram of the thermal substrate for a 2-stage cooler built         |

| using the silicon-glass-silicon process                                                         |

| Figure 4.4: 2-D axis symmetric FEM simulation of a 5-stage cooler structure used to             |

| calculate the thermal isolation of the Thermal Substrate                                        |

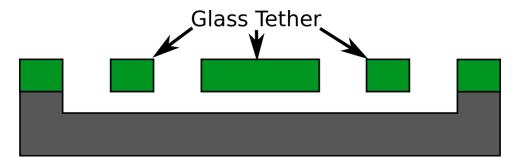

| Figure 4.5: Cross-section of the Structural Substrate used in the Silicon-Glass-Silicon         |

| process                                                                                         |

| Figure 4.6: 3-D Rendering FEM simulation of a glass tether, such as the one used in the         |

| silicon-glass-silicon process. The temperature difference was set at 10 $^{\circ}\text{C}$ 102  |

| Figure 4.7: Illustration of a shadow mask cross sections (a) with a recess around the           |

| pattern, and (b) without a recess around the pattern. Using the recess allows flux              |

| impinging the wafer at shallower angles to reach the device wafer. This is important            |

| in systems where the source is not located along the axis perpendicular to the center           |

| of the wafer                                                                                    |

| Figure 4.8: Images of TE material patterned by shadow masking. (a) The full test                |

| pattern. (b) The smallest element in the test pattern. It is 23 $\mu m$ x 130 $\mu m$ . (c) The |

| largest element in the test pattern. It is 77 μm x 117 μm                                       |

| Figure 4.9 (a) View of the top side of a shadow mask showing the recess and the pattern         |

| that will be deposited on the cooler. (b) Pattern of the backside of the wafer                  |

| showing the pattern that will be deposited. Taken from [82]                                     |

| Figure 4.10: (a) A top view of a 5-stage cooler built using the Silicon-Glass-Silicon         |

|-----------------------------------------------------------------------------------------------|

| process. (b) The inner three stages of the same 5-stage cooler, showing the                   |

| temperature sensor. 119                                                                       |

| Figure 4.11: Pictures of (a) the T1 tether, (b) the T2 tether, and (c) the T3 tether designs. |

| The pictures have been artificially colored to increase the contrast to the background        |

| and to illustrate different regions of the tether designs. Red areas indicate the             |

| regions that will be bonded to the Thermal Substrate. Blue regions are unbonded.              |

|                                                                                               |

| Figure 4.12: An SEM image of the T2 tether design used with a 5-Stage cooler. This            |

| shows the tether suspended over of 10 µm recess in a silicon wafer                            |

| Figure 4.13: Top views of three metal designs, showing (a) M1, (b) M2, and (c) M3.            |

| The metallization used in M1 is also used in the M4 pattern (not shown) but the               |

| oxide bridges are longer in the M4 design                                                     |

| Figure 4.14: A schematic representation of the thermal isolation measurement circuit.         |

| The four-point measurement system is used to avoid measuring changes in                       |

| resistance due to parasitic elements that are not located at the center of the device.        |

|                                                                                               |

| Figure 4.15: Thermal resistance measurement of the 5-stage cooler in air and in vacuum.       |

| The thermal resistance in vacuum is 27 times higher than the thermal resistance in            |

| air                                                                                           |

| Figure 4.16: A wafer map showing thermal resistance measurements across several               |

| variations of cooler designs. Die in green were testable. The top number indicates            |

| thermal resistance in K/W, and V-x indicates a variation designator as explained in                                |

|--------------------------------------------------------------------------------------------------------------------|

| the text                                                                                                           |

| Figure 4.17: Measured performance of a full 5-stage cooler plotted versus input current.                           |

| Power consumption is plotted using the right hand axis, and modeled cooling                                        |

| performance is plotted using nominal                                                                               |

| Figure 4.18: Top view of the 6-Stage cooler, Version 1. It shows the thermoelectric                                |

| elements, the temperature sensor, and the silicon rings                                                            |

| Figure 4.19: An image of the tether used for Version 2 of the 6-stage cooler. The picture                          |

| has been artificially colored to increase the contrast to the background                                           |

| Figure 4.20: Measured performance of Version 1 of a 6-stage cooler, plotted together                               |

| with simulated performance that has been fit to measured data to extract the material                              |

| properties of the TE                                                                                               |

| Figure 4.21: Simulated TE-metal contact resistance for a variety of contact geometries.                            |

| The assumed TE resistivity for these simulations is 20 $\mu\Omega$ -m, and the contact                             |

| resistivity is 1E-8 $\Omega$ -m <sup>2</sup> . The current enters the contact in the TE layer and leaves in        |

| the metal layer                                                                                                    |

| Figure 4.22: Comparison of contacts in Version 1 (right side) and Version 2 (left side).                           |

| The images show contact dimensions and the current path through 3 stages of each                                   |

| cooler                                                                                                             |

| Figure 4.23: Simulated resistance of a TE element deposited over gold. The TE                                      |

| resistivity is assumed to be 20 $\mu\Omega$ -m, and the contact resistivity is 1E-8 $\Omega$ -m <sup>2</sup> . The |

| current enters and leaves the element through the TE material                                                      |

| Figure 4.24: Top view of the 6-stage cooler, Version 2. The inset highlights the                        |

|---------------------------------------------------------------------------------------------------------|

| thermoelectric elements at the inner 4 stages, and illustrates how a single element                     |

| can span multiple stages                                                                                |

| Figure 4.25: : Measured performance of several Version 2, 6-stage coolers plotted versus                |

| input current. All demonstrate cooling of greater than 19 K                                             |

| Figure 4.26: Measured performance of Version 2 of a 6-stage cooler, plotted together                    |

| with simulated performance that has been fit to measured data to extract the material                   |

| properties of the TE                                                                                    |

| Figure 4.27: Top view of a single stage cooler with 16 TCs                                              |

| Figure 4.28: Measured performance of a 1-stage cooler, plotted together with simulated                  |

| performance that has been fit to measured data to extract the material properties of                    |

| the TE                                                                                                  |

| Figure 4.29: A 1-stage cooler tested at various thermal loads. The temperature change                   |

| achieved and the optimum current both increase as the input load increases 140                          |

| Figure 4.30: Variation in $\Delta T$ and $I_{opt}$ with respect to cold stage temperature for a 1-stage |

| cooler. The ambient temperature is maintained at 300 K, and the temperature of the                      |

| center region is increased by applying a thermal load with a resistive element 141                      |

| Figure 4.31: A Version 2 6-stage cooler tested at various thermal loads. The temperature                |

| change achieved and the optimum current both increase as the input load increases.                      |

|                                                                                                         |

| Figure 4.32: Variation in $\Delta T$ and $I_{opt}$ with respect to cold stage temperature for a 6-stage |

| cooler. The ambient temperature is maintained at 300 K, and the temperature of the                      |

| center region is increased by applying a thermal load with a resistive element 142                      |

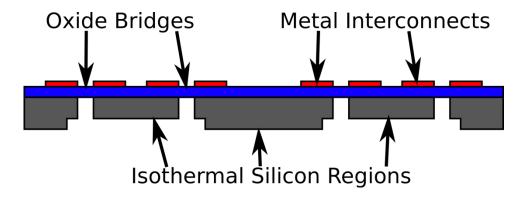

| Figure 5.1: Cross section of a 2-stage cooler implemented using the structure. The          |

|---------------------------------------------------------------------------------------------|

| thermal properties of the cooler are implemented with an oxide-metal-oxide stack            |

| that is supported by oxide pillars                                                          |

| Figure 5.2: Illustration of maximum dimension for inter-stage thermal conduction 149        |

| Figure 5.3: Illustration of heat and current flow in (a) a conventional, serially-driven 2- |

| stage cooler, and (b) a two stage cooler using a resistive network to distribute            |

| current. The electrical schematic of the device shown in (b) is provided as (c) 162         |

| Figure 5.4: (a) Illustration of a previously devised three stage cooler that distributes    |

| current through a resistive network. (b) A 3-stage cooler using the resistive               |

| network proposed in this section. (c) A modified version of the cooler shown in (b).        |

| It combines inter-stage regions of the same nominal voltage                                 |

| Figure 5.5: Cross section of a 2-stage cooler using the simplified vartion of the single    |

| wafer process                                                                               |

| Figure 5.6: A top-down SEM view of the 4-stage cooler with resistive network current        |

| distribution. The individual stages and the cold platform are highlighted 167               |

| Figure 5.7: An SEM showing the oxide pillars supporting the cold platform and stages 1      |

| and 2 of the 4-stage cooler. This image also shows how the oxide has been                   |

| removed, except directly under the TE materials                                             |

| Figure 5.8: An SEM image of the inter-stage zone between stages 2 and 3 of a 4-stage        |

| cooler. The zone is not supported by any oxide pillars, and curling of the inter-stage      |

| zone is clearly visible. This is in contrast to Figure 5.7, which shows very little         |

| deflection of the interstage zones where they are supported by the pillars 168              |

| Figure 5.9: Schematic representation of the 4 stage cooler                                  |

| Figure 5.10: FEM simulation of a cooler with resistive network current distribution,       |

|--------------------------------------------------------------------------------------------|

| using the material properties reported in Chapter 2 for co-evaporated materials            |

| deposited at the University of Michigan                                                    |

| Figure 5.11: Thermal resistance measurement of a 4-stage cooler fabricated using the       |

| simplified single wafer process. The thermal resistance is 42,539 K/W                      |

| Figure 5.12: FEM simulation of a cooler with resistive network current distribution, using |

| the material measured in section 5.4.4.2                                                   |

| Figure 5.13: Top down SEM images of 5-stage (annotated), 1-stage (left), 2-stage           |

| (center), and 3-stage coolers (right), pictured released but without TE. Only a            |

| quarter of each cooler is shown because the devices are too large to visualize             |

| completely in the SEM                                                                      |

| Figure 5.14: Simulated performance of 1, 2, 3, and 5-stage coolers with no parasitic       |

| thermal effects considered                                                                 |

| Figure 5.15: Simulated performance of 1, 2, 3, and 5-stage coolers with parasitic          |

| conduction due to supporting oxide membranes included in the model                         |

| Figure 5.16: Simulated performance of 1, 2, 3, and 5-stage coolers with parasitic          |

| conduction due to supporting oxide membranes and oxide pillars included in the             |

| model                                                                                      |

| Figure 5.17: An SEM image of an antimony telluride leg of a TC. The crack in the           |

| antimony telluride is clearly visible                                                      |

| Figure 5.18: Performance predictions based on the material properties extrapolated from    |

| the measured performance of a 3-stage cooler                                               |

| Figure 5.19: Cross section illustration of the TLP bonding process showing the low     |

|----------------------------------------------------------------------------------------|

| melting temperature metal as purple and the high melting temperature metal in          |

| yellow. The illustration includes (a) The bond pads prior to bonding, (b) the          |

| arrangement at the initiation of the bond, and (c) the diffused intermetallic          |

| compound after completing the bonding process                                          |

| Figure 5.20: An SEM image of a die bonded to an unreleased cooler structure 187        |

| Figure 5.21: SEM images as different magnification levels of the bond region after the |

| attached die has been pried away. Silicon has fractured, indicating a strong bond.     |

|                                                                                        |

### **List of Tables**

| Table 1.1: Summary of applications benefitting from cooling                                                           |

|-----------------------------------------------------------------------------------------------------------------------|

| Table 1.2: Summary of cooling techniques                                                                              |

| Table 1.3 Comparison of thermoelectric microcoolers including structure, materials,                                   |

| temperature differentials and power consumption                                                                       |

| Table 2.1: Thermoelectric Properties of Common Metals at ~300K <sup>a</sup>                                           |

| Table 2.2: Comparison of Co-evaporated Bi <sub>2</sub> Te <sub>3</sub> and Sb <sub>2</sub> Te <sub>3</sub> Thin-films |

| Table 3.1: Material Properties and Dimensions used for simulation shown in Figure 3.27.                               |

| 89                                                                                                                    |

| Table 4.1: Thermal Substrate fabrication process overview                                                             |

| Table 4.2: Structural Substrate fabrication process overview                                                          |

| Table 4.3: Cooler completion process overview                                                                         |

| Table 4.4: Critical dimensions of the 5-Stage thermoelectric cooler                                                   |

| Table 4.5: Critical dimensions of the Version-1 6-Stage thermoelectric cooler 127                                     |

| Table 4.6: Critical dimensions of the Version-2 6-Stage thermoelectric cooler                                         |

| Table 5.1: Design parameters of the 4-stage cooler fabricated using resistive network                                 |

| current distribution                                                                                                  |

| Table 5.2: Design parameters for the 1, 2, 3 and 5-stage coolers fabricated using the                                 |

| single wafer process                                                                                                  |

# Chapter 1 Introduction

Advancements in microcooling technology are being driven by applications across a number of industries. The medical industry is interested in microcoolers to aid in cryosurgical techniques. Microcoolers that can be integrated with thermal imaging sensor would be useful for defense related applications. The communications industry would benefit from the decreased noise of cooled frequency references and amplifiers, but only if the solutions are small enough and low enough in power to integrated into mobile products. Digital electronics could operate with higher speed and stability if they could be paired with integrated cooling solutions, and some MEMS devices, such as resonant gyroscopes also demonstrate performance increases as they are cooled.

Some of these application areas are being addressed. Micro Joule-Thomson coolers have been developed with cryosurgery in mind, as well as for cooling microelectronics and MEMS. Thermoelectric cooling has been used to create integrated solutions for electronics with high power dissipations. However, there are applications where these solutions are not feasible. The Joule-Thomson coolers are too complex for many applications. Thermoelectric coolers offer compact solid-state operation, but the coolers developed to date have been designed for applications with high heat loads, where the total power consumption of the system is of little interest. Devices such as LNAs and gyroscopes, on the other hand are often used in mobile applications where the total power consumption of the system is very important. Applications like these, that

require a large temperature differential and low power consumption, have not yet been addressed, and they are the motivation behind the research in this thesis.

Designing a thermoelectric microcooler for low-power, mobile applications presents many challenges. First among them, is how to design for low power operation. Although several groups have previously developed thermoelectric micro-coolers with temperature differentials greater than 40 K, they require high power consumption. Reducing the power consumption of the thermoelectric cooler without reducing the temperature differential that can be achieved is fundamental to achieving the goal of a low-power integratable device.

The second challenge is integration of the thermoelectric materials with a microfabricated supporting structure. The deposition conditions of the thermoelectric material must be optimized, and the deposition process must to be integrated with the larger process flow used to make the device. These materials are incompatible with many clean room processes and have a low thermal budget, making the integration a significant challenge. The final set of challenges center on creating an entire system with the cooler. The cooler is of no use if it cannot be applied to the applications it is intended to address. It must be integrated with a MEMS or electronic device that requires cooling, and the entire system, comprising the cooler and the target device, must be appropriately packaged. The goal of this thesis is to present a thermoelectric microcooler that addresses the design challenges discussed above. The cooler will be capable of generating large temperature differentials with a power-consumption of less than 100 mW and will be integratable with arbitrary MEMS devices.

This chapter will present the motivation behind developing a micro thermoelectric cooler. It will begin with a discussion of the applications for micro cooling, and the cooling levels need for the targeted applications. It will then proceed to an overview of cooling technologies, including both macro and micro scale systems, and a discussion of why thermoelectric cooling is a good choice for many applications at the micro scale. It will provide a comparison of various thermoelectric micro coolers that have been developed to date, and discuss the contributions that this work makes to the state of the art. Finally this chapter will provide an outline of the remainder of this thesis.

#### 1.1 Applications for micro cooling

A number of electronic and MEMS devices can exhibit improved performance characteristics when operated below room temperature. The desire to take advantage of these performance enhancements is one of the main driving forces for the development of micro scale integrated cooling systems. Different classes of devices, however, express such temperature-dependent performance increases in different ways. Similarly, different types of devices exhibit improved performance changes in different temperature ranges, and require different levels of cooling power. Table 1.1 summarizes several application areas that could potentially benefit from micro cooling. and the remainder of this section elaborates on those application areas.

Table 1.1: Summary of applications benefitting from cooling.

| Application                      | Metric of Improved<br>Performance                       | Temperature Range of<br>Improved Performance |

|----------------------------------|---------------------------------------------------------|----------------------------------------------|

| Low Noise Amplifiers             | Reduced Johnson noise                                   | 19 K – 200 K                                 |

| Infrared Detectors               | Reduced Johnson and                                     | 70 K – 250 K                                 |

|                                  | temperature noise                                       |                                              |

| Resonant MEMS                    | Increased quality factor                                | <250 K                                       |

| Chromatography                   | Improved analyte adsorption; transit speed manipulation | <300 K                                       |

| Temperature cycled applications. | Cooling speed                                           | NA                                           |

| Solid State Laser                | Required for Continuous wave IR emmision                | <264 K                                       |

#### 1.1.1 Analog Electronics

One broad class of devices that can benefit from operation at decreased temperatures are analog integrated circuits; these circuits generally see a decrease in noise figure resulting from lower Johnson noise in transistors and resistors at lower temperature. Minimizing noise figure is particularly important in the first stage of cascaded amplifiers, because the noise introduced at this stage receives the most amplification, and ultimately dominates the noise output of the entire system amplifier. To address this, special low noise amplifiers (LNAs) have been developed, and are often employed as the first stage of amplification in the front end of radio receivers. Because LNAs dominate the noise performance of the overall system, further reduction in the noise figure of these devices is important. Several groups have demonstrated that reducing the operating temperature of the devices does, in fact, yield a significant performance increase.

In one case, an LNA designed for room temperature operation from high electron mobility GaAs transistors nonetheless demonstrated a decrease in noise temperature from

approximately 200 K when operate at 297 K to 20 K when operate at 19 K, demonstrating that improvement can be achieved even in devices that have been designed for room temperature operation [1]. In another case, a shift in noise figure from near 1 dB at 300K to 0.55 dB at 70 K was observed [2]. In both of these cases the low-temperature performance was investigated at truly cryogenic temperatures. However, for some devices, significant decreases in noise can be observed at more modest temperatures. In one instance the noise temperature was observed to change from 46 K at 293 K to 28 K at 200 K [3]. Although still significantly below room temperature, 200 K is within the temperature range that can be reached by small, commercially-available thermoelectric and Joule-Thomson coolers. An additional study addressed the use of thermoelectric cooling more directly. It showed a decrease in noise temperature from over 100 K to less than 80 K over a change in temperature from to 30 C to -15 C, using a commercially available thermoelectric cooler using less than 600 mW of input power [4].

#### 1.1.2 Infrared (IR) Detectors

Infrared detectors constitute another large class of devices that can benefit from the application of micro cooling technology. There are two main types of IR detectors. One class of infrared sensors is based on the operation of photodiodes and photoconductors, in which electron-photon interactions increase the number of available carriers. However, unlike a standard photodiode, IR photon detectors are fabricated from semiconductors such as HgCdTe that have high absorption coefficients for light in the infrared region. For these detectors to be effective, the ratio of photon-generated carriers to thermally generated carriers should be greater than 1. For long and very long wavelength IR, it is necessary to cool the detectors to cryogenic temperatures in the range

of 70K or less in order to achieve this ratio. Short wave length IR detection, on the other hand, requires much less cooling, and detectors have been demonstrated that only require commercially available thermoelectric cooling units[5].

The second class of sensors are heated by impinging infrared light, and the temperature change is proportional to the intensity of the incident light. These devices consist of an IR absorber that is attached to a substrate through low thermal conductivity legs, and the temperature of the absorber can be measured either with a thermistor or thermoelectrically. In these devices, detectivity is primarily limited by thermal noise, which manifests itself both as Johnson noise in the electric components and as random temperature fluctuations of the absorber itself. The Johnson noise is proportional to T, while the temperature fluctuations are proportional to T<sup>2</sup>[6]. Decreasing the temperature of such a detector from 300 K to 250 K would therefore lead to a reduction in Johnson noise of 16.6%, and a decrease in thermal fluctuations of 30%.

#### 1.1.3 Resonant MEMS and gyroscopes

A third group of devices that can benefit from operation at decreased temperature are resonant MEMS. These devices are finding increasing applications as filters and potentially as a replacement for quartz resonators in clock and RF frequency generators. Additionally, resonant devices have been used to fabricate MEMS gyroscopes for several years now. It has been demonstrated that these devices experience an increase in the Quality Factor (Q) of their resonance at decreased temperatures. The change in Q can be quite significant, and it has been demonstrated to be a more sensitive measure of temperature than silicon RTDs for at least one resonator design [7]. However, the temperature range at which the change in Q occurs is highly dependent on the design of

the resonator. In the case of the resonant temperature sensor discussed above, which resonated at 1.3 MHz, the Q changed from less than 7 000 at 70 C to more than 12 000 at 0 C. However, in another case, resonators did not demonstrate a significant increase in Q unless they were cooled to below 110 K, at which point they showed an increase in Q from less than 100 000 to 362 768 at 5 K [8].

This variability in the temperature dependence of Q between different resonant devices means that care must be taken when pairing such devices with a cooling solution to ensure that low enough temperatures can be achieved. Gyroscopes, in particular, have demonstrated marked improvements in Q at relatively modest decreases in temperature. For example in one case, the sense mode Q was observed to change from 33,900 at 50 C to 51,700 at 5 C, while the drive mode Q changed from 54,400 to 72,500 [9]. In another design, the Q changed from approximately 10,000 at 50 C to more than 25,000 at 5 C, and this corresponded to a change in sensitivity of 57% [10].

#### 1.1.4 Other Applications

One additional application that can benefit from micro cooling is IC lasers. They have exhibited improved performance when cooled thermoelectrically to temperature of 264 K [11]. Finally micro scale cooling has applications for a new generation of micro scale gas chromatographs that are under development. These devices can benefit from increased adsorption of analytes at various stages of the chromatography process. Increased adsorption in preconcentration beds leads to higher analyte collection, and 2D chromatography uses thermal modulation in the region between the two columns to separate peaks that would otherwise coelute [12].

#### 1.1.5 Summary of Applications

It is clear from the descriptions above that a wide variety of micro scale devices can benefit from an integrated micro-scale cooling solution. In particular, a number of applications, including gyroscopes, thermal IR detectors, IC lasers, and certain LNAs have exhibited a significant increase in performance at temperatures above -50 C, potentially within the range of several types of cooling solutions. It is also important to note that several of these applications, particularly gyroscopes and passive IR sensors, dissipate very little power and are sometimes deployed in applications that require mobility and an overall low system power. This is an important consideration when evaluating potential cooling solutions; they should therefore be simple, robust and low power. Various types of cooling, their effectiveness, and their suitability to miniaturization and integration will be described in the following section.

#### 1.2 Comparison of Cooling Methods

There are a wide variety of refrigeration and cryogenic cooling solutions at the macro scale. These can be based on several different mechanisms, and demonstrate different trade-offs between achievable minimum temperature, efficiency, overall power consumption, and simplicity. Some of these technologies have properties that allow them to be effectively miniaturized, while others remain primarily macro-scale. Table 1.2 summarizes the major cooling and refrigeration technologies used at the macro scale, and these are elaborated on in the remainder of this section.

Table 1.2: Summary of cooling techniques

| Type of Cooler                              | Minimum<br>temperature                      | Applications                                                                          |

|---------------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------|

| Vapor Compression                           | ~250 K                                      | Consumer and commercial refrigeration                                                 |

| Absorption                                  | ~250 K                                      | Consumer and commercial refrigeration                                                 |

| Stirling (including pulse-<br>tube coolers) | 1.78 K                                      | Cooling for cryogenic processes; gas liquefaction possible                            |

| Joule Thomson                               | 78 K (for nitrogen)<br><20 K (for helium)   | Cooling for cryogenic process, gas liquefaction                                       |

| Laser Cooling of Gasses                     | <1 mK                                       | Specialized research                                                                  |

| Laser Cooling of Solid                      | 212 K                                       | Mechanically and electrically isolated cooling                                        |

| Demagnetization cooling                     | <1 K                                        | Specialized research                                                                  |

| Thermoelectric cooling                      | ~ 230 K – single stage<br>~170 K – 6 stages | Consumer refrigeration, IR sensors, solid state lasers, other sensors and electronics |

#### 1.2.1 Macro-scale coolers and refrigerators

#### 1.2.1.1 Fluid based systems

One broad class of macro-scale coolers is known as vapor-compression systems. The vapor-compression cycle relies on cooling through the evaporation of a working fluid. After the evaporation, the fluid undergoes adiabatic compression back to a liquid phase, during which it experiences an increase in temperature. The fluid then exchanges heat with the environment and undergoes cooling, after which it is fed back to the evaporator. This type of cooling cycle is widely used in commercial and consumer applications. Refrigerants include CO<sub>2</sub>, ammonia, and engineered refrigerants such as R22. The minimum achievable temperature is related to the boiling point of the working fluid in the system, and is usually higher than -50 C [13],[14].

Absorption coolers are related to vapor compression coolers, but utilize heat energy instead of mechanical energy to power the cooling cycle. These systems remove heat from the cold region through evaporation of a liquid working fluid. After evaporation, the gas is absorbed into another fluid, which is then transported away from the cold region, and heated to desorb the refrigerant. The desorbed, high temperature gaseous refrigerant exchanges heat with the ambient and condenses back to a liquid state. Finally, the liquid refrigerant is fed back to the evaporator and the cooling process continues. The refrigerant is often ammonia, and the temperature differentials that can be achieved are similar to those of vapor compression systems[14].

A second class of fluid-based macro-scale coolers are based on the Stirling cycle. In this thermodynamic cycle, a working fluid is expanded adiabatically, after which it absorbs heat from the area being cooled. The fluid is then forced through a thermal regenerator where it is warmed and expands further. The fluid undergoes adiabatic compression and its temperature increases. It exhausts heat to the environment, and is moved back through the regenerator, where it is cooled and decreases in volume. Stirling cycle coolers are used in a wide variety of applications ranging from commercial refrigeration systems to cryogenic cooling systems. In traditional systems the gas flow, compression, and expansion are controlled by a system of multiple pistons, or pistons and valves in the case of Gifford-MacMahon coolers. A more recent variation of the Stirling cycle, the pulse-tube cooler, utilizes a single piston, combined with a reservoir connected to the main system through an orifice, and has achieved temperatures as low as 1.78 K [15].

A third type of fluid-based cooler utilizes the Joule-Thomson cycle. In this type of cooler, a gas under high pressure is forced through a small orifice where it undergoes isenthalpic expansion. Given an appropriate initial temperature, this results in cooling of the gas. The cooled low-pressure gas then travels away from the orifice, where it exchanges heat with the high pressure gas through a counter flow heat exchanger. Due to the use of counter-flow heat exchangers, the temperature of the gas after expansion will decrease over time until liquefaction begins to occur. These systems have been used to create liquid air, N2, O2 and He. The boiling point of the liquid will define the minimum achievable temperature, and the heat of vaporization, combined with the rate of liquid generation, will define the maximum heat load that can be cooled [16].

#### 1.2.1.2 Solid State Systems

For systems where a compressed gas source is not available, there are solid-state solutions that can be applied. The most widely used are thermoelectric coolers. These devices make use of the Peltier effect, which will be discussed at length in the following chapters. At room temperature they typically use (Bi,Sb)<sub>2</sub>Te<sub>3</sub> based materials, and have been used have been applied for a wide variety of applications. Consumer products include refrigerators and wine coolers capable of maintaining temperatures as low as 0 °C [17-19]. Although they cannot achieve the same minimum temperature that a conventional refrigerator can, these devices are appealing in applications where small size and quiet operation are important. They can also be useful when standard AC power is not available but DC power is. Thermoelectric modules are also available for a wide range of performance parameters for a variety of applications. Single stage devices are capable of reaching temperatures as low as 232 K, and are marketed for use with

bolometers and laser diodes. Two stage devices can reach temperatures of 203 K and are marketed toward use with CCD arrays and IR detectors. Four-stage devices can reach temperatures as low as 173 K, and 6 stage devices can achieve 167 K and are also targeted at CCD arrays and IR detectors. Integrated thermoelectric systems are also being applied to IC cooling [20].

A second solid-state technology that has been applied to certain specialized problems is laser cooling. Laser cooling of gasses has been available for several years, and works by shining properly tuned lasers into a magnetically confined low-density gas from multiple directions. Over time this arrangement gradually reduces the average kinetic energy of the atoms in the gas, thus cooling the system. This technique is used to cool gases to below 1 mK [21]. A potentially more useful technology involves laser cooling of crystalline solids. For this technique a laser is focused on special material such as ZBLANP (ZrF<sub>4</sub>–BaF<sub>2</sub>–LaF<sub>3</sub>–AlF<sub>3</sub>–NaF–PbF<sub>2</sub>), and tuned so that electron transitions require the photon to interact with both an electron and a phonon. When the electron transitions back to its ground state, it emits all its excess energy as a photon. As a result there is a net loss in the energy of the system, equivalent to the energy of the phonon. The loss of energy causes the system cool, and has produced temperature differentials of 92 K at 300 K ambient temperature[22].

A final technique that has been used for cooling at the macro scale is demagnetization cooling. If a magnetic field is applied to certain materials under adiabatic conditions, they will increase in temperature due to the decrease in magnetic entropy. The material can then exchange heat with a thermal sink and cool back to its initial temperature. Next the sample is returned to adiabatic conditions and is

demagnetized. The increase in magnetic entropy results in a decrease in temperature. This technique can be used in refrigeration systems [23], but has also been used in cryogenic systems to achieve temperatures well below 1 K [24].

#### 1.2.2 Previous work in Micro-coolers

Although there are a wide variety of cooling options at the macro scale, only a few technologies have been investigated at the micro scale. These include a significant investigation of both Joule-Thomson coolers and thermoelectric coolers, as well limited theoretical work with micro Stirling coolers. The remainder of this section will detail the state of the art of these three technologies, and compare their benefits and weaknesses.

#### 1.2.2.1 Joule -Thomson coolers

Joule-Thomson coolers that utilize micro scale fabrication have been built by multiple groups, and with several design variations[25],[16],[26-31]. Single stage J-T coolers were fabricated at the University of Twente that reached a minimum temperature of 96 K and had a heat cooling power of at least 5 mW[25]. J-T coolers have also been fabricated at the University of Michigan [16] and the University of Colorado [31]. While effective at generating temperature differentials, such coolers have a number of drawbacks that make them an impractical solution for many integrated cooling applications. Although these devices use micro fabricated components, the total system size can still be relatively large. In all of the examples mentioned above, the counterflow heat exchanger exceeded 1 cm in at least one dimension. In addition all J-T systems require a source of high-pressure gas. This can be supplied in an open-loop system with compressed bottled gas, or with a compressor to form a closed-loop system. In either case, the need for high pressure leads to an increase in the overall size complexity and

cost of the system. It also makes J-T systems impractical for applications where small size, simplicity and integration are more important than efficiency and the absolute minimum temperature.

#### **1.2.2.2** Stirling

Limited work has been done on the development of micro Stirling coolers [32],[33]. These coolers are intriguing candidates for miniaturization because they require less compression of the gas than J-T systems, and implementation of the regenerator could potentially be less complex than the counter flow heat exchanger required for a J-T system. However, developing a micro-stirling cooler would still require fabrication of a complex, dynamic, micro mechanical system. Additionally the system must be sealed with the working fluid inside and be resistant to leaks. Although potentially smaller and more self contained than J-T coolers, this high level of complexity is still undesirable for many applications.

#### 1.2.2.3 State of the art thermoelectric micro cooling

Unlike J-T and Stirling coolers, thermo-electric coolers offer an entirely solid state solution to cooling at the micro scale, and several groups have worked on developing small scale integrated thermoelectric coolers {insert citations}. Earlier work at the University of Michigan implemented a single stage design that used Bi2Te3 as the n-type material and Sb2Te3 as the p-type, material and achieved maximum cooling of 1.3 K while consuming 41 mW [34]. Several other investigators have also made use of a single stage vertical architecture, while using a variety of materials. Huang made use of polysilicon as the thermoelectric material and achieved a maximum temperature differential of 5.6 K, while consuming 844 mW of power [35]. Fan used a SiGe/Si

supperlattice as the p-type material and metal as the n-type material to create a cooler capable of cooling by 12 K at an ambient temperature of 200 C [36]. More successfully, Bottner has produced coolers utilizing Bi2Te3 as the n-type material and Sb2Te3 as the p-type material, which have demonstrated cooling of 48 K at an ambient temperature of 85 C, at an input current of 2.2 A [37]. Bulman has made use of more complex superlattice materials consisting of layers of quaternary alloys of (Bi<sub>x</sub>,Sb<sub>x-1</sub>)<sub>2</sub>(Te<sub>y</sub>,Se<sub>y-1</sub>)<sub>3</sub>. This research yielded a single stage cooler capable of generating 55 K temperature differentials at a total power draw of 362 mW at in input current of 3.9 A [38]. The same group has also produced a 3-stage vertical cooler capable of cooling by 102 K [39]. The performance of these coolers is compared in Table 1.3. It should be noted that the most effective vertical thin film thermoelectric coolers require a large amount of input power. This is largely due to the thinness of the films and will be discussed in greater depth in Chapter 3.

A different approach is to move the heat laterally across the die. This approach allows for greater control of the geometry of the thermocouple (TC) when using thin films, and can be used create coolers with lower power requirements. This approach was investigated by Yao, who achieved cooling of only 2 K utilizing a Si/SiGe superlattice as the thermoelectric material [40]. Goncalves has also investigated planar thermoelectric coolers and has achieved 5 K of cooling utilizing Bi2Te3 and Sb2Te3 on a polyimide substrate. This cooler achieved optimal operation at an input current of 4 mA with a total power consumption of 0.48 mW [41],[42].

# 1.3 Scope of Research

The opening of this chapter gave the major challenges associated with developing a low-power thermoelectric microcooler as:

- 1) Designing for low-power operation

- 2) Integration of the thermoelectric materials into the fabrication process

- System level integration, including attachment of a device and appropriate packaging

While this thesis will seek to address all of the challenges above, its scope is nonetheless limited. The requirements of designing coolers for low power will be covered in depth, as will integration of the thermoelectric materials into the fabrication process. In fact, the materials have been integrated with two distinct fabrication processes and the challenges associated with each will be presented. Die attachment will be demonstrated, and it will be shown that the coolers are compatible with vacuum packaging techniques, both thermally and mechanically. The devices present will be tested under vacuum, however vacuum packaging itself will not be demonstrated.

and power consumption. Table 1.3 Comparison of thermoelectric microcoolers including structure, materials, temperature differentials

| Reference                           | Bulman et al                                                                      | Nextreme                                   | Bottner et al                             | Micropelt                             | Bulman et al                                                       |

|-------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------|---------------------------------------|--------------------------------------------------------------------|

| Structure                           | 1-Stage Vertical                                                                  | 1-Stage Vertical                           | 1-Stage Vertical                          | 1-Stage Vertical                      | 3-stage Vertical                                                   |

| Materials                           | $n\text{-Bi}_2\mathrm{Te}_3/$                                                     | $(Bi,Sb)_2(Te,Se)_3$ based                 | $n	ext{-}	ext{Bi}_2(	ext{Se},	ext{Te}_3)$ | $n	ext{-}	ext{Bi}_2(	ext{Se,Te})_3$   | $n-{ m Bi}_2{ m Te}_3/{ m Bi}_2{ m Te}_{2.83}{ m Se}_{0.17}$       |

|                                     | ${ m Bi}_2{ m Te}_{2.83}{ m Se}_{0.17} \ p{ m -Bi}_2{ m Te}_3/{ m Sb}_2{ m Te}_3$ | super lattice                              | $p$ -(Bi,Sb) $_2$ Te $_3$                 | $p$ -(Bi,Sb) $_2$ Te $_3$             | p-Bi <sub>2</sub> Te <sub>3</sub> /Sb <sub>2</sub> Te <sub>3</sub> |

| ZT                                  | n-type: 1.4                                                                       | Unknown                                    | n-type: 0.53                              | Unknown                               | n-type: 1.4                                                        |

|                                     | p-type: 2.4                                                                       |                                            | p-type: 0.71                              |                                       | p-type: 2.4                                                        |

| Cooling @ $I_{opt}$ ; $T_h^{(1,2)}$ | 55 K @ 3.9 A                                                                      | 40 K @ 3.8 A; 25 °C<br>47 K @ 4.8 A; 85 °C | 48 K @ 2.2 A; 85 °C                       | 44.4 K @ 1.2 A; 23 °C 61.2 K @ 1.4 A; | 102 K @ current varies by stage                                    |

| Estimated Power consumption         | 362 mW                                                                            | 760 mW @ 25 °C                             | Unknown                                   | 450 mW @ 23 °C                        | 28.11 W                                                            |

| Estimated Extrinsic ZT              | 0.54                                                                              | .31                                        | .31                                       | .35                                   | NA                                                                 |

| Reference                   | Snyder et al                      | Fan et al              | da Silva et al                    | Goncalves et al                | Huang et al      |

|-----------------------------|-----------------------------------|------------------------|-----------------------------------|--------------------------------|------------------|

| Structure                   | 1- Stage Vertical                 | 1-Stage Vertical       | 1-Stage Vertical                  | 1-Stage Horizontal             | 1-Stage Vertical |

| <b>Materials</b>            | $n	ext{-}	ext{Bi}_2	ext{Te}_3$    | p-Si/SiGe superlattice | $n	ext{-}	ext{Bi}_2	ext{Te}_3$    | $n	ext{-}	ext{Bi}_2	ext{Te}_3$ | n-poly-Si        |

|                             | p-Sb <sub>2</sub> Te <sub>3</sub> |                        | p-Sb <sub>2</sub> Te <sub>3</sub> | $p	ext{-}	ext{Sb}_2	ext{Te}_3$ | p-poly-Si        |

|                             | (electroplated)                   |                        |                                   |                                |                  |

| ZT                          | unkown                            | unknown                | n-type: 0.053                     | n-type: 0.5                    | n-type: 0.024    |