University of Michigan researchers for use in MEMs packaging technologies as a way to provide both mechanical support and thermal isolation to MEMS devices [95], and the technology was adapted for this project as a way to add support to the silicon rings and the center platform. The glass tether is shown in cross section in Figure 4.5. Pyrex 7704 glass was chosen because it is stiff, has a low thermal conductivity of about 1.15 W/m-K [96], and can be anodically bonded to silicon. The tether is designed to have a high aspect ratio. In this way, it can provide added stiffness and strength to the thermal structure without adding a significant amount of parasitic thermal conduction. A 2.5 mm tether with a 100  $\mu$ m x100  $\mu$ m cross sectional area will have a total thermal conductance of 6.96E-6 W/K, several orders of magnitude lower than the thermal conductances of the SiO<sub>2</sub> bridges that it reinforces.

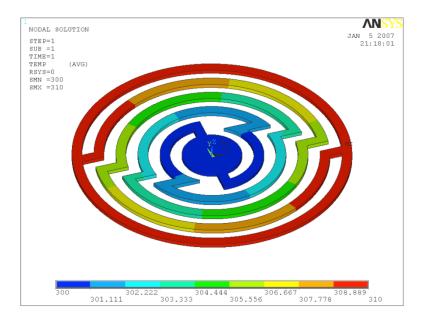

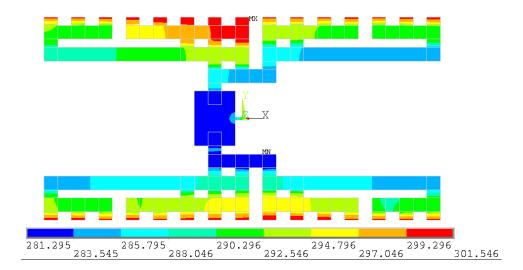

Figure 4.6: 3-D Rendering FEM simulation of a glass tether, such as the one used in the silicon-glass-silicon process. The temperature difference was set at  $10\ ^{\circ}\text{C}$ .

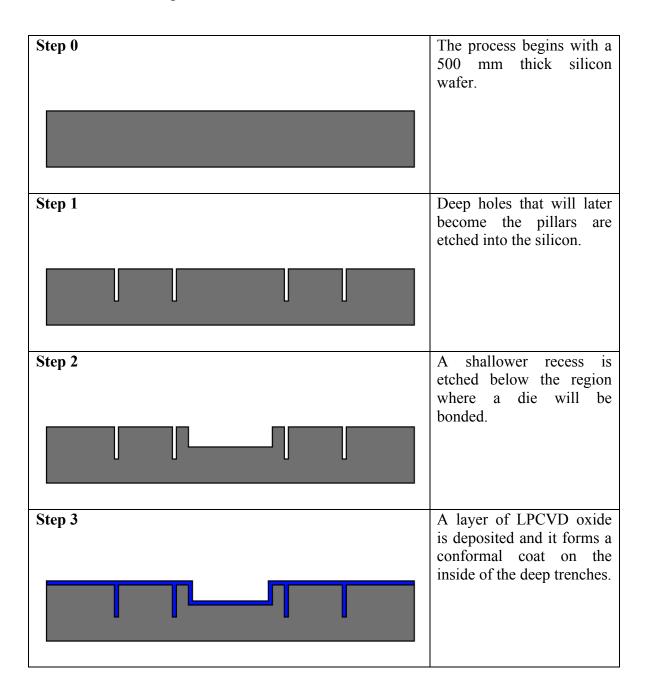

### 4.3 Fabrication Process

This section will outline the fabrication process used to make the TE micro coolers discussed in this chapter. It will begin with an overview of the fabrication process presented in Table 4.1, Table 4.2, and Table 4.3. It will then discuss several of the challenges encountered in implementing this process, and the steps taken to mitigate those challenges. The section will finish with a detailed list of the fabrication steps used to complete the coolers presented in the following sections of this chapter. All processing steps described in the following sections were performed in the Lurie Nanofabrication Facility (LNF) at the University of Michigan.

### Fabrication Process: Part 1 – Thermal Substrate

The fabrication process uses a wafer stack. The top layer implements the main thermal requirements necessary to make the TE micro-cooler, and the fabrication process for this wafer is presented below. It is referred to in the remainder of this chapter as the Thermal Substrate.

Table 4.1: Thermal Substrate fabrication process overview.

| Step 1.0                                                      | The process begins with a 100 µm thick silicon wafer.                                                                                   |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Step 1.1                                                      | PECVD oxide is deposited on the front side of the wafer.                                                                                |

| Step 1.2                                                      | Metal interconnects are deposited on top of the oxide layer.                                                                            |

| Step 1.3                                                      | A shallow DRIE etch is performed on the backside of the wafer.                                                                          |

| Oxide Bridges Metal Interconnects  Isothermal Silicon Regions | A second DRIE etch is performed on the backside of the wafer, releasing the oxide bridges/membranes between isothermal silicon regions. |

# **Fabrication Process: Part 2 – Structural Substrate**

The remaining two wafers are used to add structural support to the Thermal Substrate. Collectively they are referred to as the Structural Substrate in the remainder of this chapter, and the fabrication process is summarized below in Table 4.2.

Table 4.2: Structural Substrate fabrication process overview.

| Step 2.0               | This part of the process begins with a 500 µm thick silicon wafer.                         |

|------------------------|--------------------------------------------------------------------------------------------|

| Step 2.1               | A shallow DRIE etch is performed on the front side of the wafer.                           |

| Step 2.2               | A 100 µm thick glass wafer is bonded to the top of the silicon wafer, covering the recess. |

| Step 2.3  Glass Tether | The glass is etched in concentrated HF solution to create a released glass tether.         |

### Fabrication Process: Part 3 – Completing the Cooler

The cooler fabrication is completed by attaching the Thermal Substrate to the Structural Substrate, and depositing the thermoelectric materials as shown in Table 4.3 below.

The thermal substrate is Step 3.1 anodically bonded to the structural substrate to final complete the structure for the cooler. **Step 3.2** TE The materials TE Materials deposited on top of the wafer stack. First Bi<sub>2</sub>Te<sub>3</sub> is deposited, followed by Sb<sub>2</sub>Te<sub>3</sub>

Table 4.3: Cooler completion process overview.

# 4.3.1 Processing Challenges

### 4.3.1.1 Wafer Selection

Successfully executing the process outlined above required overcoming a number of fabrication challenges, many of which are rooted in the creation of the oxide bridges and the use of  $100~\mu m$  silicon for the top layer of the cooler. A standard  $500~\mu m$  wafer could not be used because of non-uniformity in the DRIE process step. The oxide

bridges were created by a thru-wafer DRIE etch, using the oxide on the wafer surface as an etch stop. However, the STS DRIE system available at the time in the LNF exhibited higher etch rates at the outer edges of the wafer than in the middle of the wafer. As a result, the etch reached the oxide at the edges of the wafer before reaching the oxide near the center of the wafer. The non-uniformity was high enough that the oxide in devices near the edge of the wafer was thinned and weakened before the etch was completed at the center of the device. By using a thinner 100 µm wafer, the etching process reached the oxide with less time delay across the wafer

### 4.3.1.2 Wet Processing

Although the 100 µm thick wafer improved absolute etch uniformity, the use of such a thin substrate meant that several other standard fabrication process had to be modified to complete the process. The first of these included basic handling of the wafers, which were far more fragile than standard silicon substrates. The pressure exerted by turbulence in a normal DI water quench tank, or from agitating the 100 µm thick wafers in a chemical processing tank, was enough to fracture them. When chemical processing was being done, the 100 µm wafers needed to be placed in a cassette along with additional 500 µm thick wafers that alternated slots with the thin wafers. The thicker wafers prevented the water flow from exerting pressure on the thin wafers. The cassette containing the both thin and standard wafers could be placed in a spin-rinse drier (SRD) at the completion of a chemical processing step. This was preferable to hand drying the wafers because pressure exerted on the wafers by the nitrogen gun could also easily fracture them.

Processing steps that could not accommodate a cassette, such as gold etching and developing in AZ400K, required that only one wafer at a time be processed using an individual wafer holder. The wafer was then rinsed in the down-stream side of a cascade rinse tank with the nitrogen bubbler off, before being transferred to a cassette for a final rinse and drying in the SRD. Being able to handle the thin wafers and perform wet processing was an important accomplishment because up to 4 lithography steps needed to be done to the wafers before bonding them.

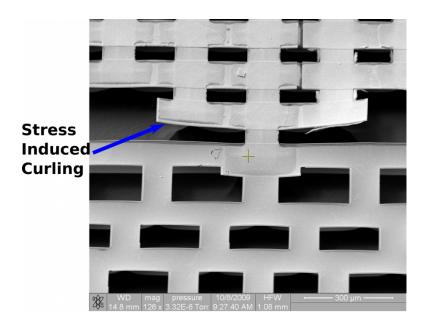

## 4.3.1.3 Oxide deposition

While successful wet chemical processing with the 100 µm wafers only required slight adjustments to normal procedures, the use of thin wafers had a larger impact on other areas of the fabrication process. The use of plasma enhanced chemical vapor deposition (PECVD) oxide deposited at 200 °C was a necessary choice, given the characteristics of 100 µm thick wafers. Oxide films deposited by thermal oxidation, low pressure chemical vapor deposition (LPCVD), and even PECVD at temperatures over 300 °C are denser and have higher mechanical strength than low temperature PECVD oxide. They also have higher levels of stress. Tests were done to use LPCVD oxide films and PECVD films deposited at 380 °C. However, for the anodic bonding that occurs later in the process to be successful, the backside of the wafer must be oxide free. With oxide on only one side of the wafer, the compressive stress in the film is high enough to visibly bow the wafer. It imparts enough curvature that the wafers cannot be clamped to the chuck of the photoresist spinner. The low temperature PECVD, on the other hand, has stress sufficiently low that wafer bow is not a hindrance to further process steps.

# 4.3.1.4 Oxide patterning and Metal Deposition

Patterning the oxide layer and depositing the interconnect metallization did not present a significant processing challenge beyond what was described above in relation to wet processing with the wafers.

## 4.3.1.5 Deep Reactive Ion Etching (DRIE)

Successfully performing DRIE on the 100 µm wafers required specialized processing. During the etch, the wafers are mechanically clamped to a chuck inside the tool, and helium gas flows over the backside of the wafer to aid with heat transfer from the wafer to the chuck. This prevents the photoresist on the wafer from burning, but it also puts pressure on the wafer that is high enough to break substrates with regions that are thinner than 250 µm. To prevent breakage, wafers that are etched deeply must be mounted on a carrier substrate. The normal mounting procedure is to spin a layer of 1827 photoresist (PR) on a carrier wafer. The device wafer is placed onto the layer of PR, and the two-wafer stack is cured in an oven at 110 °C for 30 min. However, if 100 µm thick wafers are mounted in this way and placed in the load lock of the DRIE tool, gas in the photoresist expands with enough force to shatter the 100 µm wafer. In order to process the thin wafers in DRIE, a special carrier wafer needed to be fabricated. The carrier had a pattern of criss-crossed channels 1 mm wide and 100 µm deep etched into a silicon wafer. This carrier was attached to the device wafer using the same PR bonding technique described above. When the photoresist is spun onto the carrier, the resist covers surface of the wafer and sides and bottom of the channels, but it does not fill the channels. However, when pumped to vacuum, the channels allowed the gasses to escape to the edges of the wafer and prevented the wafer from breaking.

An additional challenge associated with the DRIE steps was releasing the carrier from the device wafer without harming the structures. This was particularly true after the second DRIE step, when the oxide membranes were particularly fragile. Normally, wafers that have been bonded together with PR are released by soaking them in PRS2000, and then rinsing them in water. Placing the released wafers in flowing water caused many of the structures to break at the outer ring of oxide. To prevent this, the wafers were placed vertically in a beaker of acetone. After the acetone had dissolved the PR from between the wafers, the device wafer was carefully removed from the beaker and placed in a beaker of isopropyl alcohol to rinse off the acetone. Finally, the wafer was dried on a hot plate.

### 4.3.1.6 Wafer Bonding

Bonding also required a small change from the standard procedure. Normally, alignment of the wafers is performed using the Suss BA-6 bond aligner, but the alignment and chucking mechanism caused the thinned wafers to break. Instead, the wafers were manually aligned using through-hole alignment marks, and then placed in the bonding fixture.

### 4.3.1.7 Thermoelectric Material Integration

Integrating the thermoelectric materials with the structure described above was a significant challenge associated with this process for two reasons. First, the TE thin-films could not be patterned by lift-off or by etching. Lift-off was unavailable because of the high deposition temperature of the films. Most polymers, including the photoresists available in the LNF, will burn if heated to temperatures as high as 250 °C, where the thermoelectric deposition is optimized. When that happens, the patterns become

distorted and residue from the burned photoresist can contaminate the wafer and be difficult to remove. Etching could not be used in this case because of weak adhesion between the thin films and the substrates. Work by a previous University of Michigan student, Luciana da Silva suggested that the films etched unevenly and would quickly delaminate from the wafer [97].

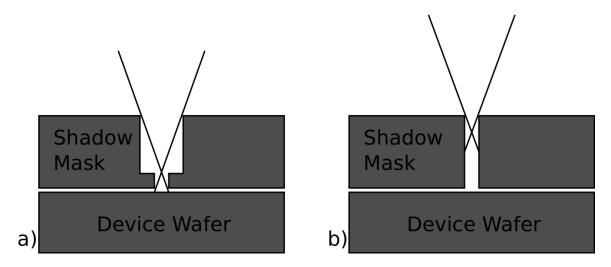

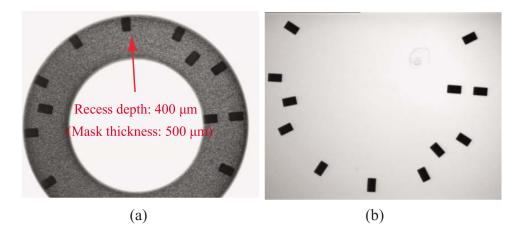

Second, the Bi<sub>2</sub>Te<sub>3</sub>and Sb<sub>2</sub>Te<sub>3</sub> are contaminants for silicon processing, so an effort was made to place the TE deposition as the last step in the fabrication process. By that point the oxide bridges have already been released, so additional processing, particularly the wet processing needed for both etching and lift-off, would not be well tolerated. Instead shadow-masks are used to pattern the TE materials. The shadow-masks, shown in cross section in Figure 4.7, are made of silicon, and require a two-step process. First, large wide recesses are patterned on the backside of the wafer, and etched using DRIE to a depth of approximately ~400 µm. Then the front side of the wafer is masked with the pattern of the TE to be deposited, and it is etched through to the recesses. By thinning the wafer in the areas around the pattern that are being deposited, the shadow-mask interferes less with the flux of incoming material, and smaller, more precise patterns can be realized.

Figure 4.7: Illustration of a shadow mask cross sections (a) with a recess around the pattern, and (b) without a recess around the pattern. Using the recess allows flux impinging the wafer at shallower angles to reach the device wafer. This is important in systems where the source is not located along the axis perpendicular to the center of the wafer.

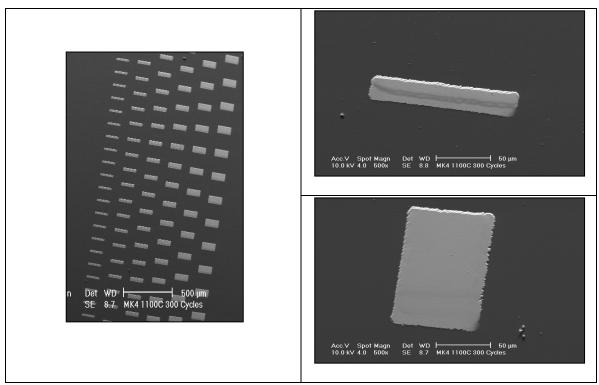

The shadow-mask has through-wafer holes that are inset with a cross pattern, which is used for alignment. On the device wafer there is a complimentary pattern. The two wafers are aligned manually under a microscope, and temporarily clamped together with spring clips. Stainless steel machine screws are then inserted into overlapping holes in the two wafers, and are used with a nut to clamp the wafers tightly during deposition. To prevent the shadow mask from exerting pressure on the fragile areas of the coolers, spacers were needed between the device wafer and the shadow mask. Pieces of  $100 \, \mu m$  silicon were used, and were placed at the sites of clamping screws. Layers of aluminum foil, approximately  $50 \, \mu m$  thick, were also used in some instances. Figure 4.8 shows a TE test pattern with high magnification views of specific features. Figure 4.9 shows top and bottom views of the shadow mask.

Figure 4.8: Images of TE material patterned by shadow masking. (a) The full test pattern. (b) The smallest element in the test pattern. It is 23  $\mu$ m x 130  $\mu$ m. (c) The largest element in the test pattern. It is 77  $\mu$ m x 117  $\mu$ m.

Figure 4.9 (a) View of the top side of a shadow mask showing the recess and the pattern that will be deposited on the cooler. (b) Pattern of the backside of the wafer showing the pattern that will be deposited. Taken from [75].

#### **4.3.2 Detailed Fabrication Process**

#### 4.3.2.1 Thermal Substrate

- 1. A 1.5  $\mu$ m thick layer of SiO<sub>2</sub> is deposited in the GSI PECVD tool with a substrate platen temperature of 200 °C .

- 2. A layer of 1827 photoresist is spun onto the wafers at 1000 rpm for 300 seconds, and the wafers are baked on a hotplate at 110 °C for 90 seconds.

- 3. The wafers are exposed on the MA-6 aligner for 20 seconds. They are developed in MIF 319 for 80 seconds, rinsed for 3 minutes in DI water, and dried in an SRD.

- 4. 400 Å of Cr and 5000 Å of Au are deposited in the Enerjet e-beam evaporator.

- 5. Lift off is performed in acetone with the aid of ultra-sonic agitation. The wafers are rinsed in isopropyl alcohol and dried on a hot plate.

- 6. A layer of 9260 is spun on the backside of the wafer at 2000 rpm for 30 seconds, and baked in an oven for 20 minutes at 90 °C.

- The photoresist is exposed on the MA-6 for 55 seconds. It is developed in AZ400K for 90 seconds, rinsed for 3 minutes in DI water, and dried in an SRD.

- 8. A layer of 1827 is spun onto the backing wafer at 3000 rpm for 30 seconds. The Thermal Substrate is mounted to the spun photoresist, and both wafers are baked at 110 °C for 20 minutes.

- 9. The wafer is etched in the STS DRIE tool for 10 minutes, using the GC standard recipe. This results in an etch that is ~30 mm deep.

- 10. The Thermal Substrate is released from the backing wafer in Acetone. It is rinsed in isopropyl alcohol, and dried on a hot plate.

- 11. A layer of 9260 is spun on the backside of the wafer at 2000 rpm for 30 seconds, and baked in an oven for 20 minutes at 90 °C.

- 12. The photoresist is exposed on the MA-6 for 55 seconds. It is developed in AZ400K for 90 seconds, rinsed for 3 minutes in DI water, and dried in an SRD.

- 13. A layer of 1827 is spun onto the backing wafer at 3000 rpm for 30 seconds. The Thermal Substrate is mounted to the spun photoresist, and both wafers are baked at 110 °C for 20 minutes.

- 14. The wafer is etched in the STS DRIE tool for 22 minutes, using the GC standard recipe. This etches through the wafer and stops on the oxide layer.

- 15. The Thermal Substrate is released from the backing wafer in Acetone. It is rinsed in isopropyl alcohol, and dried on a hot plate.

- 16. Both the front and the back sides of the wafer are cleaned using O2 plasma.

# 4.3.2.2 Mechanical Supporting Substrate

- 1. A layer of 9260 is spun on the backside of the wafer at 2000 rpm for 30 seconds, and baked in an oven for 20 minutes at 90 °C.

- The photoresist is exposed on the MA-6 for 55 seconds. It is developed in AZ400K for 90 seconds, rinsed for 3 minutes in DI water, and dried in an SRD.

- 3. The wafer is etched in the STS DRIE tool for 12 minutes, using the GC standard recipe.

- 4. The photoresist is stripped using PRS 2000. The wafer is rinsed for 3 minutes in DI water and dried using an SRD.

- 5. A 100  $\mu$ m thick pyrex glass wafer is anodically bonded to the top side of the silicon wafer using the SB6e. The bond is performed at 450 °C and 400 VDC.

- 6. The wafer is cleaned using a 1:1 mixture of H<sub>2</sub>O<sub>2</sub> and H<sub>2</sub>SO<sub>4</sub> (piranha) for 10 minutes. It is rinsed for 3 minutes in DI water and dried using an SRD.

- 7. The wafer is etched in buffered hydrofluoric acid (BHF) for 5 minutes. It is rinsed for 3 minutes in DI water and dried using an SRD.

- 8. 1000 Å of Cr and 5000 Å of Au are deposited in the Enerjet e-beam evaporator.

- 9. A layer of 9260 is spun on the backside of the wafer at 2000 rpm for 30 seconds, and baked in an oven for 20 minutes at 90 °C.

- 10. The photoresist is exposed on the MA-6 for 55 seconds. It is developed in AZ400K for 90 seconds, rinsed for 3 minutes in DI water, and dried in an SRD.

- 11. The Au and Cr layers are etched using wet etchants with a 3 minute rinse in DI water following each etch. The wafer is dried in an SRD.

- 12. The glass layer is etched though using concentrated HF solution for 18 minutes.

- 13. The photoresist is stripped using PRS 2000. The wafer is rinsed for 3 minutes in DI water and dried using an SRD.

- 14. The Au and Cr layers are stripped with a 3 minute rinse in DI water following each etch. The wafer is dried in an SRD.

## 4.3.2.3 Wafer completion

- The thermal substrate and structural substrate are manually aligned. A

wafer with a thin layer of oxide is placed on top of the Thermal Substrate

to prevent intermetallics of gold from forming with the bond chuck during

bonding. The Thermal and Structural substrates are bonded at 350 °C and

400 VDC.

- 2. The shadow mask for the Bi<sub>2</sub>Te<sub>3</sub> pattern is aligned to the device wafer and clamped. The wafer is loaded into the TE evaporator and pumped to a pressure of less than 2E-6 Torr. Bi<sub>2</sub>Te<sub>3</sub> is deposited using a flux ratio of Te:Bi of 3.0:1, and substrate temperature of 260 °C. After deposition the wafer is allowed to cool to less than 100 °C before venting the chamber.

- 3. The shadow mask for the Sb<sub>2</sub>Te<sub>3</sub> pattern is aligned to the device wafer and clamped. The wafer is loaded into the TE evaporator and pumped to a pressure of less than 2E-6 Torr. Sb<sub>2</sub>Te<sub>3</sub> is deposited using a flux ratio of Te:Sb of 2.4:1, and substrate temperature of 230 °C. After deposition the wafer is allowed to cool to less than 100 °C before venting the chamber.

# 4.4 5-Stage Coolers

# 4.4.1 Specifications

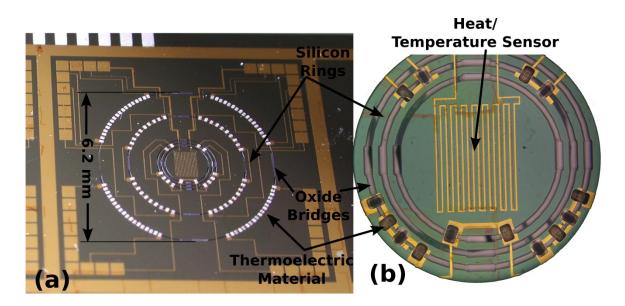

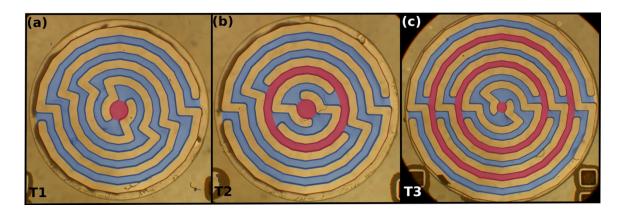

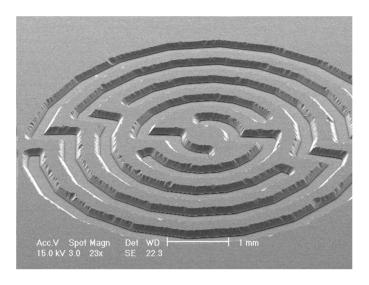

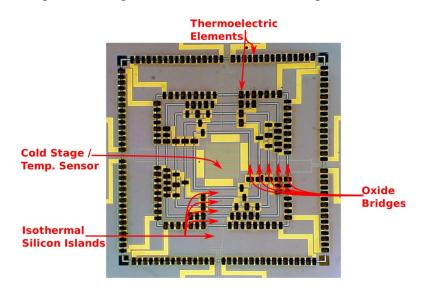

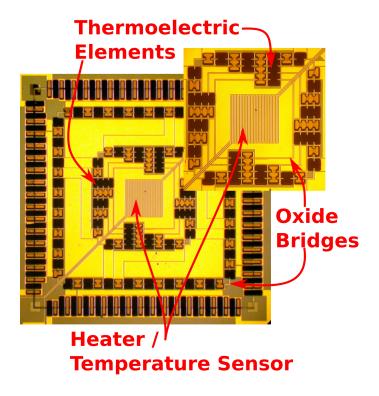

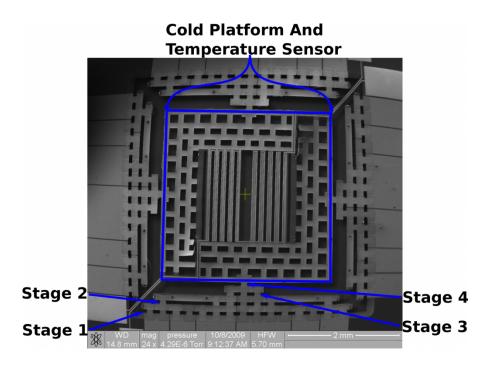

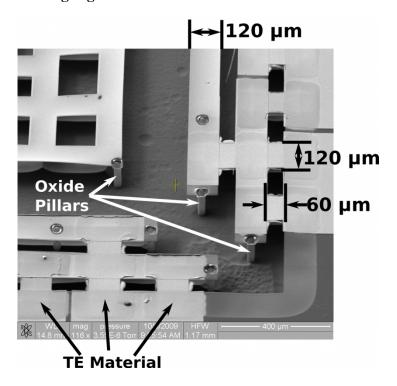

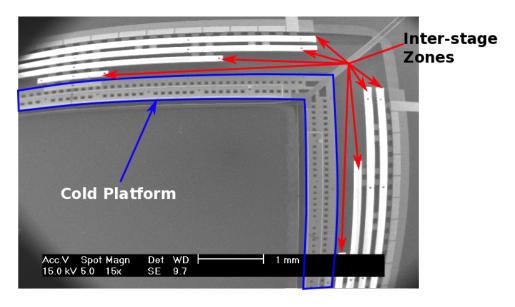

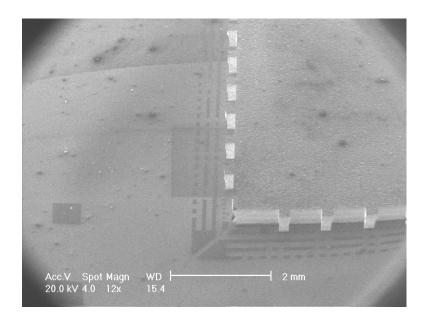

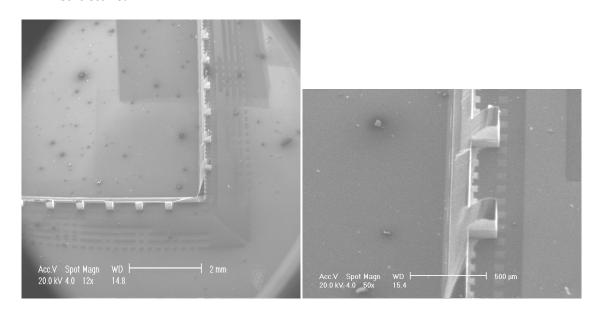

Initial devices fabricated using the process above were designed to validate the process and test the thermal resistance of the structures. They were designed secondarily to demonstrate a functioning multi-stage micro-scale cooler. However, the cooler design used in these test structures was not rigorously optimized. The initial devices all had 5 stages arranged in concentric circles as shown in Figure 4.10. The thermocouples were 30 μm long and 100 μm wide. The first stage had 36 TC, the second stage had 20, and the third, fourth and fifth stages had 4, 2, and 1 TCs, respectively. The stages were arranged in concentric circles with stage 1 having a diameter of 6.2 mm. The full design parameters are summarized in Table 4.4. The 1<sup>st</sup> and 2<sup>nd</sup> stages could both be driven by individual currents, and the inner three stages could be driven by a third input current. This combination of oxide bridges and metallization will be referred to as M3. Four variations of the glass supporting structure were tested. The first variation (T1) bonded only to the center of the cooler. The second variation (T2) supported the center and silicon between the 2<sup>nd</sup> and 3<sup>rd</sup> stages. The third variation (T3) supported the silicon between the 1<sup>st</sup> and 2<sup>nd</sup> stages, between the 2<sup>nd</sup> and 3<sup>rd</sup> stages and at the center, and the 4<sup>th</sup> variation (T4) had no supporting tether at all. T1, T2 and T3 are shown in Figure 4.11 and Figure 4.12 showns an SEM of the T2 tether design.

Table 4.4: Critical dimensions of the 5-Stage thermoelectric cooler

| Stage             | 1     | 2     | 3     | 4     | 5     |

|-------------------|-------|-------|-------|-------|-------|

| Diameter of Stage | 6.2mm | 4.1mm | 2.1mm | 1.8mm | 1.5mm |

| Number of TCs     | 36    | 20    | 4     | 2     | 1     |

| TE Width | TE Length | TE Thickness | TE Contact Area | Oxide Thickness |

|----------|-----------|--------------|-----------------|-----------------|

| 80μm     | 30 μm     | 2μm          | 50μm x 80μm     | 1.5µm           |

Figure 4.10: (a) A top view of a 5-stage cooler built using the Silicon-Glass-Silicon process. (b) The inner three stages of the same 5-stage cooler, showing the temperature sensor.

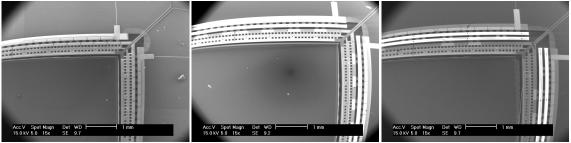

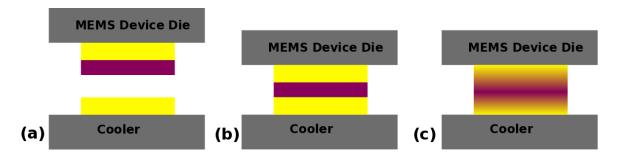

Figure 4.11: Pictures of (a) the T1 tether, (b) the T2 tether, and (c) the T3 tether designs. The pictures have been artificially colored to increase the contrast to the background and to illustrate different regions of the tether designs. Red areas indicate the regions that will be bonded to the Thermal Substrate. Blue regions are unbonded.

Figure 4.12: An SEM image of the T2 tether design used with a 5-Stage cooler. This shows the tether suspended over of 10  $\mu$ m recess in a silicon wafer.

Additionally, 3 sets of test structures were placed on the wafer simply to test the thermal resistance of the cooler structure with as little metal as possible present. Two sets of these devices were structurally identical to the cooler structures except for the metallization. One set implemented only a single resistive temperature sensor at the center of device. The combination of metal interconnects and oxide bridges will be

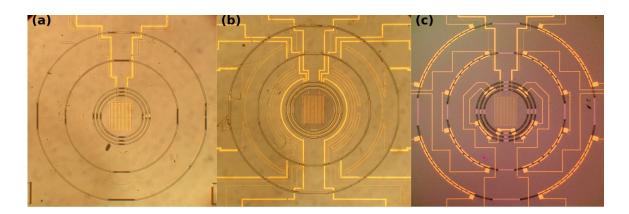

referred as design M1. A second set of devices contained resistive temperature sensors on the silicon between the 1<sup>st</sup> and 2<sup>nd</sup> stages, between the 2<sup>nd</sup> and 3<sup>rd</sup> stages, and at the center of the device. This combination of metal interconnects and oxide bridges will be referred as design M2. Variations of both these sets included devices with all 4 glass tether designs. A third set of devices with 60µm long oxide bridges were implemented for testing thermal isolation. These all used the T1 tether design. This structure was used to test the upper limits of thermal resistance that could be achieved with this fabrication process. The combination of metal interconnects and oxide bridges will be referred to as design M4. M1, M2, and M3 are shown in Figure 4.13

Figure 4.13: Top views of three metal designs, showing (a) M1, (b) M2, and (c) M3. The metallization used in M1 is also used in the M4 pattern (not shown) but the oxide bridges are longer in the M4 design.

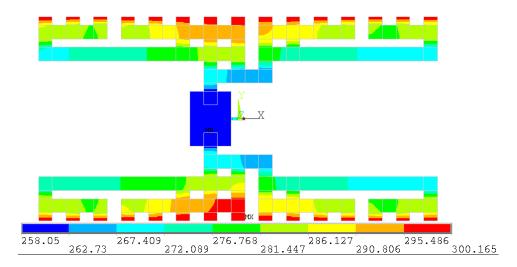

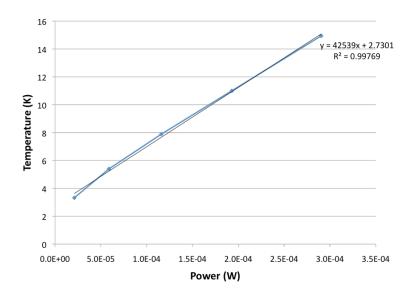

### 4.4.2 Results and Discussion

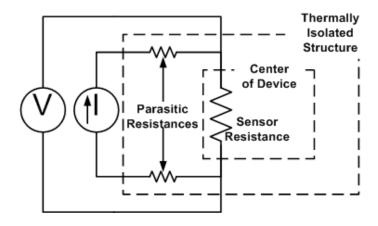

The structure was first tested to verify the thermal isolation between the center of the device and the substrate. The measurement was taken by operating the thermistor in a four-point configuration, as illustrated in Figure 4.14. The current through and voltage across the resistor were recorded, and resistance and power dissipation were calculated. Then the input current was increased and the measurements were repeated. The

increased power dissipated in the resistor resulted in an increase in temperature at the center of the device. The temperature change was sensed as an increase in the calculated resistance of the thermistor. By using the thermal co-efficient of resistance for gold, the observed change in resistance was used to calculate the change in temperature.

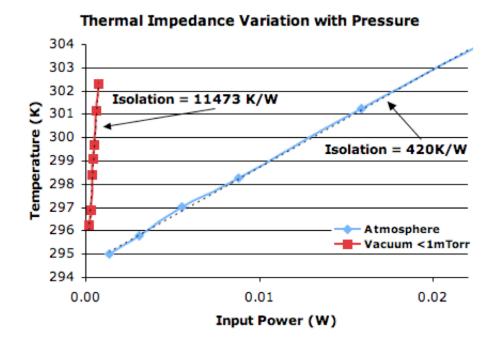

Measurements were taken at several different current levels, and the relationship between input power and temperature was analyzed using a linear regression. The slope of the line, with units of Kelvin/Watt, corresponds to the thermal resistance of the completed structure. Measurements were first performed at atmospheric pressure on devices that did not yet have the thermoelectric materials. The results showed thermal isolation values between 300 K/W and 600 K/W. Then the wafer was placed in a vacuum probe station and tested at pressures of less than 10mTorr. At low pressure the devices showed thermal resistances between 8000 K/W and 16300 K/W. The wide range in values is a result of variations in the design described above. An example of data taken at atmosphere and under vacuum is shown in Figure 4.15 and a summary of the cross-wafer performance, indicating the various designs used, is given in Figure 4.16. This result also shows the importance of operating at vacuum. At atmosphere, the parasitic thermal conduction due to air is an order of magnitude greater than the thermal conduction of the TE. In Chapter 3, it was shown that when this is the case, the expected cooling is only a small fraction of what the TE material is capable of achieving.

Figure 4.14: A schematic representation of the thermal isolation measurement circuit. The four-point measurement system is used to avoid measuring changes in resistance due to parasitic elements that are not located at the center of the device.

Figure 4.15: Thermal resistance measurement of the 5-stage cooler in air and in vacuum. The thermal resistance in vacuum is 27 times higher than the thermal resistance in air.

|   | В     | С              | D              | E              | F              | G              | н              | I              | J     |

|---|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-------|

|   |       |                |                |                | hole           |                |                |                |       |

| 4 |       | hole           |                |                |                |                |                | hole           |       |

| 5 |       | 14487<br>M1:T3 | 12507<br>M1:T2 | 12106<br>M3:T3 | 10367<br>M3:T4 | 8503<br>M3:T1  | 9978<br>M3:T2  | 16812<br>M4:T1 |       |

| 6 | align | 15835<br>M1:T1 | align          |                |                |                | align          |                | align |

| 7 |       | 14047<br>M1:T1 | 14058<br>M1:T2 | 12006<br>M3:T3 | 11473<br>M3:T4 | 11486<br>M3:T1 | 9980<br>M3:T2  | 16225<br>M4:T1 |       |

| 8 |       | hole           | 13577<br>M1:T2 |                | 12905<br>M2:T4 | 13729<br>M2:T1 | 11819<br>M2:T2 | hole           |       |

|   |       |                |                |                | hole           |                |                |                |       |

Figure 4.16: A wafer map showing thermal resistance measurements across several variations of cooler designs. Die in green were testable. The top number indicates thermal resistance in K/W, and V-x indicates a variation designator as explained in the text.

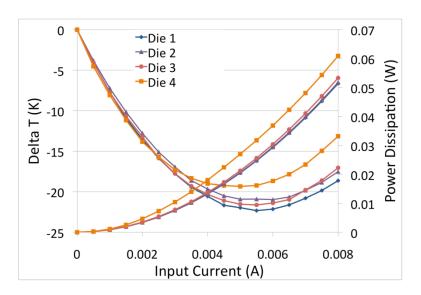

A modified temperature measurement scheme was used when evaluating the performance of the coolers. As a result of limited access to the wafer in the vacuum chamber, a four-point measurement could not be used at the time these wafers were tested. Instead a two-point measurement was used on the thermistor. This resulted in some measurement uncertainty because the resistance being measured between the contacts was not undergoing a uniform temperature change. To place maximum and minimum bounds on the temperature change, observed changes in resistance were converted to temperature changes in two ways. First, it was assumed that change in resistance was due to a uniform cooling of the entire structure, and resulted in the minimum bound for the actual cooling. Next, it was assumed that only the center of the device was cooled, and only the resistance at the center of the device contributed to the

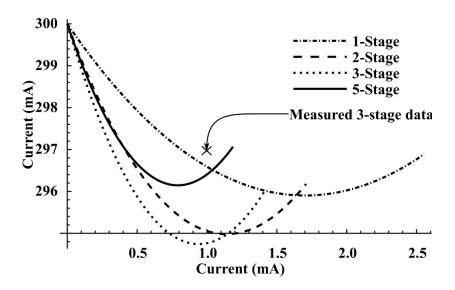

observed change in resistance. This resulted in the maximum bound on the observed cooling. Reported data is the average of the two bounds. Using this measurement scheme, cooling performance was evaluated using two different configurations of the cooling circuit. In the first configuration, all five stages of the cooler were connected in series. The devices were tested under vacuum, and a maximum temperature between the device center and the substrate of 3.45 °K was achieved. The average cooling for all four tested devices was 3.03 °K degrees.

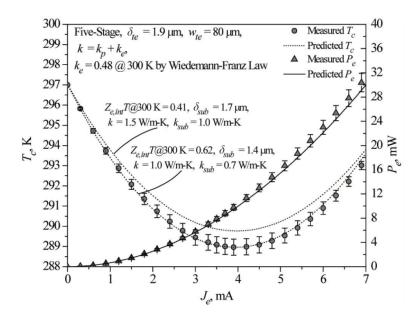

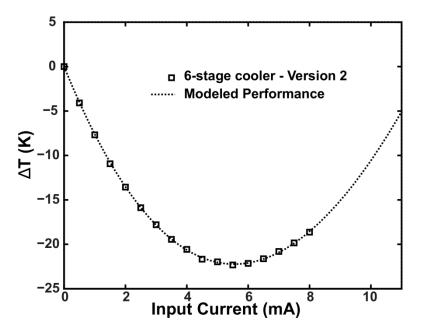

In the second configuration, only the outer two stages of the device were used, again connected in series, and this resulted in a maximum achieved cooling of 3.8 °K. In this configuration, the average cooling was 3.26 °K. Later fabrications of the same cooler design produced better results and were able to utilize the 4 point measurement scheme for temperature sensing. The best of these coolers achieved 8K of cooling, and matched well with the performance predicted by the model, as shown below in Figure 4.17.

Figure 4.17: Measured performance of a full 5-stage cooler plotted versus input current. Power consumption is plotted using the right hand axis, and modeled cooling performance is plotted using nominal (based on the properties reported in Chapter 2) and fitted material properties.

### 4.5 6-Stage Coolers

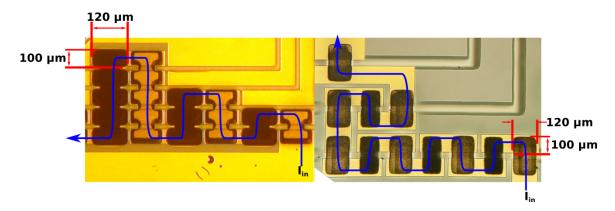

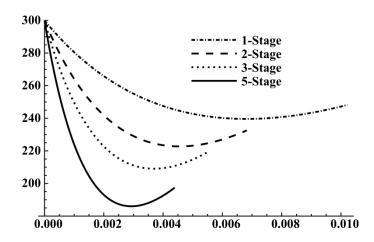

To increase performance beyond the initial 5-Stage device new coolers were designed. The layout of these devices was informed by the 1-D Mathematica and Matlab based models described in Chapter 3. Both the number of stages and the distribution of thermocouples were changed from the previous version. The new version of the cooler included 6 stages instead of 5, and the ratio of thermocouples in consecutive stages was changed to be 2 for all stages, instead of varying as in the five stage cooler. By decreasing the spacing between TCs, the overall size of the cooler was not increased, despite the addition of the sixth stage. The geometry of the TE elements was also changed slightly. The widths of the Bi<sub>2</sub>Te<sub>3</sub> and Sb<sub>2</sub>Te<sub>3</sub> was changed to compensate for the difference in Seebeck coefficient and resistance. The Bi<sub>2</sub>Te<sub>3</sub> was 100 µm wide while the

Sb<sub>2</sub>Te<sub>3</sub> was 120um wide. The length of the TE element was kept constant at 30  $\mu$ m, but the contact area were increased to 100  $\mu$ m x 100  $\mu$ m. The properties are summarized in Table 4.5, and a top-down image of the cooler is shown in Figure 4.18.

Figure 4.18: Top view of the 6-Stage cooler, Version 1. It shows the thermoelectric elements, the temperature sensor, and the silicon rings.

Table 4.5: Critical dimensions of the Version-1 6-Stage thermoelectric cooler

| Stage         | 1      | 2      | 3      | 4      | 5      | 6      |

|---------------|--------|--------|--------|--------|--------|--------|

| Stage width   | 5.7 mm | 3.5 mm | 3.0 mm | 2.5 mm | 2.0 mm | 1.5 mm |

| Number of TCs | 64     | 32     | 16     | 8      | 4      | 2      |

| TE Width                                                                                   | TE<br>Length | TE Thickness                                                                                                                | TE contact area | Oxide<br>Thickness |

|--------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|

| <b>Sb<sub>2</sub>Te<sub>3</sub>:</b> 120 μm<br><b>Bi<sub>2</sub>Te<sub>3</sub>:</b> 100 μm | 30 μm        | <b>Sb</b> <sub>2</sub> <b>Te</b> <sub>3</sub> <b>:</b> 3.8 μm <b>Bi</b> <sub>2</sub> <b>Te</b> <sub>3</sub> <b>:</b> 2.9 μm | 100 μm x 100 μm | 1.8µm              |

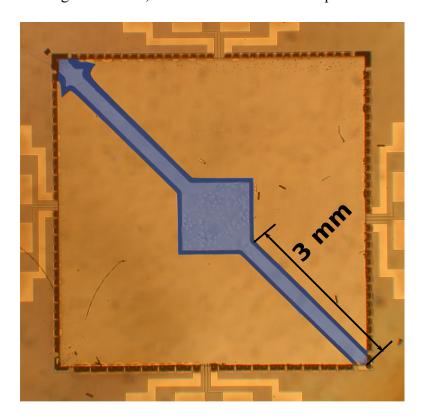

The glass tether structure was also changed for this revision of the cooler. Instead of long wrapped coil structures, such as the one presented in Figure 4.12, the new devices had a straight tether which spanned from corner-to-corner of the device as shown in Figure 4.19. The tether is still made using 100 µm thick glass, and is designed to have an

average width of 100  $\mu$ m, but the length is significantly shorter than in the previous designs. Each half of the tether is 3 mm long. Assuming a thermal conductivity for glass of 1.15 W/m-K, this results in a total thermal conductivity of 7.7E-6 W/K. This is still an order of magnitude less than the thermal conductivity presented by the oxide bridges, which for this design present a total thermal conductance of 8.5E-5 W/K. It therefore has only a mild influence on the cooling ability of the device. For, example without a tether the device above is modeled as being able achieve  $\Delta T$ =23.8 K. With the tether the cooler is modeled as reaching  $\Delta T$ =22.8 K, less than a 5% decrease in performance.

Figure 4.19: An image of the tether used for Version 2 of the 6-stage cooler. The picture has been artificially colored to increase the contrast to the background.

# 4.5.1 Results and analysis

As before, the coolers included a Cr/Au resistive temperature sensor that was used to measure the cooling achieved by the device, and the device was tested in a Lakeshore

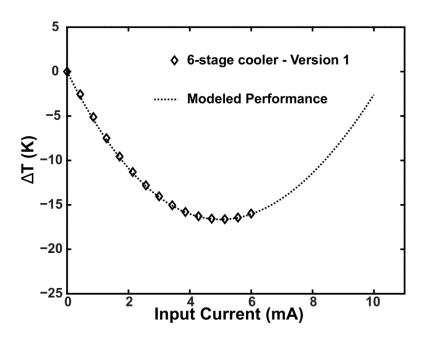

cryonics vacuum probe station. The fabricated coolers were tested with input current varying from 0 mA to 6.5 mA. The resistive temperature sensor dissipated 100  $\mu$ W of power during the testing. This amount of power dissipation by the temperature sensor raises the temperature of the cold stage above ambient by less than 1 K. Figure 4.20 shows the measured data for a 6-stage cooler. The maximum temperature difference observed was 16.6 K, and occurred with a current input of 5.1 mA. The total resistance of the cooler was 1071  $\Omega$ , resulting in a total power consumption of 26 mW.

Additional analysis of the data was performed using the Mathematica-based analytical model described in Chapter 3. To estimate the effective material properties that had been achieved in-situ, the model was fitted to the collected data using the material properties as fitting parameters. The fit was performed as if both deposited TE materials had the same properties. Contact resistance was first used to adjust the total resistance of the simulated cooler to the measured resistance of the actual cooler, assuming a resistivity of 20  $\mu\Omega$ -m. (The same results can be achieved by assuming contact resistivity as 0  $\Omega$ -m, and varying the resistivity of the thin films to match the total resistance of the completed cooler). Next, the Seebeck coefficient was adjusted so that the measured optimum current matched the simulated value, given the measured resistance of the cooler. Finally the thermal conductivity of the TE material was adjusted to fit the magnitude of the maximum simulated  $\Delta T$  with the measured results. The model used included the SiO<sub>2</sub> membrane, which was assumed to have a thermal conductivity of 1.15 W/m-K. For this version of the 6-stage cooler, Version 1, the fitting process estimated the Seebeck coefficient to be 180  $\mu$ V/K, and the thermal conductivity to be 1 W/m-K.

Figure 4.20: Measured performance of Version 1 of a 6-stage cooler, plotted together with simulated performance that has been fit to measured data to extract the material properties of the TE.

## 4.5.2 Modified 6-Stage Cooler (Version 2)

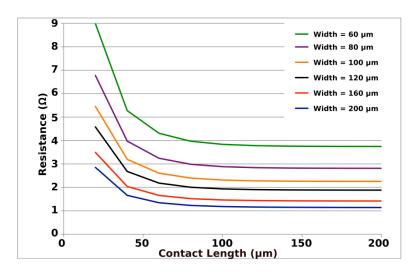

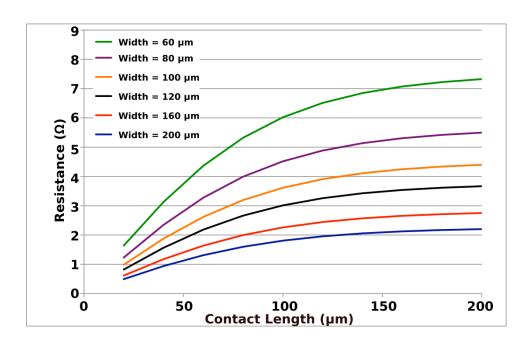

The 6-stage cooler was updated with a number of design modifications to enhance cooler performance. Most significantly, the size and shape of the TE-metal contact was changed in an effort to reduce contact resistance. To do this, several changes were made to the contact regions. For TC with a large spatial separation between adjacent stages, such as the space between stage 1 and stage 2, or stage 2 and stage 3, the size of the contact region was increased. To determine the best shape for these contacts, 3-D finite element simulations were performed using a variety of geometries. These results are plotted in Figure 4.21. They show that any increase in the size of the contact region is helpful, but increasing the width of the contact region provides a greater benefit than increasing the length. This is particularly true for contacts longer than 100 µm. Where possible, contacts with a 200 µm width and a 100 µm length were used. However, at stage 1 the perimeter was confined by overall size constraints, and there was not enough

room to add such wide contacts. In this case, the contacts were set to be 100 µm by 200 µm long. To accommodate all of the thermocouples in the 2<sup>nd</sup> stage using the new, larger contact scheme, the perimeter needed to be increased. The length of one side of the 2<sup>nd</sup> stage was 4.23 mm, compared to 3.5 mm in Version 1.

Figure 4.21: Simulated TE-metal contact resistance for a variety of contact geometries. The assumed TE resistivity for these simulations is 20  $\mu\Omega$ -m, and the contact resistivity is 1E-8  $\Omega$ -m². The current enters the contact in the TE layer and leaves in the metal layer.

In addition, it was observed that the total number of contacts at the inner stages could be reduced by passing individual TE elements across multiple stages, while at the same time reducing the size of the silicon rings acting as thermal conductors. This concept is illustrated in Figure 4.22. The contact regions are still deposited over gold as before, and the size of these contacts was also informed by FEM simulations. Contacts that are 200  $\mu$ m and 100  $\mu$ m long were chosen. The results of those simulations are shown in Figure 4.23. The purpose for these modifications was to reduce the effect of contact resistivity on the performance of the cooler. A cooler fabricated with this process had a resistance of 854  $\Omega$ , compared to 1071  $\Omega$  for version 1. A top view of the revised 6-stage cooler is shown in Figure 4.24. In addition to the changes made regarding the

contacts, the entire surface of the inter-stage regions were coated with gold to minimize any potential radiation losses.

Figure 4.22: Comparison of contacts in Version 1 (right side) and Version 2 (left side). The images show contact dimensions and the current path through 3 stages of each cooler.

Figure 4.23: Simulated resistance of a TE element deposited over gold. The TE resistivity is assumed to be 20  $\mu\Omega$ -m, and the contact resistivity is 1E-8  $\Omega$ -m<sup>2</sup>. The current enters and leaves the element through the TE material.

Table 4.6: Critical dimensions of the Version-2 6-Stage thermoelectric cooler

| Stage         | 1      | 2       | 3       | 4       | 5       | 6      |

|---------------|--------|---------|---------|---------|---------|--------|

| Stage Width   | 5.4 mm | 4.23 mm | 2.28 mm | 2.02 mm | 1.76 mm | 1.5 mm |

| Number of TCs | 64     | 32      | 16      | 8       | 4       | 2      |

| TE Width                                               | TE     | TE Thickness                                | TE Contact Area | Oxide     |

|--------------------------------------------------------|--------|---------------------------------------------|-----------------|-----------|

|                                                        | Length |                                             |                 | Thickness |

| <i>Sb</i> <sub>2</sub> <i>Te</i> <sub>3</sub> : 100 μm | 30 μm  | <b>Sb<sub>2</sub>Te<sub>3</sub>:</b> 3.2 μm | 200 μm x 100 μm | 1.5 μm    |

| <i>Bi<sub>2</sub>Te<sub>3</sub>:</i> 100 μm            |        | <i>Bi<sub>2</sub>Te<sub>3</sub>:</i> 2.7 μm |                 |           |

Figure 4.24: Top view of the 6-stage cooler, Version 2. The inset highlights the thermoelectric elements at the inner 4 stages, and illustrates how a single element can span multiple stages.

### 4.5.3 Test Results

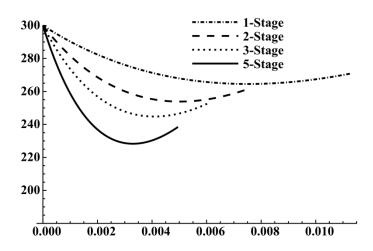

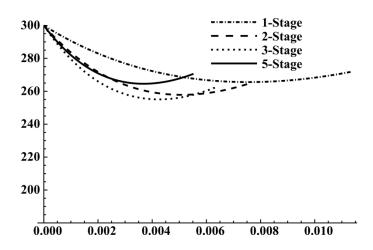

Testing was again performed under vacuum using a Lakeshore Cryogenics vacuum probe station. The temperature at the center of the cooler was measured using a resistive thermal temperature sensor fabricated in the chrome/gold interconnect layer. A source/meter with four point sensing capability was used to supply 100 uW of power to the sensor and to measure the voltage across the sensing element. Current was supplied to the thermocouples by a second source/meter, and an automated test program was used to test the cooler at a variety of input currents. Figure 4.25 shows the current vs. temperature relationship of several devices, with the best performing device achieving a temperature differential of 22.2 K at an input current of 5.5 mA. This corresponds to a total power consumption of 24.7 mW.

The Mathematica-based analytical model was fitted to this version of the cooler in same way that it was fitted to version 1 of the 6-stage cooler. The fitted curve shown with the measured data in Figure 4.26 indicates a thermal conductivity for the TE material of 1 W/m-K, but the Seebeck is lower at 166  $\mu$ V/K. This physical variation in TE material between the coolers is likely due to inaccurate control of material flux rates and substrate temperatures inside the deposition chamber.

To understand how the structure of the cooler affected the overall results, the ideal model was fitted to the data and used to calculate an effective Z. This analysis answers the question: In the absence of parasitic thermal conductance and parasitic resistance, what intrinsic figure of merit would produce a 6-stage cooler with the measured performance curve? The performance of Version 1 would be replicated by using a material with a Z of 1.6E-4 K<sup>-1</sup>, corresponding to a ZT of 0.048 at 300 K. Version 2 produced a slightly better result, requiring material with a Z of 2.2E-4 K<sup>-1</sup>, or a ZT of 0.066 at 300 K. However, both are low compared to the intrinsic material properties described in Chapter 2. This indicates that the TE material is not being effectively utilized. As already discussed, this is most likely due to the excess oxide used in the inner stages of the coolers.

Figure 4.25: : Measured performance of several Version 2, 6-stage coolers plotted versus input current. All demonstrate cooling of greater than 19 K.

Figure 4.26: Measured performance of Version 2 of a 6-stage cooler, plotted together with simulated performance that has been fit to measured data to extract the material properties of the TE.

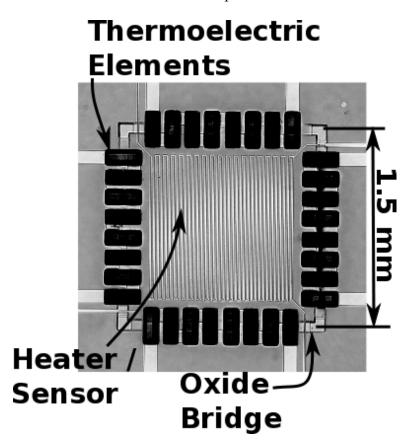

# 4.6 1-Stage cooler

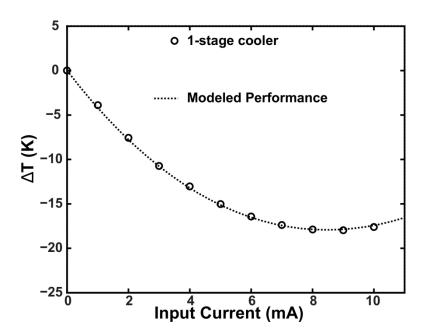

A 1-stage cooler was also fabricated on the same layout with version 2 of the 6-stage cooler. The legs of the TCs were 60 µm long by 100 µm wide, and the contacts

were 100 µm x 100 µm. There were 16 total TCs, and the width of the stage was 1.5 mm. A top-down view of the 1-stage cooler is shown in Figure 4.27. The 1-stage cooler was fabricated on the same substrate as Version 2 of the 6-Stage cooler, and was tested using the same procedure as the previous 6-stage coolers. A plot of cooler performance versus input current is shown in Figure 4.28. The 1-stage cooler was able to achieve a temperature differential of 17.9 K at a current input of 8.5 mA.

Figure 4.27: Top view of a single stage cooler with 16 TCs.

Figure 4.28: Measured performance of a 1-stage cooler, plotted together with simulated performance that has been fit to measured data to extract the material properties of the TE.

Using the same curve fitting technique described above, the average Seebeck coefficient was found to be 185  $\mu$ V/K, again with an estimated thermal conductivity of 1 W/m-K. The effective Z was also calculated for the 1-stage cooler and found to be 2.6E-4 K<sup>-1</sup>, corresponding to a ZT of 0.14. While significantly closer to the measured intrinsic value, this low number indicates that the performance of the 1-stage cooler is also hampered by parasitic effects due to contact resistance and the presence of the oxide membrane. This Seebeck coefficient is larger than the value found for the Version 2 6-stage cooler described above, even though both were fabricated on the same wafer. However, it has previously been shown that the Seebeck coefficient of the coevaporated thin films is closely related to the substrated temperature during deposition [74]. In the case of the 6-stage cooler, the center stages are highly isolated from the general substrate and thus the temperature of inner stages of the cooler may vary from the temperature of

the substrate during deposition. This likely degrades the quality of the material at the inner stages.

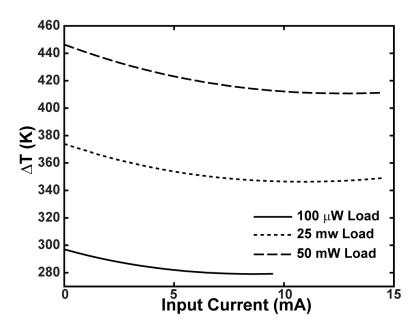

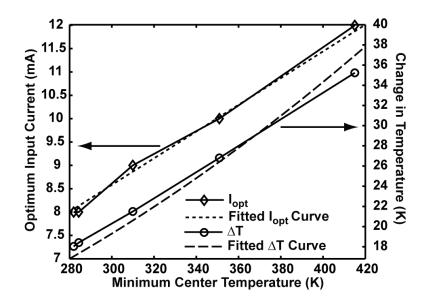

### 4.6.1.1 Thermally Loaded Testing

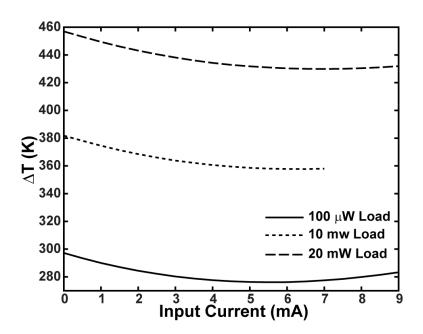

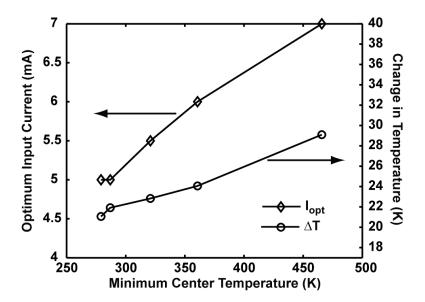

Both the 1-stage cooler and version 2 of the 6-stage cooler were tested under thermal loads. A resistive temperature sensor supplied loads of varying magnitude. As the thermal load was raised, both coolers were able to generate higher differences in temperature between their off states and their optimum current point. In addition, both the coolers exhibited an increase in the magnitude of the optimal current. With the cooler off, a 50 mW load was applied, raising the center of the 1-stage device to 450.3 K. When a current was applied, I<sub>opt</sub> was found to have increased to 12 mA, and the center region was cooled to 415.0 K. This represents a change of 35.3 K, compared to only 18.0 K using an 8 mA current when the device was loaded with 100 uW. Similarly with a 25 mW load, the 6-stage device was able to reduce the temperature of the cooler region from 494.9 K to 465.8 K, a change of 29.1 K with an optimum current of 7 mA. This apparent increase in performance is a result of the temperature dependence of  $\Delta T_{max}$  as described by Eqn. 3.9. The data from the 1-stage cooler is shown in Figure 4.29 and Figure 4.30 along with curves fitted to the ideal cooling equations. The change in temperature of the center is fitted to Eqn. 3.9 and results in a calculated Z=4.3E-4±2.6E-5 K<sup>-1</sup> with a 95% confidence interval. This corresponds to a ZT of 0.13±0.007, which is similar to the ZT value calculated above for the 1-Stage cooler. The relationship between temperature and the optimum current was also fitted to Eqn. 3.7, and produced  $\alpha/R_e=2.87E-5\pm5E-7$ , and fits the data with a sum of squares error of 5.56E-8. These curves fit the data well, and provide a reasonable estimate of the figure of merit where compared to the earlier calculations based on the cooling vs current curves. The data for the 6-stage cooler is presented in Figure 4.31 and Figure 4.32. However, because the model of a 6-stage cooler is much more complex, it is difficult to extract a value of effective Z from this data.

The lower loads were used to measure the thermal resistance of the total structure. A 1-stage cooler increased 2.7 K with a 1 mW load, leading to a calculated thermal resistance of 2700 K/W. This indicates that with a 6.6 mW load, and using the optimum input current,  $\Delta T$ =0. At this operating point the cooler uses 14.6 mW of power giving it an approximate COP of 0.45. The Version 2, 6-Stage cooler that was tested with thermal loads increased 8.9 K for a base temperature of 379.2 with a 1 mW load. It used 20.8 mW of power. This corresponds to 8900K/W thermal resistance, 2.3 mW of load at  $\Delta T$ =0, and an approximate COP of 0.1.

Figure 4.29: A 1-stage cooler tested at various thermal loads. The temperature change achieved and the optimum current both increase as the input load increases.

Figure 4.30: Variation in  $\Delta T$  and  $I_{opt}$  with respect to cold stage temperature for a 1-stage cooler. The ambient temperature is maintained at 300 K, and the temperature of the center region is increased by applying a thermal load with a resistive element.

Figure 4.31: A Version 2 6-stage cooler tested at various thermal loads. The temperature change achieved and the optimum current both increase as the input load increases.

Figure 4.32: Variation in  $\Delta T$  and  $I_{opt}$  with respect to cold stage temperature for a 6-stage cooler. The ambient temperature is maintained at 300 K, and the temperature of the center region is increased by applying a thermal load with a resistive element.

## 4.7 Process and Design Shortcomings

#### 4.7.1 Parasitic Thermal Conduction

Although the process detailed in the beginning of this chapter allowed for the fabrication of coolers with moderate temperature differentials and at low power consumption levels, it still presented shortcomings that affected both performance and usefulness in an integrated system. First, the oxide bridges covered nearly the entire perimeter of each stage. Although the oxide was thinner than the TE, this arrangement meant that the total cross section of oxide spanning each stage was nearly as large and in some cases much larger than the cross-section of the TE. For example, consider the  $6^{th}$  stage in the device above. It has two TCs that are 30  $\mu$ m x 100  $\mu$ m x 2.5  $\mu$ m. They span

a bridge that is 30  $\mu$ m long and has a perimeter of 6 mm and a thickness of 1.5  $\mu$ m,. The TCs will have total thermal conductance of 3.8e-5 W/K, while the oxide will have a thermal conductance of 3.4e-4 W/K. Remembering from Chapter 3 that the effective figure of merit ( $Z_{eff}$ ) is proportional to  $K_{TE}/K_{par}$ , this calculation suggests that  $Z_{eff}$  at the inner stages will be at best only 11% of intrinsic value. This suggests that there is very little cooling occurring at the inner stages, and this explains part of why there is so little separation in performance between the 1-stage cooler and the 6-stage cooler. If the oxide is only present below the TE elements of both devices, modeling shows that the 1-stage device would achieve a temperature differential of 23 K, and the 6-stage device would achieve a temperature differential of 31.5 K.

#### 4.7.2 Contact Resistance

The second issue is contact resistance. Although steps were taken to mitigate contact resistance, it was still present and it diminished the ability of the cooler to perform. The contacts used in this research were all made from gold. It is possible that other materials would offer lower contact resistances; however, we were unable to clean the surface of the wafers in-situ and consequently had to choose a metal that does not oxidize, such as gold. An additional strategy, which will be employed in later designs shown in chapter 5, is to mitigate the effects of the contact resistance without reducing it. This can be done by increasing the aspect ratios of the TE elements in order to increase their resistance. As R<sub>TE</sub> grows much larger than R<sub>par</sub> the relative effect of R<sub>par</sub> decreases, even though its absolute value remains the same.

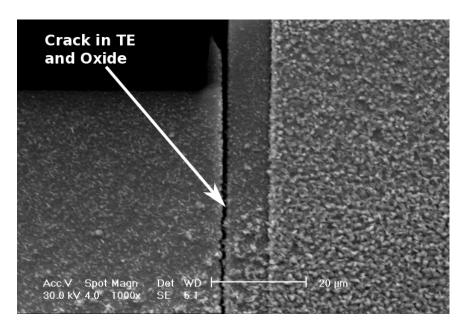

## 4.7.3 Die Attachment and support

Finally, this generation of devices did not have the necessary structural rigidity to allow for die bonding operations, which would be necessary for the device to be integrated with other MEMS and electronics. The Thermal Substrate is released very early in the overall process, and the method of release, backside DRIE, means that the die could not be bonded prior to this step. Once the Thermal Substrate is integrated with the Structural Substrate it gains some support from the glass tethers. This is enough to prevent the coolers from breaking during handling and testing; however, it is not enough to prevent the oxide bridges from breaking as pressure is applied to the center of the cooler.

## 4.8 Summary

A process has been presented for fabricating in-plane multi-stage thermoelectric coolers. Several designs have been presented, including 1-stage, 5-stage and 6-stage coolers. The devices have been tested, with the best performing 6-stage cooler achieving a ΔT=22.3 K. However, the process used to fabricate these devices is difficult to execute and forces several compromises with respect to the cooler design. Most notably, there is a significant amount of excess oxide at the center stages, which reduces the effectiveness of these stages. Additionally, because the devices are released at the time of deposition, the temperature of the inner stages is not well controlled during deposition, making it difficult to achieve optimum properties across all of the stages. These problems were addressed by development of a new process which is presented in Chapter 5.

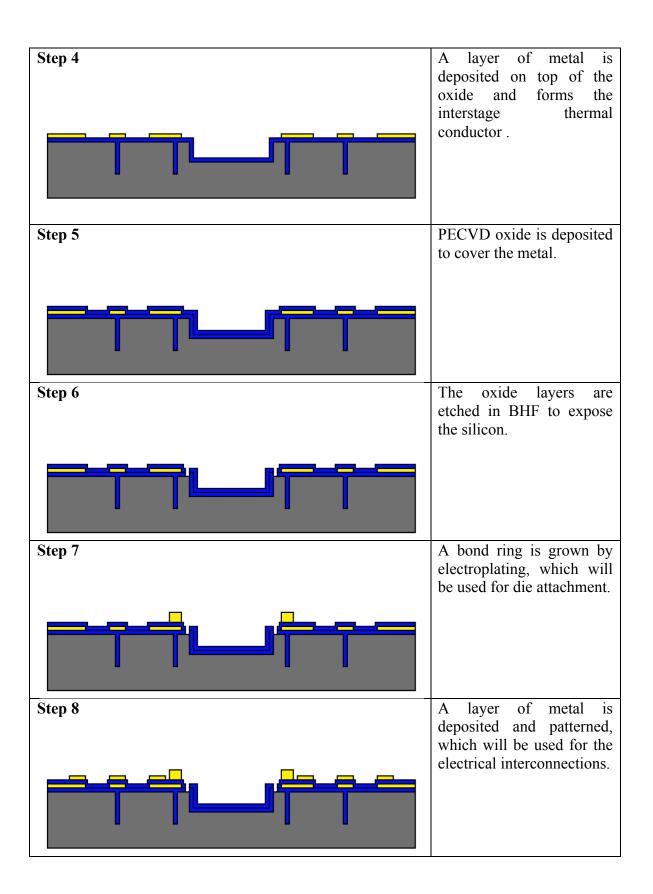

# Chapter 5 Single Wafer Process

#### 5.1 Introduction

The devices presented in Chapter 4 were capable of achieving temperatures of 22.3 K, but the process ultimately had several drawbacks which limited the manufacturability of the coolers, as well as the performance of the devices produced. The most significant problem, from a performance standpoint, was the low effective ZT of the inner stages, caused by the large amount of oxide spanning them. This limited the performance of those stages to less than 1/10<sup>th</sup> of the expected intrinsic performance.

Additionally there were significant drawbacks to the process itself. First, handling the 100 µm thick silicon wafers used to fabricate the top layer of the structure was a challenge. The wafers would break easily during routine processing steps, and were not stable until they could be bonded to the structural substrate. Because, these wafers required several processing steps prior to bonding, a significant amount of scrap was produced from this part of the process. Second, the previous process required deposition of the TE material onto coolers that were already released. This meant that during the shadowmask alignment procedure the coolers were already in a very fragile state, and aligning the shadowmask, even with protective spacers resulted in many of the oxide bridges breaking, causing very low yield on individual wafers.

Finally, and perhaps most importantly, the silicon-glass-silicon process was not capable of accepting an external device to be cooled. Any potential device attachment

would need to take place at after the release of the silicon had been removed from he backside of the oxide bridges, and at that point the cooler is too fragile to withstand the pressure required for bonding. This represents a critical flaw in the process. Recall from Chapter 1, that the primary motivation for developing a low-power thermoelectric microcooler is to improve the performance of other low-power microdevices such as gyroscopes, passive IR sensors, and low-power LNAs. Without the ability to interface with such devices, the coolers associated with the previous process have failed to answer the fundamental problem motivating the development of low-power thermoelectric coolers.

To address these shortcomings a new cooler structure and fabrication process were developed. The new process is based around a single 500 µm silicon wafer, and was design to produce a structure with lower parasitic losses, as well as more robust process that produces less scrap. It was also designed to allow for the attachment of arbitrary microdevices prior to release of the cooler structure, bringing it much closer to fulfilling the ultimate goals of the research.

This chapter will begin by discussing the structure of the new cooler devices. It will then present the process used to fabricate the devices, and address some of the challenges associated with this process. Next, a 4-stage cooler with novel power distribution will be presented. Following that, a group of serially driven coolers with 1, 2, 3, and 5 stages will be presented, and their performance will be compared. Finally, the die attachment process will be detailed and characterized.

#### **5.2** Device Overview

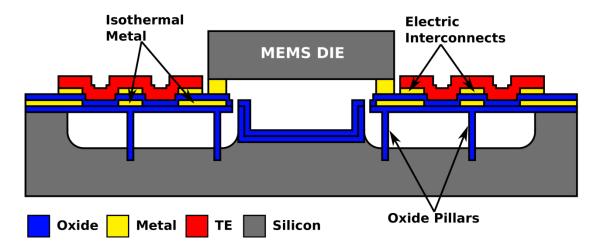

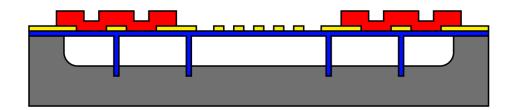

Figure 5.1: Cross section of a 2-stage cooler implemented using the structure. The thermal properties of the cooler are implemented with an oxide-metal-oxide stack that is supported by oxide pillars.

A new, simplified process was developed that would allow for deposition of the TE elements and die bonding prior to releasing the structure, while also still meeting the thermal properties required for effective multistage cooling. TE materials were again deposited on top of a supporting layer of silicon dioxide. However, unlike the previous process where the glass tether provided mechanical support to the central region and/or some of the inter-stage regions, the new structure supports these regions between stages with silicon dioxide pillars that are anchored into the silicon below the device. By fabricating the pillars as hollow tubes, the parasitic conduction that they contribute can be kept to a minimum. For example, a pillar that is 150  $\mu$ m long, with a 15  $\mu$ m x 15  $\mu$ m square cross section and an oxide wall thickness of 0.8  $\mu$ m will have a thermal conductance of 3.5E-7 W/K for a thermal conductivity of 1.1 W/m-K. For comparison, a single TE element with dimensions 3  $\mu$ m x 100  $\mu$ m x 30  $\mu$ m has a thermal conductance of 1E-5. If there were a pillar supporting every single TE element in a one stage cooler,

parasitic thermal conductance due to the pillars would be less than 10% of the total thermal conductance of the device. As Chapter 3 established, this is low enough that it will not have a significant impact on the performance of the device.

The use of the oxide pillars also makes it possible to reduce the parasitic thermal conduction compared to the previous design by reducing the amount of oxide used to support the TE. The devices presented in Chapter 4 had oxide directly underneath the TE, but also bridging the entire gap between the inter-stage regions. Analysis in Chapter 3 showed that this created a significant reduction in the effective ZT at the inner stages, and resulted in a large decrease in performance. In the new structure there is still oxide directly underneath the TE material, but all the oxide between adjacent TE elements can be removed. This is possible because each inter-stage region can be supported with multiple pillars, and the oxide must only support the TE material. This is in contrast to the previous design in which the oxide bridges also had to support one or more of the silicon inter-stage regions. By removing the excess oxide, the parasitic conduction of the first stage of the cooler can be reduced by approximately 50%, and the parasitic conduction of the fifth stage and sixth stages will be reduced by 90% or more.

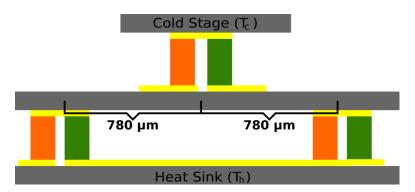

Multistage cooling also requires providing sufficient thermal conduction in regions between consecutive stages. In the previous designs, this function was performed by bulk single crystal silicon. In the new device, the silicon is replaced by 0.5  $\mu$ m gold thin-films that are encapsulated in silicon dioxide. The same type of analysis that was used in Chapter 4 to evaluate silicon as the thermal conductor for the previous structure can be used to evaluate the choice of gold in this case. Chapter 3 established that the quantity  $K_{in}A_{ratio}\rho/(\alpha^2T_hN_2)>10$ . If we consider a simple cooler with 1 TC at stage 2 and

2 TCs at stage 1, and  $\rho$ =12.9  $\mu\Omega$ -m,  $\alpha$ =210  $\mu$ V/K and a TC aspect ratio of 266,666 (corresponding to 3  $\mu$ m x 100  $\mu$ m x 80  $\mu$ m) then  $K_{in}$  should be more than 3.86E-5. If the gold is 0.5  $\mu$ m thick and 100  $\mu$ m wide, then the two thermocouples of the first stage can be separated from the thermocouple of the second stage by up to 780  $\mu$ m each (See Figure 5.2 for illustration). This indicates that the gold provides enough thermal conductance for a realistic cooler design to be largely unaffected by the substitution of thin gold film for the thick silicon used in the previous design. Having the gold underneath a layer of silicon dioxide decreases the thermal conductance of the path slightly. However, the thermal conductance through 1  $\mu$ m of oxide over an area of 150  $\mu$ m x 100  $\mu$ m is 0.015 W/m-K. This is 3 orders of magnitude greater than the minimum allowed thermal conductance of the gold, and will have a negligible effect on the total thermal conductance in the inter-stage region.

Figure 5.2: Illustration of maximum dimension for inter-stage thermal conduction.

The final requirement for multistage cooling is the need for more increased heat removal at the outer stages. Like the previous designs, this structure allows this requirement to be met by placing additional thermocouples at the outer stages. However, because this structure allows the oxide between TE elements to be removed, there is more flexibility in the layout of the stages. In particular, there is no longer a need to minimize

the perimeter of the inner stages in an effort to minimize parasitic thermal conduction. Instead, the cold stage can be made an arbitrary size without having an adverse affect on the performance of the cooler.

The above structure also deviates from the devices presented in the previous chapters by allowing for the attachment of other devices such as the gyroscopes and passive IR sensors discussed in Chapter 1. To allow for the die attachment, two features were added to the structure. The first feature is a metal bond that is grown by electroplating. The bond ring is separated into 8 segments and provides both the electrical and thermal connections between the cooler and device being cooled. The second feature is the inclusion of the pre-etched recess below the region where the die will sit. This feature gives the cooled device some separation from the hotter wafer, reducing parasitic thermal conduction through the air. It is pre-etched into the wafer and coated with oxide early in the process in order to facilitate faster release at the end of the process, and it will be discussed in more detail in section 5.3.

## 5.3 Process description

## 5.3.1 Process-related challenges and design decisions

Unlike the process presented in Chapter 4, where a number of standard processing steps had to be changed to accommodate the use of thin silicon wafers, this process is generally more straight-forward, with two exceptions. One main challenge is caused by the recess etched below the attached MEMS die. The recess is 100 µm deep, and spinning photoresist would produce very non-uniform layers. This was particularly true on devices near the edge of the wafer, where there would be a significant build up of photoresist on the inner edge of the recess, and significant thinning of resist on the outside part of the recess. The thickest areas were more than 20 µm thick, while the thinnest areas were only 3-4 µm. Such large differences in thickness made lithography

difficult because the thinnest areas would significantly over-develop and delaminate before patterns in the thickest areas completely developed.

If the only factor at stake was the photoresist, the simplest solution would be to move the etch step in order to form the recess later in the process; however, the recess is etched early in the process for a particular reason. If the etch were done as the step directly prior to the TE deposition, there would be no way to deposit oxide on the entire wall of the recessed cavity. In such a case the XeF<sub>2</sub> would start etching directly in and down from the bottom of the recess. That would create a situation where the pillars closest to the recess could be undercut and released. Placing the recess etch as the second step in the process and then coating the walls with LPCVD oxide before metal deposition means that the walls are completely coated and etching can only begin at the top surface during the release step. To fix the problem, photoresist was manually dripped into the recesses, and cured without spinning. A second layer of photoresist was then applied and spun on the wafer. This technique allowed for much better photoresist coating to be achieved, and made lithography near the edges of the recesses more repeatable.

#### **5.3.2** Full Process Flow

The following steps detail the fabrication process summarized above.

- 1. The holes for the oxide pillars are etched.

- 1.1. 5 μm of spr220 PR are spun on the surface of a 500 μm thick silicon wafer using the ACS200.

- 1.2. The PR is exposed for 12 seconds on the MA-6 contact aligner.

- 1.3. The wafer is baked on a hotplate at 115 °C for 90 seconds and developed for 30 seconds in MIF 300 on the ACS200.

- 1.4. The wafer is etched in the STS Pegasus DRIE tool for 45 minutes usingLNF recipe 2 to form the deep holes for the pillars.

- 1.5. The PR is stripped in PRS2000, rinsed for 3 minutes in DI water and dried in an SRD.

- 2. The shallow recess DRIE etch is performed.

- 2.1. AZ9260 PR is spun at 3000 rpm for 30 seconds, and baked for 20 minutes in an oven at 90 °C.

- 2.2. The wafer is exposed for 55 seconds on the MA-6 contact aligner.

- 2.3. The wafer is developed for 90 seconds in AZ400K, rinsed for 3 minutes in DI water, and dried in an SRD.

- 2.4. The wafer is etched in the STS Pegasus DRIE tool for 12 minutes usingLNF recipe 2 to form the shallow recess.

- 2.5. The PR is stripped in PRS2000, rinsed for 3 minutes in DI water and dried in an SRD.

- 3. The bottom layer of oxide is deposited.

- 3.1. Pre-furnace clean is performed on the wafer.

- 3.2. Low pressure chemical vapor deposition (LPCVD) is used to deposit 0.8 µm of silicon dioxide on the surface of the wafer.

- 4. The first layer of metal is deposited.

- 4.1. The recesses are filled with 1813 PR and cured for 10 minutes on a 110 °C hotplate.

- 4.2. HMDS is spun onto the wafer at 4000 rpm for 10 seconds, and the wafer is baked at 110 °C for 90 seconds.

- 4.3. AZ9260 PR is spun at 2000 rpm for 30 seconds, and baked for 20 minutes in an oven at 90 °C.

- 4.4. The wafer is exposed for 75 seconds on the MA-6 contact aligner.

- 4.5. The wafer is developed for 90 seconds in AZ400K, rinsed for 3 minutes in DI water, and dried in an SRD.

- 4.6. 1000 A of chrome and 5000 A of gold are deposited onto the surface of the wafer using the Enerjet evaporator.

- 4.7. Lift-off is performed in acetone. An ultrasonic bath is used to speed the lift-off process. The wafers are rinsed with acetone and then with IPA and dried with a nitrogen sprayer.

- 5. The second layer of oxide is deposited.

- 5.1. PECVD is used to deposit 0.6-1.0 µm of oxide onto the surface of the wafer. The oxide is deposited with a substrate temperature of 380 °C.

- 6. The oxide layers are patterned.

- 6.1. The recesses are filled with 1813 PR and cured for 10 minutes on a 110 °C hotplate.

- 6.2. HMDS is spun onto the wafer at 4000 rpm for 10 seconds, and the wafer is baked at 110 °C for 90 seconds.

- 6.3. 1827 PR is spun at 2000 rpm for 30 seconds, and baked for 20 minutes in an oven at 90 °C.

- 6.4. The wafer is exposed for 35 seconds on the MA-6 contact aligner.

- 6.5. The wafer is developed for 90 seconds in MIF 319, rinsed for 3 minutes in DI water, and dried in an SRD.

- 6.6. The wafer is etched in BHF for 7 minutes, rinsed in DI water for 3 minutes, and dried in an SRD.

- 6.7. The PR is stripped from the wafer in PRS2000, and the wafer is rinsed for 3 minutes in DI water and dried in an SRD.

- 7. The metal bond rings are deposited.

- 7.1. The recesses are filled with 1813 PR and cured for 10 minutes on a 110 °C hotplate.

- 7.2. HMDS is spun onto the wafer at 4000 rpm for 10 seconds, and the wafer is baked at 110 °C for 90 seconds.

- 7.3. AZ9260 PR is spun at 2000 rpm for 30 seconds, and baked for 20 minutes in an oven at 90 °C.

- 7.4. The wafer is exposed for 75 seconds on the MA-6 contact aligner.

- 7.5. The wafer is developed for 90 seconds in AZ400K, rinsed for 3 minutes in DI water, and dried in an SRD.

- 7.6. 1000 A of chrome and 5000 A of gold are deposited onto the surface of the wafer using the Enerjet evaporator. This will be the seed layer for electroplating the bond ring.

- 7.7. Lift-off is performed in acetone. An ultrasonic bath is used to speed the lift-off process. The wafers are rinsed with acetone and then with IPA and dried with a nitrogen sprayer.

- 7.8. The recesses are filled with 1813 PR and cured for 10 minutes on a 110 °C hotplate.

- 7.9. HMDS is spun onto the wafer at 4000 rpm for 10 seconds, and the wafer is baked at 110 °C for 90 seconds.

- 7.10. AZ9260 PR is spun at 1000 rpm for 30 seconds, and baked for 20 minutes in an oven at 90 °C.

- 7.11. The wafer is exposed for 75 seconds on the MA-6 contact aligner.

- 7.12. The wafer is developed for 90 seconds in AZ400K, rinsed for 3 minutes in DI water, and dried in an SRD.

- 7.13. 6 µm of gold are electroplated, using the patterned PR as a mold.

- 7.14. The PR is stripped from the wafer in PRS2000, and the wafer is rinsed for 3 minutes in DI water and dried in an SRD.

- 7.15. The recesses are filled with 1813 PR and cured for 10 minutes on a 110 °C hotplate.

- 7.16. HMDS is spun onto the wafer at 4000 rpm for 10 seconds, and the wafer is baked at 110 °C for 90 seconds.

- 7.17. AZ9260 PR is spun at 1000 rpm for 30 seconds, and baked for 20 minutes in an oven at 90 °C.

- 7.18. The wafer is exposed for 90 seconds on the MA-6 contact aligner.

- 7.19. The wafer is developed for 90 seconds in AZ400K, rinsed for 3 minutes in DI water, and dried in an SRD.

- 7.20. The chrome/gold seed layer is etched away, and the wafer is rinsed for3 minutes in DI water and dried in an SRD.

- 7.21. The PR is stripped from the wafer in PRS2000, and the wafer is rinsed for 3 minutes in DI water and dried in an SRD.

- 8. The second layer of interconnect metal is deposited.

- 8.1. The recesses are filled with 1813 PR and cured for 10 minutes on a 110 °C hotplate.

- 8.2. HMDS is spun onto the wafer at 4000 rpm for 10 seconds, and the wafer is baked at 110 °C for 90 seconds.

- 8.3. AZ9260 PR is spun at 2000 rpm for 30 seconds, and baked for 20 minutes in an oven at 90 °C.

- 8.4. The wafer is exposed for 75 seconds on the MA-6 contact aligner.

- 8.5. The wafer is developed for 90 seconds in AZ400K, rinsed for 3 minutes in DI water, and dried in an SRD.

- 8.6. 1000 A of chrome and 5000 A of gold are deposited onto the surface of the wafer using the Enerjet evaporator. This will be the seed layer for electroplating the bond ring.

- 8.7. Lift-off is performed in acetone. An ultrasonic bath is used to speed the lift-off process. The wafers are rinsed with acetone and then with IPA and dried with a nitrogen sprayer.

- 9. The TE material is deposited.

- 9.1. The shadow mask for the Bi<sub>2</sub>Te<sub>3</sub> pattern is aligned to the device wafer and clamped. The wafer is loaded into the TE evaporator and pumped to a pressure of less than 2E-6 Torr. Bi<sub>2</sub>Te<sub>3</sub> is deposited using a flux ration of Te:Bi of 3.0, and substrate temperature of 260 °C . After deposition the wafer is allowed to cool to less than 100 °C before venting the chamber.

- 9.2. The shadow mask for the Sb<sub>2</sub>Te<sub>3</sub> pattern is aligned to the device wafer and clamped. The wafer is loaded into the TE evaporator and pumped to a pressure of less than 2E-6 Torr. Sb<sub>2</sub>Te<sub>3</sub> is deposited using a flux ration of Te:Sb of 2.4, and substrate temperature of 230 °C . After deposition the wafer is allowed to cool to less than 100 °C before venting the chamber.

- 10. The Die is attached. See section 5.6 for details

- 11. The cooler is released.

- 11.1. The TE is protected with a coat of photoresist, which is sprayed onto the wafer. It is exposed through a special mask which has recesses to accommodate the attached die.

- 11.2. The wafer is diced or cleaved into groups of up to 4 die.

- 11.3. The groups of die are released in XeF<sub>2</sub> using the Xactix etching tool. 4 coolers can be released using 200 etching cycles at 30s per cycle with a pressure of 3 Torr.

- 11.4. An oxygen plasma ash is used to release to completed device.

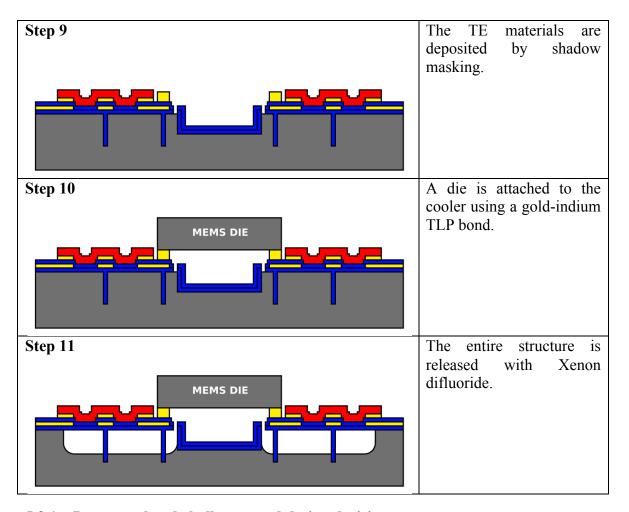

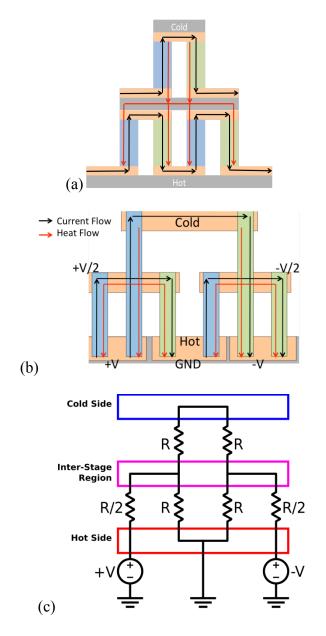

## 5.4 The 4 stage device

Using a simplified version of the process described in section 5.3, a 4-stage cooler with a unique current distribution was developed. The coolers described in Chapter 4, and the coolers described by the process in 5.3 rely on using one region of material as the thermal conductor of the inter-stage region (i.e. silicon or the lower metal layer), and a second region of material as the electrical conductor connecting the thermocouples.

However, the design presented in this section combines both functions, electrical and thermal conduction, into a single region of material.

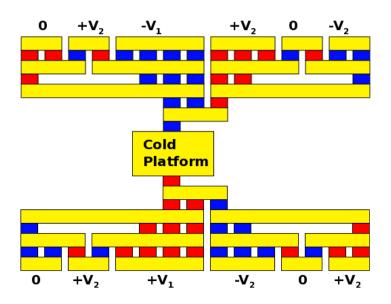

#### 5.4.1 Current drive mechanism

The designs that have been presented so far have all had TCs arranged in series. The electrical conductors are thermally connected to the inter-stage thermal conductor, but are electrically isolated from it, as shown in Figure 5.3(a). This is necessary to maintain the proper current flow through the series TCs. To combine the electrical conductor and the thermal conductor into a single region requires moving away from a driving current through the TCs serial.

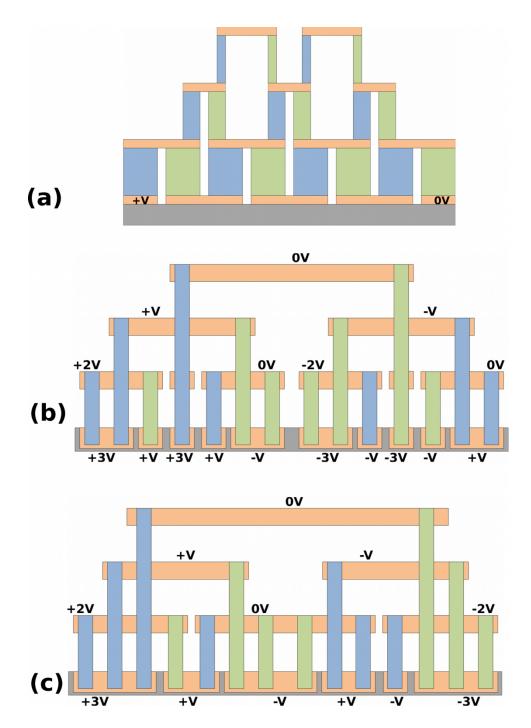

Figure 5.3: Illustration of heat and current flow in (a) a conventional, serially-driven 2-stage cooler, and (b) a two stage cooler using a resistive network to distribute current. The electrical schematic of the device shown in (b) is provided as (c).

To understand how this can be accomplished, a diagram of a 2-stage cooler and its equivalent electrical circuit is shown in Figure 5.3 (b-c). In this example, 3 voltage inputs are supplied to the hot side of the first stage, and the current is distributed through the resistive network of the cooler. If the n-type and p-type have the same resistance and

are the same size, the current will be the same through all of the TE legs, resulting in a cooler that has the same cooling characteristics as a 2-stage, serially driven cooler with 3 TCs at stage 1 and 1 TC at stage 2. For a 2-stage cooler, this design approach produces a device that is the equivalent to the design proposed by O'Brien [81]. When extended to 3 or more stages however, the two designs diverge. A 3-stage example of the current design, as well as the O'Brien design, is shown in Figure 5.4 (a-b).

The O'Brien design requires only two inputs to function correctly, but it requires a significant variation in the size of the TE elements at each stage. Although not shown in the schematic, the O'Brien design also requires variations in the size of the TE elements within a stage if the optimal current flow is to be achieved. The design presented here, on the other hand, uses multiple voltage inputs (4 inputs are required for a three stage cooler) but all the TE legs can be made the same size. Uniform size of the TE is an advantage when working with the current process, because the minimum size of the elements is limited by the resolution of the shadow mask deposition process. At the same time, very wide TE legs are impractical because they would take a very long time to undercut with the XeF<sub>2</sub> etch process. Long release etches are undesirable because they can result in undercutting the oxide support pillars before the cooler is released.

Figure 5.4: (a) Illustration of a previously devised three stage cooler that distributes current through a resistive network. (b) A 3-stage cooler using the resistive network proposed in this section. (c) A modified version of the cooler shown in (b). It combines inter-stage regions of the same nominal voltage.

The design shown in Figure 5.4(b) is the simplest implementation of this design principle, and is helpful for examining how heat and current flow through the cooler.

However, it is not optimal because it contains isolated regions in the inter-stage zone between stages 1 and 2 which do not have higher cooler capacity at stage 1 compared to stage 2. To fix this problem, inter-stage zones that share a common nominal voltage can be combined into a single zone as shown in Figure 5.4 (c)

## **5.4.2** Structure and process simplification