# ANALYSIS AND OPTIMIZATION OF MULTIPROGRAMMED COMPUTER SYSTEMS USING STORAGE HIERARCHIES

Ashby Woolf

University of Michigan

Approved for public release; distribution unlimited

#### **FOREWORD**

The research described in this technical report was accomplished under Contract F30602-69-C-0214, Job Order Number 55810000 at the University of Michigan, Ann Arbor, MI. Mr. Rocco F. Iuorno (ISIS) was the Rome Air Development Center project engineer.

This report has been reviewed by the Office of Information (OI) and is releasable to the National Technical Information Service (NTIS).

This technical report has been reviewed and is approved.

Approved:

ROCCO F. IUORNO

Project Engineer

Software Sciences Section

Approved:

RANK TOMAINI

Ch, Info Processing Branch Info Sciences Division

#### ABSTRACT

The research described in this report centers around the development and application of a general and comprehensive mathematical model of computer systems which use storage hierarchies consisting of 2, 3 or more levels and in which the storage management is carried out automatically (i.e. transparent to the user.) This model has been implemented in the form of a highly interactive computer program which provides the user with an animated view of the system performance as model parameters are varied.

There are roughly 50 independent variables in the model. (The number of independent variables is dependent on the hardware configuration.) These variables describe the system architecture, data paths and routing, storage device characteristics, CPU performance, and user program behavior.

The overall model can best be described in terms of several component models. The storage device models take into account the effects of queueing for the device itself (such as a disk drive), queueing for channel service, seek time, latency time, and transfer time. The specific parameters may vary according to the specific device being modeled. Models for a core or random access device, drum, disk and data cell are described and implemented. The model which describes user program behavior is dependent on the storage allocated at each level in the hierarchy, the logical record or page size at each level, the size of the user program, and five other system independent variables. The user program model and the storage device models are linked together by a final model which relates user program behavior and the storage device performance. The macroscopic model includes effects of system architecture, data paths, queueing for the CPU, CPU lookahead and system software overhead.

The solution of the combined system model involves numerical techniques. A complete solution requires approximately 1 sec., based on IBM 360/67. When the model is used in the context of optimization, an evaluation can be obtained in approximately 50 ms. In practical terms this means that in the case of analysis the printing of results is more expensive than the analysis itself. In the case of optimization over 1000 systems can be examined in 1 minute or over 60,000 per hour.

### TABLE OF CONTENTS

|      |            |                                                                | Page       |

|------|------------|----------------------------------------------------------------|------------|

|      |            |                                                                |            |

|      |            |                                                                |            |

|      |            |                                                                |            |

|      |            |                                                                |            |

| Chap | <u>ter</u> |                                                                |            |

| I    | INTI       | RODUCTION                                                      | 1          |

|      | 1.1        | A General Discussion                                           | 1          |

|      | 1.2        | The Nature of the Problem                                      | 4<br>5     |

|      | 1.3        | Objectives                                                     |            |

|      | 1.4        | A Preview                                                      | 6          |

| II   | A M        | ODEL OF PROGRAM BEHAVIOR                                       | 16         |

|      | 2.1        | A General Description of Program Behavior                      | 16         |

|      |            | Basic Model Description                                        | 20         |

|      |            | Effects of Program Loop Lengths on Page Faults                 | 23         |

|      | 2.4        | Effects of Allocation During Initial Paging                    | 29         |

|      |            | Consideration of a Distribution of Loop Lengths                | 37         |

|      |            | Final Model Development                                        | 42         |

|      |            | Examples of Model Behavior With Varying Allocatio              |            |

|      | 2.8        | Example of Model Behavior With Varying Page Size               | 68         |

| Ш    | MAC        | CROSCOPIC MODEL                                                | 82         |

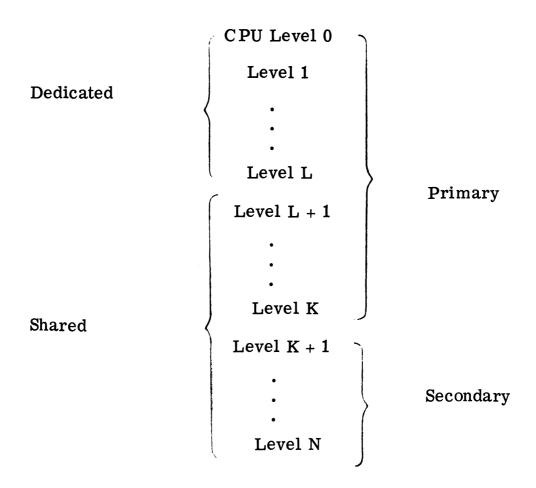

|      | 3.1        | The N Level Hierarchy                                          | 82         |

|      | 3.2        | Storage Allocation                                             | 83         |

|      | 3.3        | Multiprogramming                                               | 91         |

|      |            | Interlevel Data Traffic                                        | 94         |

|      |            | Primary and Secondary Levels of Storage                        | 101        |

|      |            | Dedicated and Shared Levels of Storage                         | 108        |

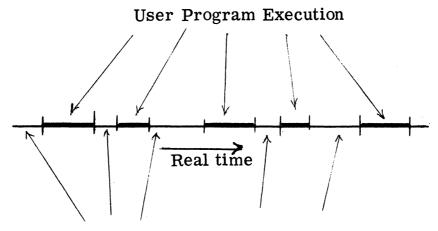

|      |            | Traffic Description At Individual Levels                       | 117        |

|      |            | Storage Hardware Performance                                   | 125        |

|      |            | Primary and Secondary Access Time                              | 128<br>143 |

|      |            | Interaction Between CPU and Primary Storage System Performance | 143<br>148 |

|      |            | Solution                                                       | 155        |

|      | 0.10       | DOLUMENT                                                       | 100        |

## TABLE OF CONTENTS (Continued)

| Chap | <u>ter</u>                                                                                         | Page        |

|------|----------------------------------------------------------------------------------------------------|-------------|

| IV   | HARDWARE MODEL FOR INDIVIDUAL LEVELS OF STORAGE                                                    | 162         |

|      | 4.1 Basic Model 4.2 Solution of Basic Model                                                        | 163<br>172  |

|      | 4.3 Solution Algorithm 4.4 Disk Model                                                              | 176<br>179  |

|      | 4.5 Data Cell Model                                                                                | 189         |

|      | 4.6 Core Model                                                                                     | 191         |

|      | 4.7 Drum Model                                                                                     | 192         |

|      | 4.8 Effect of Specific Record Sizes                                                                | 195         |

| v    | A CASE STUDY IN ANALYSIS                                                                           | 198         |

|      | 5.1 Program Description                                                                            | 198         |

|      | 5. 2 System Description                                                                            | 201         |

|      | 5.3 A Hardware Modification                                                                        | 242         |

|      | 5.4 A Change in User Program Characteristics 5.5 Changing the Number of User Programs              | 246<br>253  |

|      | 5.6 Summary                                                                                        | 259         |

| VI   | SYSTEM OPTIMIZATION                                                                                | 261         |

|      | 6.1 Objective Function and Method                                                                  | 261         |

|      | 6.2 A Simple Example                                                                               | 266         |

|      | <ul><li>6.3 Changing the User Program Size</li><li>6.4 Changing the Number of Core Units</li></ul> | 278<br>281  |

| VII  | CONCLUSIONS                                                                                        | <b>2</b> 86 |

| Appe | ndices                                                                                             |             |

| Α    | SOLUTION FOR INTEGRALS OF EQUATION 2.54                                                            | 289         |

| В    | REQUEST DISTRIBUTION                                                                               | 299         |

| С    | COMPUTATIONAL DIFFICULTIES IN COMPUTING $\beta$                                                    | 311         |

| втвт | JOGRAPHY                                                                                           | 316         |

### LIST OF FIGURES

| Figure | •                                                                   | Page       |

|--------|---------------------------------------------------------------------|------------|

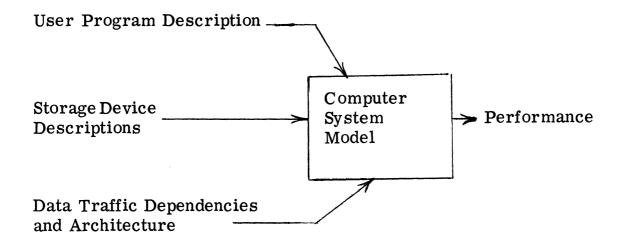

| 1.1    | System Analysis Model                                               | 7          |

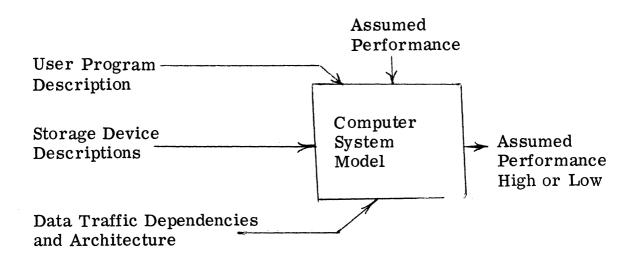

| 1.2    | System Model                                                        | 7          |

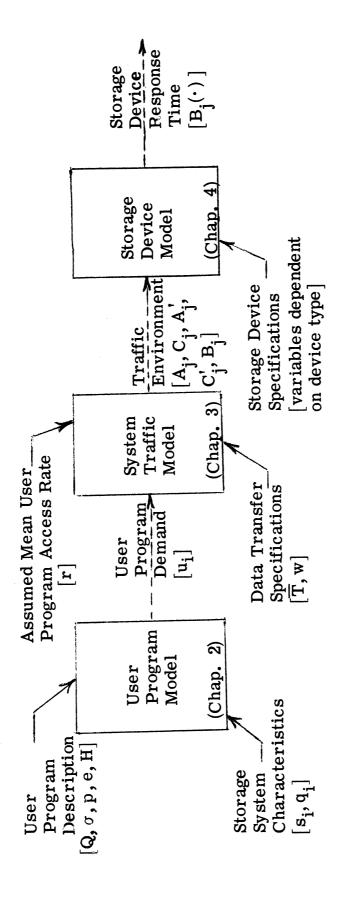

| 1.3    | Detailed System Model, Part 1                                       | 10         |

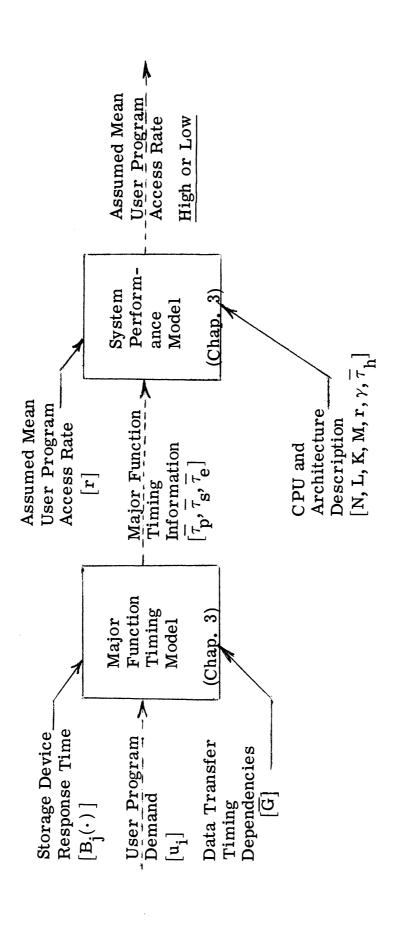

| 1.4    | Detailed System Model, Part 2                                       | 11         |

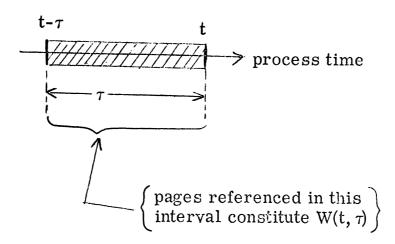

| 2.1    | Definition of $W(t, \tau)$                                          | 17         |

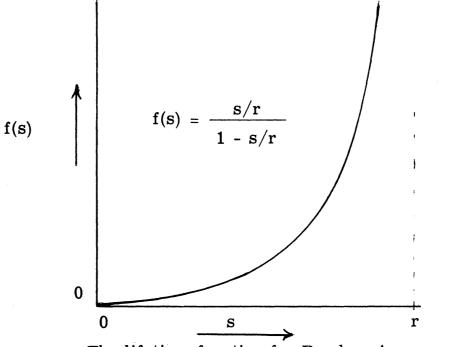

| 2.2    | The Lifetime Function for Random Accesses                           | 19         |

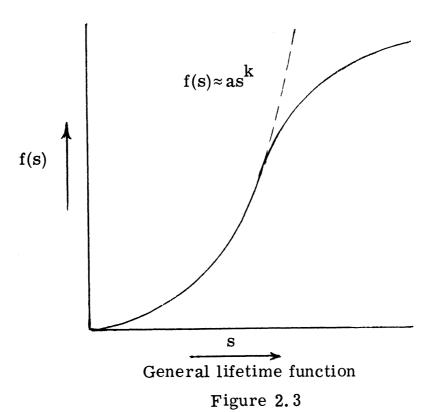

| 2.3    | General Lifetime Function                                           | 19         |

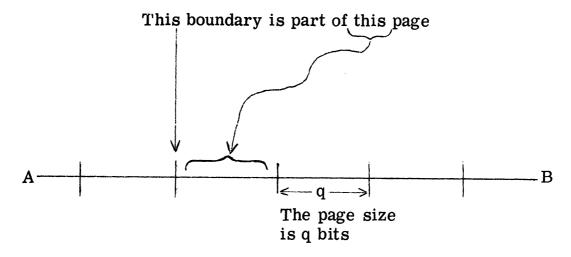

| 2.4    | The Virtual Address Space                                           | 23         |

| 2.5    | Access Loop                                                         | 24         |

| 2.6    | Loop Position                                                       | <b>2</b> 5 |

| 2.7    | The Δ Distribution                                                  | 39         |

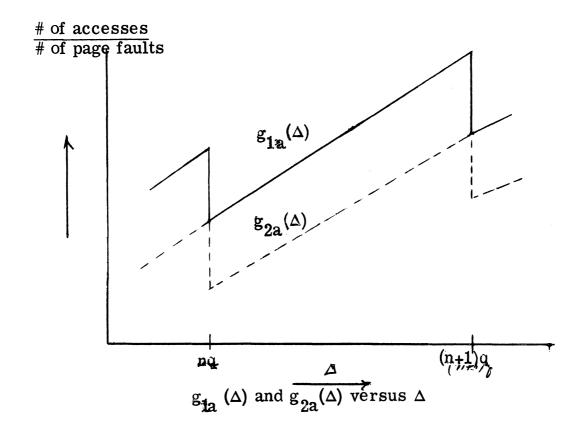

| 2.8    | $g_{ia}$ as a Function of $\Delta$                                  | 45         |

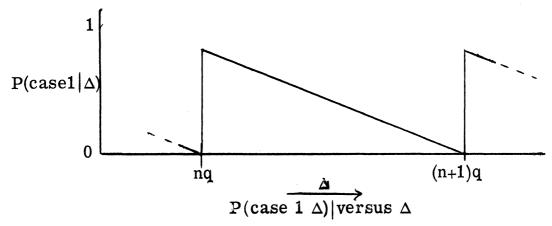

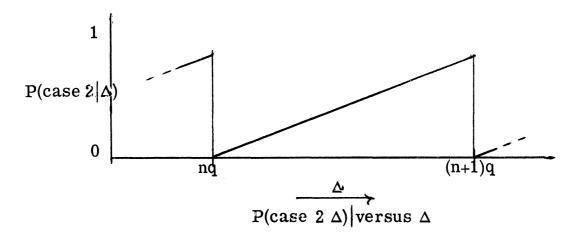

| 2.9    | The Components of $H_1(\Delta)$                                     | 46         |

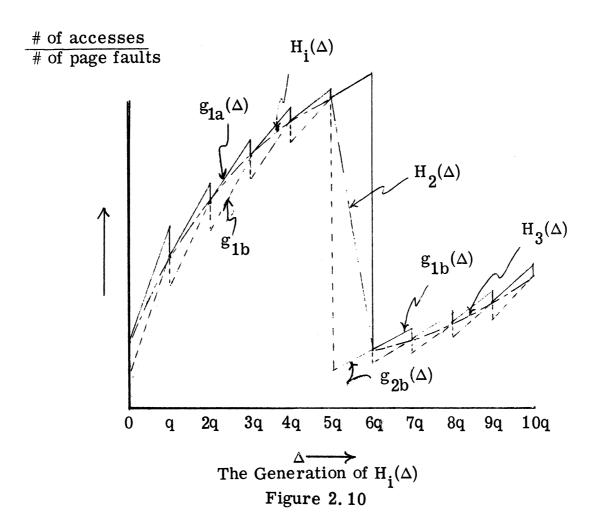

| 2.10   | The Generation of $H_i(\Delta)$                                     | 48         |

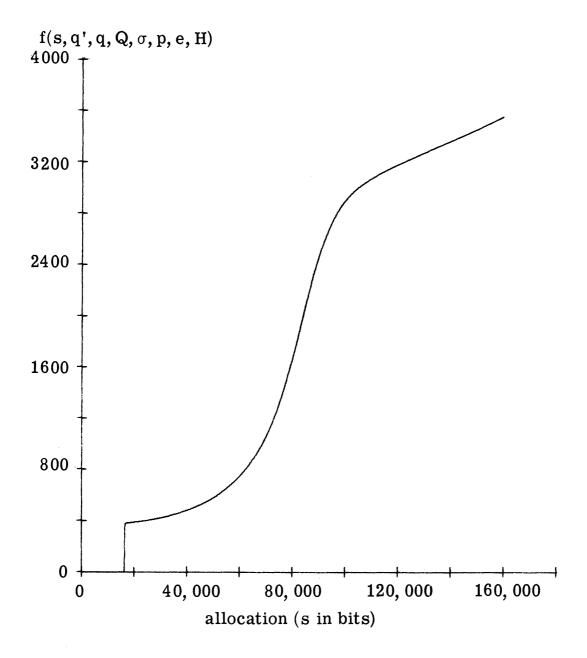

| 2.11   | The Lifecycle Function Versus Allocation for the                    |            |

|        | ''Standard'' Case                                                   | 57         |

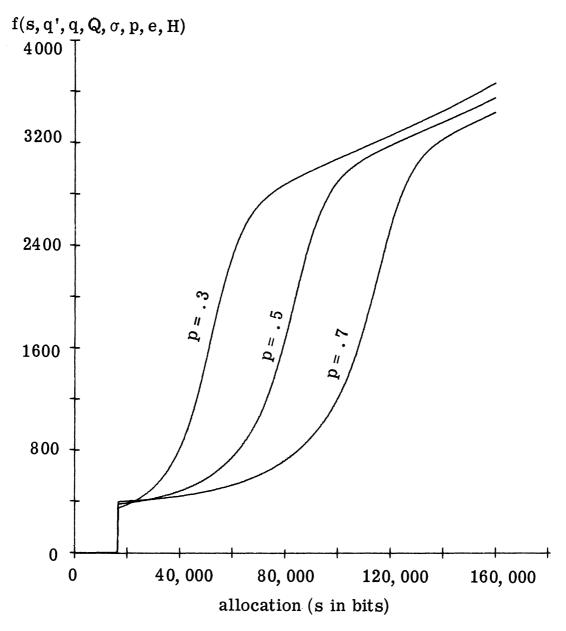

| 2.12   | The Lifecycle Function Versus Allocation With                       |            |

|        | Variations in p                                                     | 59         |

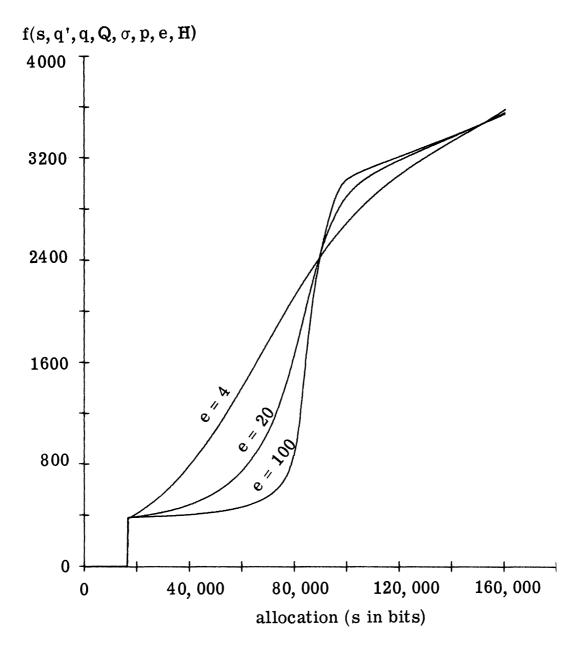

| 2.13   | The Lifecycle Function Versus Allocation With                       |            |

|        | Variations in e                                                     | 60         |

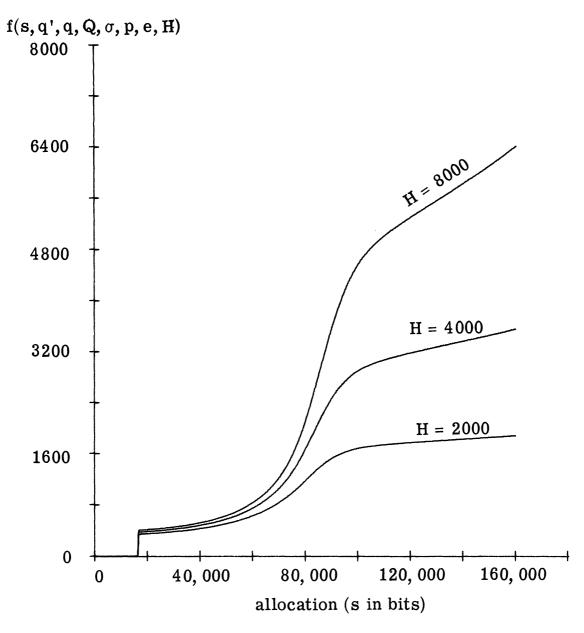

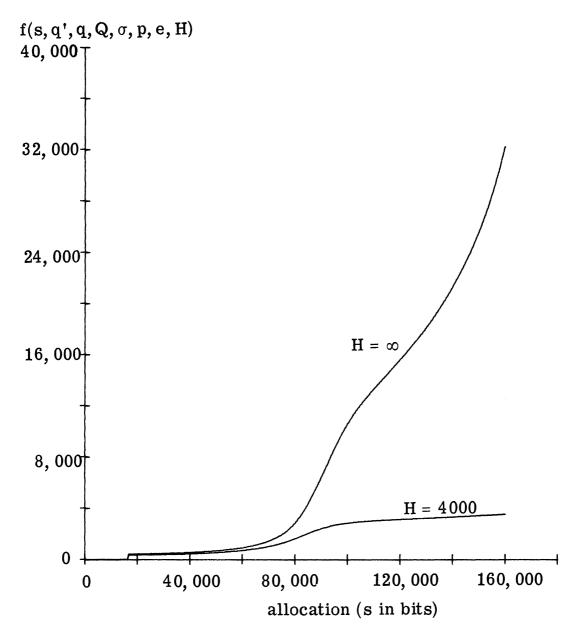

| 2.14   | The Lifecycle Function Versus Allocation With                       |            |

|        | Variations in H                                                     | 62         |

| 2.15   | The Lifecycle Function Versus Allocation for $H = \infty$           | 63         |

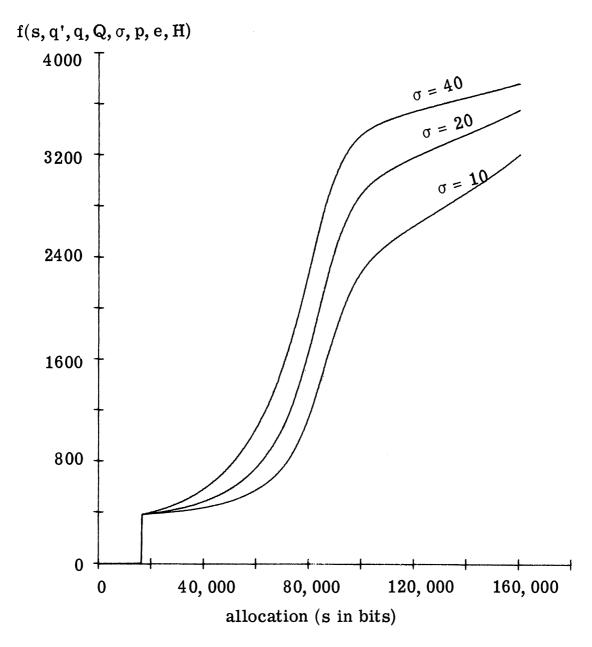

| 2.16   | The Lifecycle Function Versus Allocation With                       |            |

|        | Variations in $\sigma$                                              | 64         |

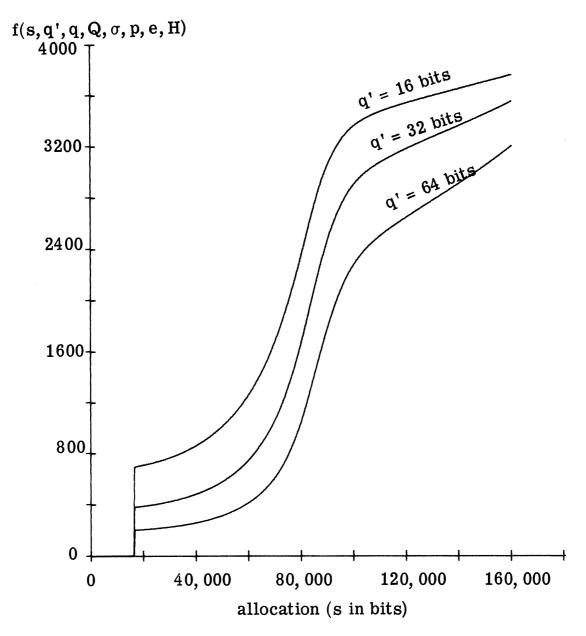

| 2.17   | The Lifecycle Function Versus Allocation With                       |            |

| 0.40   | Variations in q'                                                    | 66         |

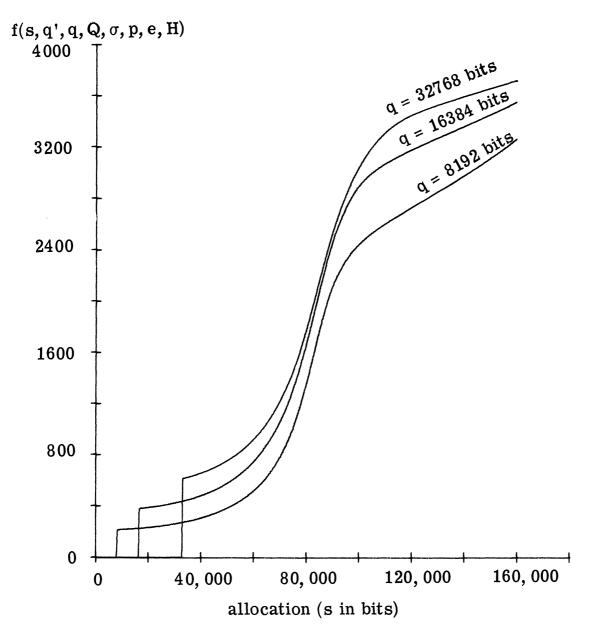

| 2.18   | The Lifecycle Function Versus Allocation With                       | ۰          |

| 0.10   | Variations in q                                                     | 67         |

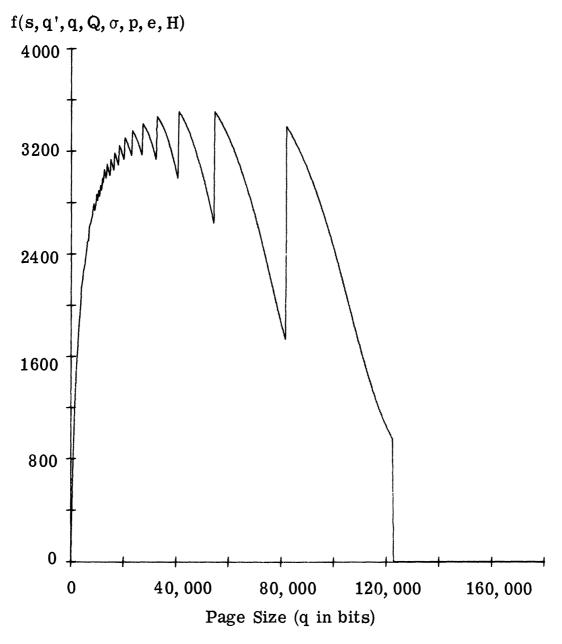

| 2.19   | The Lifecycle Function Versus Page Size for the                     | 00         |

| 0 00   | "Standard" Case                                                     | 69         |

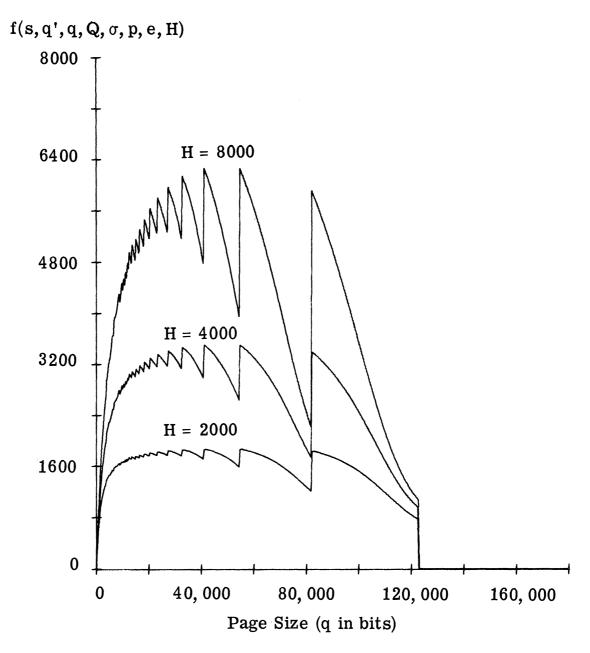

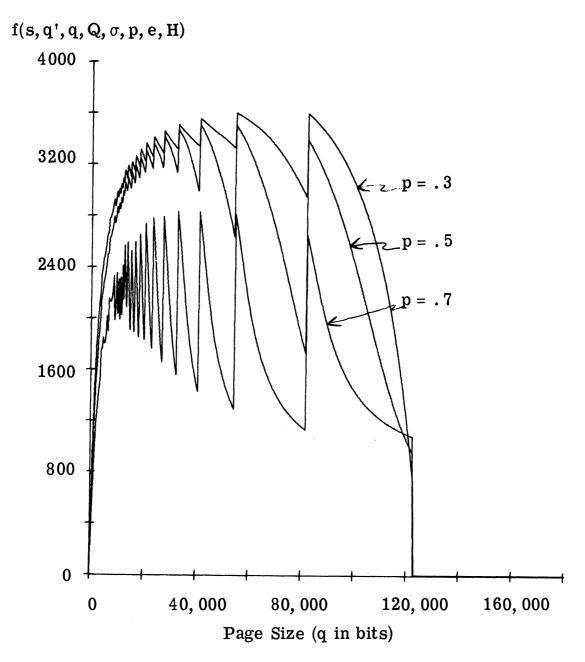

| 2. 20  | The Lifecycle Function Versus Page Size With                        | 70         |

| 0 01   | Variations in H                                                     | 72         |

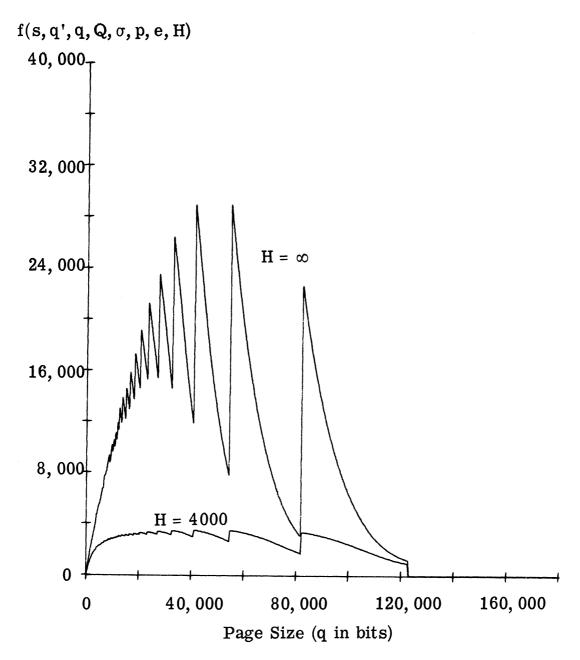

| 2. 21  | The Lifecycle Function Versus Page Sice for H = ∞                   | 73         |

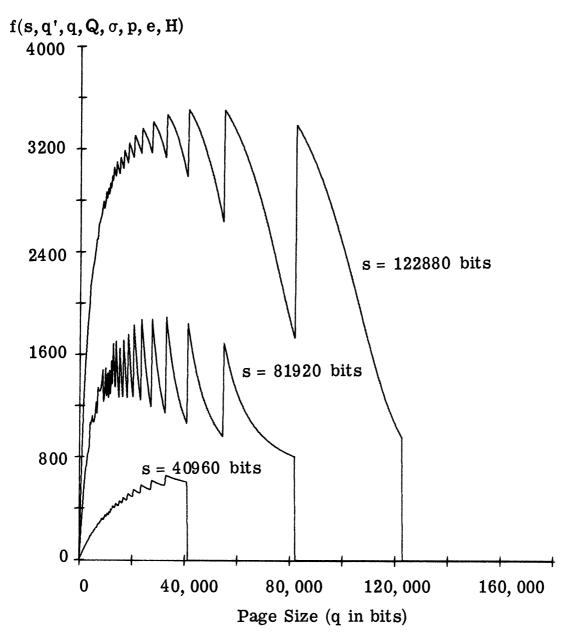

| 2.22   | The Lifecycle Function Versus Page Size With                        | 75         |

| n no   | Variations in s                                                     | 75         |

| 2. 23  | The Lifecycle Function Versus Page Size With                        | 77         |

| 0 04   | Variations in p                                                     | 77         |

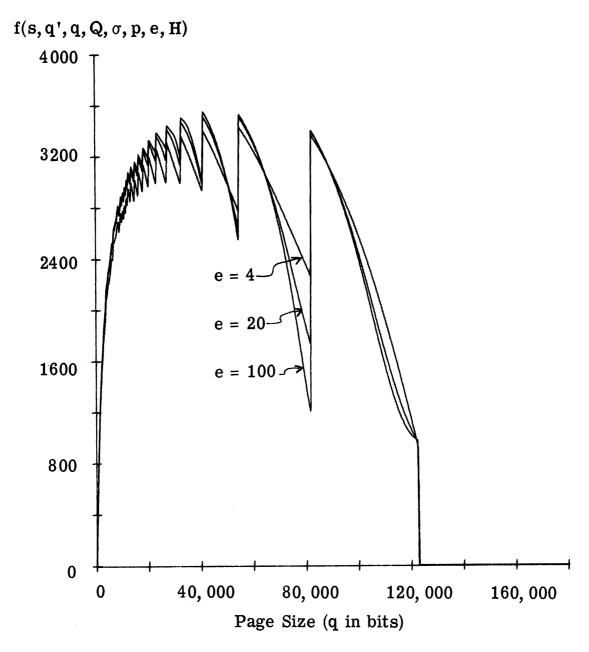

| 2.24   | The Lifecycle Function Versus Page Size With                        | 70         |

| 9 95   | Variations in e                                                     | <b>7</b> 8 |

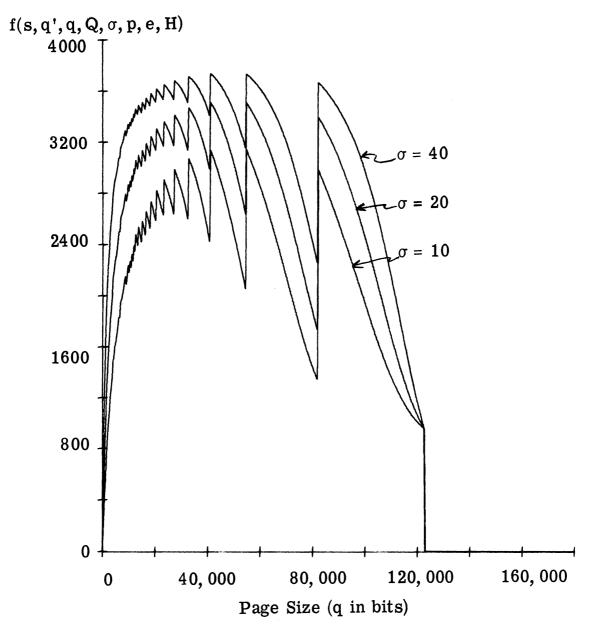

| 2. 25  | The Lifecycle Function Versus Page Size With Variations in $\sigma$ | 80         |

|        | valiations in ()                                                    | OU         |

# LIST OF FIGURES (Continued)

| Figur | <u>e</u>                                                         | Page |

|-------|------------------------------------------------------------------|------|

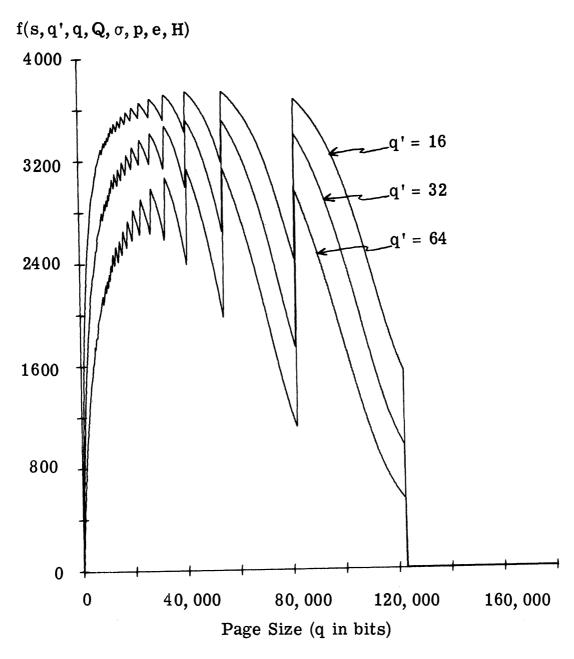

| 2. 26 | The Lifecycle Function Versus Page Size With                     |      |

|       | Variations in q'                                                 | 81   |

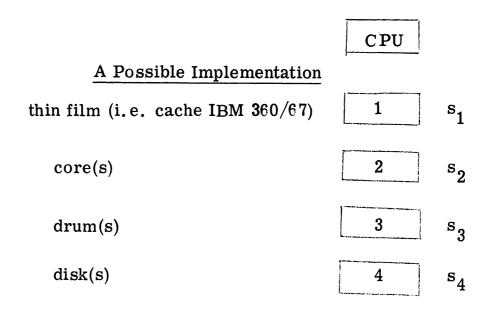

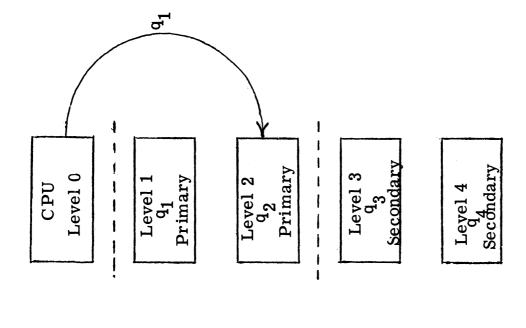

| 3.1   | A Four Level Hierarchy                                           | 83   |

| 3.2   | Access Distribution                                              | 86   |

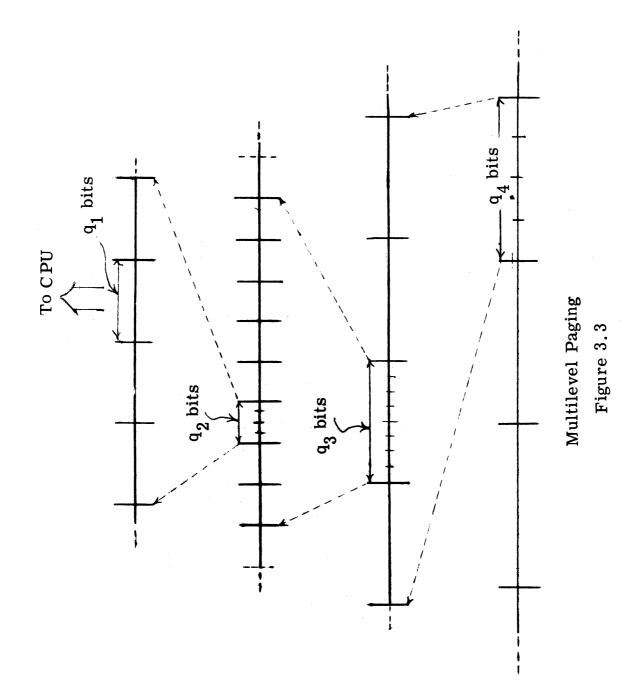

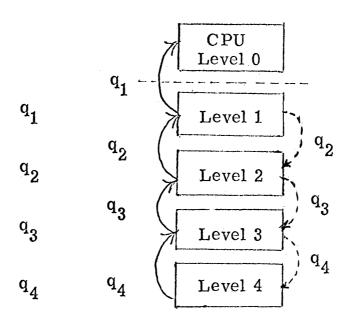

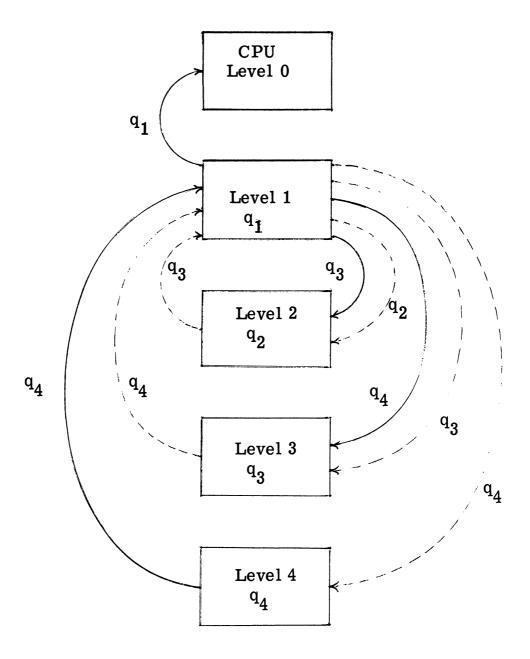

| 3.3   | Multilevel Paging                                                | 88   |

| 3.4   | Traffic - Primary Read to Level 4                                | 95   |

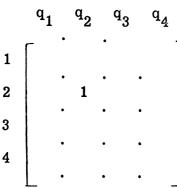

| 3.5   | T Array for Example 1                                            | 97   |

| 3.6   | Transfer Pattern 4-Level Hierarchy for User                      |      |

|       | Induced Level 4 Read                                             | 99   |

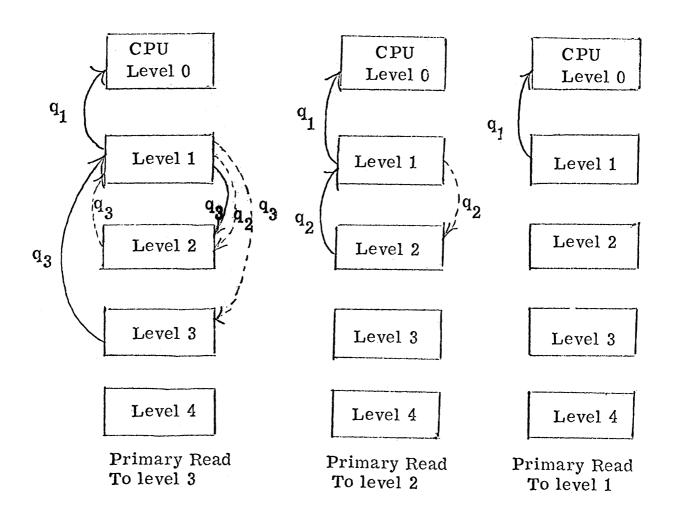

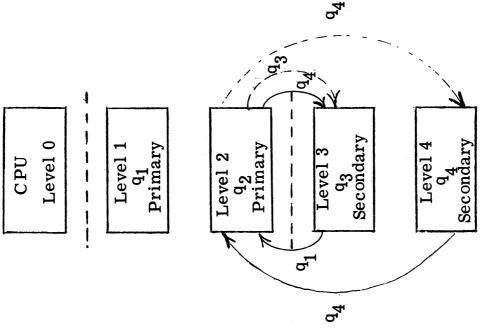

| 3.7   | Traffic Diagrams                                                 | 102  |

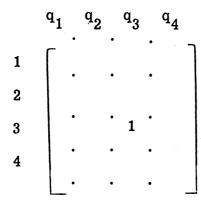

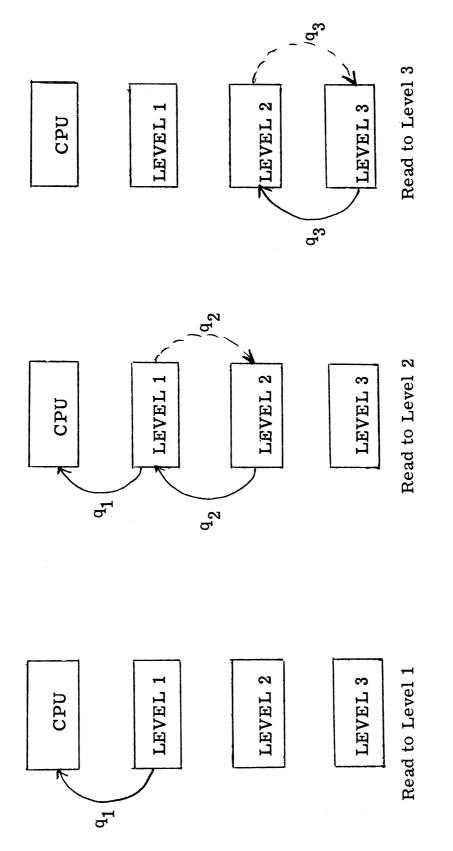

| 3.8   | T Array for Example 2                                            | 103  |

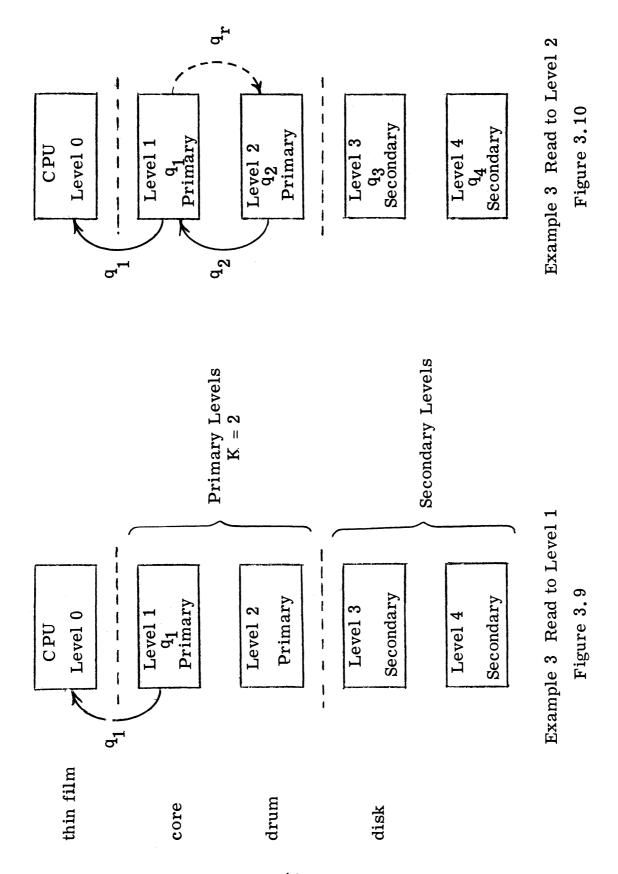

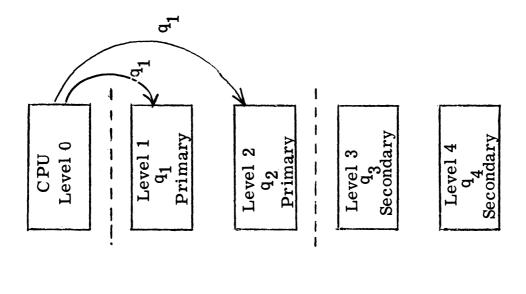

| 3.9   | Example 3 Read to Level 1                                        | 105  |

| 3.10  | Example 3 Read to Level 2                                        | 105  |

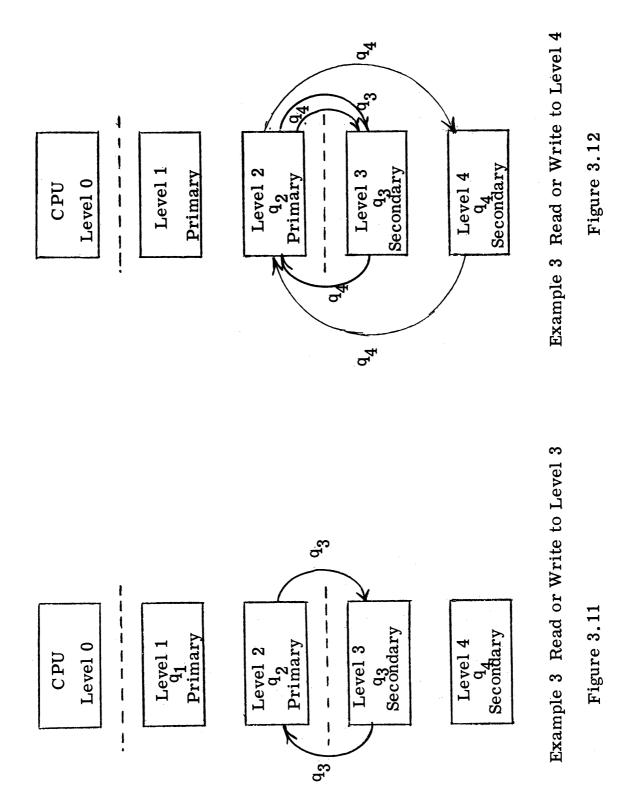

| 3.11  | Example 3 Read or Write to Level 3                               | 106  |

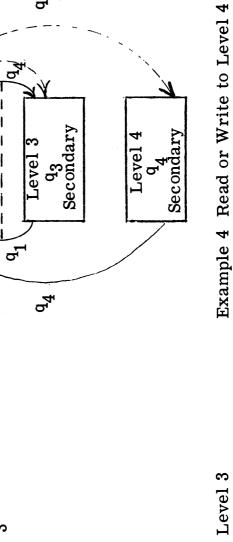

| 3.12  | Example 3 Read or Write to Level 4                               | 106  |

| 3,13  | T Array for Example 3                                            | 107  |

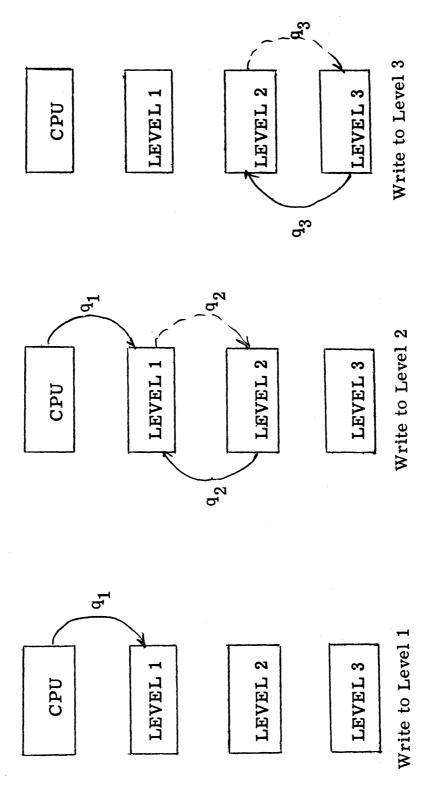

| 3.14  | Example 4 Read to Level 1                                        | 109  |

| 3.15  | Example 4 Write to Level 1                                       | 109  |

| 3.16  | Example 4 Read to Level 2                                        | 110  |

| 3.17  | Example 4 Write to Level 2                                       | 110  |

| 3.18  | Example 4 Read or Write to Level 3                               | 112  |

| 3.19  | Example 4 Read or Write to Level 4                               | 112  |

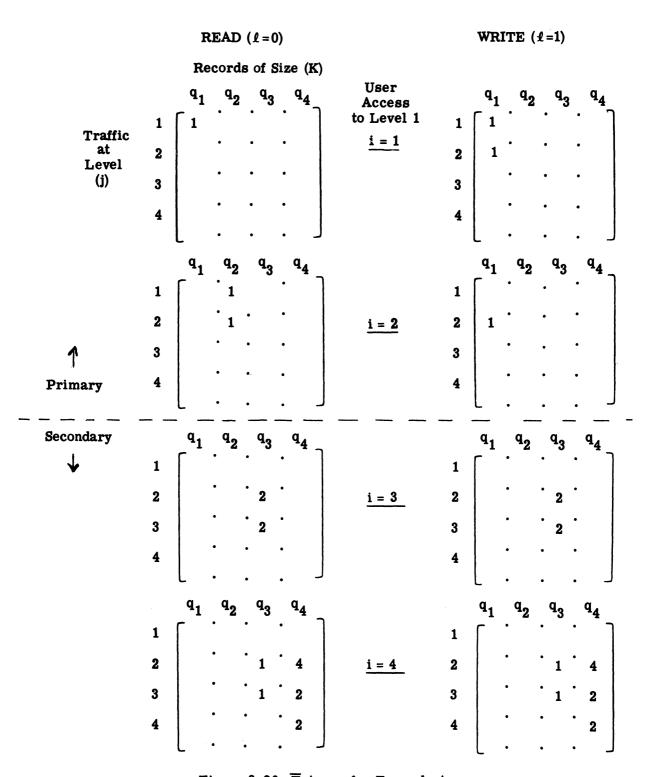

| 3.20  | $\overline{\mathbf{T}}$ Array for Example 4                      | 113  |

| 3.21  | Regions of Storage                                               | 115  |

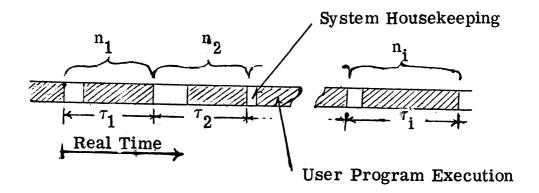

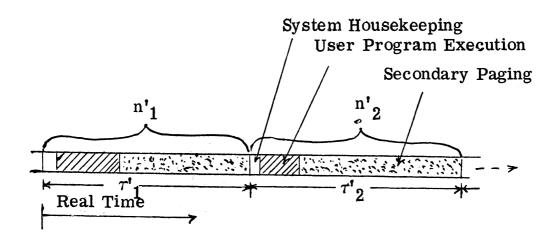

| 3.22  | Periods of User Program Execution                                | 118  |

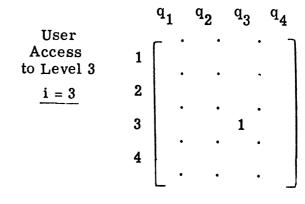

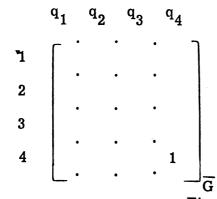

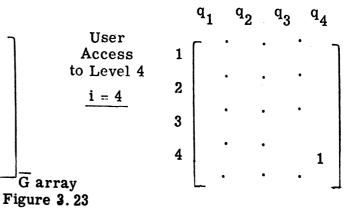

| 3.23  | $\overline{\mathbf{G}}$ Array                                    | 132  |

| 3.24  | 3-Level Hierarchy                                                | 138  |

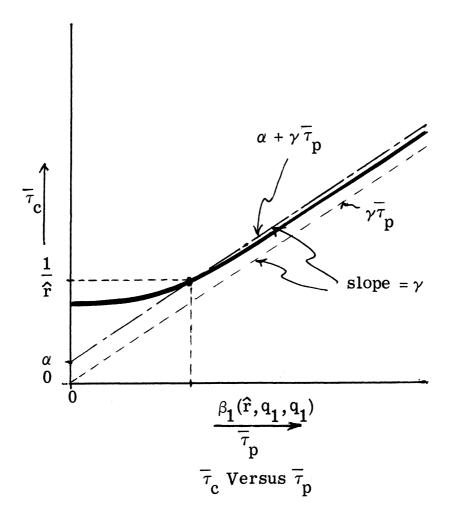

| 3.25  | $\overline{	au}_{	extsf{C}}$ Versus $\overline{	au}_{	extsf{D}}$ | 144  |

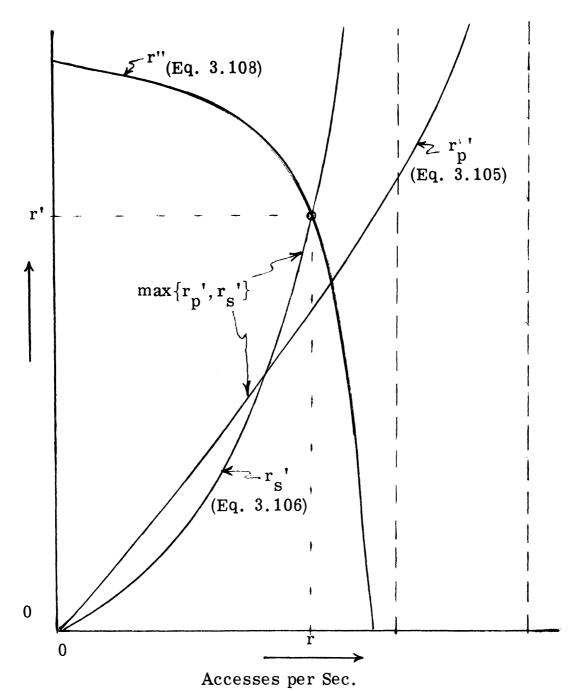

| 3.26  | Primary Bound Operation                                          | 150  |

| 3.27  | Secondary Bound Operation                                        | 152  |

| 3.28  | Solution for r and r'                                            | 158  |

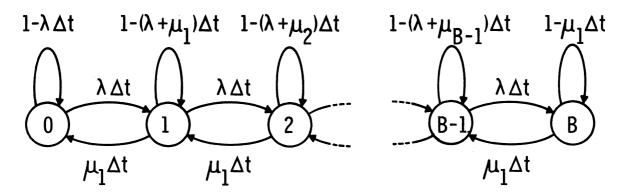

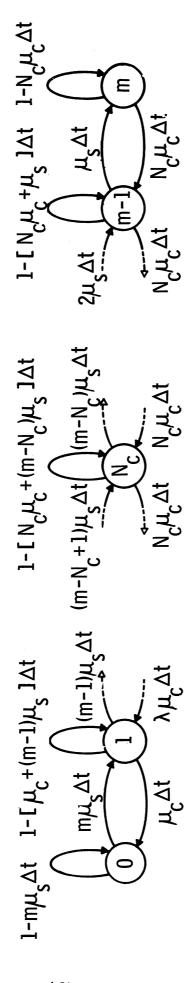

| 4.1   | State Diagram for Basic Model                                    | 164  |

| 4.2   | State Diagram for Basic Model                                    | 165  |

| 4.3   | State Diagram for General Model                                  | 171  |

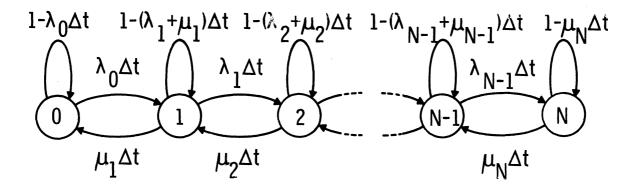

| 4.4   | Service Rate Versus Arrival Rate                                 | 174  |

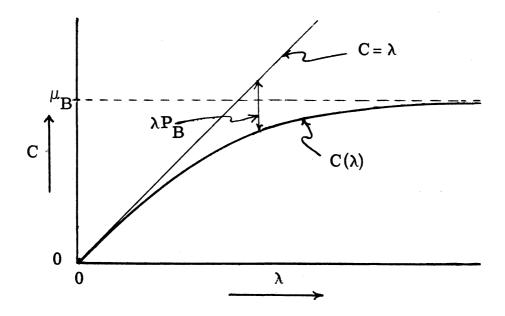

| 4.5   | Disk Service Timing Diagram                                      | 181  |

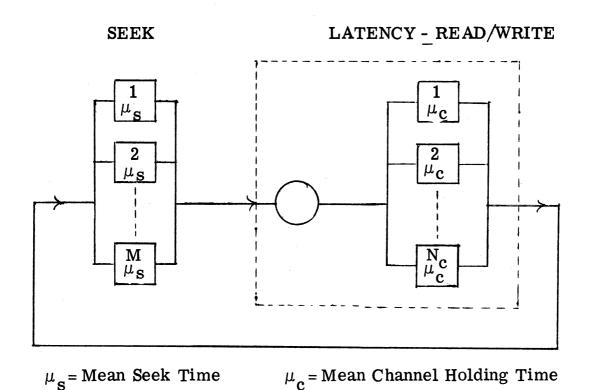

| 4.6   | Channel Queueing Model                                           | 185  |

| 4.7   | State Diagram for Channel Queueing Model                         | 187  |

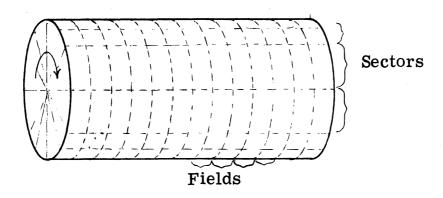

| 4.8   | Drum Sectors and Fields                                          | 193  |

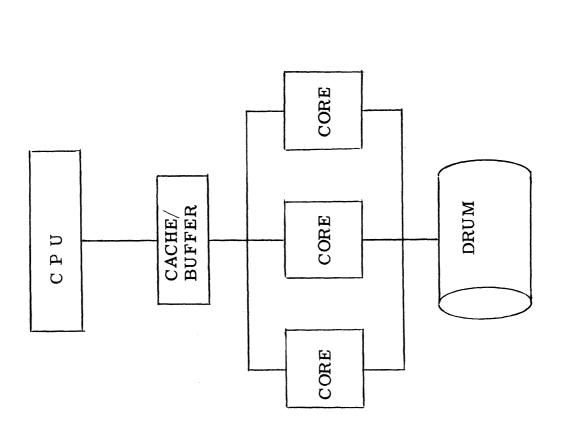

| 5.1   | System Diagram                                                   | 200  |

| 5.2   | System Variables                                                 | 203  |

| 5.3   | Level 1 Hardware Description                                     | 205  |

# LIST OF FIGURES (Continued)

| Figure |                                                       | Page        |

|--------|-------------------------------------------------------|-------------|

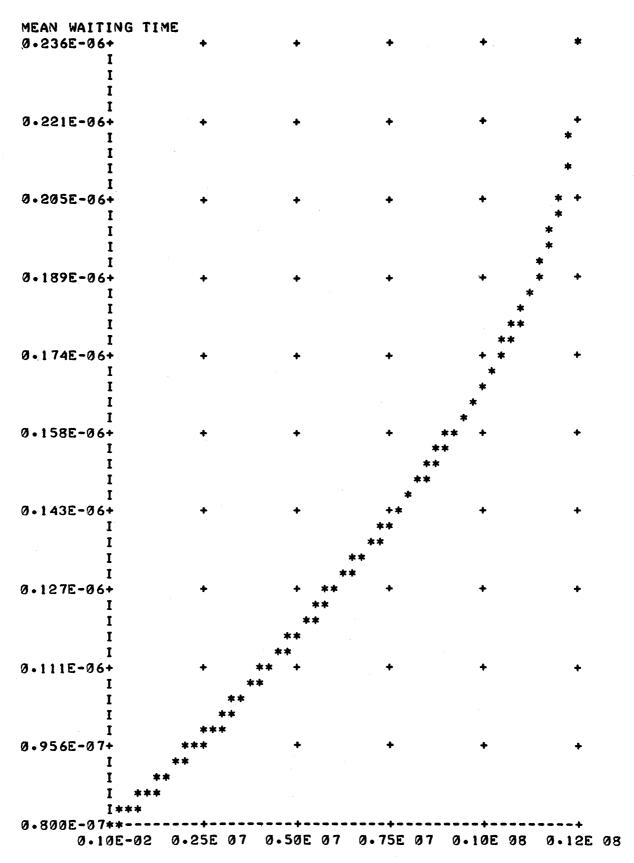

| 5.4    | Level 1 Performance                                   | 206         |

| 5.5    | Level 1 Queueing                                      | 207         |

| 5.6    | Level 2 Hardware Description                          | 210         |

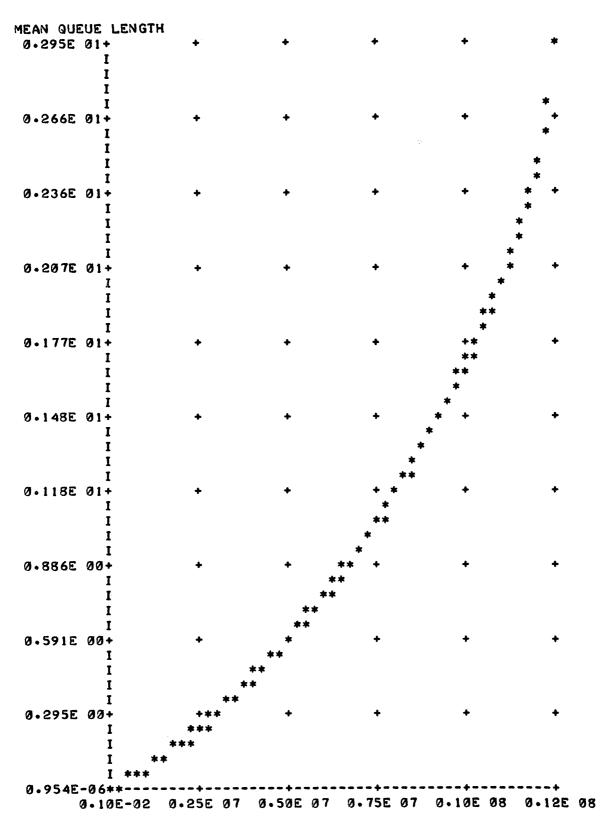

| 5.7    | Level 2 Performance                                   | 211         |

| 5.8    | Level 2 Queueing                                      | 212         |

| 5.9    | Level 3 Hardware Description                          | 215         |

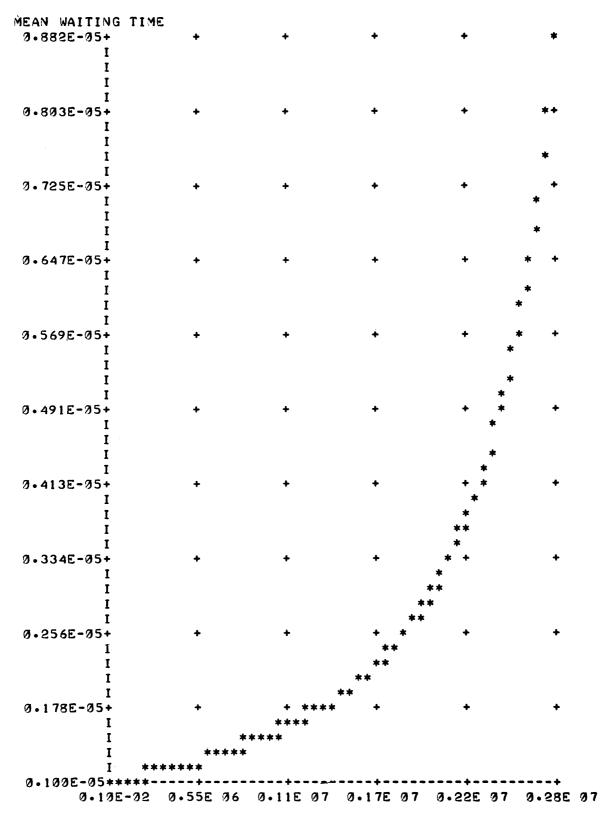

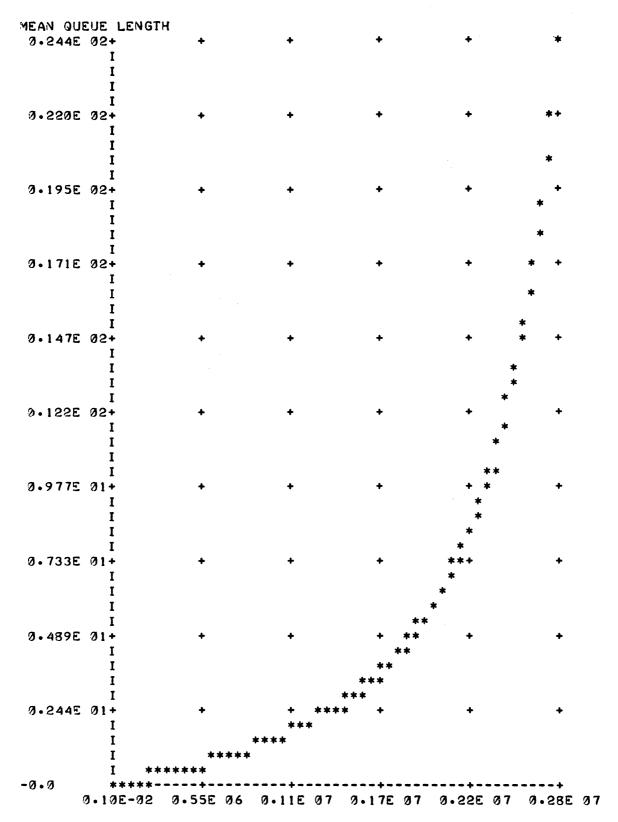

| 5.10   | Level 3 Performance                                   | 216         |

| 5.11   | Level 3 Queueing                                      | 217         |

| 5.12   | Traffic Patterns Resulting From User Program Reads    | 219         |

| 5.13   | Traffic Patterns Resulting From User Program Writes   | 220         |

| 5.14   | The Traffic Array for User Program Reads              | 222         |

| 5.15   | The Traffic Array for User Program Writes             | 223         |

| 5.16   | The Critical Read/Write Array for User Program Reads  | 225         |

| 5.17   | The Critical Read/Write Array for User Program Writes | 226         |

| 5.18   | User Program Specifications                           | <b>22</b> 8 |

| 5.19   | User Program Behavior                                 | 229         |

| 5.20   | Dependent Variables, Part 1, "Standard" Case          | 232         |

| 5.21   | Dependent Variables, Part 2, "Standard" Case          | 233         |

| 5.22   | Dependent Variables, Part 3, "Standard" Case          | 234         |

| 5.23   | Dependent Variables, Part 1, for Drum RPM = 3600      | 243         |

| 5.24   | Dependent Variables, Part 2, for Drum RPM = 3600      | 244         |

| 5.25   | Dependent Variables, Part 3, for Drum RPM = 3600      | 245         |

| 5.26   | Dependent Variables, Part 1, for p=.3                 | 247         |

| 5.27   | Dependent Variables, Part 2, for p=.3                 | 248         |

| 5.28   | Dependent Variables, Part 3, for p=.3                 | 249         |

| 5.29   | Dependent Variables, Part 1, for p=.7                 | 250         |

| 5.30   | Dependent Variables, Part 2, for p=.7                 | 251         |

| 5.31   | Dependent Variables, Part 3, for p=.7                 | 252         |

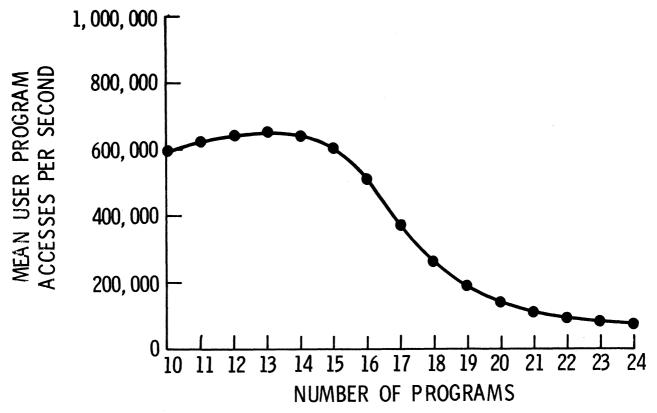

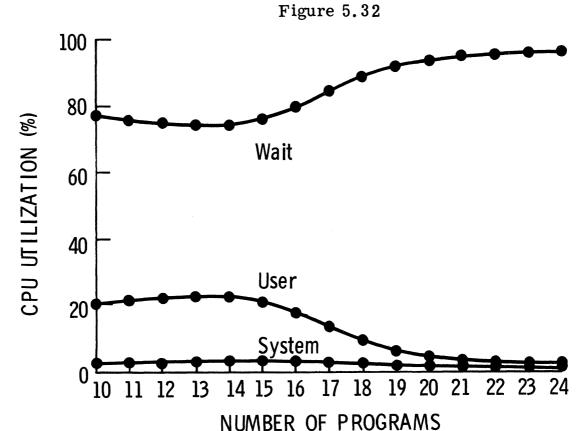

| 5.32   | Performance Versus Number of Programs                 | 254         |

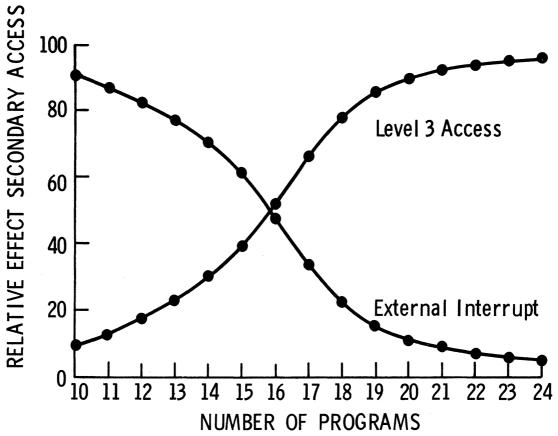

| 5.33   | CPU Utilization Versus Number of Programs             | 254         |

| 5.34   | Relative Effect Versus Number of Programs             | 255         |

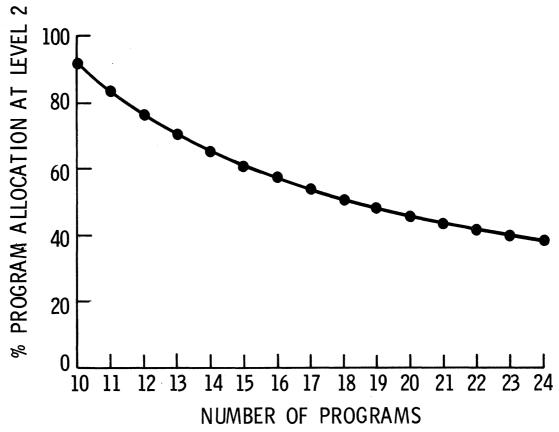

| 5.35   | Allocation Versus Number of Programs                  | 255         |

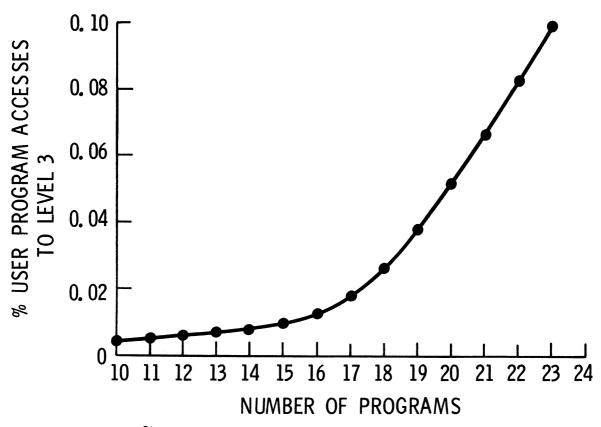

| 5.36   | % of Level 3 Accesses Versus Number of Programs       | 257         |

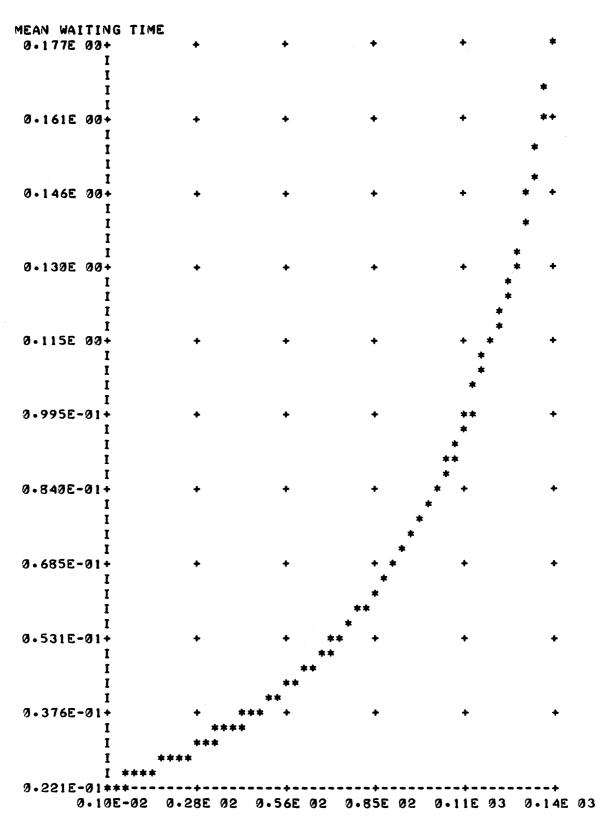

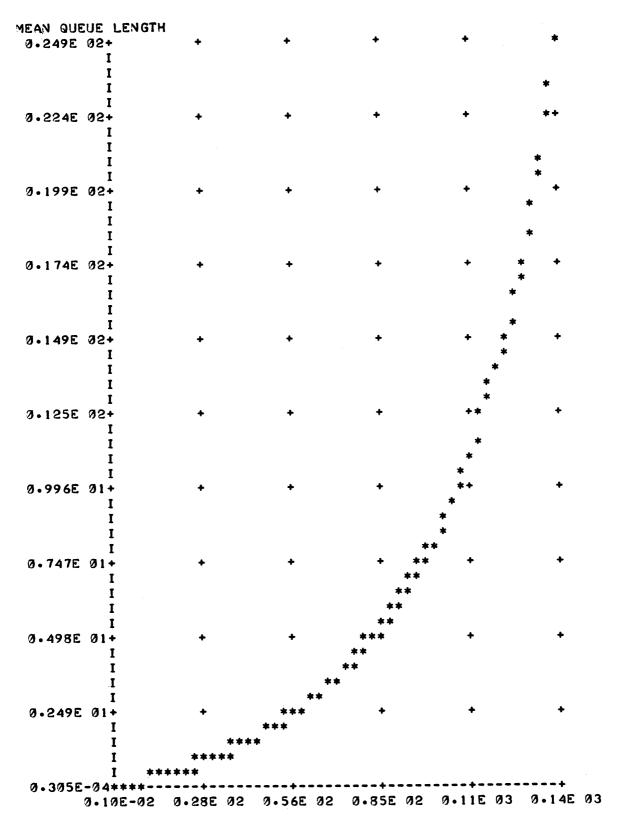

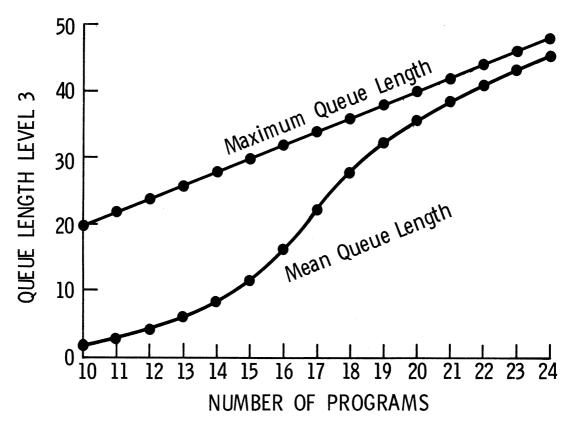

| 5.37   | Queue Length Versus Number of Programs                | 257         |

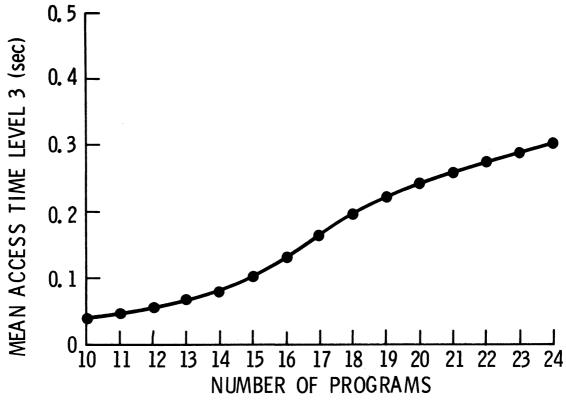

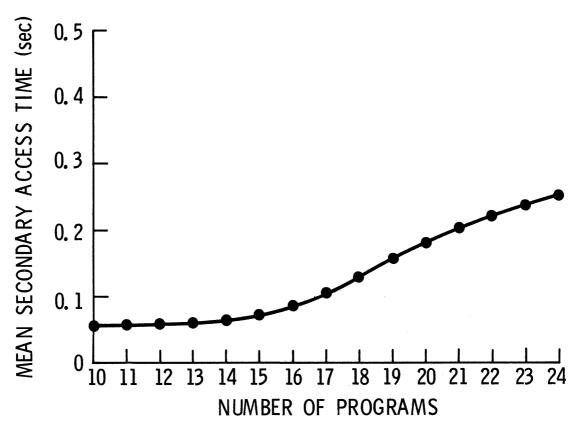

| 5.38   | Access Time Versus Number of Programs                 | <b>2</b> 58 |

| 5.39   | Secondary Access Time Versus Number of Programs       | <b>2</b> 58 |

| 6.1    | Decision Variables for "Standard" Case                | <b>26</b> 8 |

| 6.2    | Decision Variables for Optimal \$250, 000 System      | 269         |

| 6.3    | Dependent Variables, Part 1, for Optimal \$250,000    |             |

|        | System                                                | 270         |

| 6.4    | Dependent Variables, Part 2, for Optimal \$250,000    |             |

|        | System                                                | 271         |

## LIST OF FIGURES (Continued)

| <u>Figure</u> |                                                    | Page        |

|---------------|----------------------------------------------------|-------------|

| 6.5           | Decision Variables, Part 3, for Optimal \$250,000  |             |

|               | System                                             | 272         |

| 6.6           | Decision Variables for Optimal \$300, 000 System   | 274         |

| 6.7           | Decision Variables, Part 1, for Optimal \$300,000  |             |

|               | System                                             | <b>27</b> 5 |

| 6.8           | Dependent Variables, Part 2, for Optimal \$300,000 |             |

|               | System                                             | 276         |

| 6.9           | Dependent Variables, Part 3, for Optimal \$300,000 |             |

|               | System                                             | 277         |

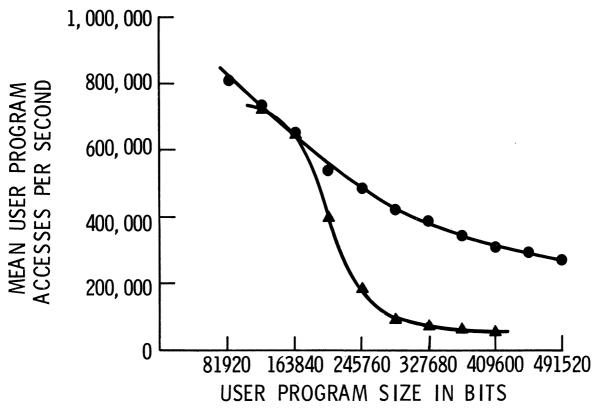

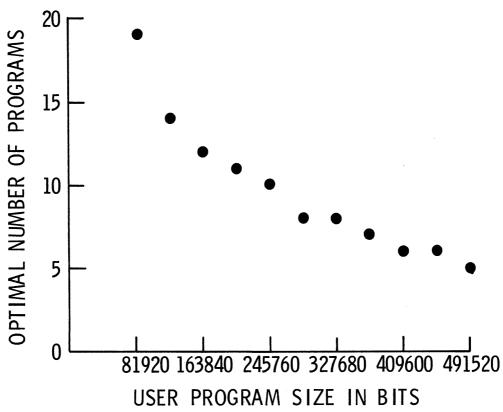

| 6.10          | Performance Versus User Program Size               | 279         |

| 6.11          | Optimal Number of Programs Versus Program Size     | 279         |

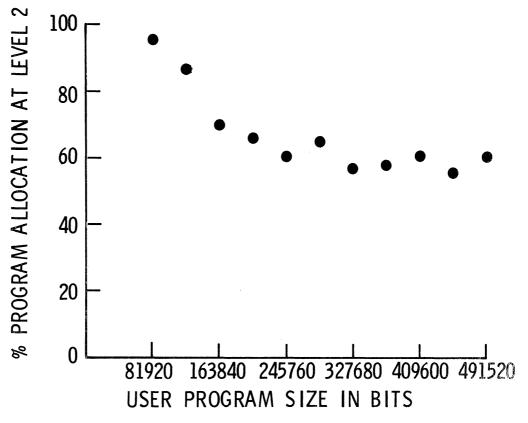

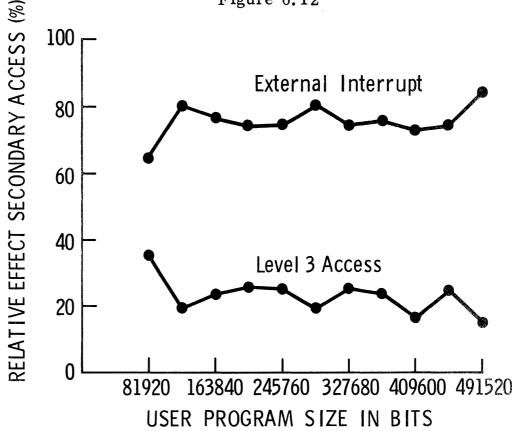

| 6.12          | Allocation Versus User Program Size                | 280         |

| 6.13          | Relative Effect Versus User Program Size           | 280         |

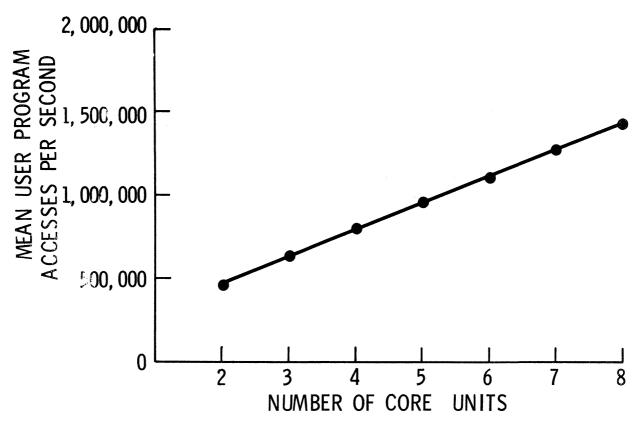

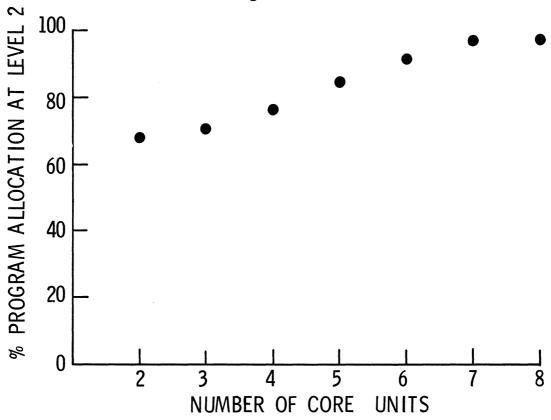

| 6.14          | Optimal Performance Versus Number of Core Units    | 282         |

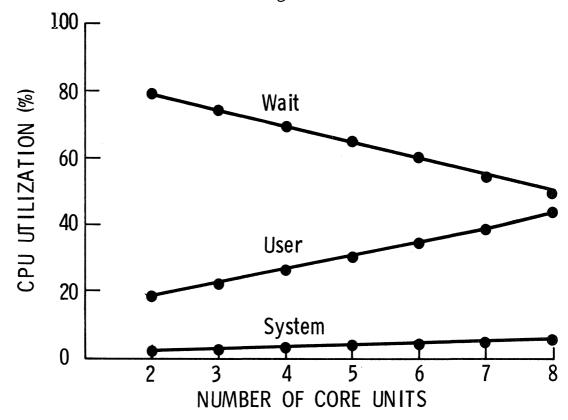

| 6.15          | CPU Utilization Versus Number of Core Units        | 282         |

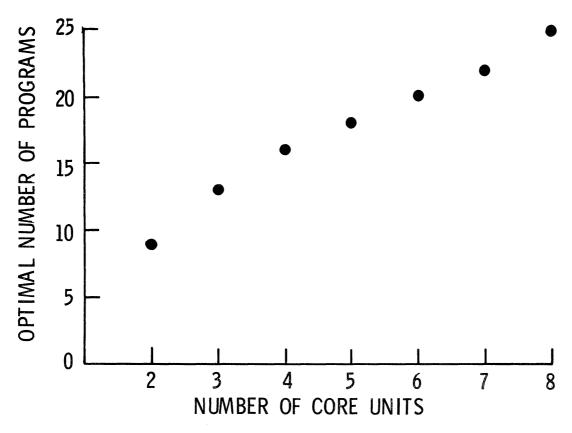

| 6.16          | Optimal Number of Programs Versus Number of Core   |             |

|               | Units                                              | 283         |

| 6.17          | Allocation Versus Number of Core Units             | 283         |

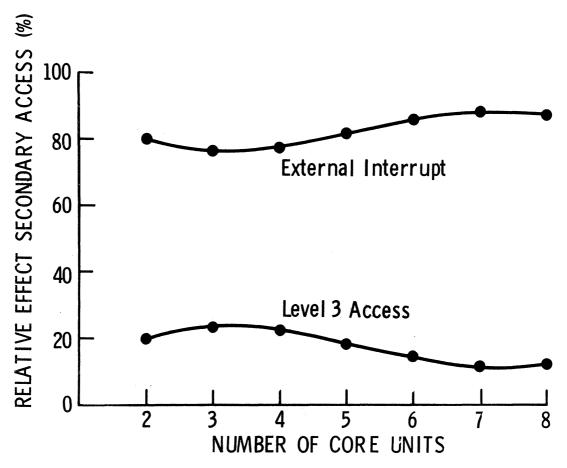

| 6.18          | Relative Effect Versus Number of Core Units        | 284         |

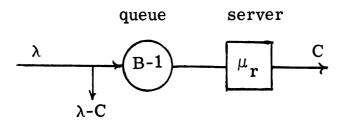

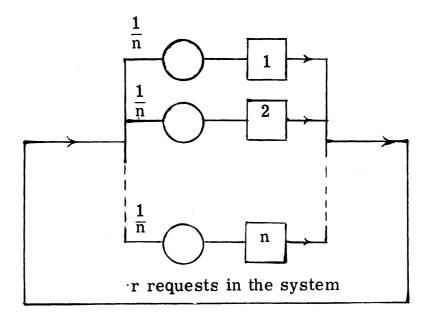

| В1            | Circulating Queue                                  | 300         |

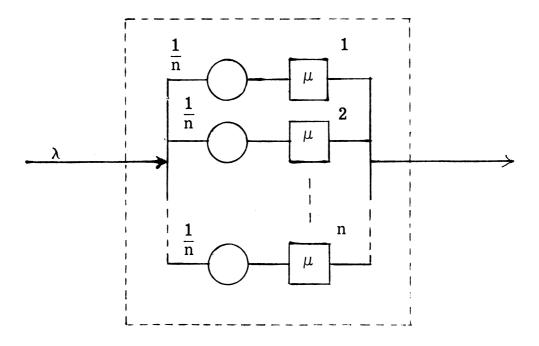

| B2            | Open Queueing Model                                | 305         |

#### Chapter 1

#### Introduction

The design and application of large computing systems involves considerable risk. One can draw a parallel between those who have designed and applied today's computing systems and those who, in the early days of flight, strapped wings to their backs and jumped from the roofs of barns. Neither had adequate methods of predicting system performance. The work reported here attempts to contribute to computer system technology through the development of improved methods of predicting system performance.

#### 1.1 A General Discussion

Throughout the development of computing systems there has been an effort to make a given hardware technology perform better as a system. The primary emphasis in the early days of development was on hardware technology. However, as computing systems have progressed, there has been a continued and growing interest in the design of systems which make the best and most efficient use of a given hardware technology.

One important method of achieving efficient use of a given hardware technology has been the use of storage hierarchies. Storage hierarchies are not unique to computer systems. Your pocket, your desk or dresser drawer and your basement represent a storage hierarchy. The basic idea is simply to store those items used most frequently in an easily accessible location. Those items seldom used may be stored in less accessible and correspondingly less costly locations.

The storage hierarchy was first implemented in a computing system developed at the University of Manchester in England in 1949.

As computer system designed have progressed, two things have happened.

First the complexity of the hierarchy itself has increased. We commonly see systems with 5, 6, or more different kinds of storage hardware capability, for instance registers, cores, drums, disks, data cells, magnetic tapes, punched cards, and punched paper tape. A second and very important change has occurred in the management responsibility of the hierarchy.

The gains achieved by the storage hierarchy have imposed considerable burden upon the programmer. At the outset the programmer was responsible for deciding what information should be stored on what device at each instant of time. In addition the programmer was responsible for carrying out the necessary operations required to move the information about as required. Lastly and very importantly, the programmer was responsible for keeping track of how and where everything was stored as it was moved about in the system. As we have progressed and hierarchies have become more complex the operating systems and hardware have assumed these responsibilities in varying degrees. In some cases all responsibilities for management of a hierarchy have been assumed by the operating system and/or hardware and the hierarchy is invisible to the programmer.

Another area of computer systems development has been in the use of multiprogramming. A computer is often limited by its slowest (or most overworked) component, often an IØ device. One of the methods used to alleviate this problem has been multiprogramming or the practice of working with more than one user program at a time.

One of the effects of multiprogramming is to provide the system with a more balanced workload. If a system processes one program at a time, it will find some programs using a great deal of CPU resource and leaving the IØ devices idle, while others leave the CPU idle and do voluminous IØ. On the other hand, if a system is processing 10 or 20 programs at once, it is unlikely that the system will see this group of programs exhibit the wide variations in resource demand exhibited by the individual programs in the group. In other words system loading is more consistent and predictable when the sample space grows larger.

The second effect of multiprogramming is to introduce parallel paths in the workload as seen by the computing system. If a computing system must follow a single thread of execution, a delay in any part of the system holds up the entire system. Multiprogramming is one way of providing the necessary parallel paths of execution which, if properly used, can increase resource utilization.

The difficulty with multiprogramming is complexity. The problems of resource scheduling are difficult. The problems of protecting one user from another, protecting the operating system itself, and charging for resource use become most complex. However, the rewards for efficient resource utilization can be great. There has been considerable motivation for complexity in the effort to better utilize computing system resources. This has been added to by the response requirements of time-sharing and real time systems.

This need for complexity has placed the modern computing system outside the capability of man's unaided intuition.

#### 1.2 The Nature of the Problem

In very few words the problem is that of predicting and controlling the behavior of complex computing systems using storage hierarchies and multiprogramming.

A computing system using a storage hierarchy generally involves 2 or more different types of storage devices. Different device types have widely varying performance characteristics. Drums, cores and disks all behave differently under load. A system's performance may be determined by a complex balance of workload throughout the system of devices or may be determined by the performance characteristics of a single overworked device.

User programs can be big or small. They can access data in a serial or random manner. They can do large quantities of IØ or almost none at all.

The data paths and routing of information influence the load seen by storage devices. The logical record sizes throughout the

system also influence the load seen by storage devices and in turn their response times.

The number of programs running in a multiprogrammed system affects the storage allocations of user programs. This in turn influences the demands placed on the system by user programs.

All of these factors and many others combine to create an enormously complex and remarkably difficult analysis problem. It is difficult to merely determine what a given system will and will not do in a given circumstance. It is even more difficult to design such systems especially if some kind of optimal or near optimal design is required.

#### 1.3 Objectives

The specific objective of this research is to develop and demonstrate a mathematical model of a computing system. The computing systems in question here fall into the class of those systems using storage hierarchies of 2, 3 or more levels and multiprogramming. The model will exhibit the following characteristics:

- 1. The model will include the effects of user program behavior, operating system characteristics and hardware performance.

- 2. The model will be versatile and easily applied to a wide range of system configurations. The model should be useful as a tool for the investigation of computing systems in general as well as applicable to the detailed investigation of a particular system.

- 3. The model will be useful as a tool for both analysis and optimization.

- 4. The results obtained from the model will approach the accuracy and realism of those obtained from simulation models.

#### 1.4 A Preview

At this point we will attempt a broad preview of the coming chapters. It is hoped that this section will serve to place the contents of the chapters to follow in proper perspective and serve as a reader's guide.

The overall model for computer system analysis is shown in Figure 1.1. On the left we see 3 categories of independent variables. First we have the user program description. This includes independent variables such as the size of the user programs and other characteristics of user program behavior. Next is the storage device descriptions. This includes such items as drum RPM, disk seek time and variables relevant to storage device performance. Last we have data traffic dependencies and architecture. This includes CPU performance characteristics, logical record sizes, data transfer timing dependencies and other global system characteristics. As an output for the model we show performance. In the narrow sense, performance is defined as the mean rate at which the collection of user programs running on the system make reference or access to data and instructions. In the broad sense the performance also includes many

System Analysis Model Figure 1.1

System Model Figure 1.2

details such as mean queue lengths at various devices in the storage system and CPU utilization.

Figure 1.1 shows the model as seen by the designer when being used for analysis. Figure 1.2 shows the model in slightly greater detail and from a different point of view. It is this model that we will deal with in the next 3 chapters. We see that the independent variables on the left have not changed. However, the model shown here does not give us performance (mean user program access rate) directly but rather tells us if an assumed performance is greater than or less than a given system's capability. For analysis we will carry out a simple search to find the performance of a given system. The primary advantage of this particular approach to the problem occurs in optimization where systems are compared in a search for a system configuration with the greatest performance or mean user program access rate.

Figure 1.3 and 1.4 show a detailed breakdown of the model of Figure 1.2. Beginning at the left of Figure 1.3 we see the User Program Model. The independent variables supplied to this model fall into two classes, the user program description and the storage system characteristics. The user program description consists of 5 independent variables which describe the characteristics of the user program. The variables are shown in brackets here for reference in later chapters. The storage system characteristics consist of the

storage allocation at each level in the hierarchy and the logical record size at each level. The user program model, given this information, determines what fraction of a user program's accesses will be directed to each level in the hierarchy of storage. This is referred to and shown in the figure as user program demand. For example, in a two level system with a core and a drum, this would be the fraction of user program references or accesses to storage which are satisfied at the core and the fraction which require drum activity.

The user program model is discussed at length in chapter 2.

The model is an outgrowth of the "lifetime function" concept proposed by Belady and Kuehner [6]. The model is also indebted to the "working set" concept introduced by Denning [21].

The next block in Figure 1.3 shows the System Traffic Model. This model has as its independent variables the assumed mean user program access rate (assumed performance), the user program demand and the data transfer specifications. The data transfer specifications describe what happens when a user program accesses a given level in the hierarchy. We are treating the user program access to a given level as a cause and the activity generated in the system as a result of that access as the effect. The effect takes the form of data transfers in the system. The data transfer specifications describe the data transfers which occur as a result of user program accesses to

Detailed System Model, Part 1

Figure 1.3

Detailed System Model, Part 2

Figure 1.4

some level in the hierarchy. Using this information along with the mean user program access rate and the fraction of user program accesses to each level (user program demand) the System Traffic Model generates a description of the traffic environment at each level in the hierarchy. The traffic environment is given in terms of the mean rate at which records are being read and written at each level, the mean record size being read and written at each level, and the maximum number of requests for service that can be generated by the system for each level. This System Traffic Model is discussed in detail in Chapter 3.

We arrive now at the Storage Device Model at the right hand side of Figure 1.3. The storage device model is actually a collection of models, any one of which can be used to represent the hardware at any level in the storage hierarchy. The device models give us the mean time required to read or write a record of a given size at a given level in the hierarchy. The model independent variables are the traffic environment seen by the level in question and device specification relevant to the device type at that level.

The storage device models are discussed at length in Chapter 4.

Models for core or random access devices, drums, disks, and data

cells have been developed. The models are not particularly unique or

special in any real sense. They are based on finite Markov chains

and require a numerical solution. The models were designed to provide generality of application, realistic results and rapid solution.

Backing away from the details of Figure 1.3, we can review what goes in and what comes out of this portion of the system model. We provide as independent variables a description of user program behavior and some storage system characteristics. From this we learn how the user program behaves in the system. Next, assuming a mean user program access rate and given the data trasfers which occur as a result of user program behavior, we compute the traffic flows at each level in the system. Given this and a description of the hardware at each level we compute the mean time required to read or write records of various sizes at each level. The principal result of the portion of the model shown in Figure 1.3 is simply the mean response time for each of the levels in the hierarchy.

We will now turn to Figure 1.4 where the second portion of the system model is shown. On the left we have the Major Function Timing Model which is discussed in detail in chapter 3. This model is responsible for timing information such as the mean time that a user program remains ineligible for execution following an access to some lower level of storage. The independent variables of this model are the storage device response times, the user program demand, and the data transfer timing dependencies. The data transfer timing dependencies require some explanation.

Imagine a system having a core and a drum. If a user program references some piece of data that happens to be on the drum a record or page will be read from the drum and written in core. There may also be a transfer from the core to the drum in order to make room for the new information coming into core. Here we see the possibility for 4 reads or writes. There is the operation of reading a record from the drum and writing that record in core and reading a record from core and writing it on the drum. However, in a typical system the only delay experienced by the executing program is that of reading the record from the drum. The other reads and writes do occur and do contribute to the congestion in the system but are generally carried out in such a way as to avoid a direct delay in execution. The data transfer timing dependencies specify precisely which reads and writes contribute directly to delays in program execution.

Finally on the right of Figure 1.4 we have the system performance model again covered in Chapter 3. This model has as its independent variables the assumed mean user program access rate, the major function timing information and certain items of a CPU and architecture description. This submodel determines if in fact the assumed mean user program access rate is too high or too low. This completes the model giving us the final result as shown in Figure 1.2.

This description of the model has been necessarily incomplete and simplified somewhat to aid in explanation. The detailed description

of the various model components are found in Chapters 2, 3, and 4 as indicated. Chapter 5 is concerned with examples involving analysis and Chapter 6 with examples of optimization.

Chapters 2, 3, and 4 are long and concentrate on the detailed development of the various parts of the model described. The difficulties of placing the numerous but necessary details in proper perspective may be greatly reduced by becoming familiar with the examples of Chapters 5 and 6. Section 5.2 of Chapter 5 is of particular interest in this regard. A complete example is covered in Section 5.2 including some mention of all of the independent and dependent variables.

#### Chapter 2

#### A Model of Program Behavior

In an effort to identify and describe the characteristics of a computer program or process L. A. Belady and C. J. Kuehner [6] proposed the lifetime function. The lifetime function expresses a program's mean execution interval between references to secondary storage, as a function of the storage allocation in core or primary storage. Belady and Kuehner are not alone in attempting to model this aspect of a process. Very similar constructs have been considered by Peter J. Denning [21]. These efforts are at least in part attempting to determine what part of a program or process must be located in core to avoid an excessive number of transfers between core and drum.

#### 2.1 A General Description of Program Behavior

It is generally agreed that most processes have a non-uniform storage access behavior and that it is meaningful to discuss the currently active part of a process. The concept of the currently active part of a process has been expressed in several different and useful ways. This idea is basic to the question of what part of a process should be in core.

P. J. Denning [21] refers to this currently active part as the working set. In Denning's words, "We define the working set of information  $W(t, \tau)$  of a process at time t to be the collection of

information referenced by the process during the process time interval  $(t-\tau,t)$ ".

Figure 2.1 Definition of  $W(t, \tau)$

There are many other ways to define a set of currently active pages. For instance we may modify the working set by considering t and  $\tau$  of  $W(t,\tau)$  to be real time instead of process time. We might consider a different parameterization such as the set W'(t,n) defined as the n most recently used pages as a function of process time t. This is very similar in concept to the work by L. A. Belady and C. J. Kuehner [6]. Belady and Kuehner define the <u>locality</u> of storage references as a basic program property. "<u>Locality</u> is defined as the total range of storage references during a given execution interval." The remainder of the paper [6] if not the definition of <u>locality</u> would indicate that Belady's notion of locality is very similar to if not W'(t,n).

### The Two Level Hierarchy

The concept of a lifetime function was developed by Belady and Kuehner [6] in the context of a paging system consisting of a

core and a drum. Here we will extend this concept in several ways but first we will consider it in a form close to Belady's original form as developed for two levels of storage.

When a program begins execution following a page fault (a reference requiring a page transfer from the drum) some of its pages will be in core and others generally will not. The precise information contained in core will determine the number of execution cycles required to generate another page fault. Since we are considering a paged system the information contained in core is determined by three factors:

- 1. The method of selecting pages to be paged in and out.

- 2. The number of pages remaining in core.

- 3. The page size.

If we consider 1 and 3 to be fixed we may express the average number of execution cycles required to produce a page fault as a function of 2.

Belady defines his lifetime function as a relation between the size of the core allocation and the average length of an execution interval. In order to get a feel for the general shape of this function let us consider the simple case of completely random accesses. In this case the lifetime function is given in [6] as

$$f(s) = \frac{s/r}{1 - s/r} = s/r + (s/r)^2 + (s/r)^3 + \dots$$

(2.1)

where r is the size of the program in bits and s is the core allocation in bits.

The lifetime function for Random Accesses

Figure 2.2

This function is clearly convex and a curve of this form is shown in Figure 2.2. The general shape of a more realistic lifetime function is shown in Figure 2.3 with a solid line as well as an approximation proposed by Belady. Belady's approximating function is of the following form where a and k are constants to be adjusted to fit specific program behavior

$$f(s) = a s^k (2.2)$$

#### 2.2 Basic Model Description

Belady's functional model for approximating program behavior has several deficiencies.

- 1. The model parameters a and k are not clearly related to properties of the program being modeled.

- 2. The model is valid only over part of the range of s for realistic programs.

- 3. The value of the lifetime function is expressed in units of execution time which limits its use in certain contexts.

In addition to removing the above deficiencies we would like to develop a model which considers the lifetime function as a function of both allocation, s, and page size, q.

We will refer to the model of program behavior developed here as the lifecycle function. This name reflects a change in units from execution time to the number of user program storage references required to produce a page fault.

conclusion by noting that with independent and equally probable random accessing, the specifics of what information is in core are irrelevant.

Thus the lifecycle function is only a function of s and is independent of q.

As an aside we might consider what the optimal page size would be if programs did in fact behave in this manner. Since the lifecycle function is independent of q we have no motivation to make q larger than 1 word. A larger q and its associated information movement would be without effect on the lifecycle function and serve only to clutter channels and devices. This is of course an extreme case and has few representatives in the real world.

Now we will consider a second extreme case one which is the antithesis of the above. Consider a process which accesses storage sequentially from its first location to its last and then continues by repeating these accesses forming a large loop. Here accesses will be made proceeding sequentially through a page and into the next, producing a page fault. If the entire process is not in core (i. e. s < q[Q/q] where [x] is the smallest integer  $\ge x$  and Q is the actual program size) the page needed will have always been paged out. This of course assumes a first in first out, least recently used or similar page out selection algorithm. Since we will produce a page fault at the end of each page we can write

$$f(s,q) = q \text{ for } s < q[Q/q]. \qquad (2.3)$$

Where Q is the actual program size  $\lceil Q/q \rceil$  is the smallest integer  $\geq Q/q$  and  $q\lceil Q/q \rceil$  is the apparent program size as seen by a system with a page size q.

When  $s \ge q[Q/q]$  we may write

$$f(s,q) = \sigma q \text{ for } s \ge q \lceil Q/q \rceil$$

(2.4)

where  $\sigma$  is the number of times the loop is executed.

Again we may stop to consider an optimal page size for processing such a process. It is clear that q should be large, in fact on the order of s,thereby refreshing the entire allocated storage with each page fault. Having considered these two extremes we will now turn to a more realistic model.

#### A Process Model

We will consider here a stochastic model of a process which is in some sense a combination of the two extremes just discussed. We may describe the access behavior as follows:

- 1. Randomly select a location  $\alpha$  in the virtual address space of the process.

- 2. Randomly select a loop length  $\Delta$ .

- 3. Access the  $\Delta$  locations in the loop of 2 above sequentially  $\sigma$  times.

- 4. Repeat the above steps.

Where a loop which extends beyond the last virtual address of the process is continued at the beginning of the virtual address space.

Our pattern of access is then one of a series of loops where both the position and size of the loops change in a random fashion. Our immediate concern will be to develop the lifecycle function f(s,q) for such an access behavior.

#### 2.3 Effects of Program Loop Lengths on Page Faults

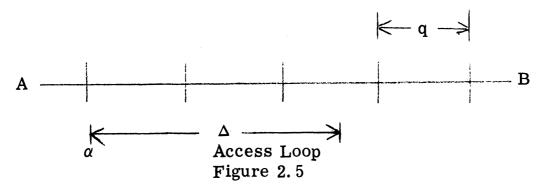

The first step in developing this lifecycle function is to determine the number of distinct pages accessed when accessing the loop. This is a function of two things, the loop length and the position of the loop in virtual address space. The virtual address space can be represented as shown in Figure 2.4.

The Virtual Address Space

Figure 2.4

The line A-B in Figure 2.4 depicts a segment of virtual address space. The division lines represent page boundaries and the boundary is assumed to be part of the page to the right. The page size is q and is in bits.

We will now consider a loop of length  $\Delta$  which begins on a page boundary at the beginning of a page.

Here we may write the number of unique pages accessed in the loop as  $\lceil \Delta/q \rceil$ , where  $\lceil x \rceil$  is defined as the smallest integer  $\geq x$ .

Examining Figure 2.5 we can see that if we move the position of the loop  $\alpha$  to the right the number of unique pages accessed will remain  $\lceil \Delta/q \rceil$  until the right end of the loop crosses a page boundary. At this point the number of pages accessed will increase by 1 to  $\lceil \Delta/q \rceil + 1$  and remain so until the left end of the loop crosses a page boundary. Thus the number of unique pages accessed by a loop of length  $\Delta$  will be either  $\lceil \Delta/q \rceil$  or  $\lceil \Delta/q \rceil + 1$  depending upon the position of the loop in the virtual address space.

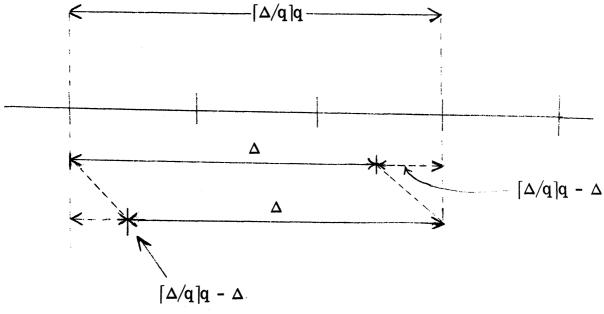

We will now consider what positions of the loop will involve  $\lceil \Delta/q \rceil$  unique pages and what positions of the loop will involve  $\lceil \Delta/q \rceil + 1$  unique pages. We will consider the position of the loop in virtual address space to be indicated by the starting address of the loop or the left end when diagrammed. We will first point out that if it is positioned or begins on any one of the first  $\lceil \Delta/q \rceil q - \Delta$  bit positions a page  $\lceil \Delta/q \rceil$  unique pages will be accessed by the loop.

Figure 2.6 Loop Position

As shown in Figure 2.6 there are  $\lceil \Delta/q \rceil q$  bits in the unique pages accessed by a loop of length  $\Delta$  when the loop is positioned on a page boundary. Thus it is clear that in this case there are  $\lceil \Delta/q \rceil q - \Delta$  bit positions not used by the loop. Thus one may position the loop on any one of the first  $\lceil \Delta/q \rceil q - \Delta$  bit positions of any page and access only  $\lceil \Delta/q \rceil$  unique pages. Correspondingly if the loop is positioned on any one of the  $q - (\lceil \Delta/q \rceil q - \Delta)$  or  $q - \lceil \Delta/q \rceil + \Delta$  bit positions of any page the loop will access  $\lceil \Delta/q \rceil + 1$  unique pages.

We will consider  $\alpha$  the position of each loop, to be a uniformly distributed random variable whose range is the entire virtual address space of the process. Thus we may write the probability of accessing any given number of unique pages in a loop as:

P(accessing N unique pages) =

$$\lceil \Delta/q \rceil - \Delta/q$$

for N =  $\lceil \Delta/q \rceil$  (2.5)

=  $1 - \lceil \Delta/q \rceil + \Delta/q$  for N =  $\lceil \Delta/q \rceil + 1$

= 0 otherwise

#### Page Faults

Up to this point we have considered the number of unique pages accessed by a loop of length  $\Delta$  in a system with a page size q. Here we will consider the number of page faults generated while accessing such a loop.

There are two important factors that must be taken into consideration here. We must determine if the number of unique pages accessed by the loop is greater than the space allocated s/q. If this is the case we will exhibit almost continuous paging. This is the simple result of the fact that as we access sequentially around the loop pages will be paged out before we complete the loop and access them again. Here one might say that the working set is larger than the allocated space.

A second condition occurs if the allocated space, s/q, is larger than or equal to the number of unique pages accessed in the loop. Here we will experience an initial burst of page faults as the pages associated with the loop are paged in and then a period of execution uninterrupted by additional page faults.

A second factor to be considered is that of finding needed pages in core (or some equivalent high level in the hierarchy) as a result of paging which occurred earlier. This means that as we begin each new loop of accesses we may find some of (and possibly all of) the needed pages resident in core.

Our immediate interest will be to find the ratio between the number of accesses made and the number of page faults which occur while accessing a loop  $\Delta$  bits in length  $\sigma$  times. At least initially we will be interested in this ratio as a function of  $\Delta$  the loop length. Thus we will define

$$g(\Delta) = \frac{\text{# of accesses}}{\text{# of page faults.}}$$

(2.6)

In order to express  $g(\Delta)$  it will be necessary to consider several special cases. We will begin by considering the two special cases

$$g(\Delta) = g_1(\Delta)$$

when  $\alpha$  falls in the first  $[\Delta/q]q - \Delta$  bits of a page

$$= g_2(\Delta)$$

when  $\alpha$  falls in the last  $q - [\Delta/q]q + \Delta$  bits of a page (2.7)

where  $\alpha$  is the virtual address position of the beginning of a loop.

The need for these two cases is generated by the different number of unique pages accessed in each case . In Case 1, for  $g_1(\Delta)$ ,  $\lceil \Delta/q \rceil$  and in Case 2, for  $g_2(\Delta)$ ,  $\lceil \Delta/q \rceil + 1$  unique pages are accessed. The development of  $g_1(\Delta)$  and  $g_2(\Delta)$  are quite

similar with this difference of a single page being the only distinction. Thus we will develop  $g_1(\Delta)$  in some detail and write  $g_2(\Delta)$  by extending the same arguments.

# An Expression for $g_1(\Delta)$

As we vary  $\Delta$  we find that  $g_1(\Delta)$  itself falls into two rather special cases. We will consider these two cases as Case 1a and Case 1b and write them as

$$g_1(\Delta) = g_{1a}(\Delta)$$

for  $\lceil \Delta/q \rceil \le s/q$

=  $g_{1b}(\Delta)$  for  $\lceil \Delta/q \rceil > s/q$  (2.8)

To begin, notice that s/q is the number of pages allocated in core. In Case 1a the number of unique pages accessed is less than or equal to this allocation. Thus after the initial accessing of all the pages in the loop no further paging will be required. It should be clear that at most there will be  $\lceil \Delta/q \rceil$  page faults during the accessing of this loop for after the loop has been accessed once all the required pages will be in core and repeated accesses in this loop will produce no further page faults.

Let us now consider Case 1b. Here  $\lceil \Delta/q \rceil > s/q$ , or more unique pages are accessed in the loop than the allocated space in core. This means that as we reach the end of the loop more pages will have been accessed than space has been allocated for. Assuming a least recently used, first in first out or similar page out selection

scheme we may be sure that after accessing the first s/q unique pages in the loop a page fault will occur each time the sequence of accesses crosses a page boundary. This will continue as long as the loop is accessed. Since the loop will be accessed  $\sigma$  times a maximum of  $[\Delta/q]\sigma$  page faults will occur.

### 2.4 Effects of Allocation During Initial Paging

Another factor to be considered is that of finding one or more of the  $\lceil \Delta/q \rceil$  unique pages needed, in core. When the loop now being considered is begun there will be s/q pages in core as a result of one or more previous access loops. These pages may very well be some of those needed in the new loop and may remain in core (i.e. not be paged out) at the time of its first access in the new loop. It is clear at the outset that the number of page faults avoided in this manner is a random variable. It is also apparent that this random variable's mean and density function may be a function of all previous  $\Delta$ 's and  $\alpha$ 's. We will avoid these complications by making certain assumptions and replacing this random variable with its mean. Before we proceed with this, let us recall that our ultimate objective is not to accurately model the described process but to develop a function which may be used to approximate the lifetime functions of real programs. Thus we have a great deal of flexibility in the assumptions we may make as we proceed as long as the final result is suitable and useful for our purposes.

As we begin a new loop we will assume that the s/q pages remaining in core from previous accesses are scattered about randomly in the virtual address space of the process. Thus as we begin the new loop the

probability of finding the first page in core =  $\frac{s/q}{\lceil Q/q \rceil}$

probability of finding the second page in core =  $\frac{s/q - 1}{\lceil Q/q \rceil - 1}$  or in general

probability of finding the ith page in core =  $\frac{s/q - i+1}{[Q/q] - i+1}$  (2.9)

This only holds true for the first s/q pages or the number of pages accessed in the loop whichever is smaller. In the case of the first page accessed there are s/q pages in core and the process uses  $\lceil Q/q \rceil$  pages. On each successive access the number of these left over pages is reduced by one either by the paging out process caused by a page fault or by its use and lack of availability. This of course assumes that  $s < q\lceil Q/q \rceil$  for if  $s \ge q\lceil Q/q \rceil$  no such paging out will occur and the probability of finding the i-th page in core will always be 1. Thus we may write

Prob(i<sup>th</sup> page in core) =

$$\frac{s/q - i+1}{\lceil Q/q \rceil - i+1}$$

for  $s < q\lceil Q/q \rceil$

= 1 for  $s > q\lceil Q/q \rceil$  (2.10)

Unfortunately this expression of probability leads to excessive complications later when we consider a distribution of loop lengths,  $\Delta$ , and integrate with respect to  $\Delta$ . However we can successfully approximate using

$$Prob(i^{th} page in core) = \frac{s/q - i+1}{\lceil Q/q \rceil} \quad for s < q \lceil Q/q \rceil$$

$$= 1 \quad for s \ge q \lceil Q/q \rceil \quad (2.11)$$

There are several reasons why this approximation serves us well. First it is reasonably accurate for small i and small i's predominate. The value of i cannot exceed s/q or  $\lceil \Delta/q \rceil + 1$ . This means that in order to be involved with large i's, we must have both a large allocation s and a long loop length  $\Delta$ . Second we will be using a summation of these probabilities for i = 1 to  $\lceil \Delta/q \rceil$  or in some cases  $\lceil \Delta/q \rceil + 1$ . The values of the terms in both Equation 2.10 and 2.11 decrease with increasing i. Thus the dominant terms in the series are those with small i for which the approximation is most accurate.

We may write the expected value of the number of such "free" pages which will occur with each new loop as

$$\sum_{i=1}^{K} \frac{s/q - i+1}{\lceil Q/q \rceil} = \frac{K(s/q + 1) - \sum_{i=1}^{K} i}{\lceil Q/q \rceil}$$

$$= \frac{K s/q + K - K(K+1)/2}{\lceil Q/q \rceil} \qquad (2.12)$$

for s < q[Q/q]

and

$$\sum_{i=1}^{K} 1 = K \qquad \text{for } s \ge q[Q/q]$$

where  $K = \lceil \Delta/q \rceil$  in case 1a

and K = s/q in case 1b

We will digress for a moment to insure that the source of the two values of K above is clear. In case 1a the number of pages referenced is less than or equal to the number allocated. In this case we must terminate the sum at the number of unique pages accessed which is  $\lceil \Delta/q \rceil$ . In case 1b the number of unique pages referenced is greater than the number allocated. The number allocated is s/q and we can only expect to find "free" pages during the first s/q unique page accessed.

Making these substitutions for case 1a and 1b: Case 1a substituting  $K = \lceil \Delta/q \rceil$

when s < q[Q/q]

$$\sum_{i=1}^{\lceil \Delta/q \rceil} \frac{s/q - i + 1}{\lceil Q/q \rceil} = \frac{s/q \lceil \Delta/q \rceil + \lceil \Delta/q \rceil - \frac{1}{2} \lceil \Delta/q \rceil^2 - \frac{1}{2} \lceil \Delta/q \rceil}{\lceil Q/q \rceil} = \frac{[\Delta/q] (s/q - \frac{1}{2} \lceil \Delta/q \rceil) + \frac{1}{2} \lceil \Delta/q \rceil}{\lceil Q/q \rceil}$$

$$= \frac{\lceil \Delta/q \rceil (s/q - \frac{1}{2} \lceil \Delta/q \rceil) + \frac{1}{2} \lceil \Delta/q \rceil}{\lceil Q/q \rceil}$$

when  $s \ge q[Q/q]$

$$\sum_{i=1}^{\lceil \Delta/q \rceil} 1 = \lceil \Delta/q \rceil$$

(2. 14)

Case 1b substituting K = s/q

when s < q[Q/q]

$$\sum_{i=1}^{s/q} \frac{s/q - i+1}{[Q/q]} = \frac{s/q (s/q + 1) - s/q (s/q + 1)/2}{[Q/q]}$$

$$= \frac{1}{2[Q/q]} (s^2/q^2 + s/q)$$

(2.15)

Recalling that case 1b occurs when

$\lceil \Delta/q \rceil > s\lceil Q/q \rceil$ , Equation (2.8), and that  $\lceil \Delta/q \rceil \leq \lceil Q/q \rceil$  we see that in case 1b

$$s < q[\Delta/q] \le q[Q/q] \qquad (2.16)$$

Thus in case 1b it is always the case that  $s < q \lceil Q/q \rceil$

Here we will substitute the expected number of "free" pages for the actual number of the pages which is a random variable

(except when  $s \ge q[Q/q]$ ). By subtracting the number of "free" pages from the number of possible page faults we will obtain the number of actual page faults. There are several cases:

# of page faults (1a) =

$$\lceil \Delta/q \rceil$$

-  $\frac{\lceil \Delta/q \rceil (s/q - \frac{1}{2} \lceil \Delta/q \rceil) + \frac{1}{2} \lceil \Delta/q \rceil}{\lceil Q/q \rceil}$

=  $\lceil \Delta/q \rceil [1 - \frac{s}{q \lceil Q/q \rceil} - \frac{1}{2 \lceil Q/q \rceil} + \frac{1}{2 \lceil Q/q \rceil} \lceil \Delta/q \rceil]$

for  $s < q \lceil Q/q \rceil$

=  $\lceil \Delta/q \rceil - \lceil \Delta/q \rceil = 0$  for  $s \ge q \lceil Q/q \rceil$

# of page faults (1b) =

$$\lceil \Delta/q \rceil \sigma - \frac{1}{2\lceil Q/q \rceil}$$

(s<sup>2</sup>/q<sup>2</sup> + s/q) (2.18)

for s < q[Q/q]

(Note s never equals q[Q/q] in case 1b)

In all cases the number of accesses made is the same.

# of accesses =

$$\Delta \sigma/q'$$

(2.19)

where  $q' = \#$  of bits in a word.

Thus we may write:

Case 1a:

$$g_{1a}(\Delta) = \frac{\Delta \sigma/q'}{\left[\Delta/q\right]\left[\left(1 - \frac{s}{q[Q/q]} - \frac{1}{2[Q/q]} + \frac{1}{2[Q/q]} \left[\Delta/q\right]\right]} (2.20)$$

for  $\lceil \Delta/q \rceil \le s/q$

and s < q[Q/q]

$$=\frac{\Delta \sigma/q'}{0} = \infty \tag{2.21}$$

for  $\lceil \Delta/q \rceil < s/q$

and s > q[Q/q]

and

$$g_{1b}(\Delta) = \frac{\Delta \sigma/q'}{[\Delta/q]\sigma - \frac{1}{2[Q/q]} (s^2/q^2 + s/q)}$$

(2.22)

for

$$\lceil \Delta/q \rceil > s/q$$

The expressions for  $g_{2a}(\Delta)$  and  $g_{2b}(\Delta)$  may be obtained directly from  $g_{1a}(\Delta)$  and  $g_{1b}(\Delta)$  by substituting  $[\Delta/q] + 1$  for  $[\Delta/q]$ . This does not fall into the category of those things which are intuitively clear even to the most casual observer. However we will not go into a lengthy justification here because the development of case 2 is identical to case 1 which we have just considered. Any

questions concerning case 2 may be resolved by referring to the discussion of case 1 and substituting 2a, 2b and  $\lceil \Delta/q \rceil + 1$  in the appropriate places.

We may write  $g_{2a}(\Delta)$  and  $g_{2b}(\Delta)$  as follows.

and

$$g_{2b}(\Delta) = \frac{\Delta \sigma/q'}{([\Delta/q] + 1) \sigma - \frac{1}{2[Q/q]} (s^2/q^2 + s/q)}$$

(2. 25)

for

$$\lceil \Delta/q \rceil + 1 > s/q$$

#### Note:

We will make a small alteration to the expressions for  $\mathbf{g_{1a}(\Delta),\ g_{1b}(\Delta),\ g_{2a}(\Delta)\ and\ g_{2b}(\Delta)\ at\ a\ later\ point\ in\ the\ text.}$

#### 2.5 Consideration of a Distribution of Loop Lengths

In order to compute  $E[g(\Delta)]$  we must have a density function for  $\Delta$ . The question arises as to what should such a density function look like. One would imagine that a real program would be best modeled by a number of fixed length loops in addition to several variable length loops. The fixed length loops are generated by such things as actual DO loops. Variable length loops are generated by such activities as searching a list for some value. This would produce a density function containing a number of "spikes". However, the level of this model does not lend itself to such a detailed description of a program. We can however consider a density function with a single dominant peak with appropriate variables which allow control over the sharpness and the position of the peak. A function of the form

$$\frac{1}{a + (b - \Delta)^2}$$

provides us with the needed peak and control over the sharpness of the peak. Here the peak will occur at  $\Delta$  = b and will have a maximum value of 1/a.

For our purposes we will choose the constants in the equation to more closely suit our problem. Thus choosing

$$\frac{1}{\frac{1}{e^2} + \left(p - \frac{\Delta}{\lceil Q/q \rceil q}\right)^2}$$

(2. 26)

as our basic function we may position the peak at any point in the virtual address space by choosing a p in the range  $0 \le p \le 1$ . Thus if we wish to locate the peak of the distribution of  $\Delta$ 's at .2 of the length of the program then we choose p=.2. Notice that as we change the size of the program the peak will remain in the same relative position. We will consider this aspect in more detail later.

In order to make this function into a density function we must normalize it. Taking the integral

$$\int_{0}^{[Q/q]q} \frac{d\Delta}{\frac{1}{e^{2}} + (p - \frac{\Delta}{[Q/q]q})^{2}} = q[Q/q]e[tan^{-1}(\frac{e}{q[Q/q]}\Delta - ep)]_{0}^{[Q/q]q}$$

$$= q[Q/q]e[tan^{-1}e(1-p) + tan^{-1}ep]$$

(2. 27)

and normalizing we have a density function for  $\Delta$

$$f_{\Delta}(\Delta) = \frac{1}{q[Q/q]e[\frac{1}{e^{2}} + (p - \frac{\Delta}{[Q/q]q})^{2}][tan^{-1}e(1-p) + tan^{-1}ep]}$$

$$for 0 \le \Delta \le [Q/q]q$$

$$= 0 for 0 > \Delta > [Q/q]q$$

Although this appears to be rather complex it is simply of the form

$$\frac{1}{a\Delta^2 + b\Delta + c}$$

where the constants a, b and c are rather cumbersome.

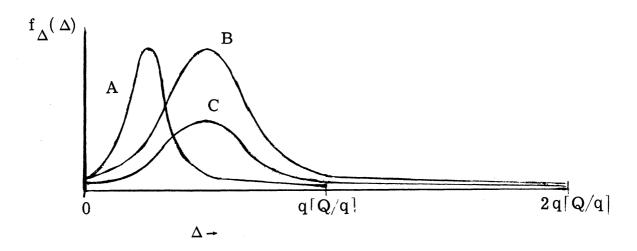

This density function was purposely constructed so that changes in the program size Q produce reasonable changes in the density function  $f_{\Delta}(\Delta)$ . The assumption has been made that as the size of a program increases the size of the access loops increase proportionally. The inclusion of  $\lceil Q/q \rceil q$ , the number of bits associated with the process, in this function performs exactly that function. We may draw a graph to illustrate this. Figure 2.7 shows what happened to the density function when the number of pages used by the program is doubled. Curve A depicts the density function for a program using  $\lceil Q/q \rceil$  pages. Here p=.25 making the most frequent loop length 1/4 the size of the program. A program using twice as many pages  $2\lceil Q/q \rceil$  but with the same p and e parameters would appear as curve C. Curve C may be obtained by

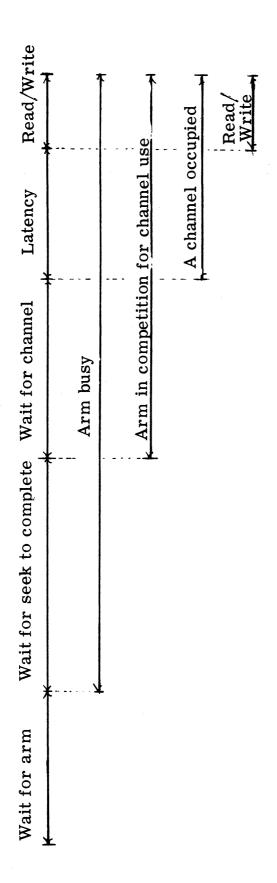

The Δ Distribution Figure 2.7

first making a simple linear scale change to obtain curve B and then normalizing to obtain curve C.

There is another aspect of normalizing with respect to q[Q/q]which must be considered. The term q[Q/q] represents the apparent size of the program when the actual size is Q and the page size is q. Thus we see that the probability of a given loop length is affected by the page size. For instance if a program's actual size Q is "poorly" matched to the page size q the program will appear larger due to wasted space. We will assume that this wasted space is scattered at random throughout the programs virtual address space and thereby expands the length of loops being executed. This has one effect which must be corrected for. Earlier we said that the number of accesses made by a loop of length  $\Delta$  traversed  $\sigma$  times would be  $\Delta \sigma/q$  where q' is the word size. However the process of normalizing the distribution of  $\Delta$  to the apparent size of the program means that loops contain wasted space which does not contribute to actual program accesses. In order to account for this wasted space contained in loops we will express the number of program accesses in a given loop as:

# of accesses =

$$\frac{\Delta \sigma}{q'} \frac{Q}{q[Q/q]}$$

(2.29)

The term  $\frac{Q}{q\lceil Q/q\rceil}$  can be recognized as the ratio between the actual size of the program and the apparent size of the program. Including

this change the expressions for  $g_{1a}(\Delta)$ ,  $g_{1b}(\Delta)$ ,  $g_{2a}(\Delta)$  and  $g_{2b}(\Delta)$  become:

$$g_{1a}(\Delta) = \frac{(\Delta \sigma/q') (Q/q[Q/q])}{[\Delta/q][(1 - \frac{s}{q[Q/q]} - \frac{1}{2[Q/q]} + \frac{1}{2[Q/q]} [\Delta/q]]}$$

(2.30)

for  $\lceil \Delta/q \rceil \le s/q$

for s < q[Q/q]

$$= \frac{\Delta \sigma/q'}{0} = \infty \tag{2.31}$$

for  $\lceil \Delta/q \rceil \leq s/q$

and  $s \ge q[Q/q]$

$$g_{1b}(\Delta) = \frac{(\Delta \sigma/q') (Q/q[Q/q])}{[\Delta/q]\sigma - \frac{1}{2[Q/q]} (s^2/q^2 + s/q)}$$

(2.32)

for  $\lceil \Delta/q \rceil > s/q$

$$g_{2a}(\Delta) = \frac{(\Delta \sigma/q') (Q/q \lceil Q/q \rceil)}{(\lceil \Delta/q \rceil + 1) \left[ (1 - \frac{s}{q \lceil Q/q \rceil} - \frac{1}{2 \lceil Q/q \rceil}) + \frac{1}{2 \lceil Q/q \rceil} (\lceil \Delta/q \rceil + 1) \right] }$$

(2.33) for  $\lceil \Delta/q \rceil + 1 \le s/q$  and  $s < q \lceil Q/q \rceil$

and

$$g_{2b}(\Delta) = \frac{(\Delta \sigma/q') (Q/q[Q/q])}{([\Delta/q] + 1) \sigma - \frac{1}{2[Q/q]} (s^{2}/q^{2} + s/q)}$$

$$for [\Delta/q] + 1 > s/q$$

(2.35)

# 2.6 Final Model Development

We may express the expected value of  $g(\Delta)$  as

$$E[g(\Delta)] = \int_{0}^{q[Q/q]} [g_{1}(\Delta) P(Case 1 | \Delta) f_{\Delta}(\Delta)$$

$$+ g_{2}(\Delta) P(Case 2 | \Delta) f_{\Delta}(\Delta) ]d\Delta$$

(2. 36)

This integral must be divided into three separate integrals in order to accommodate the changes in functional representation which occur at  $\Delta=qs[Q/q]-1$  and  $\Delta=qs[Q/q]$ . Thus it will take the form  $E[g(\Delta)]=\int_0^{(s-q)}[g_{1a}(\Delta)\ P(Case\ 1|\Delta)f_{\Delta}(\Delta)\ +g_{2a}(\Delta)\ P(Case\ 2|\Delta f_{\Delta}(\Delta)]d\Delta$

$$+ \int_{s-q}^{s} [g_{1a}(\Delta) \ P(Case \ 1 \big| \Delta) f_{\Delta}(\Delta) \ + g_{2b}(\Delta) \ P(Case \ 2 \big| \Delta) f_{\Delta}(\Delta) ] d\Delta$$

$$+ \int_{s}^{q[Q/q]} [g_{1b}(\Delta) P(Case 1 | \Delta) f_{\Delta}(\Delta) + g_{2b}(\Delta) P(Case 2 | \Delta) f_{\Delta}(\Delta)] d\Delta$$

(2.37)

The probabilities P(Case  $1 | \Delta$ ) and P(Case  $2 | \Delta$ ) may be taken from Equation (2.5). They are:

$$P(\text{Case 1}|\Delta) = \lceil \Delta/q \rceil - \Delta/q \qquad (2.38)$$

$$P(\text{Case 2}|\Delta) = 1 - [\Delta/q] + \Delta/q \qquad (2.39)$$

We can at this point simplify our equations considerably. We will proceed by examining the terms in the above integrals in some detail. Beginning with the term in the first integral we will factor out  $f_{\Delta}(\Delta)$  giving us

$$[g_{1a}(\Delta) P(Case 1 | \Delta) + g_{2a}(\Delta) P(Case 2 | \Delta)] f_{\Delta}(\Delta)$$

(2.40)

Let us now consider the function  $g_{1a}(\Delta)$  in some detail. Rewriting it

$$g_{1a}(\Delta) = \frac{(\Delta \sigma/q') (Q/q[Q/q])}{[\Delta/q][(1 - s - \frac{1}{2[Q/q]}) + \frac{1}{2[Q/q]} [\Delta/q]]}$$

(2.41)

$$\text{ for } \lceil \Delta/q \rceil \, \le \, \, s\lceil Q/q \rceil$$

and

$$s \neq 1$$

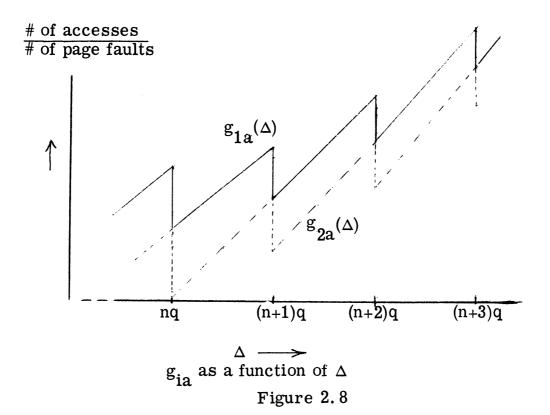

Notice that between values where  $\lceil \Delta/q \rceil$  changes abruptly  $g_{1a}(\Delta)$  increases linearly with  $\Delta$ . This is simply because only the numerator contains a  $\Delta$  that is not in the form  $\lceil \Delta/q \rceil$  and this  $\Delta$  is in effect multiplied times a constant except in the neighborhood of points where  $\Delta/q$  is an integer. Thus we would expect a graph of  $g_{1a}(\Delta)$  to be a series of straight lines connected by discontinuities.

The form of  $g_{2a}(\Delta)$  is the same as  $g_{1a}(\Delta)$  except that  $\lceil \Delta/q \rceil$  is replaced by  $\lceil \Delta/q \rceil + 1$ . It should be clear that our comments about  $g_{1a}(\Delta)$  also apply to  $g_{2a}(\Delta)$ .

Another most important characteristic of these two functions is that

$$g_{2a}(\Delta) = \lim_{\epsilon \to 0} g_{1a}(\Delta + \epsilon) \text{ for } \Delta/q = \text{integer}$$

(2.42)

In Figure 2.8 we show a graph of  $g_{1a}(\Delta)$  and  $g_{2a}(\Delta)$  showing the characteristics we have just discussed.

Next we would like to turn to a detailed examination of the term

$$[g_{1a}(\Delta) P(Case 1 | \Delta) + g_{2a}(\Delta) P(Case 2 | \Delta)]$$

(2.43)

over a range of delta from nq to (n+1)q. Figure 2.9 shows three graphs one displayed a detailed graph of  $g_{1a}(\Delta)$  and  $g_{2a}(\Delta)$  and two others showing P(Case  $1|\Delta$ ) and P(Case  $2|\Delta$ ) over the same range.

If we examine these graphs and the term in question we can see that at a point just to the right of  $\Delta=nq$  (or  $\Delta=nq+\varepsilon$  where  $\varepsilon$  is arbitrarily small) the Expression 2.43 is equal to  $g_{1a}(\Delta)$ . Correspondingly at the other end of the range where  $\Delta=(n+1)q$  the expression is equal to  $g_{2a}(\Delta)$ . The value of the expression clearly begins on the left equal to  $g_{1a}(\Delta)$  and progresses between the two function  $g_{1a}(\Delta)$  and  $g_{2a}(\Delta)$  equaling  $g_{2a}(\Delta)$  at the page boundary. The expression is clearly never greater than  $g_{1a}(\Delta)$  nor less than  $g_{2a}(\Delta)$ .

The Components of  $H_1(\Delta)$ Figure 2.9

We will replace Expression 2.43 with the function

$$H_{1}(\Delta) = \frac{(\Delta \sigma/q') (Q/q[Q/q])}{(\Delta/q + 1)[(1 - \frac{s}{q[Q/q]} - \frac{1}{2[Q/q]}) + \frac{1}{2[Q/q]} (\Delta/q + 1)]}$$

$$= \frac{2 \sigma q Q}{q'} \times \frac{\Delta}{(\Delta + q)(2(q[Q/q] - s) + \Delta)} \qquad (2.44)$$

We can recognize  $H_1(\Delta)$  as  $g_{2a}(\Delta)$  where  $\lceil \Delta/q \rceil$  has been replaced by  $\Delta/q$ .  $H_1(\Delta)$  is clearly an exact replacement for Expression 2.43 at page boundaries and is a smooth function which conforms to

$$g_{2a}(\Delta) \leq H_1(\Delta) \leq g_{1a}(\Delta).$$

(2.45)

Keeping in mind that we will be integrating the product  $H_1(\Delta) f_{\Delta}(\Delta)$  it is clear that any errors introduced by the use of  $H_1(\Delta)$  are trivial when compared to the rather arbitrary choice of  $f_{\Delta}(\Delta)$ .

If we examine the other two integrals of Equation 2.37 we see that the situation in each is approximately the same. In each we have two functions which are straight lines between page boundaries and have discontinuities at the page boundaries. Figure 2.10 shows the general form of the functions  $g_{1a}(\Delta)$ ,  $g_{2a}(\Delta)$ ,  $g_{1b}(\Delta)$  and  $g_{2b}(\Delta)$ . In this plot we have plotted these functions over the ranges where they appear in the integrals of Equation 2.37 in the case of s=5q.

Turning to the third integral of Equation 2.37 we will replace the term

$$[g_{1b}(\Delta) P(Case 1 | \Delta) + g_{2b}(\Delta) P(Case 2 | \Delta)]$$

(2.46)

with

$$H_{3}(\Delta) = \frac{(\Delta \sigma/q') (Q/q[Q/q])}{(\Delta/q + 1) \sigma - \frac{1}{2[Q/q]} (s^{2}/q^{2} + s/q)}$$

(2.47)

$$= \frac{Q}{q'[Q/q]} \times \frac{\Delta}{(\Delta + (q - \frac{q}{2\sigma[Q/q]}(s^2/q + s/q)))}$$

The function  $H_3(\Delta)$  can be recognized as  $g_{2b}(\Delta)$  where  $[\Delta/q]$  has been replaced by  $\Delta/q$ . Again  $H_3(\Delta)$  is equal to the expression in question at page boundaries and satisfies

$$g_{2b}(\Delta) \leq h_3(\Delta) \leq g_{1b}(\Delta) \tag{2.48}$$

In the case of the second integral of Equation 2.37 we will factor out the term

$$[g_{1a}(\Delta) \text{ P(Case 1}|\Delta) + g_{2b}(\Delta) \text{ P(Case 2}|\Delta)].$$

(2.49)

This term combines both cases a and b and is illustrated in Figure 2. 10 in the range of  $\Delta$  from 5q to 6q. We will replace this term with a straight line which connects the values of the term at the page boundaries. The general form of this approximation will be simply

$$H_2(\Delta) = (\text{slope}) \Delta + (\text{constant}).$$

(2.50)

Since the value of  $H_1(\Delta)$  and  $H_2(\Delta)$  is exact at the page boundaries we may compute the slope as

slope =

$$\frac{H_3(s) - H_1(s - q)}{s - (s - q)}$$

$$= \frac{H_3(s) - H_1(s - q)}{q} \qquad (2.51)$$

and slope for the constant

$$constant = H_3(s) - (slope) s$$

Expanding these terms we see that

$$H_{2}(\Delta) = \begin{bmatrix} s(Q/q[Q/q]) & 2 \sigma Q (s - q) \\ q'(s + q - \frac{q}{2\sigma[Q/q]} (s^{2}/q^{2} + s/q)) & q's(2(q[Q/q] - s) + s - q) \end{bmatrix} \Delta$$

$$+ \left[ \frac{((q-s)s)(Q/q[Q/q])}{q'(s+q-\frac{q}{2\sigma[Q/q]}(s^2/q^2+s/q))} - \frac{2\sigma Q(s-q)}{q'(2(q[Q/q]-s)+s-q)} \right]$$

(2. 52)

We can now write  $E[g(\Delta)]$  using the approximating functions.

$$E[g(\Delta)] = 1 \qquad (2.53)$$

$$for 0 \leq s \leq q$$

$$= \int_{0}^{s-q} H_{1}(\Delta) f_{\Delta}(\Delta) d\Delta + \int_{s-q}^{s} H_{2}(\Delta) f_{\Delta}(\Delta) d\Delta$$

$$+ \int_{s}^{q[Q/q]} H_{3}(\Delta) f_{\Delta}(\Delta) d\Delta \qquad (2.54)$$

(2.54)

This integral is evaluated in Appendix A and the results follow: