# THE UNIVERSITY OF MICHIGAN ANN ARBOR, MICHIGAN

THREE-TERMINAL PUNCH-THROUGH DEVICES

bу

H. Yilmaz

Technical Report No. 168

Electron Physics Laboratory

Department of Electrical and Computer Engineering

#### **ABSTRACT**

The objective of this investigation is to study the gate field controlled <u>barrier injection transit-time</u> (GFC-BARITT) device and <u>static injection transistor</u> (SIT) theoretically and experimentally. The GFC-BARITT device is proposed and its potential is explored.

The physics of three-terminal punch-through (TTPT) devices, SIT, metal semiconductor metal (MSM) and n+pn+ GFC-BARITT devices are studied in detail. The particle current injection process for various TTPT devices is examined and identified as diffusion over a gate controlled potential barrier. Dc, small-signal and large-signal ac models for the TTPT devices have been derived by using (1) drift and (2) drift-diffusion approximations. The transit-time effect is included in the small- and large-signal models. Also the small-signal noise properties of the TTPT devices are considered. The potential distribution in the device is calculated by using a two-dimensional Poisson equation solver. The level of carrier injection in GaAs GFC-BARITT devices is lower than that in silicon of InP devices. However, the level of carrier injection in SIT devices is independent of the material. To obtain high current from TTPT devices, high carrier saturation velocity and high carrier injection are required. The forward bias voltage  $V_F$  and the gate-source distance are the most critical parameters for the operation of these devices.

A noniterative large-signal model is proposed. This model was applied to the various FET devices. The results indicate that InP FETs can generate more power than either the GaAs or Si FETs. FETs are treated as a special mode of operation of the SIT device, because either an increase in the channel doping concentration or the channel width of a SIT device results in an FET mode of operation.

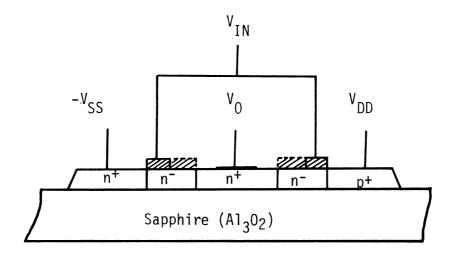

MSM and  $n^{\dagger}pn^{\dagger}$  GFC-BARITT devices and ring oscillators were fabricated utilizing silicon on sapphire (SOS). The principles of operation of GFC-BARITT devices and their superiority over MOSFETs for digital logic circuits are discussed.

# TABLE OF CONTENTS

|         |     |       |                  |                       |                                                                         | <u>Page</u> |

|---------|-----|-------|------------------|-----------------------|-------------------------------------------------------------------------|-------------|

| CHAPTER | I.  | INTRO | DUCTION          | l                     |                                                                         | 1           |

|         |     |       | Introdu          |                       | peration of Three-                                                      | 1           |

|         |     | 1.6   |                  |                       | Through Devices                                                         | 2           |

|         |     |       | 1.2.1            | GFC-BARI              | TT Devices                                                              | 2           |

|         |     |       |                  | (                     | MSM GFC-BARITT Device:<br>Current Transport<br>Mechanism                | 4           |

|         |     |       | 1.2.2            | Static I<br>(SITs)    | nduction Transistors                                                    | 11          |

|         |     | 1.3   | Outline          | e of the              | Present Study                                                           | 14          |

| CHAPTER | II. |       |                  | SICS AND<br>AND SIT   | DC CHARACTERISTICS OF<br>DEVICES                                        | 16          |

|         |     |       |                  | Physics<br>C-BARITT   | Device                                                                  | 16<br>16    |

|         |     |       | 2.2.1            | Diffusio<br>Field Re  | n Effect in the Low                                                     | 19          |

|         |     |       | 2.2.2            | Dc Curre              | nt Density of a<br>TT Device                                            | 28          |

|         |     |       |                  |                       | Drift-Diffusion Current<br>Approximation<br>Drift Current Approximation | 28<br>33    |

|         |     |       | 2.2.3            | Potentia              | 1 Distribution                                                          | 36          |

|         |     | 2.3   | Static           | -Inductio             | n Transistor                                                            | 43          |

|         |     |       |                  |                       | of the SIT Device<br>cteristics of the SIT Device                       | 46<br>47    |

|         |     | 2.4   |                  | racterist<br>Transist | cics of a Vertical Field-<br>cor                                        | 52          |

|         |     | 2.5   | Thermi<br>Curren |                       | ration of the Diffusion                                                 | 57          |

|                   |                    |          |                          |                                                | Page     |

|-------------------|--------------------|----------|--------------------------|------------------------------------------------|----------|

| CHAPTER III. SMAL | L- AND             | LARGE-S  | IGNAL MODE               | L                                              | 59       |

|                   | introdu<br>Small-S |          | rcuit Elemo              | ents                                           | 59<br>60 |

| 3                 | 3.2.1              | Transcon | ductance                 |                                                | 60       |

|                   |                    | 3.2.1.1  | Silicon D                | evices                                         | 62       |

|                   |                    |          |                          | GFC-BARITT and<br>SIT Devices                  | 62       |

|                   |                    |          | 3.2.1.1b                 | Vertical FETs                                  | 62       |

|                   |                    | 3.2.1.2  | III-V Com<br>Semicondu   | pound<br>ctor Devices                          | 63       |

|                   |                    |          | 3.2.1.2a                 | GFC-BARITT and<br>SIT Devices                  | 63       |

|                   |                    |          | 3.2.1.2b                 | Vertical FETs                                  | 64       |

| 3                 | 3.2.2              | Conducta | nce                      |                                                | 64       |

|                   |                    | 3.2.2.1  | Silicon D                | evices                                         | 65       |

|                   |                    |          |                          | GFC-BARITT and<br>SIT Devices<br>Vertical FETs | 65<br>65 |

|                   |                    | 3.2.2.2  | III-V Com<br>Semicondu   |                                                | 65       |

|                   |                    |          | 3.2.2.2a                 |                                                |          |

|                   |                    |          | 3.2.2.2b                 | and SITs<br>Vertical FETs                      | 65<br>66 |

| 3                 | 3.2.3              | Gate-Sou | ırce Capaci              | tance                                          | 66       |

|                   |                    |          | GFC-BARITT<br>Vertical F | and SIT Devices<br>ETs                         | 66<br>68 |

| ;                 | 3.2.4              | Drain-Ga | te Feedbac               | k Capacitance                                  | 68       |

|                   |                    |          | GFC-BARITT<br>Vertical F | and SIT Devices<br>ETs                         | 68<br>69 |

|                   | 3.2.5              | Drain-Sc | ource Capac              | itance                                         | 69       |

|                   |                    |          | GFC-BARITT               | and SIT Devices                                | 69<br>70 |

|     |                         |                                                                                                                                   | Page                       |

|-----|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 3.3 | Diffus<br>Parame        | ion Effects on Small-Signal Circuit<br>ters                                                                                       | 71                         |

|     | 3.3.2<br>3.3.3<br>3.3.4 | The Transconductance The Conductance The Gate-Source Capacitance The Drain-Gate Feedback Capacitance The Drain-Source Capacitance | 71<br>72<br>72<br>73<br>73 |

| 3.4 | Carrie                  | r Transit Time Effect                                                                                                             | 74                         |

|     |                         | Silicon Devices                                                                                                                   | 75                         |

|     | 3.4.2                   | III-V Compound Semiconductor<br>Devices                                                                                           | 76                         |

| 3.5 | Large-                  | Signal Analysis                                                                                                                   | 77                         |

|     |                         | Introduction<br>Large-Signal Circuit Parameters                                                                                   | 77<br>78                   |

|     |                         | 3.5.2.1 GFC-BARITT and SIT Devices 3.5.2.2 Vertical FETs                                                                          | 79<br>82                   |

|     |                         | 3.5.2.2a Silicon FETs 3.5.2.2b III-V Compound Semiconductor FETs                                                                  | 82<br>86                   |

| 3.6 | Small-                  | Signal Circuit Properties                                                                                                         | 88                         |

|     | 3.6.2<br>3.6.3          | Admittance Parameters<br>S-Parameters<br>Gain and Gain Bandwidth Product<br>The Stability Analysis                                | 88<br>91<br>93<br>95       |

| 3.7 | Large-<br>Device        | -Signal Power and Gain of the TTPT                                                                                                | 95                         |

| 3.8 | Noise                   | Analysis                                                                                                                          | 97                         |

|     | 3.8.1                   | Introduction                                                                                                                      | 97                         |

|     | 3.8.2                   | Noise in Punch-Through Diodes                                                                                                     | 99                         |

|     |                         | Noise Sources of the Three-<br>Terminal Punch-Through Devices<br>The Noise Figure and the Noise                                   | 100                        |

|     |                         | Measure The Noise Temperatures                                                                                                    | 103<br>106                 |

|     | 4 24 6                  | ING NOISG IGMDAYATUYAS                                                                                                            | 1111                       |

|             |            |                  |                                                                                                                | Page                     |

|-------------|------------|------------------|----------------------------------------------------------------------------------------------------------------|--------------------------|

| CHAPTER IV. | DEV        | ICE SIM          | JLATION PROGRAM (SIM-GFC)                                                                                      | 109                      |

|             | 4.2<br>4.3 | Materi           | uction<br>m Description<br>al Parameters<br>Physics                                                            | 109<br>110<br>111<br>118 |

|             |            | 4.4.2            | The Potential Distribution<br>The Injected Carrier Distribution<br>The Space-Charge Effect                     | 118<br>127<br>133        |

|             | 4.5        | Dc Cha           | racteristics                                                                                                   | 135                      |

|             |            | 4.5.2<br>4.5.3   | The Impurity Concentration Effect Temperature Effect The Geometry Effect Dc and Small-Signal Device Parameters | 135<br>139<br>144<br>151 |

|             | 4.6        | Small-           | Signal Performance                                                                                             | 166                      |

|             |            |                  | GFC-BARITT Devices<br>SIT Devices                                                                              | 167<br>177               |

|             | 4.7        | Large-           | Signal Performance                                                                                             | 197                      |

|             |            | 4.7.1            | Results and Discussions of the Large-Signal Operation                                                          | 204                      |

|             | 4.8        | Compar           | ison of the Different Devices                                                                                  | 218                      |

| CHAPTER V.  | DEVI       | CE FABR          | ICATION AND MEASUREMENTS                                                                                       | 221                      |

|             | 5.1<br>5.2 | Introd<br>Materi | uction<br>al Selection                                                                                         | 221<br>222               |

|             |            | 5.2.1            | SOS Samples                                                                                                    | 225                      |

|             | 5.4        | Dc Cha<br>Introd | Fabrication<br>racteristics<br>luction to Digital Circuit                                                      | 228<br>233               |

|             |            |                  | ations                                                                                                         | 240                      |

|             |            |                  | Basic Structure and Principles of Operation                                                                    | 242                      |

|             |            | 5.5.3            | Ring Oscillator Fabrication<br>Results and Discussion<br>Delay Time                                            | 245<br>246<br>256        |

|             |            |                  | 5.5.4.1 A GFC-BARITT Device<br>Inverter<br>5.5.4.2 Injection Control Logic                                     | 256<br>259               |

|              |                                                            | Page |

|--------------|------------------------------------------------------------|------|

|              | 5.5.5 Conclusion                                           | 260  |

| !            | 5.6 Comparison of the Theoretical and Experimental Results | 265  |

| CHAPTER VI.  | CONCLUSIONS AND SUGGESTIONS FOR FURTHER STUDY              | 268  |

| APPENDIX A.  | FACR METHOD                                                | 271  |

| APPENDIX B.  | SIM-GFC PROGRAM                                            | 277  |

| LIST OF REFE | RENCES                                                     | 279  |

# LIST OF FIGURES

| Figure |                                                                                                                                            | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------|------|

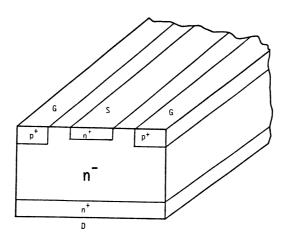

| 1.1    | Structure of an Ideal GFC-BARITT Device.                                                                                                   | 3    |

| 1.2    | MSM GFC-BARITT Device.                                                                                                                     | 5    |

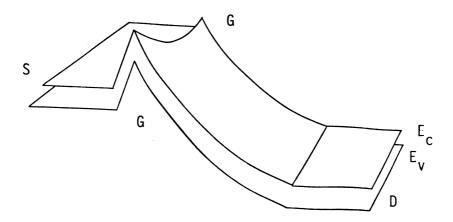

| 1.3    | MSM GFC-BARITT Device Energy Bands.                                                                                                        | 7    |

| 1.4    | Energy Band Diagram at $ V_{DS}  \ge  V_{FB} $ .                                                                                           | 9    |

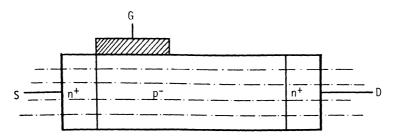

| 2.1    | GFC-BARITT Device.                                                                                                                         | 18   |

| 2.2    | Field, Velocity and Carrier Distributions of a TTPT Device.                                                                                | 27   |

| 2.3    | A TTPT Device.                                                                                                                             | 29   |

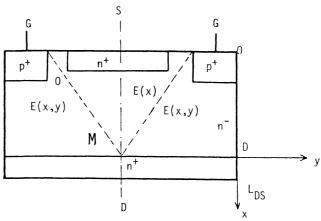

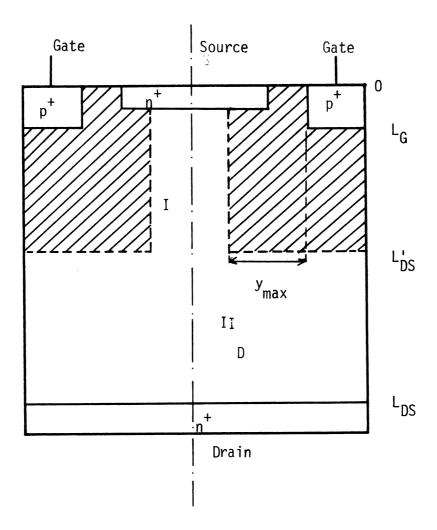

| 2.4    | SIT Device. ( $G = Gate, D = Drain and S = Source$ ).                                                                                      | 47   |

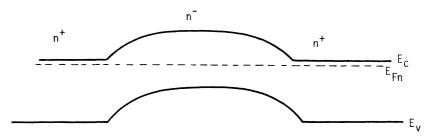

| 2.5    | A SIT Device.                                                                                                                              | 50   |

| 2.6    | Vertical FET Structure.                                                                                                                    | 53   |

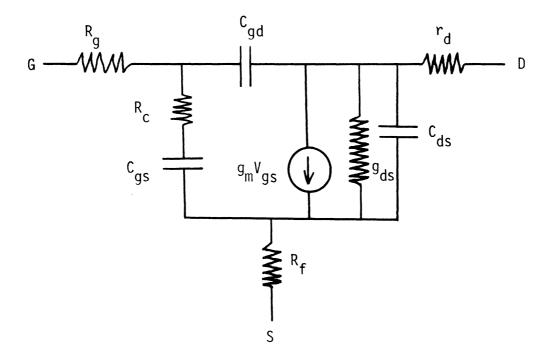

| 3.1    | Small-Signal Equivalent Circuit of a SIT or a GFC-BARITT Device.                                                                           | 61   |

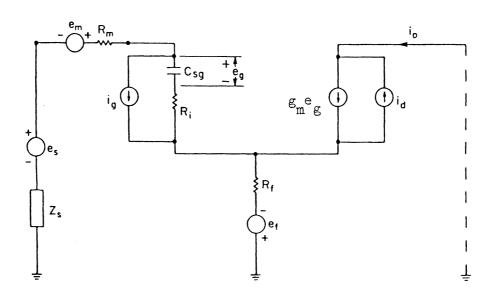

| 3.2    | Equivalent Circuit Used in Noise Analysis.                                                                                                 | 104  |

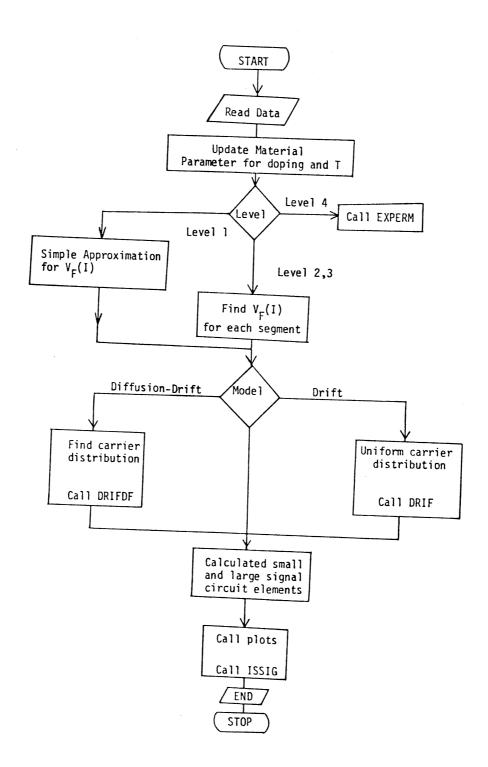

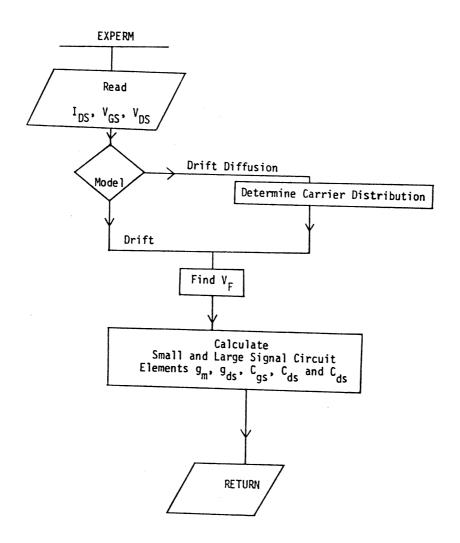

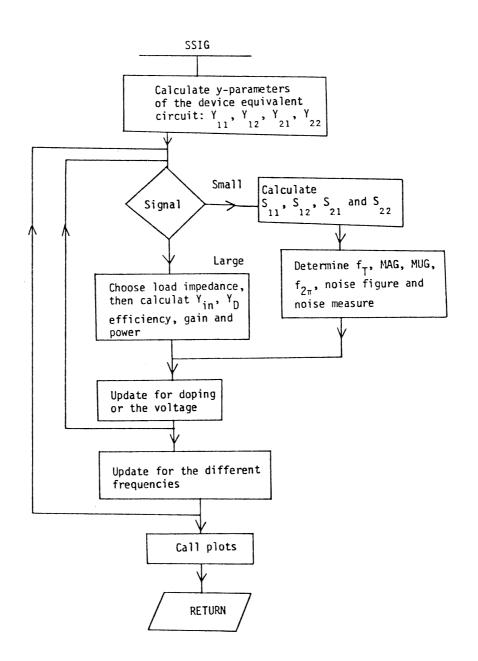

| 4.1    | Flow Chart.                                                                                                                                | 112  |

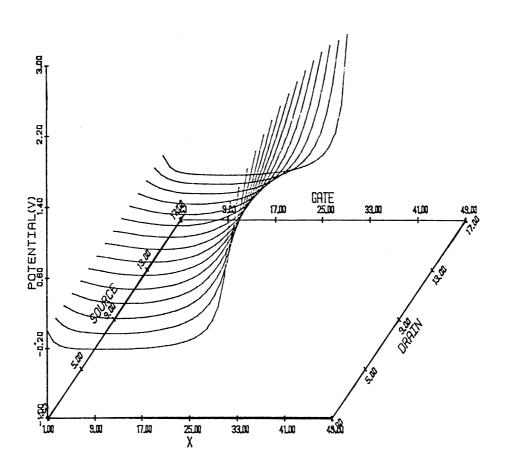

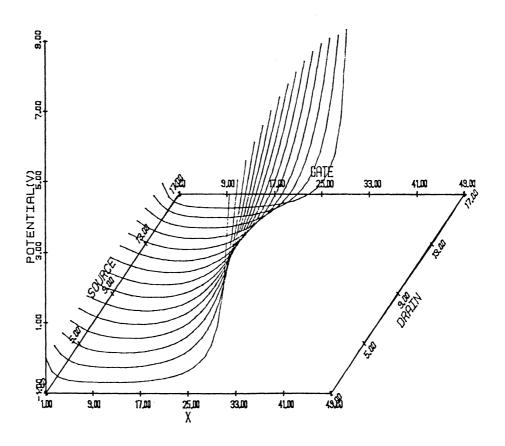

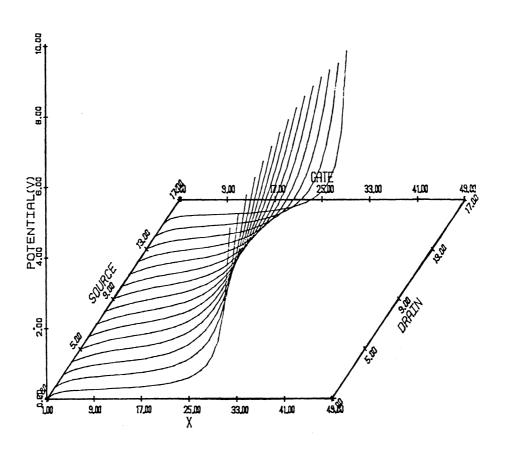

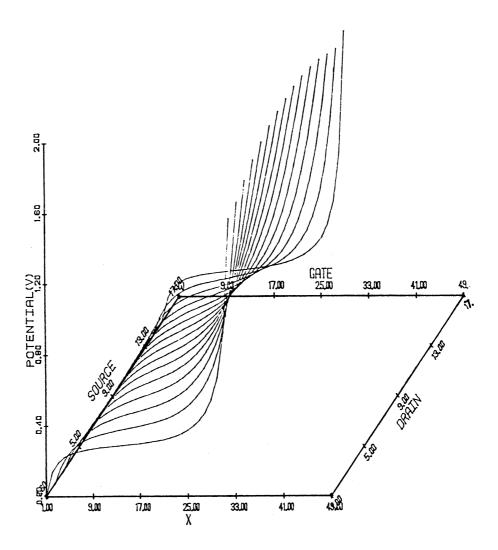

| 4.2    | The Potential Distribution.                                                                                                                | 121  |

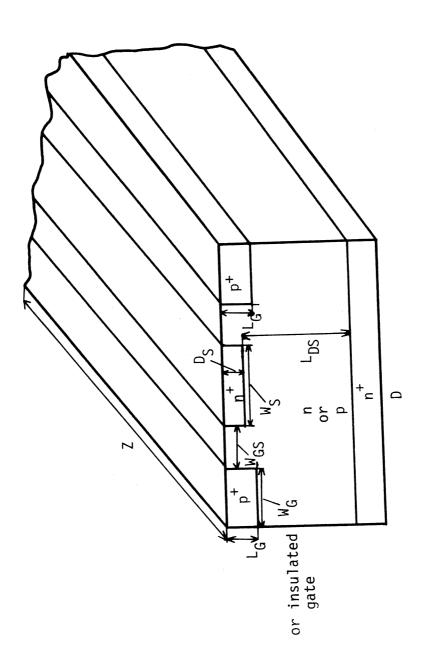

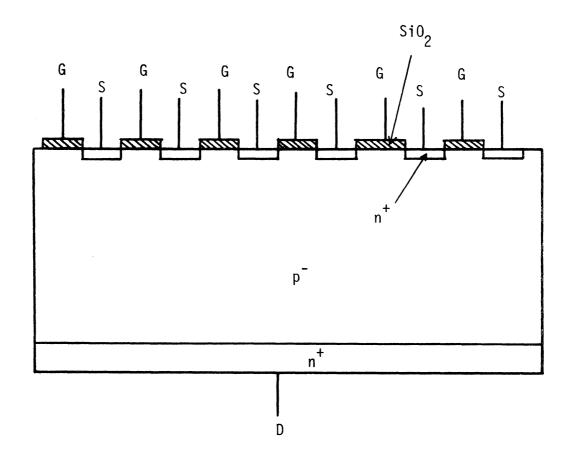

| 4.3    | A Multi-Channel Surface Gate (Insulator or Schottky) TTPT Device.                                                                          | 126  |

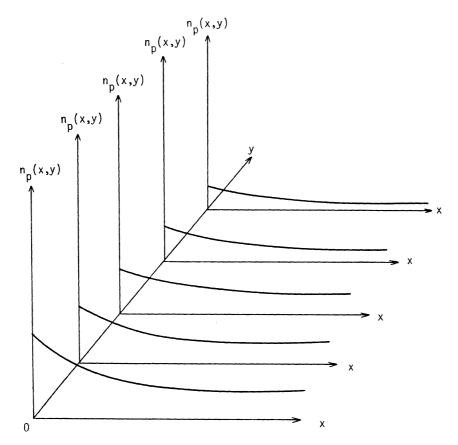

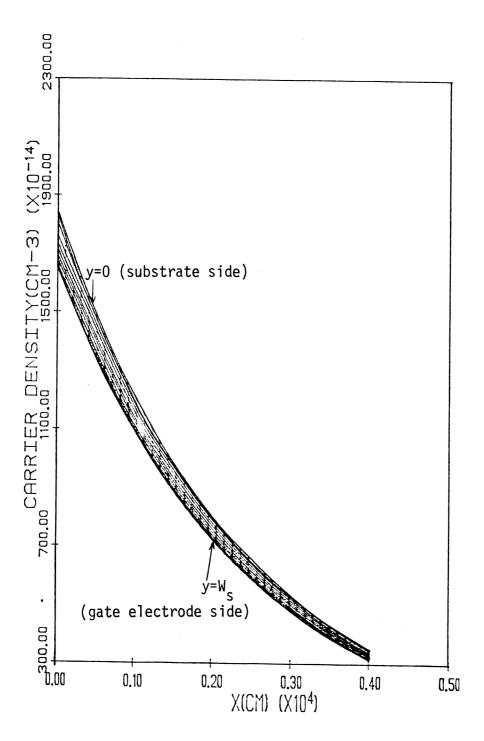

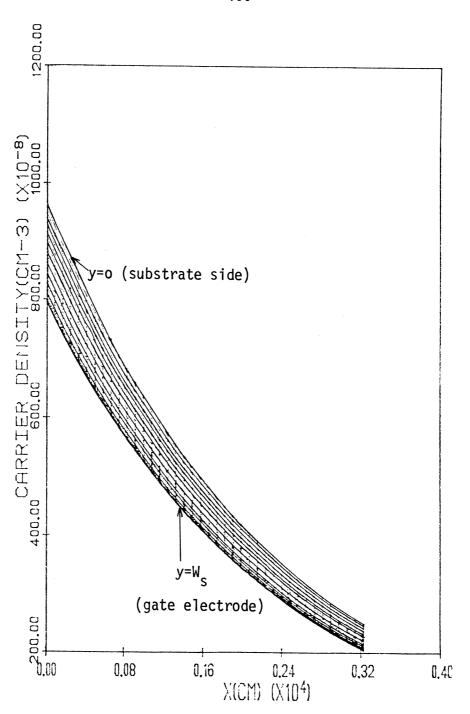

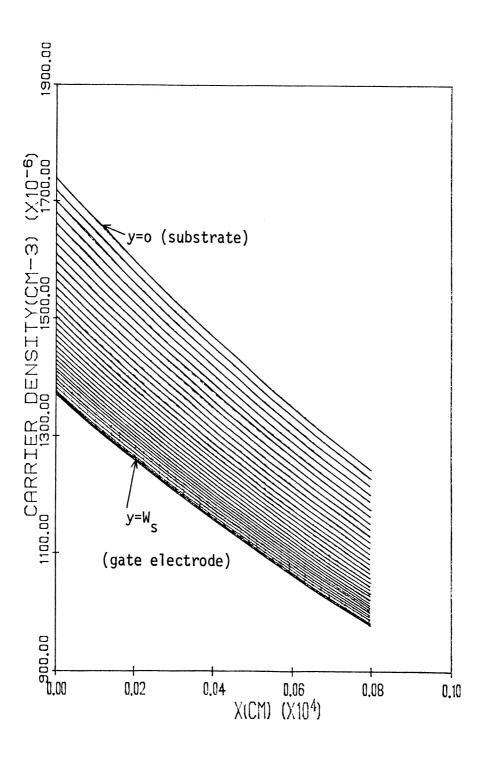

| 4.4    | Carrier Distribution as a Function of Distance at the Different Points Across the Channel, y and Distance Along the Conduction Path, $x$ . | 129  |

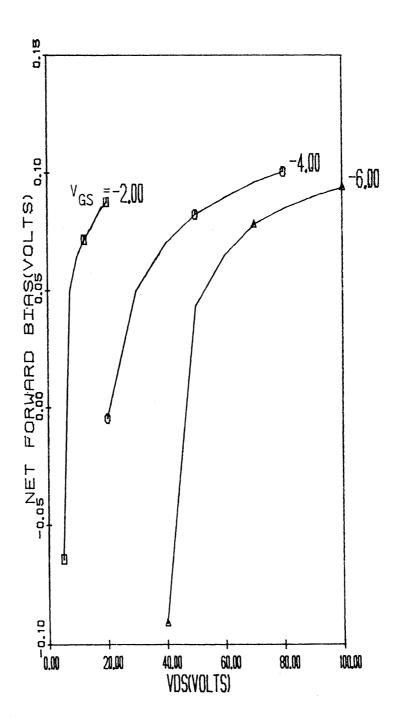

| 4.5    | ${ m V_F}$ Vrriation as a Function of ${ m V_{DS}}$ at Different Gate Voltages (Device S2).                                                | 134  |

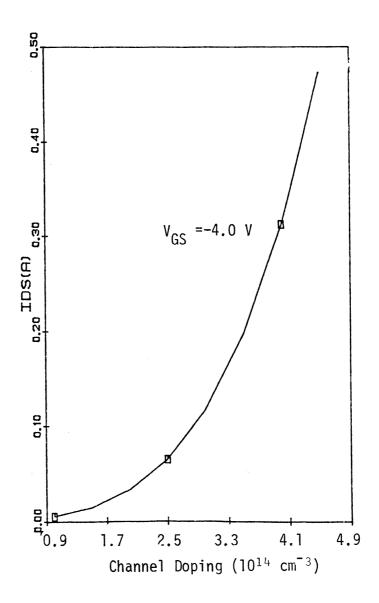

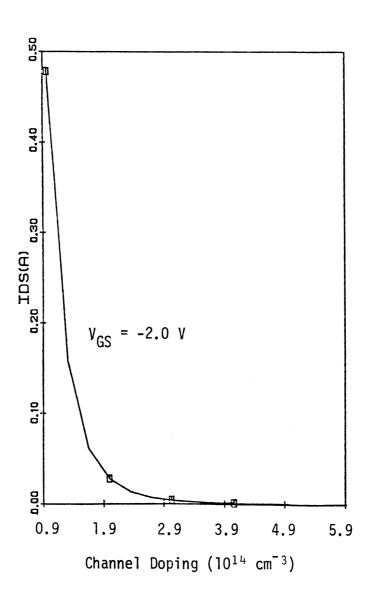

| 4.6    | Dc Current of a SIT as a Function of the Channel Doping Concentration (Device S2).                                                         | 136  |

| <u>Figure</u> |                                                                                                                                                 | Page |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|

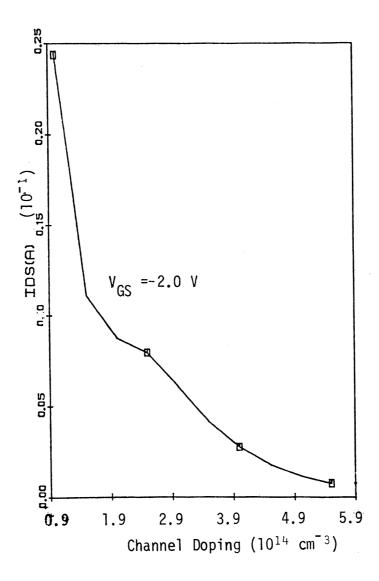

| 4.7           | Dc Current of a GFC-BARITT Device as a Function of the Channel Doping Concentration (Device B1).                                                | 137  |

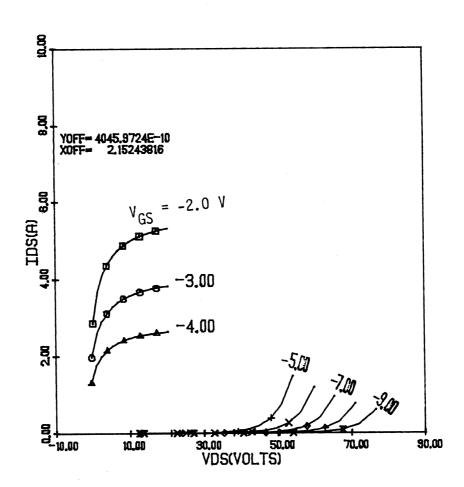

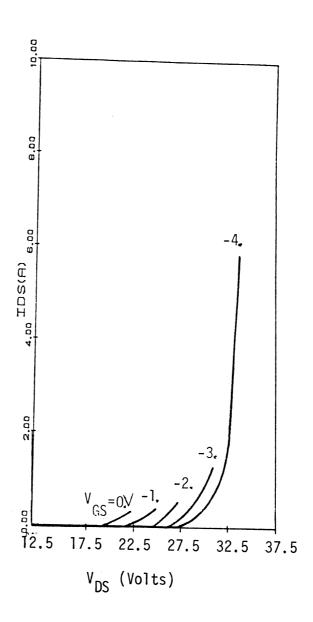

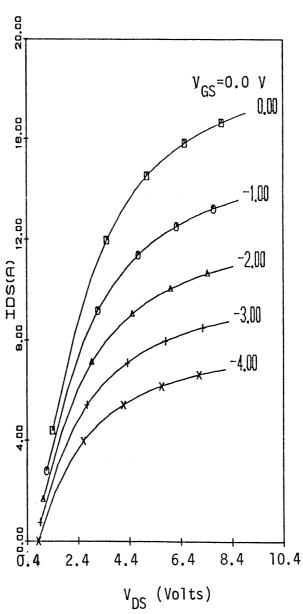

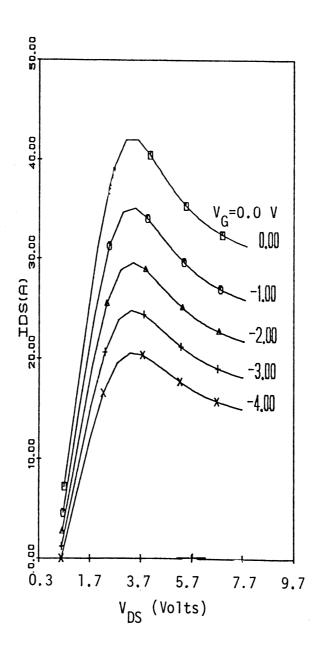

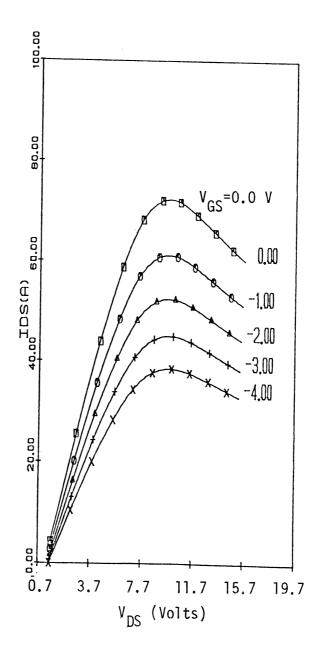

| 4.8           | The Current Voltage Characteristics of a SIT Operating in FET and Injection (SIT) Modes (Device S1).                                            | 141  |

| 4.9           | A GFC-BARITT Device Current as a Function of the Channel Doping at $T = 400^{\circ}K$ (Device B1, Compared to Fig. 4.7 at $T = 300^{\circ}K$ ). | 143  |

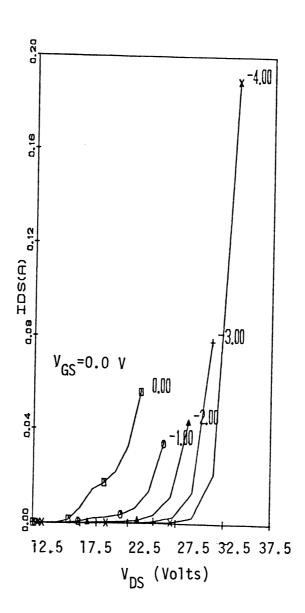

| 4.10a         | The Gate-Source Spacing, $W_{\mbox{GS}}$ , Effect on the I-V Characteristics of a GFC-BARITT Device.                                            | 146  |

| 4.10b         | The Gate-Source Spacing, $W_{\mbox{GS}}$ , Effect on the I-V Characteristics of a GFC-BARITT Device.                                            | 147  |

| 4.11a         | The I-V Characteristics of the Vertical FETs.                                                                                                   | 148  |

| 4.11b         | The I-V Characteristics of the Vertical FETs.                                                                                                   | 149  |

| 4.11c         | The I-V Characteristics of the Vertical FETs.                                                                                                   | 150  |

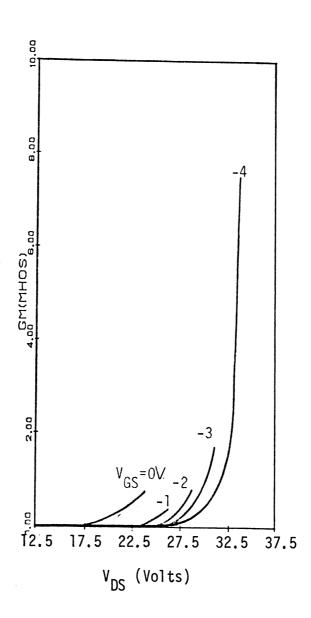

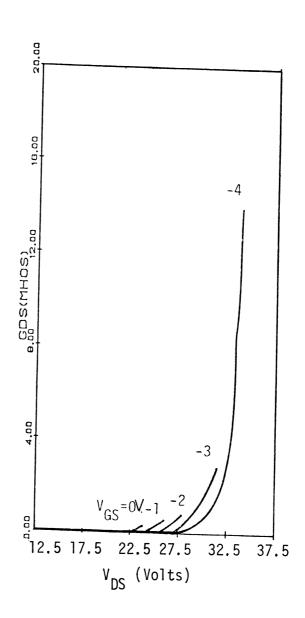

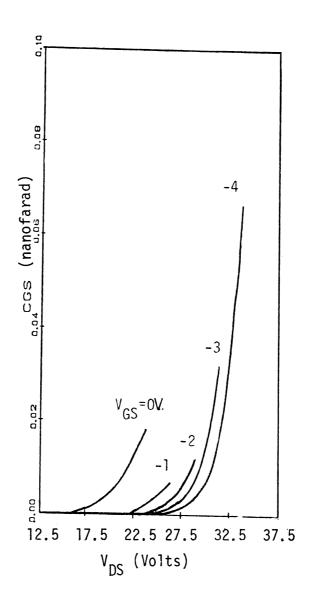

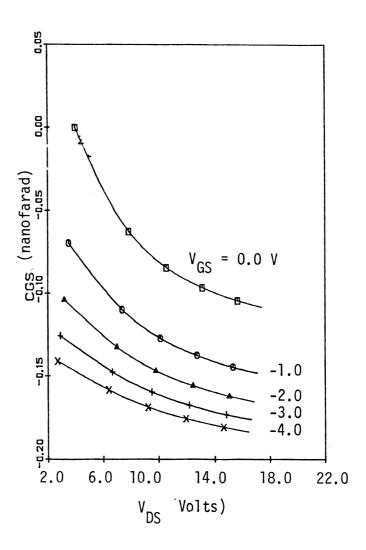

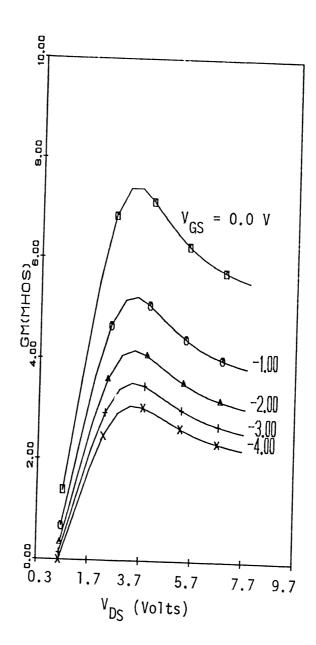

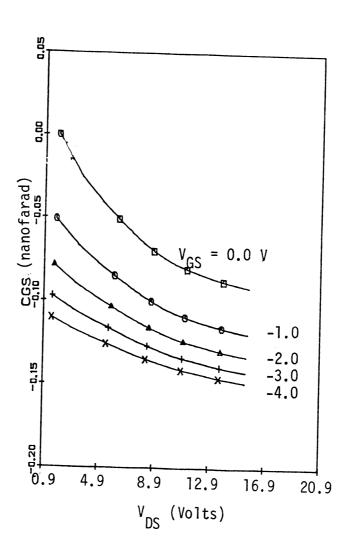

| 4.12a         | Small-Signal Parameters of a GFC-BARITT Device as a Function of $V_{DS}$ for Different Values of $V_{GS}$ (Device B2).                          | 153  |

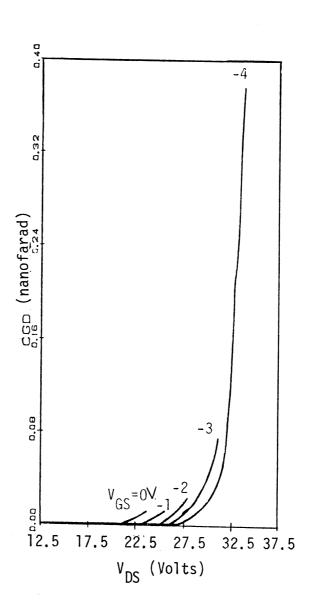

| 4.12b         | Small-Signal Parameters of a GFC-BARITT Device as a Function of the $\rm V_{DS}$ with Different $\rm V_{GS}$ Voltages (Device B2).              | 154  |

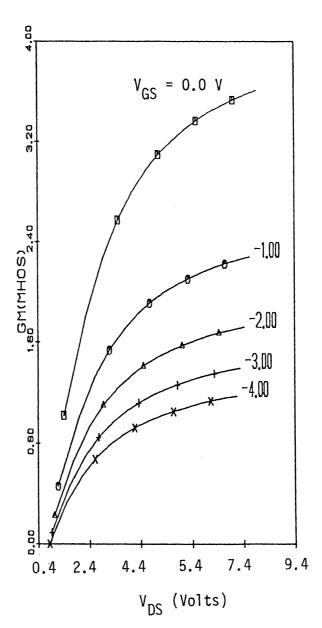

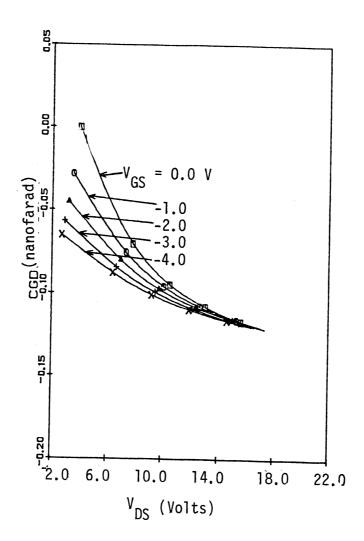

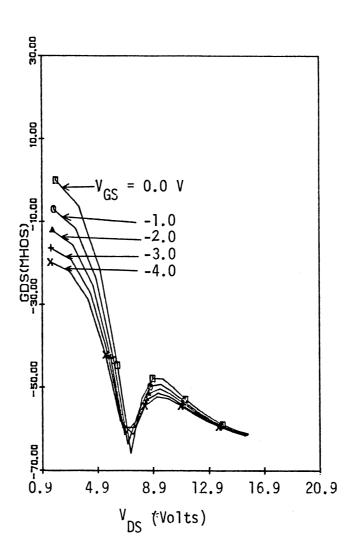

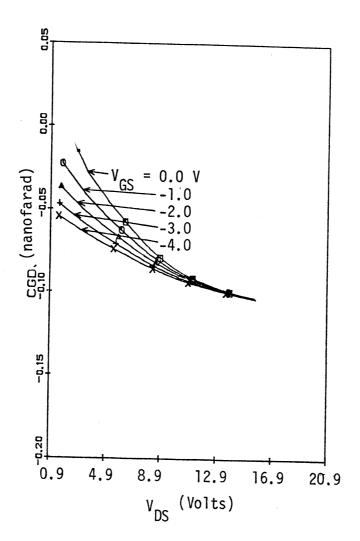

| 4.12c         | The Small-Signal Parameters of a GFC-BARITT Device as a Function of the $V_{DS}$ with Different $V_{GS}$ Voltages (Device B2).                  | 155  |

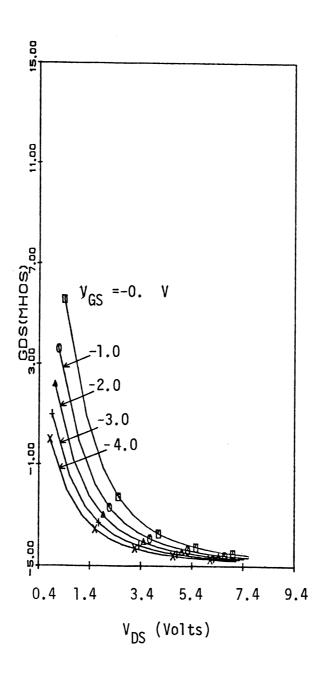

| 4.12d         | Small-Signal Parameters of a GFC-BARITT Device as a Function of the $V_{DS}$ with Different $V_{GS}$ Voltages (Device B2).                      | 156  |

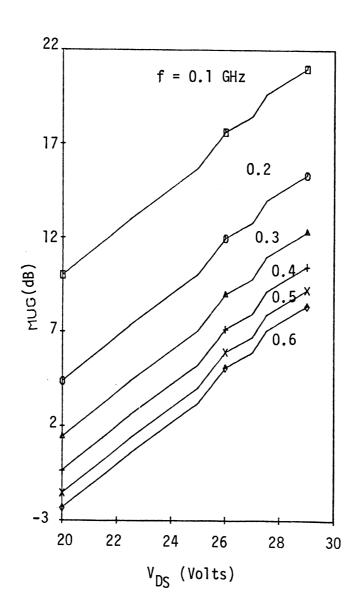

| 4.13a         | The Small-Signal Equivalent Circuit Parameters of a Silicon FET, S3.                                                                            | 158  |

| 4.13b         | The Small-Signal Equivalent Circuit Parameters of a Silicon FET. S3.                                                                            | 159  |

| <u>Figure</u> |                                                                                                                                           | <u>Page</u> |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 4.13c         | The Small-Signal Equivalent Circuit Parameters of a Silicon FET, S3.                                                                      | 160         |

| 4.13d         | The Small-Signal Equivalent Circuit Parameters of a Silicon FET, S3.                                                                      | 161         |

| 4.14a         | The Small-Signal Equivalent Circuit Parameters of a GaAs FET, S4.                                                                         | 162         |

| 4.14b         | The Small-Signal Equivalent Circuit Parameters of a GaAs FET, S4.                                                                         | 163         |

| 4.14c         | The Small-Signal Equivalent Circuit Parameters of a GaAs FET, S4.                                                                         | 164         |

| 4.14d         | The Small-Signal Equivalent Circuit Parameters of A GaAs FET, S4.                                                                         | 165         |

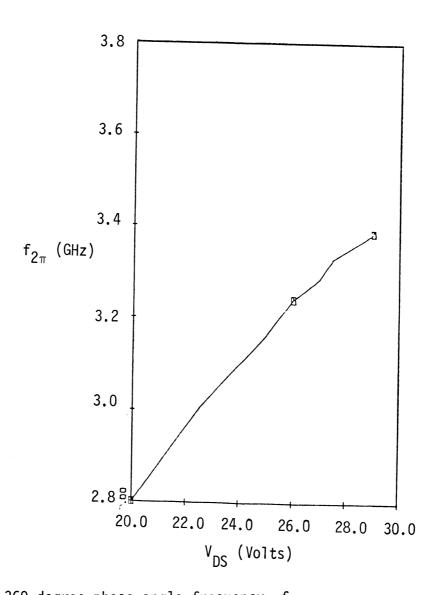

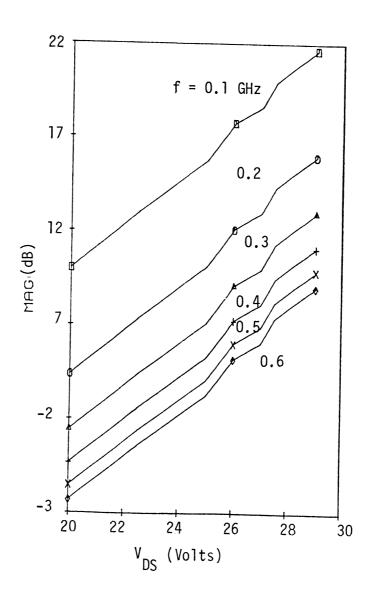

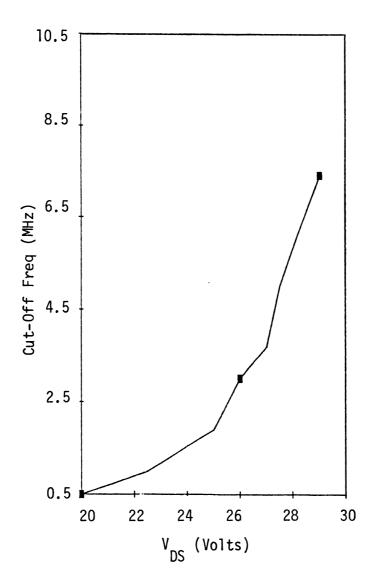

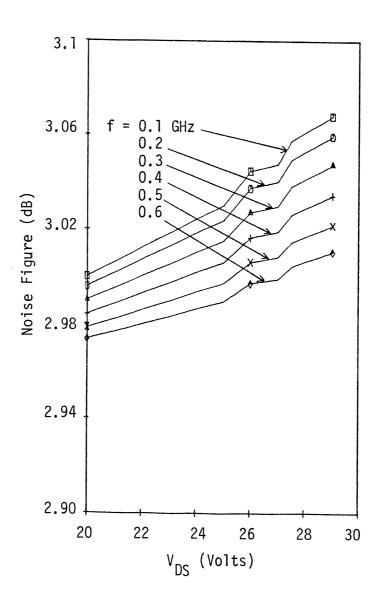

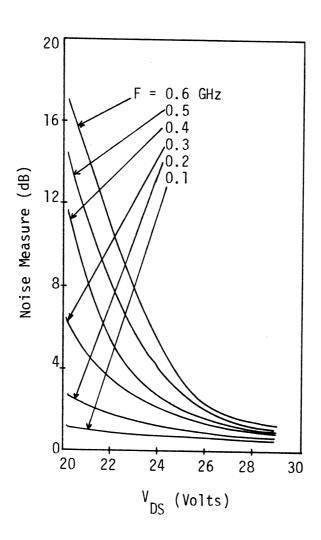

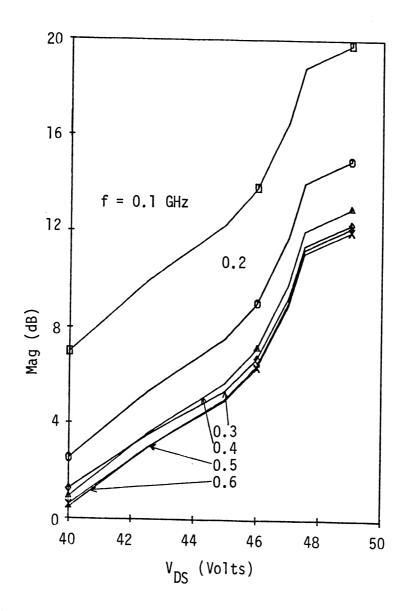

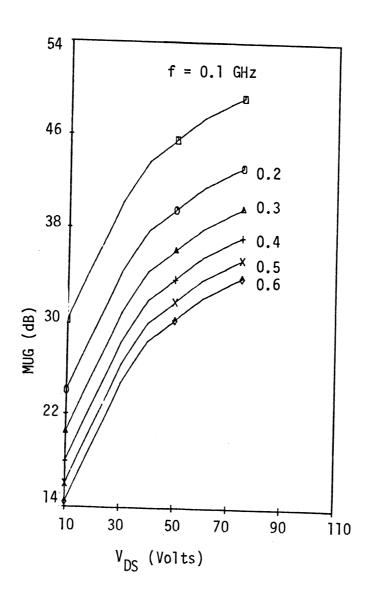

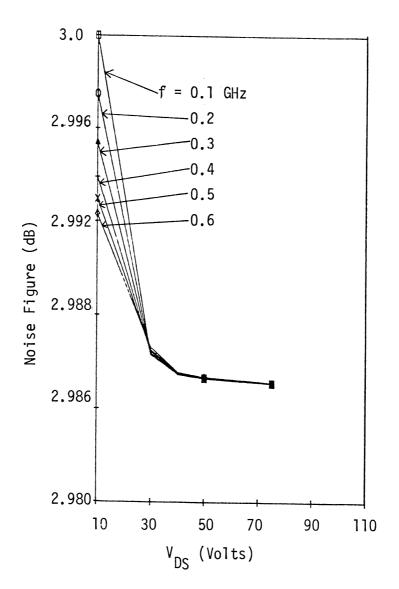

| 4.15a         | The Small-Signal Performance of a Si GFC-BARITT Device, B4, as a Function of the V <sub>DS</sub> at Different Frequencies 0.1 to 0.6 GHz. |             |

|               | $(V_{GS} = 0 V)$                                                                                                                          | 168         |

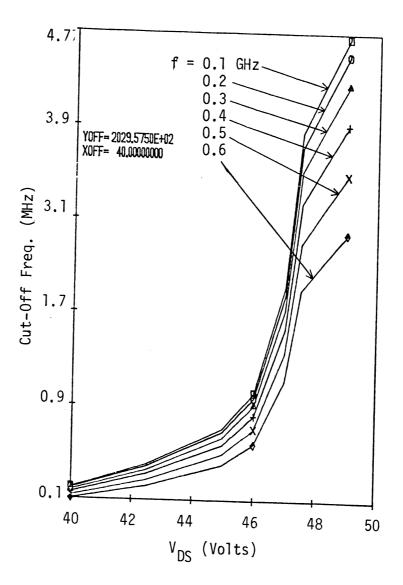

| 4.15b         | The Small-Signal Performance of a Si GFC-BARITT Device, B4, as a Function of the V <sub>DS</sub> at Different Frequencies 0.1 to 0.6 GHz. |             |

|               | $(V_{GS} = 0 V)$                                                                                                                          | 169         |

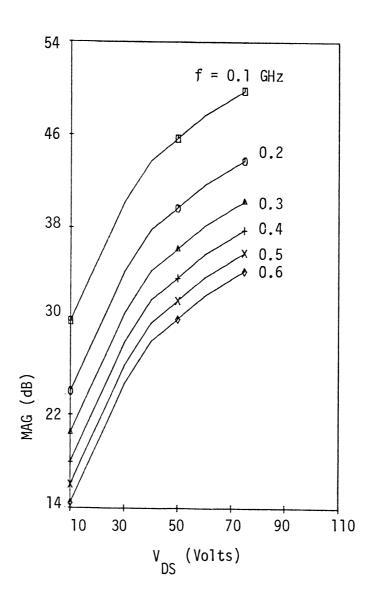

| 4.15c         | The Small-Signal Performance of a Si GFC-BARITT Device, B4, as a Function of the V <sub>DS</sub> at Different                             |             |

|               | Frequencies 0.1 to 0.6 GHz. $(V_{GS} = 0 \ V)$                                                                                            | 170         |

| 4.15d         | The Small-Signal Performance of a Si GFC-BARITT Device, B4, as a Function of the V <sub>DS</sub> at Different                             |             |

|               | Frequencies 0.1 to 0.6 GHz. (V <sub>GS</sub> = 0 V)                                                                                       | 171         |

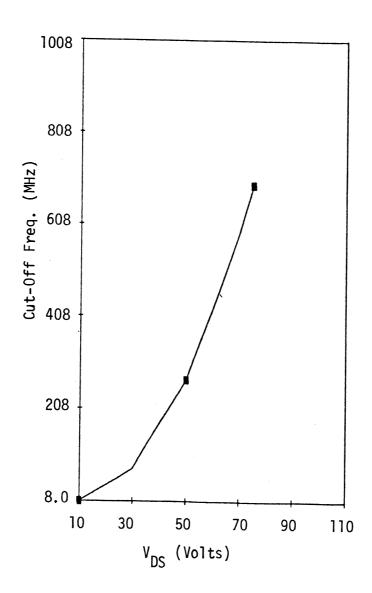

| 4.15e         | The Small-Signal Performance of a Si GFC-BARITT Device, B4, as a Function of the ${ m V}_{ m DS}$ at Different                            |             |

|               | Frequencies 0.1 to 0.6 GHz. (V <sub>CS</sub> = 0 V)                                                                                       | 172         |

|               | \ 'CC ~ */                                                                                                                                | 1/2         |

| Figure |                                                                                                               | Page |

|--------|---------------------------------------------------------------------------------------------------------------|------|

| 4.15f  | The Small-Signal Performance of a Si GFC-BARITT Device, B4, as a Function of the V <sub>DS</sub> at Different |      |

|        | Frequencies 0.1 to 0.6 GHz.                                                                                   |      |

|        | $(V_{GS} = 0 \ V)$                                                                                            | 173  |

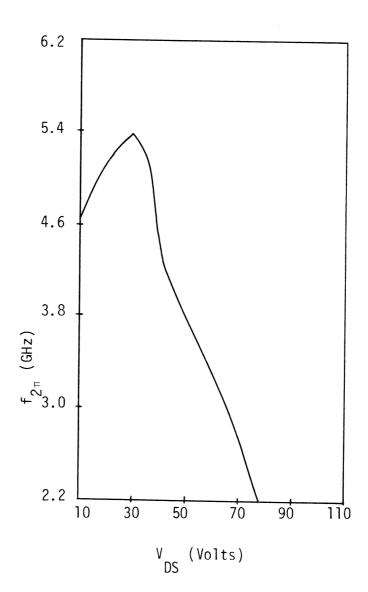

| 4.16a  | The Transit-Time Effect on the Small-Signal Device Performance of Device B4.                                  | 175  |

| 4.16b  | The Transit-Time Effect on the Small-Signal Device Performance of Device B4.                                  | 176  |

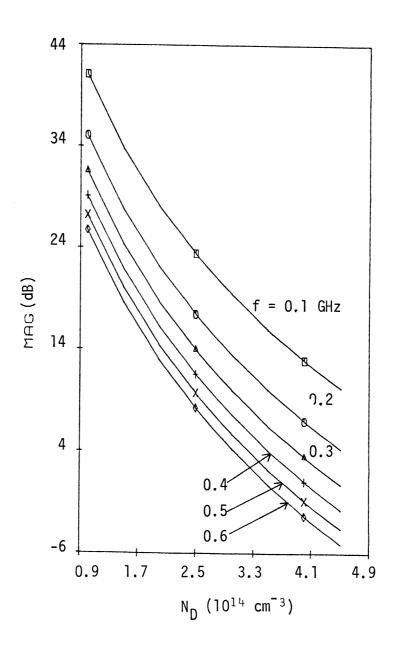

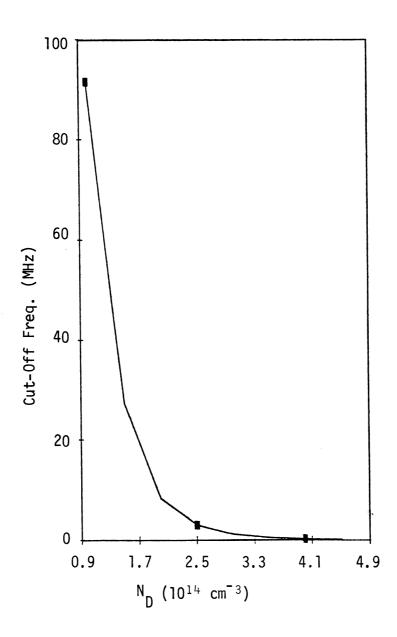

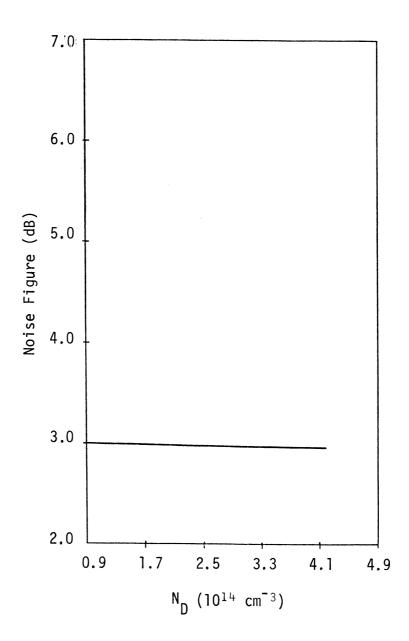

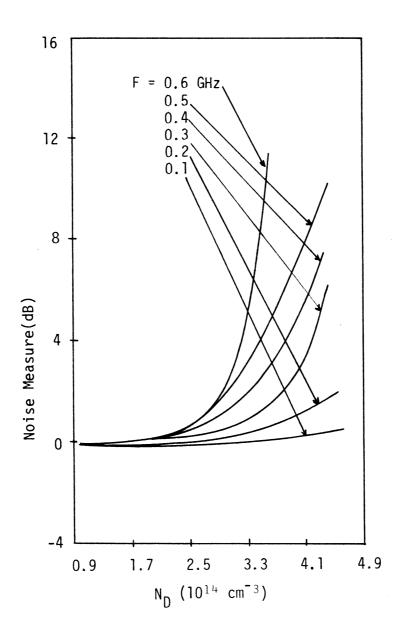

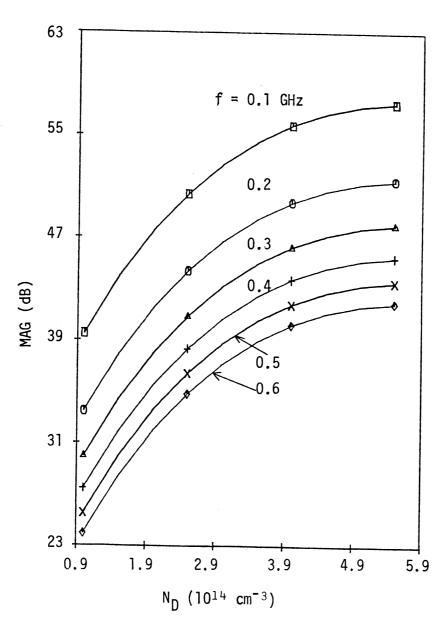

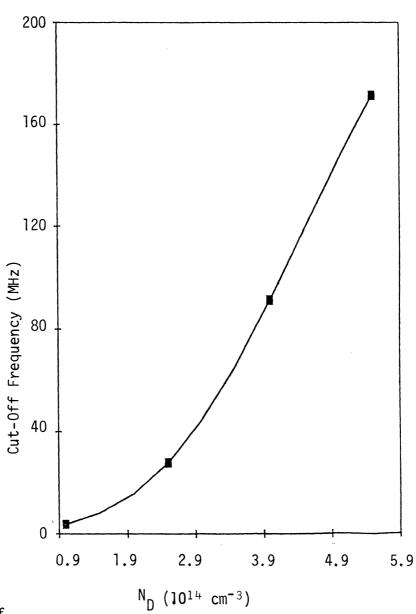

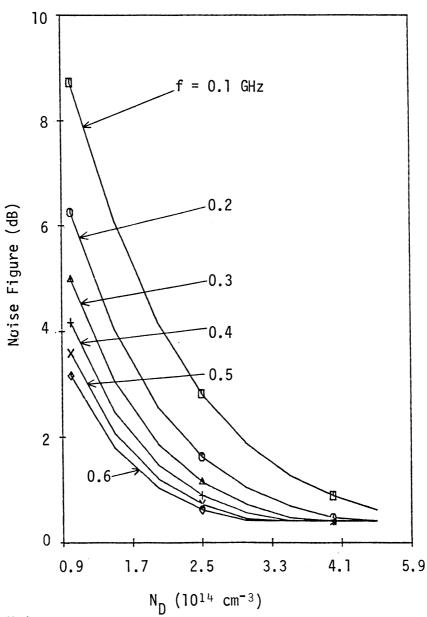

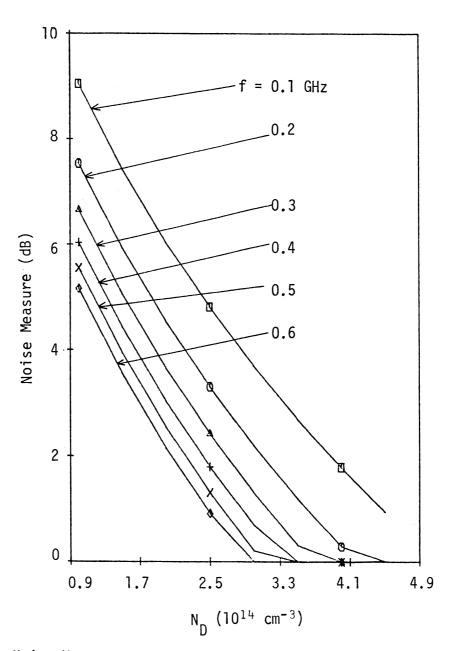

| 4.17a  | The Small-Signal Performance of a GFC-BARITT Device, Bl, as a Function of Channel Doping.                     | 178  |

| 4.17b  | The Small-Signal Performance of a GFC-BARITT Device, Bl, as a Function of Channel                             | 179  |

| 4.17c  | The Small-Signal Performance of a GFC-BARITT Device, Bl, as a Function of Channel                             | 180  |

| 4.17d  | The Small-Signal Performance of a GFC-BARITT Device, Bl, as a Function of                                     | 181  |

| 4.17e  | The Small-Signal Performance of a GFC-BARITT Device Bl, as a Function of the Channel Doping.                  | 182  |

| 4.17f  | The Small-Signal Performance of a GFC-BARITT Device, Bl, as a Function of the Channel Doping.                 | 183  |

| 4.18a  | The Small-Signal Performance of a GaAs SIT, S6 as a Function of the $V_{DS}$ . $(V_{GS} = 0 \ V)$             |      |

|        | D3                                                                                                            | 184  |

| 4.18b  | The Small-Signal Performance of a GaAs SIT, S6. $(V_{GS} = 0 \ V)$                                            | 185  |

| 4.18c  | The Small-Signal Performance of a GaAs SIT, S6. $(V_{GS} = 0 \ V)$ .                                          | 186  |

| 4.18d  | The Small-Signal Performance of a GaAs SIT, S6. (V <sub>GS</sub> = 0 V)                                       | 187  |

| 4.18e  | The Small-Signal Performance of a GaAs SIT, S6. $(V_{GS} = 0 \ V)$                                            |      |

|        |                                                                                                               | 188  |

| Figure |                                                                                                                                                                                       | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.18f  | The Small-Signal Performance of a GaAs SIT, S6. $(V_{GS} = 0 \ V)$                                                                                                                    | 189  |

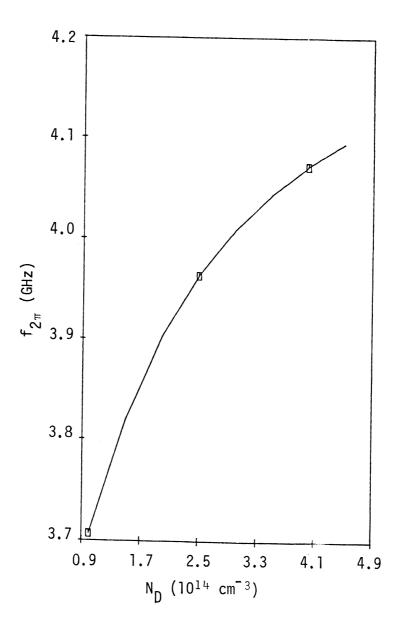

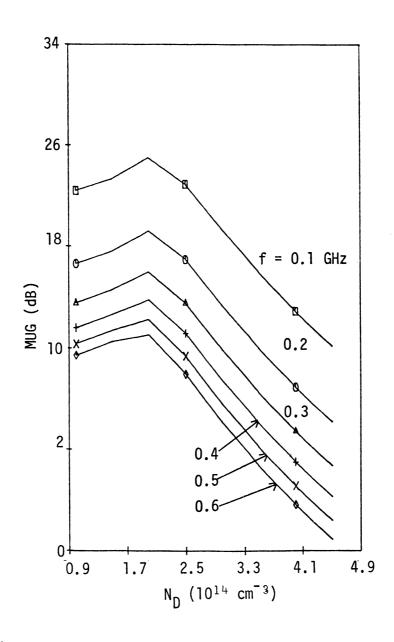

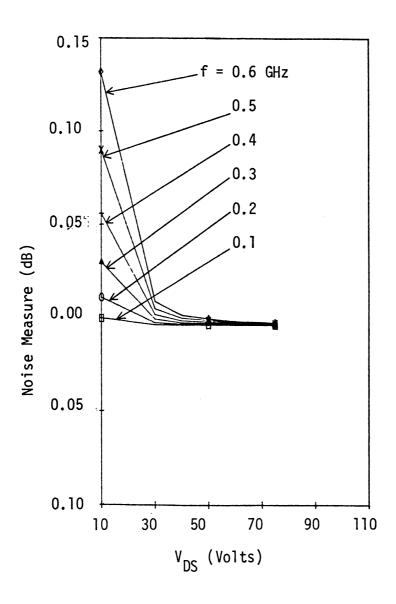

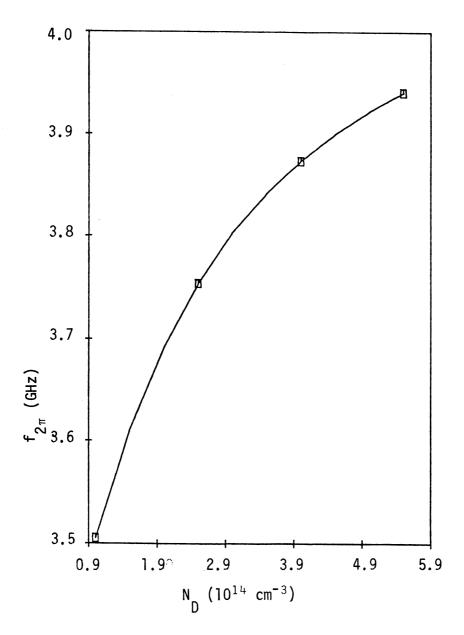

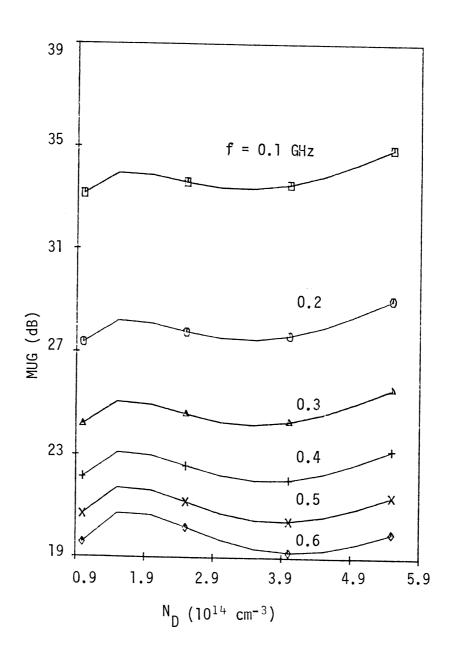

| 4.19a  | The Small-Signal Performance of a SI SIT, S2 as a Function of the Channel Doping, $N_D$ . ( $V_{DS} = V_{pt} + 8 \text{ V}$ and $V_{GS} = -3 \text{ V}$ )                             | 191  |

| 4.19b  | The Small-Signal Performance of a Si SIT, S2 as a Function of the Channel Doping, $N_{\hbox{\scriptsize D}}$ at Different Frequencies.                                                | 192  |

| 4.19c  | The Small-Signal Performance of a Si SIT, S2 as a Function of the Channel Doping, $N_D$ at Different Frequencies. ( $V_{DS} = V_{PT} + 8 \text{ V}$ and $V_{GS} = -3 \text{ V}$ )     | 193  |

| 4.19d  | The Small-Signal Performance of a Si SIT, S2 as a Function of the Channel Doping , $N_{DS}$ at Different Frequencies. ( $V_{DS} = V_{PT} + 8 \text{ V}$ and $V_{GS} = -3 \text{ V}$ ) | 194  |

| 4.19e  | The Small-Signal Performance of a Si SIT, S2 as a Function of the Channel Doping $N_D$ at Different Frequencies. ( $V_{DS} = V_{PT} + 8 \text{ V and } V_{GS} = -3 \text{ V}$ )       | 195  |

| 4.19f  | The Small-Signal Performance of a Si SIT, S2 as a Function of the Channel Doping at Different Frequencies. ( $V_{DS} = V_{PT} + 8 \text{ V}$ and $V_{GS} = -3 \text{ V}$ )            | 196  |

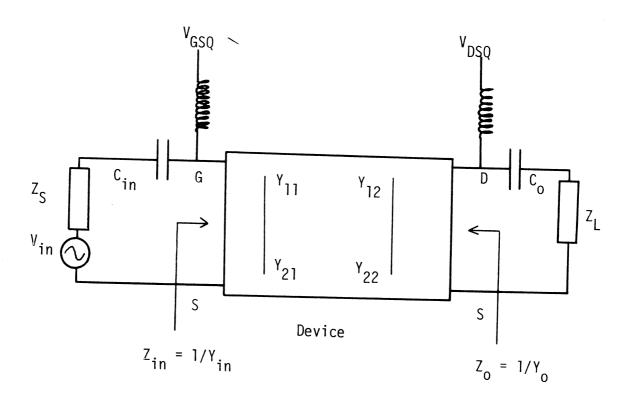

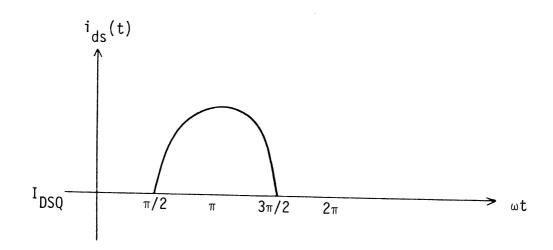

| 4.20   | A Large-Signal Amplifier Circuit.                                                                                                                                                     | 198  |

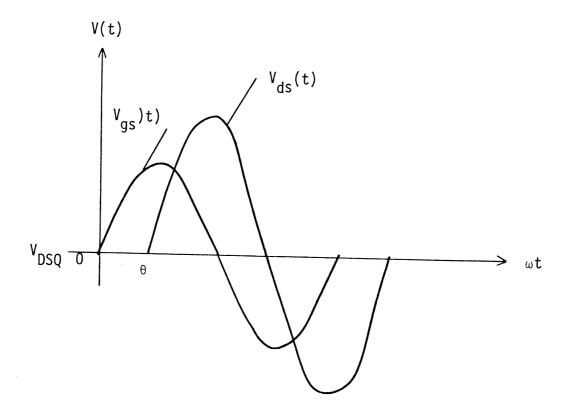

| 4.21   | The Current and Voltage Waveforms under Large-<br>Signal Conditions.                                                                                                                  | 202  |

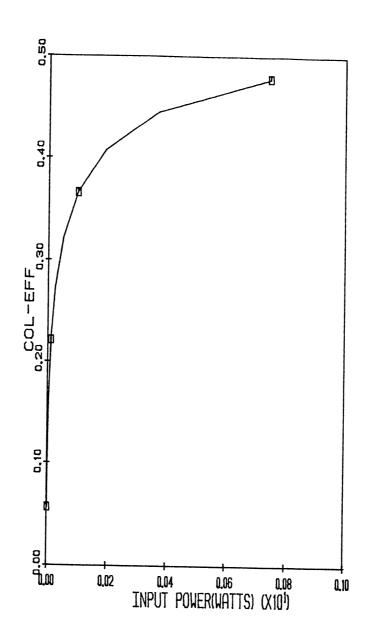

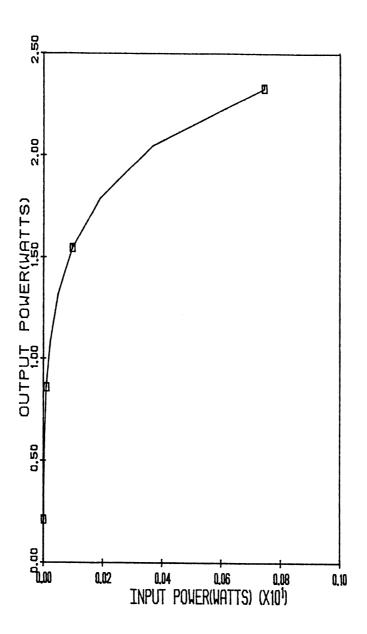

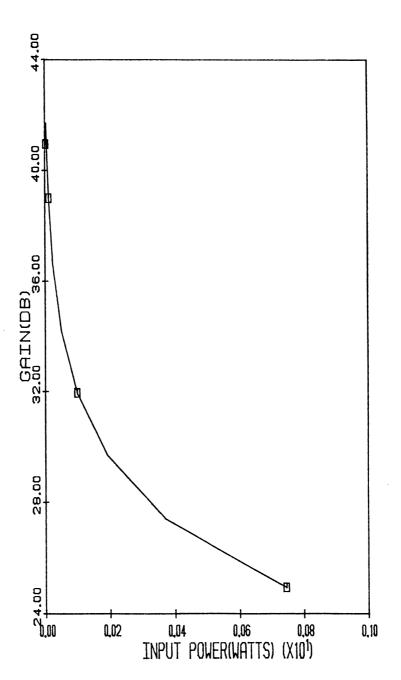

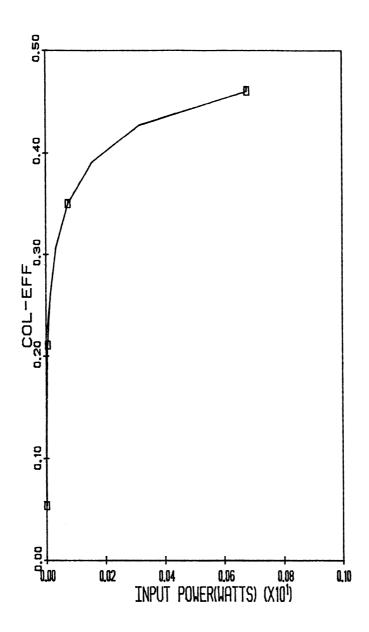

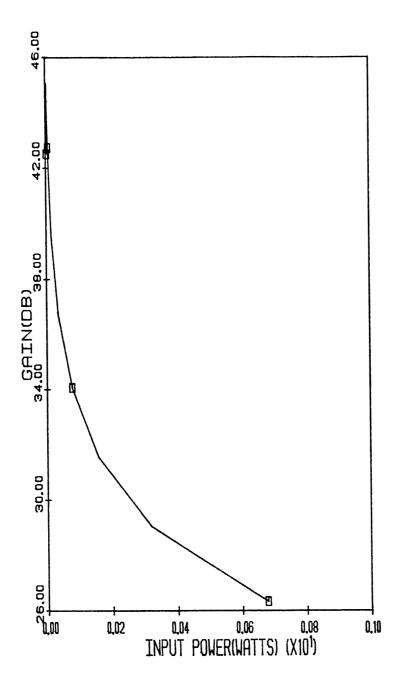

| 4.22a  | The Large-Signal Performance of a GaAs FET (Device S7) at 5.0 GHz.                                                                                                                    | 206  |

| 4.22b  | The Large-Signal Performance of a GaAs FET (Device S7) at 5.0 GHz.                                                                                                                    | 207  |

| 4.22c  | The Large-Signal Performance of a GaAs FET (Device S7) at 5.0 GHz.                                                                                                                    | 208  |

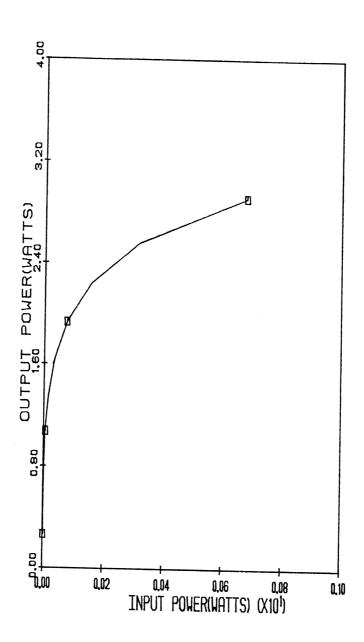

| 4.23a  | The Large-Signal Performance of an InP FET (Device S8) at 5.0 GHz.                                                                                                                    | 209  |

| 4.23b  | The Large-Signal Performance of an InP FET (Device S8) at 5.0 GHz.                                                                                                                    | 210  |

| 4.23c  | The Large-Signal Performance of an InP FET (Device S8) at 5.0 GHz.                                                                                                                    | 2.17 |

| 4.24 The Output Power of a Si FET (Device S9) at 5.0 GHz as a Function of the Input Powers.                                                              | 212   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

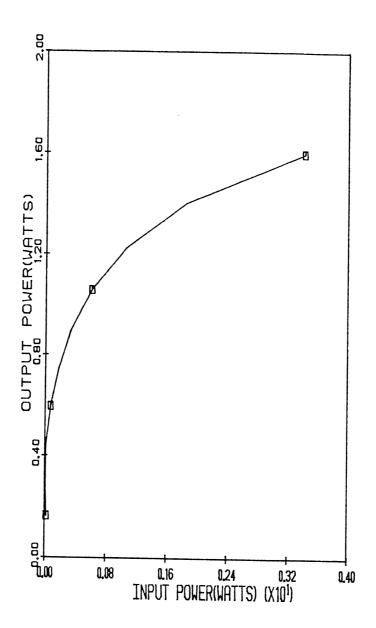

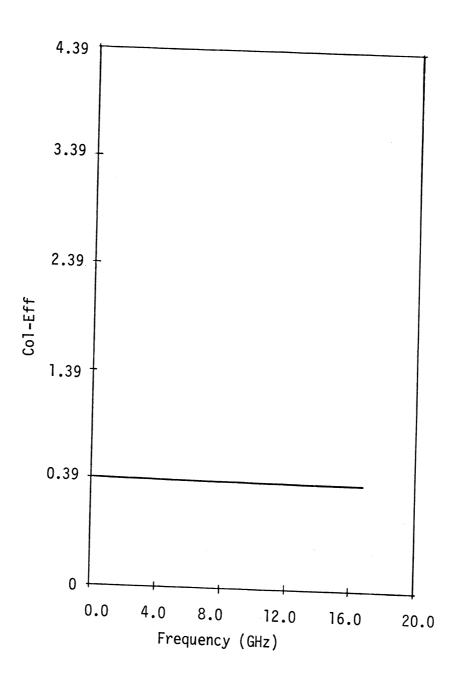

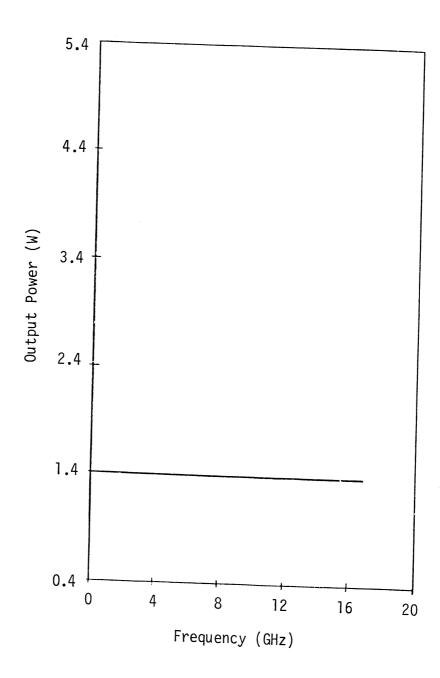

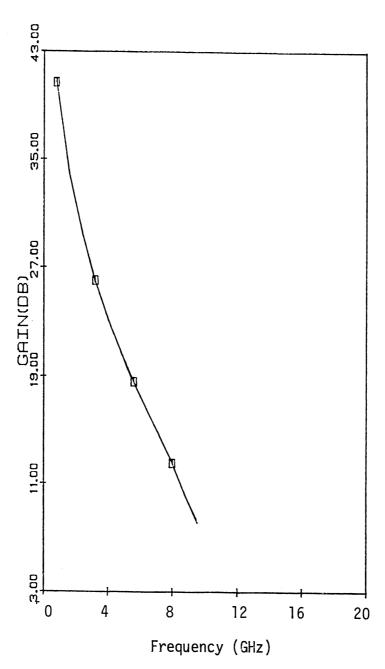

| 4.25a The Large-Signal Performance of an InP FET (Device S8) as a Function of Frequency.                                                                 | 213   |

| 4.25b The Large-Signal Performance of an InP FET (Device S8) as a Function of Frequency.                                                                 | 214   |

| 4.25c The Large-Signal Performance of an InP FET (Device S8) as a Function of Frequency.                                                                 | 215   |

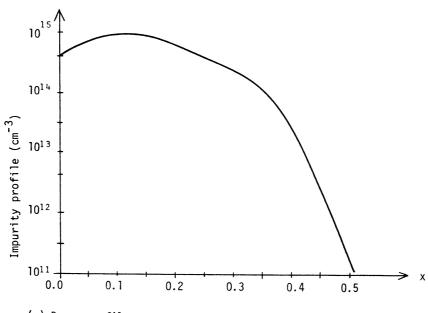

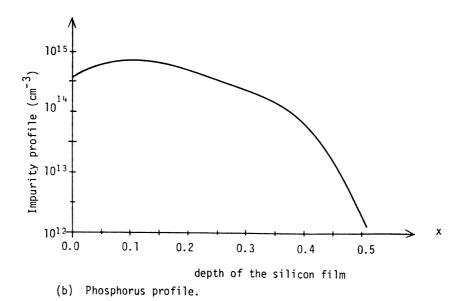

| 5.1 Profile of the Ion Implanted Impurities.                                                                                                             | 227   |

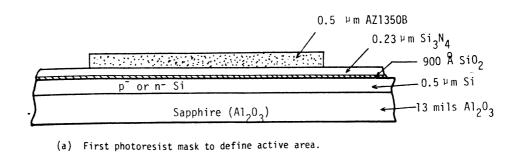

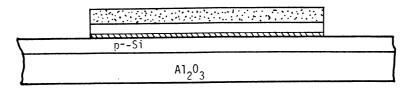

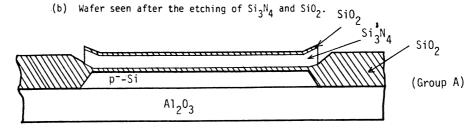

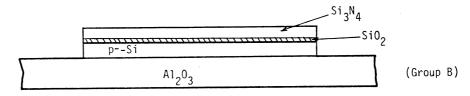

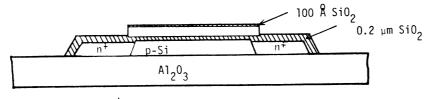

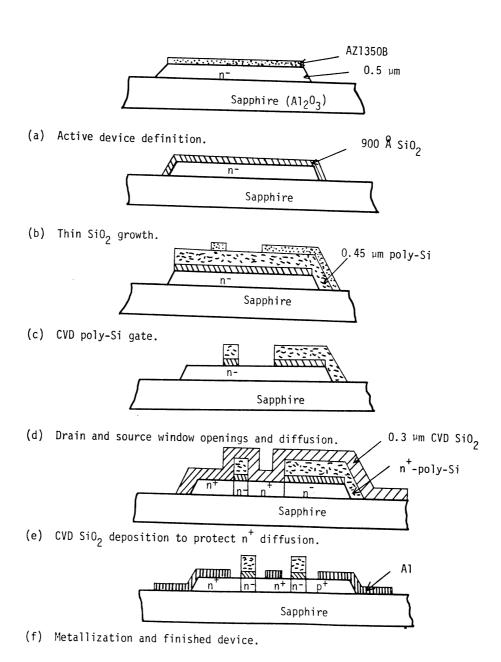

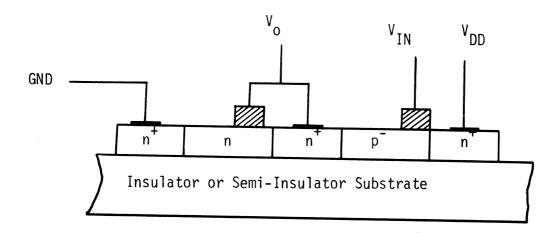

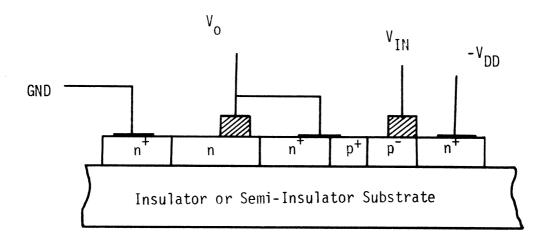

| Fabrication Processes of the MSM and Junction (J) GFC-BARITT Devices.                                                                                    | 229   |

| 5.3 Ideal Schottky Barrier GFC-BARITT Device.                                                                                                            | 234   |

| 5.4 Fabricated GFC-BARITT Device.                                                                                                                        | 235   |

| 5.5 $n^+p^-n^+$ Device (Z = 0.2025 cm, L <sub>G</sub> = 5 $\mu$ m and L <sub>DS</sub> = 20 $\mu$ m).                                                     | 236   |

| 5.6 MSM GFC-BARITT Device. (Z = 500 $\mu$ m, L <sub>SG</sub> = 2.5 $\mu$ m, L <sub>GD</sub> = 12.5 $\mu$ m, and 0.5 $\mu$ m thick).                      | 237   |

| Insulated Gate $n^+ n^- n^+$ SIT Device. (Z = 125 $\mu$ m, $L_{SG}$ = 3.5 $\mu$ m, $L_{GS}$ = 10 $\mu$ m, $L_{DS}$ = 30 $\mu$ m, and 0.5 $\mu$ m thick). | 238   |

| 5.8. $n^+p^-n^+$ GFC-BARITT Device. (Z = 125 $\mu$ m, $L_{SG}$ = 5 $\mu$ m, $L_{GS}$ = 10 $\mu$ m, $L_{DS}$ = 30 $\mu$ m, and 0.5 $\mu$ m thick).        | 241   |

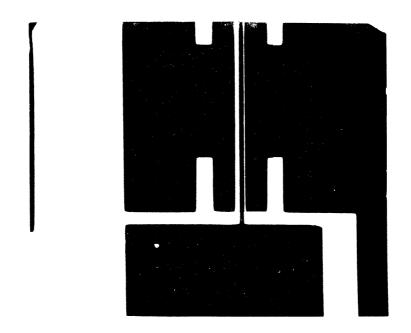

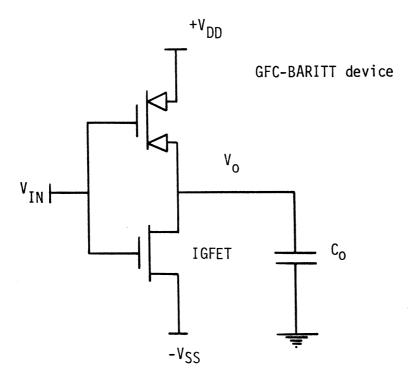

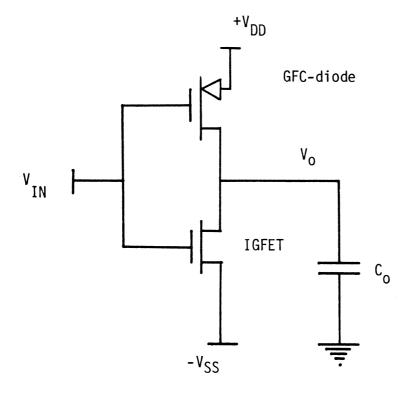

| 5.9 Inverter Structures.                                                                                                                                 | 243   |

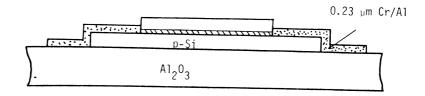

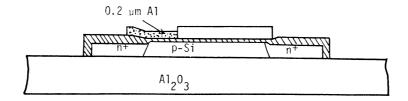

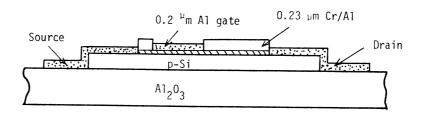

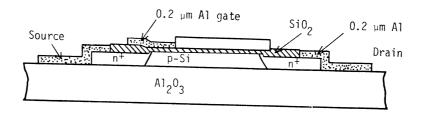

| 5.10 Fabrication Steps.                                                                                                                                  | 247   |

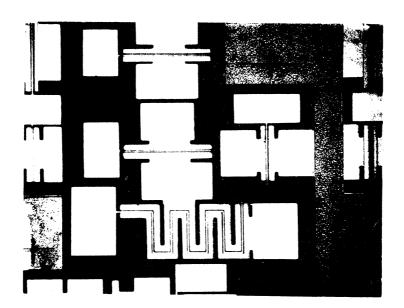

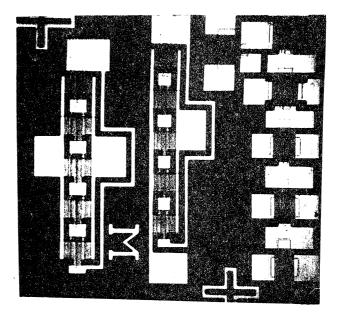

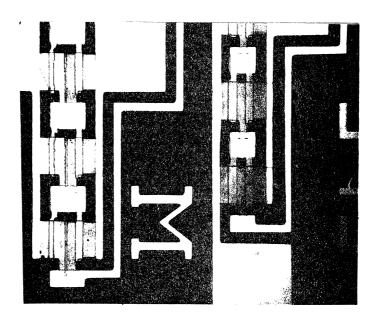

| 5.11 Photomicrograph of the Five-Stage Ring Oscillators.                                                                                                 | . 248 |

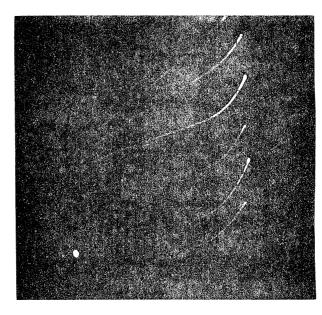

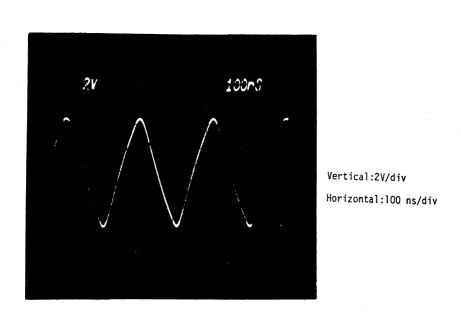

| 5.12 Output Waveforms of the Complementary ICL Ring Oscillator.                                                                                          | 249   |

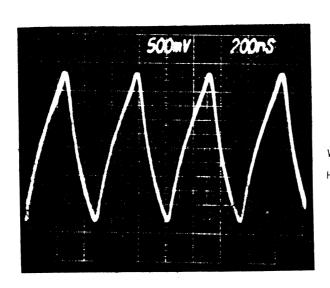

| 5.13 Output Waveforms of the CMOS/SOS Ring Oscillator.                                                                                                   | 250   |

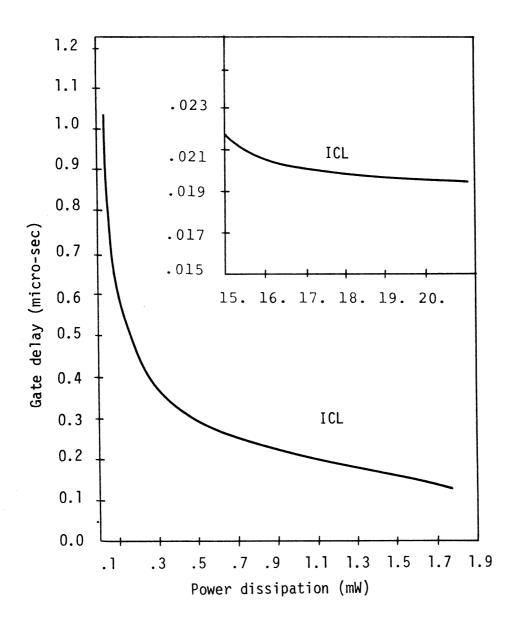

| 5.14 Switching Speed of the Injection Controlled Logic Gate as a Function of the Power Dissipation.                                                      | 251   |

| Figure |                                                                                    | Page |

|--------|------------------------------------------------------------------------------------|------|

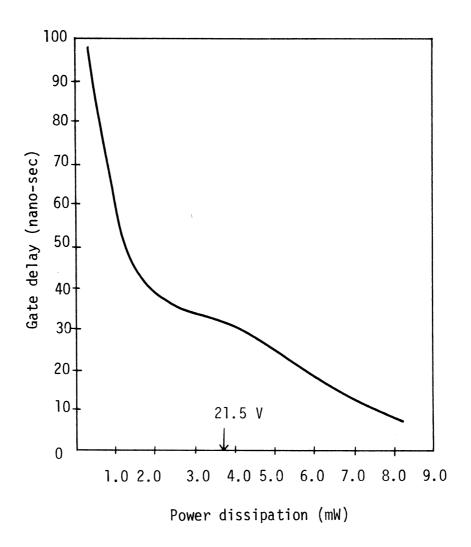

| 5.15   | Switching Speed of the Punch-Through Logic Gate as a Function of Power Dissipation | 252  |

| 5.16   | GFC-BARITT Device Inverter Circuit with a Capacitive Load.                         | 257  |

| 5.17   | ICL inverter Circuit with a Capacitive Load.                                       | 261  |

| 5.18   | Inverter Structure for Semiconductors with High Electron Mobilities.               | 263  |

# LIST OF TABLES

| <u>Table</u> |                                                     | Page |

|--------------|-----------------------------------------------------|------|

| 1.1          | Potential Power Devices                             | 14   |

| 2.1          | Power Performance of SITs                           | 45   |

| 4.1          | List of the Devices                                 | 119  |

| 5.1          | Energy Bandgap for Various Semiconductor Materials. | 224  |

| 5.2          | Ion-Implantation Data                               | 226  |

#### LIST OF SYMBOLS

A\*\* The effective Richardson's constant.

D One half of the device thickness.

$\mathbf{D}_{\mathbf{n}}$  Diffusion coefficient.

$D_p, D_n$  The hole and electron diffusion coefficients.

E Electric field.

$\mathbf{E}_{\mathbf{C}}$  The field at the peak velocity.

${\sf E}_{\sf FR}$  The field at the forward-biased junction side.

$\mathsf{E}_\mathsf{RB}$  The maximum field at the reverse-biased junction side.

E<sub>sat</sub> The field where velocity reaches half of the saturated

velocity.

f Frequency.

$f_T$  Cut-off frequency.

$f_{2\pi}$  Frequency where the phase delay becomes  $2\pi$  .

F The noise figure.

G The carrier generation rate.

$J_0 = qv_{sat}n_p$  Current density.

$J_p, J_n$  Hole and electron current densities, respectively.

J<sub>so</sub> Maximum current density of a BARITT diode.

k<sub>.</sub> A constant.

k A constant.

L<sub>DS</sub> Channel length.

Length of the depletion layer from the forward-

biased junction side.

Ln Diffusion length for electrons. Length of the depletion layer from the reverse-biased  $L_{R}$ junction side of the n+pn+ diode. Distance between the source and the point where the  $L_{S}$ velocity of carrier saturates. Effective mass of electrons. m М Noise measure. Electron density. n Intrinsic carrier density. n<sub>i</sub> n<sub>in.i</sub>(I) Density of the injected carriers at the Ith segment. Minority carrier density at thermal equilibrium. npo Source doping concentration. ns  $n_{th} = N_D$ SIT. Number of segments or BARITT diodes of a GFC-BARITT N device. N Number of channels. Impurity concentration of the p-type semiconductor. NΔ  $N_{D}$ Impurity concentration of the n-type semiconductor. Hole density. p  $^{\mathsf{P}}\mathsf{DC}$ Dissipated power. RF input power. Pin Po Output power. Hole and electron densities which would exist if the p<sub>t</sub>,n<sub>t</sub> Fermi level coincided with the trap level. A constant which is less than unity. r Source resistance. rs The "real part". Re

$R_{\mathbf{f}}$

Thermal noise of the source parasitic resistance.

$R_{\rm m}$ Thermal noise of the gate parasitic resistance. Time. t T Temperature in °K. Turn-off time of an inverter. TOFF  $\mathsf{T}_{\mathsf{ON}}$ Turn-on time of an inverter. Voltage. Carrier velocity as a function of the local electric v(x)field along the conduction path. Hole and electron drift velocities (dependent upon E). V<sub>p</sub>,V<sub>n</sub> Saturated velocity.  $v_{sat}$ Initial output voltage. Voi V<sub>02</sub> Final output voltage. Velocity of the thermionic emission over a potential V<sub>TE</sub> barrier of zero height.  $V_{B}$ Built-in potential of a p-n junction of an MSM BARITT diode.  $V_{B1}$ Total barrier height. V<sub>B2</sub> Built-in potential between the gate and channel. Forward biasing voltage across the source-channel ٧F junction. Flat band voltage.  $V_{FB}$ ٧<sub>F</sub>(I) Forward bias voltage at the Ith segment. Punch-through voltage for the distance of L<sub>DS</sub>-L<sub>G</sub>. VPTG Source gate voltage. V<sub>GS</sub> k is the Boltzmann constant and q is the electronic  $V_T = kT/q$ Distance between the source and the gate. WGS Channel width. Ws Distance that carriers travel in the conduction path. Х

Input admittance.

$^{\rm y}$ in

$Y_L$ Load admittance. Z Gate width. Impedance of the noise source. Zs α(I) Barrier modulation parameter. Hole and electron ionization coefficients.  $\alpha_{p}$ Δf Frequency bandwidth. Power efficiency.  $\eta_a$ Collector efficiency.  $^{\eta}c$ Forward bias due to  $V_{\rm DS}$ . φG Barrier height inducted by the gate-source voltage.  $\phi_{G}(I)$ Potential of the Ith segment along the y-direction due to applied gate-source voltage.  $^{\varphi}\mathsf{n}_1$ Minimum barrier height of a metal-semiconductor junction (Schottky barrier).  $^{\phi}$ so Junction potential barrier. Delay angle due to transit time. Hole and electron lifetimes.  $n^{\tau}q^{\tau}$ Angular frequency. ω

#### CHAPTER I. INTRODUCTION

### 1.1 Introduction

This study is concerned with basic device theory and modelling of <u>Three-Terminal Punch-Through</u> (TTPT) devices, such as <u>Gate-Field-Controlled Barrier Injection Transit Time</u> (GFC\_BARITT) and <u>Static Induction Transistor</u> [1] (SIT) devices. Even though the operating principles of these two devices are different, both can be characterized by the same type of mathematical expressions. The theory developed in this study directly pertains to  $n^+pn^+$  and <u>Metal Semi-conductor-Metal</u> (MSM) GFC-BARITT devices, and  $n^+n^-n^+$  SITs. The results can be easily adapted to the analysis of the other device structures, such as  $p^+np^+$  GFC-BARITT and  $p^+p^-p^+$  SIT devices.

As a result of the low gate-source capacitance and the parasitic capacitance, and the high transconductance of TTPT devices in general, they are capable of operation at high frequencies. The experimental studies of SIT devices indicate that they are promising in the areas of high frequency and high power analog circuit applications [2]. Although there has been some experimental work on SIT devices [1] and [3], there have been no published studies on the theoretical capabilities and limitations of TTPT devices. For these reasons, this present study will focus on the theoretical constraints of the maximum frequency of operation of TTPT devices. An experimental study of the switching speed of SOS GFC-BARITT

devices to show their feasibility for digital circuit applications and the fabrication of a new MSM GFC-BARITT device are also included.

# 1.2 Principles of Operation of Three-Terminal Punch-Through Devices

There are two types of TTPT devices. These are (a) the minority carrier devices such as the GFC-BARITT and Lateral Punch Through Transistor [4], and (b) the majority carrier devices such as the junction gate SIT and the insulated gate SIT devices. In all these devices, the carrier injection, either majority or minority, is controlled by a third electrode. This electrode can be an insulated gate as in the GFC-BARITT devices, a junction gate as in SIT devices or an ohmic-contact gate as in Lateral Punch-Through Transistors. In the following sections, the GFC-BARITT and SIT devices will be considered.

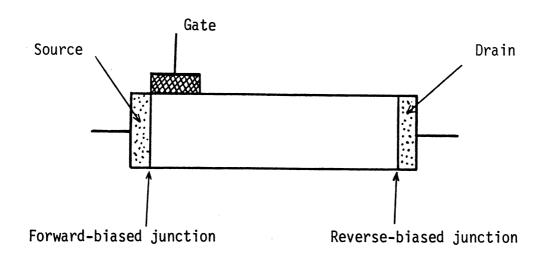

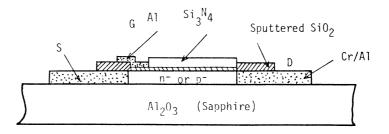

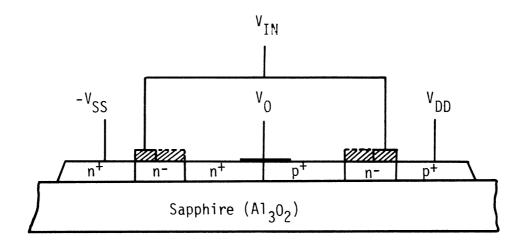

Fig. 1.1 Structure of an Ideal GFC-BARITT Device.

carrier device which uses a junction gate instead of an insulated gate.

In a minority-carrier type of structure, the carrier injection is controlled by a reverse-biased junction in a punch-through diode such as that found in MSM, p<sup>+</sup>np<sup>+</sup> or n<sup>+</sup>pn<sup>+</sup> type of BARITT diodes. An insulated gate electrode has been added to a BARITT diode to control the injection through the gate. A two-terminal diode then becomes a three-terminal device with all the features of a transit-time device. The advantages of a three-terminal device over a two-terminal device are: (i) a three-terminal device requires simple circuitry, and (ii) its efficiency is also much higher than that of a two-terminal device.

The operation of a pn junction-type GFC-BARITT device can be summarized as the control of the injection of the minority carriers from the source to the channel through an insulated gate. Even though the same principle holds true for the injection of the minority carriers in a MSM GFC-BARITT device, the details of the current transport of a MSM device are different from that of a p-n junction type device. Because of this difference the following section elaborates on the current transport mechanism of a MSM GFC-BARITT device.

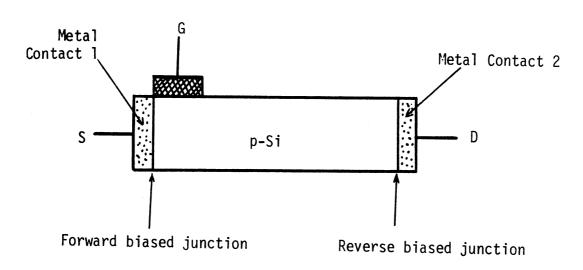

1.2.1a MSM GFC-BARITT Device: Current Transport Mechanism. A MSM BARITT device with an insulated gate in the close vicinity of the forward-biased junction is shown in Fig. 1.2. A MSM BARITT diode allows current to flow when the applied bias voltage exceeds a critical voltage across the drain-source terminals. The critical

Fig. 1.2 MSM GFC-BARITT Device.

voltage is referred to as the punch-through ( $V_{PT}$ ) or the reach through ( $V_{RT}$ ) voltage at which the depletion regions of the forward and reverse biased junctions are joined together. For voltages in excess of  $V_{PT}$ , the barrier height between contact 1 metal (the source) and the semiconductor will be lowered. This is illustrated in Figs. 1.3(a) and 1.3(b). As a result of this lowering of the barrier, electrons from the metal will be injected into the semiconductor by way of thermionic emission. The current transport mechanism of an MSM BARITT diode prior to punch-through has been analyzed in [7] and is outside the scope of this present study.

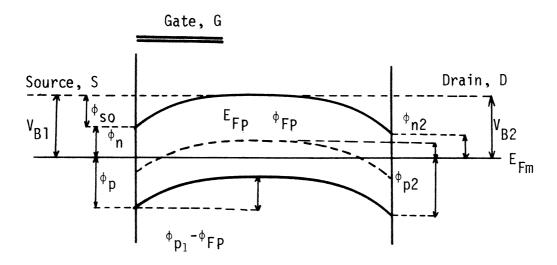

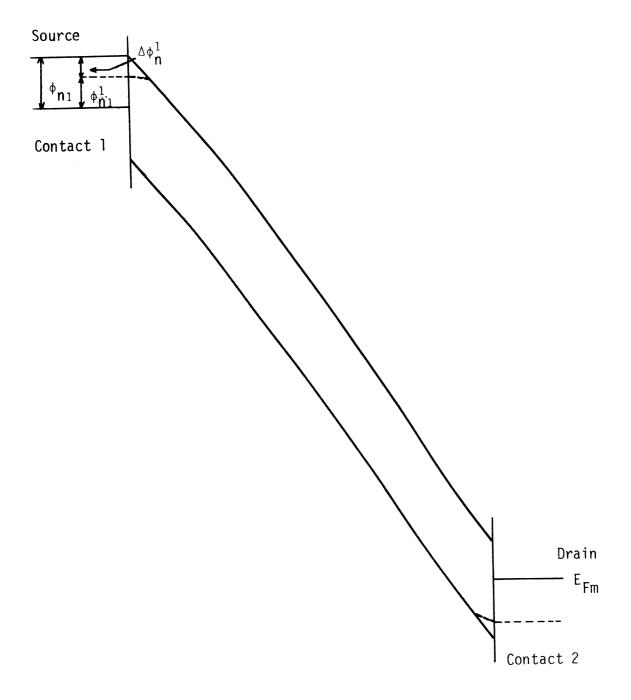

In Fig. 1.3(a), the initial energy band diagram and the barrier heights are indicated. In that figure,  $\phi_{p1}$ - $\phi_{FP}$  is the Schottky barrier height against the holes in the p-type semiconductor.  $\phi_{n1}$  is the minimum barrier height against the electron injection from metal to semiconductor.  $\phi_{s0}$  is the junction potential barrier also against the electron injection.  $V_{B1}$  is the final barrier height for the electron injection at contact 1. At contact 2, the same symbols with index number 2 have the same meaning as those in contact 1. However, in Fig. 1.3(b), the total barrier height against the electrons is reduced. The electron current can be approximated as in Eq. 1.1, by following Sze's treatment [7]:

$$J_{DS} = A^{**}T^{2} DEXP(-V_{B1}/V_{T})$$

, (1.1)

where A\*\* is the effective Richardson's constant, T is the temperature in degrees Kelvin, and  ${

m V}_{\rm B1}$  is the total barrier height against

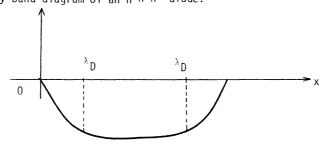

(a) At thermal equilibrium.

(b) At  $V_{DS} \ge V_{PT}$  (beyond punch-through).

Fig. 1.3 MSM GFC-BARITT Device Energy Bands.

electron injection and  $V_T = kT/q$  where k is the Boltzmann constant and q is the electronic charge.

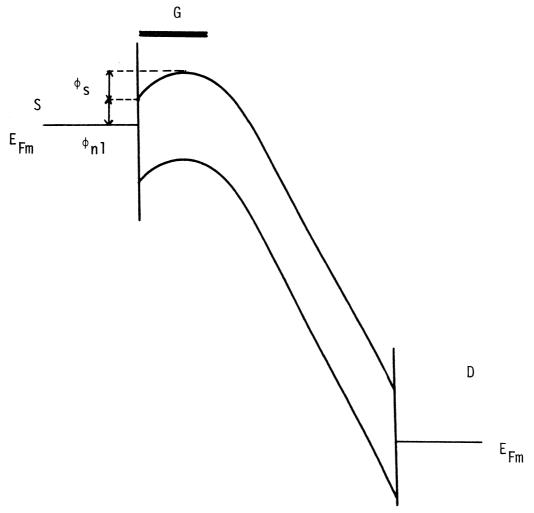

As the voltage is increased further, a point is reached at which the energy band at contact 1 become flat. This is the flat band condition with the corresponding flat band voltage,  $V_{FB}$ . For voltages in excess of  $V_{FB}$ , the energy band is bent further down. If the length of the p-semiconductor is  $L_{DS}$ , the corresponding flat band voltage expression is given by

$$V_{FB} = \frac{qN_A}{2\varepsilon_S} L_{DS}^2 , \qquad (1.2)$$

where N  $_{\!A}$  is the impurity concentration of the p-semiconductor and  $\epsilon_s$  is the semiconductor permittivity.

The increase in the applied voltage  $V_{DS}$  between the  $V_{PT}$  and  $V_{FB}$  voltages results in an exponential increase of the electron current. The electron current, however, increases slowly with  $V_{DS}$  in excess of  $V_{FB}$ . This current increase is due to the barrier lowering effect of the electric field shown in Fig. 1.4. The reduction in barrier height is given by Eq. (1.3):

$$\Delta \phi_{n1} = \left(\frac{q(V_{DS} - V_{FB})}{4\pi\epsilon_{S} L_{DS}}\right)^{1/2} . \qquad (1.3)$$

The minimum barrier height,  $\phi_{n1}$  is one of the main differences between a pn junction (n<sup>+</sup>pn<sup>+</sup> or p<sup>+</sup>np<sup>+</sup>) and a MSM BARITT diode.

Fig. 1.4 Energy Band Diagram at  $|V_{DS}| \ge |V_{FB}|$ .

Unlike a MSM BARITT diode in which the metallurgy determines the minimum barrier height, the pn junction type BARITT diode has no such characteristic. There is, however, a space-charge limitation to the injection of the minority carriers in the case of a pn junction type BARITT diode. If  $\phi^1_{n_1}$  ( $\phi^1_{n_1} = \phi_{n_1} - \Delta \phi_n$ ) is high, a MSM BARITT diode biased even at voltages in excess of  $V_{PT}$ , does not show its usual exponential current voltage (I-V) characteristic until the avalanche breakdown occurs. This unique characteristic of a MSM diode distinguishes it from other pn junction type diodes.

In the discussion given above, the assumption was made that the doping concentration was light enough and the length of the semiconductor was long enough so that the flat band condition occurs before avalanche breakdown occurs at the reverse-biased junction.

In this analysis, neither the role of an insulated gate close to the forward biased junction (contact 1), nor the effect of the diffusion of the injected carriers at the low field region on the I-V characteristics have been considered.

The following discussion considers the effect of the insulated gate on the I-V characteristics of an M-pS-M BARITT diode. The applied gate voltage will modify the minimum barrier height  $\phi_{n_1}^1$  of the forward biased junction of a MSM BARITT device. For a positive gate voltage, the barrier height  $V_{B1}$  and the minimum barrier height of an MSM BARITT diode are lowered. This is why a M-pS-M GFC-BARITT device is able to conduct higher currents than a conventional M-pS-M BARITT diode of the same size. However, if the gate voltage is negative, the current flow will be reduced.

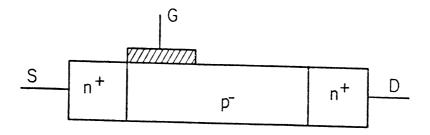

1.2.2 Static Induction Transistors (SITs). One can characterize a SIT as a three-terminal punch-through device, even though the punch-through occurs between the gate and the drain rather than between the source and the drain. If the channel of a vertical FET is lightly doped, then the whole channel will be depleted at the pinch-off condition. If the drain-source voltage is further increased beyond the pinch-off condition, the FET operates as a SIT, assuming that the drain-gate breakdown does not occur.

The SIT is a majority carrier injection-type device. Only the Dc analysis of this device has been undertaken [1]. The Dc current expressions for different approximations are given by

$$I_{DS} = q \left[ \frac{kT}{2\pi m^*} \right]^{1/2} An_s \exp \left[ - \left( \frac{\phi + r_o V_{GS}}{V_T} \right) \right] \qquad (1.4)$$

for the thermionic emission approximation and

$$I_{DS} = qA \frac{D_n}{L_n} n_s \exp \left[ -\left( \frac{\phi + r_0 V_{GS}}{V_T} \right) \right]$$

(1.5)

for the diffusion approximation.

The following expressions are given for the multi-channel SIT device in [3]:

$$I_{DS\phi} = A \int_{-D}^{+D} exp \left[ - \frac{\phi(y) - (V_{GS}(y) - I_{DS}r_s)}{V_T} \right] dy$$

(1.6)

and

$$I_{DS} = I_{DS1}I_{DS\phi}$$

for the thermionic approximation and

$$I_{DS} = I_{DS2}I_{DS\phi}$$

for the diffusion approximation.

Where

$$I_{DS1} = qn_s \left(\frac{kT}{2\pi m^*}\right)^{1/2} N$$

,

$$I_{DS2} = q \frac{D_n}{W_G} n_s N ,$$

$D_n$  = diffusion coefficient,

$L_n$  = diffusion length

N = number of channels,

$r_0$  = a constant which is less than unity,

r<sub>s</sub> = source resistance

k = Boltzmann constant,

m\* = effective mass of electrons,

$W_{GS}$  = the distance between the source and the gate

$A = ZW_{s}$

Z = gate width

$W_S$  = channel width

$n_s$  = the source doping concentration

$\phi$  = forward bias due to  $V_{DS}$  and

${\rm V}_{\rm GS}$  = the source gate voltage.

As the published reports indicate, the SIT is a high power device [2], [8]. The major limitation of a SIT device is that its performance is too process-sensitive as reported in [9] and [10]. This makes it difficult to fabricate reproducible SIT devices. The process sensitivity of the SIT as a power device is not as critical as in the case of digital circuit applications.

A summary of the principles of operation and limitations of various TTPT devices including SIT devices are listed in Table 1.1.

## 1.3 Outline of the Present Study

The objective of this study is to carry out a theoretical and experimental investigation of the capabilities and limitations of TTPT GFC-BARITT and SIT devices. Analytical equations, mainly circuit models and computer solutions of the analytical device expressions are utilized to determine dc small-signal, noise, and large signal behavior of these devices.

In Chapter II, dc expressions for the GFC-BARITT and SIT devices are derived for different semiconductors, dc expressions are given for three different simplified cases: (i) a drift-diffusion approximation, (ii) a drift approximation, and (iii) a thermionic diffusion approximation.

In Chapter III, small-signal, noise, and large-signal models for GFC-BARITT and SIT devices are discussed. Also, the effect of the transit time on the performance of these devices are considered. The carrier temperature variation as a function of the electric field, and its effect on the device noise is also accounted for.

Table 1.1

Potential Power Devices

| Major Limitation |         | insulated gate technology                         | through an insu- insulated gate technology<br>lated gate | through an insu- insulated gate technology<br>lated gate    | limited voltage swing             | limited voltage swing due<br>to obmic gate (high gate<br>current) |

|------------------|---------|---------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------|-----------------------------------|-------------------------------------------------------------------|

| Modulation       |         | through an insu-<br>lated gate                    | through an insu-<br>lated gate                           | through an insu-<br>lated gate                              | reverse bias<br>pn junction       | ohmic gate                                                        |

| 00:+0:10a00      | Collaga | injection of<br>minority carriers                 | injection of<br>majority carriers                        | thermionic emission<br>or injection of<br>minority carriers | injection of<br>majority carriers | injection of<br>minority carriers                                 |

| Ç<br>Ç           | lype    | minority<br>carrier                               | majority<br>carrier                                      | minority<br>carrier                                         | majority<br>carrier               | minority<br>carrier                                               |

| •                | Device  | GFC-BARITT<br>n <sup>+</sup> pn/p <sup>+</sup> np | d_d_d<br>+ - + +                                         | MSM                                                         | SIT<br>+ - +<br>n n n n           | Lateral punch-<br>through tran-<br>sistor                         |

In Chapter IV, the outline of a computer program is developed which calculates the DC current voltage characteristics, the small signal circuit gain, and noise, and large-signal circuit gain and efficiency of TTPT devices. In addition, a simple model for the vertical field effect transistors is included in the simulation program (SIM-GFC). All of the calculations can be extended to silicon and/or III-V compound semiconductors, such as GaAs and InP.

In Chapter V, the fabrication, design, and testing of a GFC-BARITT device are given. The resulting experimental and theoretical data are then compared.

Finally, in Chapter VI, a summary of the results of this work, and some suggestions are given for the further study of the TTPT devices.

# CHAPTER II. DEVICE PHYSICS AND DC CHARACTERISTICS OF GFC-BARITT AND SIT DEVICES

#### 2.1 Device Physics

This chapter presents a discussion of the physics of two types of punch-through semiconductor devices. These are:

- (a) A majority carrier device which is called a static induction transistor [1] and

- (b) A minority carrier device which is proposed and studied for the first time here, the GFC-BARITT device. This is basically a barrier injection transit-time device with a third terminal which controls the injection of the carriers from the source to the channel.

Both of these devices are two-dimensional and it is difficult to derive analytical expressions for the device parameters. Therefore, where possible, analytical expressions have been used along with some numerical approximations. Expressions for the  $d_{\rm C}$  current and voltage characteristics include a field-dependent velocity expression to account for the effect of the velocity saturation in the drift region and the effect of the carrier diffusion at the low-field region. A simplified solution of the carrier distribution is also given.

#### 2.2 The GFC-BARITT Device

Although the device theory that is developed throughout this chapter is general in nature, only the  $n^+pn^+$  abrupt-junction

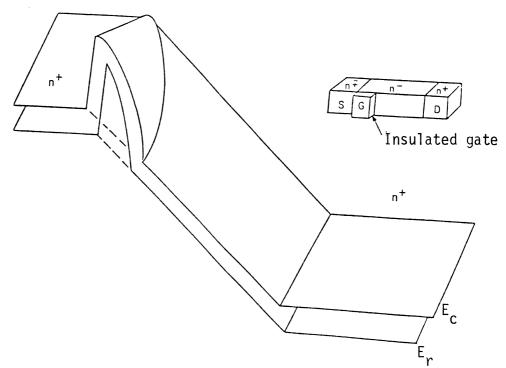

uniformly doped silicon and GaAs or InP structures will be dealt with in detail. A Gate Field Controlled BARITT device (GFC-BARITT) is a BARITT with an insulated gate. Adding an insulated gate to the source side of the BARITT structure results in a GFC-BARITT device. A typical device structure which is considered in this study is shown in Fig. 2.1(a). A two-dimensional band structure of a GFC-BARITT device is shown in Fig. 2.1(b). The principle of operation of this device is based on the control of the injection of carriers from the source electrode into the fully depleted channel through an insulated gate. This device looks and acts like a BARITT diode from the drain side and responds like a MOSFET from the gate side.

Although the operating principle is simple, the description of the characteristics of the device is complicated. In general, this device exhibits the disadvantages of a BARITT diode such as (i) space charge limitation of the injection of the minority carriers (self limitation) and (ii) diffusion effects at the low field region. It also has some advantages over BARITT diodes such as (i) a three-terminal device can be used in microwave and high-speed circuits, (ii) since the gate is insulated, the only limitation on RF input voltage is the gate breakdown voltage and (iii) Class Band C amplifiers can be realized with this device. Changing the polarity of the gate voltage either enhances or suppresses the injection of the minority carriers. As a result the drain-source current can be modulated.

The structure shown in Fig. 2.1(a) is an n<sup>+</sup>pn<sup>+</sup> abrupt-junction GFC-BARITT device. One can describe the device operation physically

(a) Ideal device structure.

(b) Two-dimensional energy band diagram.

Fig. 2.1 GFC-BARITT Device.

as the injection of carriers from one terminal, modulation of these injected carriers through a second terminal (gate), their drift in a high-field region, and the collection of the carriers at the third terminal. Physically abrupt-junctions are not necessary. They can be either a graded junction or a Schottky barrier but the gate has to be insulated. Throughout this study uniformly doped  $n^+pn^+$  structures are considered for simplicity.

2.2.1 <u>Diffusion Effect in the Low Field Region</u>. The exact distribution of the injected carriers requires the simultaneous solution of the basic semiconductor device equations. These are Poisson's equation and the hole and electron continuity equations together with several auxiliary equations which relate the basic solution variables (hole density, electron density and voltage) to the electric field, current density and charge generation. The equations are:

#### Principal Equations:

$$\nabla^2 V = \frac{q}{\epsilon_s} (n - p - N_D) , \qquad (2.1)$$

$$\frac{\partial p}{\partial t} = -\text{div}(J_p/q) + G \qquad (2.2)$$

and

$$\frac{\partial n}{\partial t} = \operatorname{div}(J_n/q) + G . \qquad (2.3)$$

### Auxiliary Equations:

$$E = -grad V , \qquad (2.4)$$

$$J_{p}/q = pv_{p} - D_{p} \operatorname{grad} p , \qquad (2.5)$$

$$J_n/q = -nv_n + D_n \text{ grad } n \qquad (2.6)$$

and

$$G = \alpha_{p} |J_{p}/q| + \alpha_{n} |J_{n}/q| + \frac{pn - n_{1}^{2}}{\tau_{p}(n+n_{t}) + \tau_{n}(p+p_{t})} . \qquad (2.7)$$

The variables in Eqs. 2.1 through 2.7 are defined as follows:

V = the voltage,

p = the hole density,

n = the electron density,

$N_{D}$  = the doping density (positive for donors, negative for acceptors),

t = time,

$J_p, J_n$  = the hole and electron current densities, respectively,

G = the carrier generation rate,

E = the electric field,

$D_p, D_n$  = the hole and electron diffusion coefficients,

$v_p, v_n$  = the hole and electron drift velocities (dependent upon E),

$\alpha_p, \alpha_n$  = the hole and electron ionization coefficients,

$\tau_p, \tau_n$  = the hole and electron lifetimes,

$n_i$  = the intrinsic carrier density and

$p_t, n_t$  = the hole and electron densities which would exist if the Fermi level coincided with the trap level.

The generation recombination term, Eq. (2.7) contains the effects of impact ionization and trapping. Both of the terms will be neglected under the low-field punch-through operating conditions.

In this analysis, however, the exact solutions of the basic device equations (Eq. 2.1 through Eq. 2.3) will not be attempted. Instead, Poisson's equation is solved for low injections to determine the potential distribution. Then the barrier height and the location of the point of the carrier injection are determined. From the known potential distribution, the distribution of the injected carriers can be determined by solving only one continuity equation. Since TTPT devices are monopolar devices, the effects of only the injected carriers are important.

Since for an  $n^+p^-n^+$  and M-pS-M GFC-BARITT and  $n^+n^-n^+$  SIT devices, the electrons are injected carriers, the problem to be solved is

$$\frac{\partial n_p(x,t)}{\partial t} = -\frac{1}{q} \operatorname{div}(J_n) , \qquad (2.8)$$

where  $n_{\rm p}$  is the density of the injected carriers.

In the steady state, Eq. (2.8) reduces simply to

$$\frac{1}{q}\operatorname{div}(J_n) = 0 . (2.9)$$

At the low field region, the current density is given by

$$J_{n} = qn_{p}(x)\mu_{n}E(x) + qD_{n}\frac{\partial n_{p}}{\partial x}. \qquad (2.10)$$

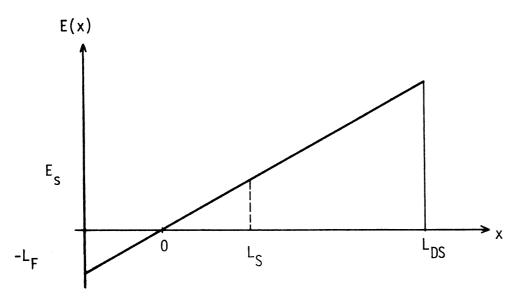

Assuming that the electric field is a linear function of the distance along the conduction path, x, the electric field can be expressed as

$$E(x) = \frac{2(V_{DS} + V_{B})}{L_{DS}^{2}} x$$

, (2.11)

where  $V_{DS}$  is the applied voltage between the drain and the source,  $V_{B}$  is the built-in potential of the  $n^{+}p$  junction between the drain or source and the channel, and  $L_{DS}$  is the length of the channel or distance between the drain and the source electrodes.

By defining

$$\gamma = \frac{2(V_{DS} + V_{B})}{L_{DS}^{2}}$$

Eq. (2.11) becomes

$$E(x) = \gamma x . \qquad (2.12)$$

Using Eq. (2.12) in the expression of the current density yields

$$J_n(x) = qn_p(x)\mu_{no} E(x) + qD_nn_p^i$$

, (2.13)

where  $\mu_{\mbox{no}}$  is the low-field mobility and  $n_p'$  is the first derivative of  $n_p(x)$  with respect to x.

In Eq. (2.13), mobility variation along the path of conduction x is omitted for simplicity. This is a valid assumption for the first-order approximation, since Eq. (2.13) is only valid at the low field region.

Finally, the continuity equation (Eq. 2.9) results in

$$qD_n n_p^n x + qn_p^n(x) \mu_{no} x + q\mu_{no} \gamma n_p(s) = 0$$

, (2.14)

where  $n_p^{"}(x)$  is the second derivative of  $n_p(x)$  with respect to x. After further simplification Eq. (2.14) becomes

$$n_{p}^{"}(x) + \alpha x n_{p}^{'}(x) + \alpha n_{p}^{'}(x) = 0$$

, (2.15)

where

$$\alpha = \frac{2V_{DS}}{L_{DS}^2V_{T}},$$

$$V_T = kT/q$$

and k is the Boltzmann constant, and T is the temperature in degrees Kelvin. After rearranging and integration Eq. (2.15) over x, the

second-order nonlinear differential equation reduces to a first-order differential equation:

$$\frac{d}{dx} [n'_{p}(x) + \alpha x n_{p}(x)] = 0 . \qquad (2.16)$$

Therefore

$$n_{p}'(x) + \alpha x n_{p}(x) = k_{1},$$

(2.17)

where k is a constant. Rewriting Eq. (2.17) as in Eq. (2.18):

$$\frac{dn_p(x)}{dx} + \alpha x n_p(x) = k_1$$

(2.18)

and then rearringing Eq. (2.18) results in

$$\frac{dn_{p}(x)}{n_{p}(x)} + _{\alpha}x dx = k_{1} \frac{dx}{n_{p}(x)} . \qquad (2.19)$$

Now Eq. (2.19) can be integrated over x which yields

$$\ln(n_{p}(x)) + \frac{1}{2} \alpha x^{2} - \ln k_{2} = k_{1} \int \frac{dx}{n_{p}(x)} . \qquad (2.20)$$

The right-hand side of Eq. (2.20) can be approximated as  $k_1(x/n_{sat})$  to obtain an analytical solution where  $n_{sat}$  is the carrier density at a point,  $L_S$ , where the velocity of the carriers saturate. Equation (2.20) then becomes

$$\ln(n_p(x)/k_2) + 0.5 \alpha x^2 \simeq k_1 \frac{x}{n_{sat}}$$

(2.21)

Finally,  $n_p(x)$  can be obtained from Eq. (2.21) and expressed as

$$n_p(x) = k_2 \exp[-0.5 \alpha x^2 + k_1(x/n_{sat})]$$

(2.22)

Applying the boundary conditions to Eq. (2.22),  $k_1$  and  $k_2$  can be found:

(i) the first boundary is the injection point at x = 0

$$n_p(x)_{x=0} = n_{inj}$$

this gives  $k_2 = n_{inj}$ , (2.23)

where  $n_{\mbox{\scriptsize inj}}$  is the density of the injected carriers into the channel and

(ii) the second boundary is a virtual point where the carrier velocity saturates. This boundary was introduced by McCleer [11] and gives the following:

$$n_p(x)|_{x=L_S} = n_{sat}$$

,

$$n_{sat} = n_{inj} \exp(-0.5 \alpha L_{\dot{S}}^2 + k_1 L_{\dot{S}}/n_{sat})$$

and

$$k_{1} = n_{sat} \left[ 0.5 \quad \alpha L_{s} - \frac{\ln(n_{inj}/n_{sat})}{L_{s}} \right] \cdot (2.24)$$

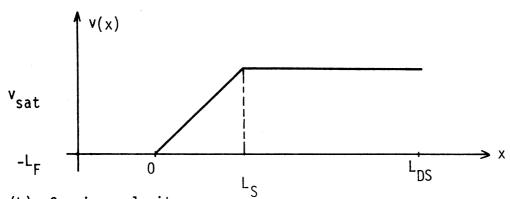

To clarify the boundary conditions, the electric field [Fig. 2.2(a)] the velocity [Fig. 2.2(b)] and the density of minority carriers [Fig. 2.2(c)] are shown as a function of distance x in Fig. 2.2.

The current density must be the same along the path of conduction, x. Therefore,  $n_{\text{sat}}$  can be obtained by equating the pure diffusion current at x=0 to the drift current at  $x=L_S$ . This gives

$$qD_n \frac{\partial^n p}{\partial x}\Big|_{x=0} = qv_{sat}^n_{sat},$$

(2.25)

where  $v_{sat}$  is the carrier saturation velocity. Finally, by combining Eqs. (2.22 through 2.24) with Eq. (2.25), a nonlinear expression for  $n_{sat}$  can be found as follows:

$$n_{\text{sat}} = \frac{0.5 \text{ } \alpha^{\text{L}}_{\text{S}} \text{ } n}{v_{\text{sat}}} n_{\text{inj}} - \frac{D_{\text{n}}}{v_{\text{sat}}^{\text{L}}_{\text{S}}} \ln(n_{\text{inj}}/n_{\text{sat}}) n_{\text{inj}}, (2.26)$$

where  $n_{inj} = n_{po} \exp[(V_F - \phi_G/V_T]]$ ,

$$L_{S} = \frac{E_{TH}}{2V_{DS}/L_{DS}^{2}},$$

$$E_{TH} = v_{sat}/\mu_{no}$$

V<sub>F</sub> = the forward biasing voltage across the source-channel

junction and

$\phi_{G}$  = the barrier height induced by the gate-source voltage.

(a) Electric field.

(b) Carrier velocity.

(c) Injected carrier.

Fig. 2.2 Field, velocity and carrier distributions of a TTPT Device.

2.2.2 Dc Current Density of a GFC-BARITT Device. The expression for the current density  $J_{DS}$  requires knowledge of the distribution of the carriers and the field along the path of conduction. For an exact solution of the current density, Poisson's equation and the continuity equation must be solved simultaneously with the appropriate boundary conditions. This is true for any semiconductor device. It is, however, extremely difficult to obtain analytical solutions for the current density, potential and carrier distributions.

By considering the principle of the device operation, one may obtain quasi-numerical expressions for the current density and electric field. This approach is satisfactory as far as the understanding of a certain device and simplifies the equations considerably. In the course of this study, analytical solutions of the characteristic equations of a device are obtained by making certain simplifications. From Section 2.2.1 the carrier distribution in the device can be used to obtain the current density. In another approach, the diffusion effect is neglected by assuming that all the injected carriers drift along the channel and contribute to the current. In the following sections, two approximations for the current density expression will be given.

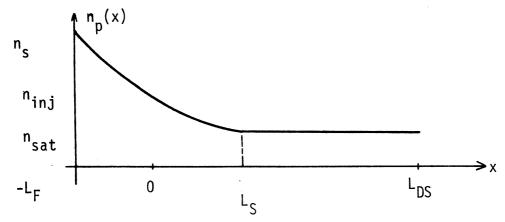

2.2.2a <u>Drift-Diffusion Current Approximation</u>. The GFC-BARITT device operation is governed by the two-dimensional potential distribution. A device is divided into a number of thin devices as shown in Fig. 2.3(a) where each of them has different injection levels as in Fig. 2.3(b). The next important problem is to find the level

(a) Device segmented into N numbers of  $\Delta y$ -thick BARITT diodes.

(b) Carrier distribution in each segment.

Fig. 2.3 A TTPT Device.

of injection in each segment or  $\Delta y$ -thick BARITT diode. The potential distribution is assumed to be the superposition of the potential along the x-direction and the potential along the y-direction. The superposition assumption will simplify the problem of the two-dimensional potential distribution in a GFC-BARITT device. The potential along the y-direction "gate potential" is then expressed as:

$$\phi_{G}(I) = (V_{GS} + V_{B2}) \left[1 - \left(\frac{I - 0.5}{N}\right)\right]^{2}, \quad (2.27)$$

where  $V_{GS}$  = the applied gate-source voltage at the surface of the channel,

$V_{\rm B2}$  = the built-in potential between the gate and the channel,

N = the number of segments or BARITT diodes of a GFC-BARITT device and

$\phi_{G}(I)$  = the potential of the Ith segment along the y-direction due to the applied gate-source voltage.

The potential distribution along the x-direction can be approximated from the BARITT diode expression [12]. In general, it is a quadratic function of x (conduction path). The potential  $V_F(I)$  at the source side of the device must be known in addition to a general knowledge of the potential variation along x. The combination of  $V_F(I)$  and  $\phi_G(I)$  will give the level of forward biasing of each  $\Delta y$ -thick BARITT diode or segment. The density of injected carriers,  $n_{inj}$  can be expressed as:

$$n_{inj}(I) = n_{po} \exp\left(\frac{q}{kT}(V_F(I) - \phi_G(I))\right), \quad (2.28)$$

where  $n_{po}$  = the steady state density of minority carriers in the channel (p-type semiconductor),  $n_{po} = n_i/N_A$ ,

$V_F(I)$  = the forward bias voltage at the Ith segment. An expression for this will be derived in the next section,

$N_A$  = the impurity concentration of the p-type semiconductor,  $n_{\mbox{inj}}(I)$  = the density of the injected carriers at the Ith segment. The current density,  $J_{\mbox{DS}}(I)$  of the Ith segment is:

$$J_{DS}(I) = qv_{sat}n_{sat}(I) , \qquad (2.29)$$

where  $n_{sat}$  is given in Eq. (2.26) and  $v_{sat}$  is the saturated velocity of the carriers. Rearranging Eq. (2.29) and combining it with the expression for  $n_{sat}$ , the  $J_{DS}(I)$  expression of the Ith segment becomes

$$J_{DS}(I) = qn_{in,i}(I) \exp[-0.5 \alpha L_S^2 + k_1^1 L_S] v_{sat}$$

, (2.30)

whe re

$$k_1^1 = 0.5 \alpha L_S - \frac{\ln(n_{inj}(I)/n_{sat})}{L_S}.$$

The expression in Eq. (2.30) is given for the total current which is equal to the drift current beyond  $L_S$ . If one requires drift and diffusion currents separately, the distribution function of the carriers in the channel can be used. The diffusion current density would therefore be:

$$J_{DS_{diff}}(x,I) = qD_n \frac{\partial n_p(x,I)}{\partial x}$$

(2.31)

or

$$^{J}DS_{diff}(x,I) = qD_{n}(k_{1} - \alpha x)n_{p}(x,I)$$

and the drift current density is

$$J_{DS}_{drift}(x,I) = q_{\mu_{no}} n_{p}(x,I) E(x)$$

or

$$J_{DS}_{drift}(x,I) = q_{\mu_{no}} n_{p}(x,I) \gamma x , \qquad (2.32)$$

where

$$n_p(x,I) = n_{inj}(I) \exp[0.5 \alpha x^2 + k_1^1 x]$$

.

For  $x \ge L_S$ ,

$$\frac{\partial n_p(x,I)}{\partial x} = (k_1^1 - \alpha x) n_p(x,I) ,$$

$E(x) = \gamma x$ , the linear electric field, and  $\mu_{no}$  = the low field mobility.

At every point

$$J_{DS}(I) = J_{DS_{diff}}(x,I) + J_{DS_{drift}}(x,I)$$

.

At  $x = L_S$  the point diffusion current becomes negligible. Therefore at  $x \ge L_S$ , the total current density,  $J_{DS}(I)$  is equal to  $J_{DS}(I)$  drift  $(L_S, I)$ .

Finally, the total current  $I_{DS}$  can be obtained from the current density expression of the Ith segment which is given in Eq. (2.30):

$$I_{DS} = 2Z\Delta y \sum_{I=}^{N} J_{DS}(I)$$

, (2.33)

where Z = the width of the device,

$\Delta y = D/N$ ,

D = the half of the channel width ( $W_{\varsigma}/2$ ) and

N = the number of segments into which the GFC-BARITT device is divided.

2.2.2b <u>Drift Current Approximation</u>. In the previous section the effect of the diffusion was discussed. The velocity of the carriers was assumed to be a linear function of the field at the low field region, but constant at the high field region. This approximation, by itself, may introduce a larger error than by neglecting the diffusion effect. Therefore, in this section the effect of the diffusion is neglected, but the velocity as a nonlinear function of the electric field is considered.

A nonlinear velocity expression as a function of the electric field for Si [13] and for III-V compound semiconductors[14] are given as follows.

For silicon:

$$v(E) = v_{sat} \frac{E}{E + E_{sat}} . \qquad (2.34)$$

For III-V compound semiconductors:

$$v(E) = \frac{\left[\mu_{no}E + \nu_{sat}(E/E_c)^4\right]}{\left[1 + (E/E_c)^4\right]},$$

(2.35)

where  $v_{sat}$  = the saturated velocity,

$E_c$  = the field at the peak velocity,

E = the electric field.

The assumptions for the drift current approximation are:

- (a) Negligible generation-recombination in the depleted channel and hole current (unipolar conduction) are assumed.

- (b) The device is an  $n^+pn^+$  structure and is divided into N number of segments as in Section 2.2.1, Fig. 2.3(a).

- (c) The diffusion effect at the low field region of the device is neglected.

- (d) The carrier distribution along the conduction path is uniform.

- (e) The potential of the Ith segment due to the applied gate voltage is  $\varphi_{G}(\textbf{I}).$

- (f) The forward bias voltage due to the applied voltage between the drain and source terminals is  $V_{\rm F}({\rm I})$ .

The current density of the Ith segment is

$$J_{DS}(x,I) = qn_p(x,I)v(E)$$

(2.36)

and

$$n_p(x,I) = n_{po} \exp[(V_F(I) - \phi_G(I)/V_T]$$

(2.37)

The field dependent velocity expressions are given in Eq. (2.34) and Eq. (2.35).

The current density expression for Si devices is

$$J_{DS}(x,I) = qn_p v_{sat} \frac{E}{E + E_{sat}}, \qquad (2.38)$$

where E = dV/dx, the field along the conduction path, x. The integration of Eq. (2.38) with respect to x results in an average current density expression for the low level injection case as follows:

$$J_{DS}(I) = .qv_{sat} \frac{V_{DS}}{V_{DS} + E_{sat}L_{DS}} n_{po} \exp \frac{q}{kT} \left[V_{F}(I) - \phi_{G}(I)\right] . \quad (2.39)$$

The current density of GaAs or InP can be found by using Eq. (2.35) for v(E) in Eq. (2.36) and integrating Eq. (2.36) with respect to the conduction path, x. This yields

$$J_{DS}(I) = J_{O} \exp([V_{F}(I) - \phi_{G}(I)] / V_{T}),$$

(2.40)

where

$$J_{o} \simeq q \frac{n_{i}^{2}}{N_{A}} \frac{\left[0.5 \, \mu_{no} E_{RB} + 0.2 \, v_{sat} (E_{RB}/E_{c})^{4}\right]}{\left[1 + 0.2 (E_{RB}/E_{c})^{4}\right]}$$

and

anu

$$E_{RB} \simeq 2V_{DS}/L_{DS}$$

.

Finally, the drift current can be obtained either from Eq. (2.39) or from Eq. (2.40) and given by

$$I_{DS} = 2Z \frac{D}{N} \sum_{I=1}^{N} J_{DS}(I)$$

(2.41)

The current in a GFC-BARITT device can be calculated either from Eq. (2.41) or from Eq. (2.33), if only  $V_F(I)$  is known. In the next section, an expression for  $V_F(I)$  of the Ith segment of a GFC-BARITT device will be derived.

2.2.3 <u>Potential Distribution</u>. Each segment of a GFC-BARITT device is a BARITT diode. Therefore, Poisson's equation for each segment can be expressed as

$$\frac{\partial E}{\partial x} = -\frac{qN_A}{\varepsilon_S} - \frac{qn_p(x, I)}{\varepsilon_S}. \qquad (2.42)$$

Equation (2.42) is the general expression which includes the space charge effect (or injected carrier effect) on the field distribution. It is necessary however to solve Eq. (2.42) simultaneously with the current density and the continuity equations. To obtain an

analytic solution of the problem (Eq. 2.42), some simplifying assumptions have been made. These are:

- (i) The potential along the y-direction is assumed to be constant so one could solve a one-dimensional Poisson's equation.

- (ii) The injected carrier distribution  $n_p(x)$  is replaced by  $J_{\mbox{\footnotesize{DS}}}/v.$  This gives

$$\frac{\partial E}{\partial x} = -\frac{2}{\varepsilon_{S}} N_{A} - \frac{J_{DS}(I,x)}{\varepsilon_{S}V} \qquad (2.43)$$

The expressions for the velocities are given in Eq. (2.34) for Si and in Eq. (2.35) for GaAs or InP.

The inclusion of the velocity expression in Eq. (2.35) for III-V compound semiconductors is difficult to implement as it is. A modified expression for the velocity is given by

$$v(E) = v_{sat} \frac{E}{E + E_{sat}}, \qquad (2.44)$$

where

$$E_{sat} = v_{sat}/2\mu_{no}$$