# Maskless Laser-Write Lithography of a-Si:H TFT Passive Pixel Sensor for Hemispherical Imager

by

Geonwook Yoo

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2011

#### **Doctoral Committee:**

Professor Jerzy Kanicki, Chair Professor Peter F. Green Professor Kensall D. Wise Associate Professor Jamie D. Phillips © Geonwook Yoo 2011

### Acknowledgements

I sincerely appreciate Prof. Jerzy Kanicki, my research advisor and doctoral committee chair, for his support and guidance throughout my graduate study. It was a great and precious opportunity for me to work with him on this exciting project. I am deeply grateful for my doctoral committee members, Prof. Kensall D. Wise, Prof. Peter F. Green, and Prof. Jamie D. Phillips for their help in completing my thesis.

I also truly thank Daniela Radtke at Fraunhofer Institute for Applied Optics and Precision Engineering in Germany, Tae-Kyung Won at AKT America, Inc., Sandro Tedde at Siemens AG TC, and Werner Salewski at Heidelberg Instrument. A large portion of the success of this work is attributed to their collaboration and advice. My special thanks belong to Daniela for her help on laser-write lithography. I express my gratitude to all LNF staffs, especially to Brian VanDerElzen.

I thank my current and previous group members: Gwanghyeon Baek, Dr. Hojin Lee, Dr. Alex Kuo, Dr. Tze-ching Fung, Dr. Charlene Chen, and Dennis Feng. It was their support and friendship that helped me to get through the course of graduate study. In addition I am very grateful to all my seniors and friends both in U.S and Korea for their belief and support.

I would like to thank DARPA/MTO HARDI program (Dr. D. Shenoy), Samsung scholarship program, and EECS department for their financial supports. The views, opinions, and/or findings contained in this paper are those of the authors and should not be interpreted as representing the official views or policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the Department of Defense (approved for public release, distribution unlimited)

Lastly and most importantly, much gratitude from the bottom of my heart is due to my family in Seoul, Korea for their support and love.

# **Table of Contents**

| A  | knowle    | dgements                                                 | ii     |

|----|-----------|----------------------------------------------------------|--------|

| Li | st of Tal | bles                                                     | viii   |

| Li | st of Fig | ures                                                     | ix     |

| Cł | napter    |                                                          |        |

| 1. | Introd    | uction                                                   | 1      |

|    | 1.1       | Motivation/Overview                                      | 1      |

|    | 1.2       | Organization of Dissertation                             | 6      |

| 2. | Advan     | ced a-Si:H Thin-Film Transistor Structures for           | Sensor |

| Ap | plicatio  | on                                                       | 10     |

|    | 2.1       | Introduction                                             | 10     |

|    | 2.2       | Fabrication of Fork and Hexagonal a-Si:H TFT             | 11     |

|    | 2.3       | Electrical Properties and Instability of Fork a-Si:H TFT | 13     |

|    | 2.3.      | 1 Experimental results                                   | 13     |

|    | 2.3.      | 2 Discussion of fork a-Si:H TFT geometry effect          | 15     |

|    | 2.3.      | Fork TFT parameters extraction                           | 23     |

|    | 2.3.      | 4 Electrical instability of fork a-Si:H TFT              | 26     |

|    | 2.4       | Electrical Instability of Hexagonal a-Si:H TFT           | 27     |

|    | 2.4.      | 1 Experiments                                            | 27     |

|    | 2.4.      | 2 Experimental results and discussion                    | 30     |

|    | 2.5       | Conclusion                                               | 32     |

| 3. | Maskless Laser-Write Lithography |                                                             |       |  |  |

|----|----------------------------------|-------------------------------------------------------------|-------|--|--|

|    | 3.1                              | Introduction                                                | 35    |  |  |

|    | 3.2                              | Maskless a-Si:H TFT Processing using a Standard LWL of      | on a  |  |  |

|    |                                  | FlatSurface                                                 | 36    |  |  |

|    | 3.2.                             | 1 Fabrication of a-Si:H TFTs                                | 36    |  |  |

|    | 3.2.2                            | 2 Experimental results and discussions                      | 41    |  |  |

|    | 3.2.3                            | 3 Summary                                                   | 45    |  |  |

|    | 3.3                              | Modified LWL System for TFT Processing on a Non-Planar Surf | ace   |  |  |

|    |                                  |                                                             |       |  |  |

|    | 3.3.1                            | 1 Laser source                                              | 47    |  |  |

|    | 3.3.2                            | 2 Substrate table                                           | 47    |  |  |

|    | 3.3.3                            | 3 Optical and metrology system                              | 47    |  |  |

|    | 3.3.4                            | Data preparation/conversion and exposure                    | 48    |  |  |

|    | 3.3.5                            | 5 Subfield and stitching                                    | 51    |  |  |

|    | 3.3.6                            | 6 Structuring accuracy of LWL on a curved surface           | 52    |  |  |

|    | 3.3.7                            | Advanced LWL system for device/circuit fabrication proces   | ssing |  |  |

|    |                                  | on a curved surface with FOV = 120 $^{\circ}$               | 55    |  |  |

|    | 3.4                              | Conclusion                                                  | 57    |  |  |

| 4. | Maskl                            | ess Processing of a-Si:H TFT on a Curved Surface            | 60    |  |  |

|    | 4.1                              | Introduction                                                | 60    |  |  |

|    | 4.2                              | Fabrication of a-Si:H TFTs on a Curved Surface using Masi   | kless |  |  |

|    |                                  | LWL                                                         | 61    |  |  |

|    | 4.2.1                            | 1 Customized curved glass substrate                         | 61    |  |  |

|    | 4.2.2                            | •                                                           |       |  |  |

|    | 4.2.3                            |                                                             |       |  |  |

|    | 4.2.4                            |                                                             |       |  |  |

|    |                                  |                                                             |       |  |  |

|    | 4.2            | .5    | Concentric expos    | sure strat                              | egy                                     | •••••             |               |          | 69       |

|----|----------------|-------|---------------------|-----------------------------------------|-----------------------------------------|-------------------|---------------|----------|----------|

|    | 4.2            | .6    | Maskless LWL        | TFT fab                                 | rication pr                             | ocess sec         | quence        | on       | a curved |

|    |                |       | surface             |                                         |                                         | •••••             |               |          | 71       |

|    | 4.3            | Ele   | ctrical Properties  | of a-Si:H                               | I TFT on a                              | Curved S          | urface        |          | 73       |

|    | 4.3            | .1    | Experimental res    | ults and                                | discussion                              |                   |               |          | 73       |

|    | 4.4            | Coı   | nclusion            |                                         |                                         |                   |               |          | 77       |

|    |                |       |                     | •                                       | •                                       | •••••             |               | •••••    |          |

| 5. | Elect          | rical | Instability         | of the                                  | a-Si:H                                  | TFTs              | on            | a        | Curved   |

| Su | rface          | ••••• | •••••               | •••••                                   | •••••                                   | ••••••            | •••••         | ••••     | 81       |

|    | 5.1            | Intr  | oduction            |                                         |                                         |                   |               |          | 81       |

|    | 5.2            | Exp   | periments           |                                         |                                         |                   |               |          | 82       |

|    | 5.3            | Res   | ults and Discussion | ons                                     |                                         |                   |               |          | 86       |

|    | 5.4            | Coı   | nclusion            | • • • • • • • • • • • • • • • • • • • • |                                         | •••••             | •••••         |          | 94       |

| 6. | Mask           | dess  | processing of       | a-Si·H                                  | TFT Pag                                 | ssive Pi          | vel Sø        | ากรถ     | rs on s  |

|    |                |       | ce                  |                                         |                                         |                   |               |          |          |

| Cu | i ved b        | uiiu  |                     | • • • • • • • •                         | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • | • • • • • • • | ••••     |          |

|    | 6.1            | Intr  | oduction            |                                         |                                         | •••••             | •••••         | •••••    | 96       |

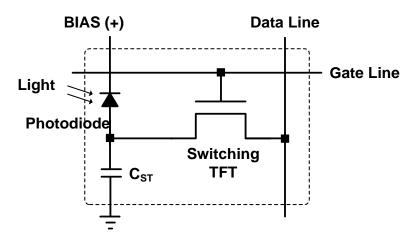

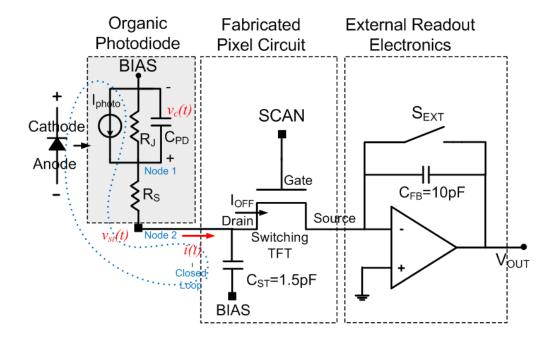

|    | 6.2            | Pas   | sive Pixel Sensor   | and its C                               | peration                                |                   |               |          | 97       |

|    | 6.3            | Fab   | rication of a-Si:H  | TFT PP                                  | S on a Cur                              | ved Surfa         | ce usir       | ng L'    | WL 102   |

|    | 6.4            | Exp   | perimental and Te   | sting Set                               | -up                                     | •••••             |               |          | 103      |

|    | 6.5            | Exp   | perimental Results  | and Dis                                 | cussion                                 | •••••             |               |          | 106      |

|    | 6.5.1<br>6.5.2 |       | Electrical charac   | teristics                               | and instabil                            | ity of the        | switch        | ning     | TFT.106  |

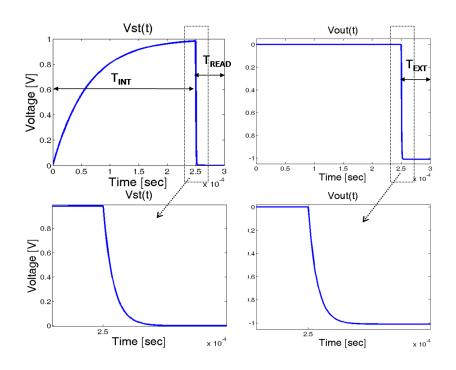

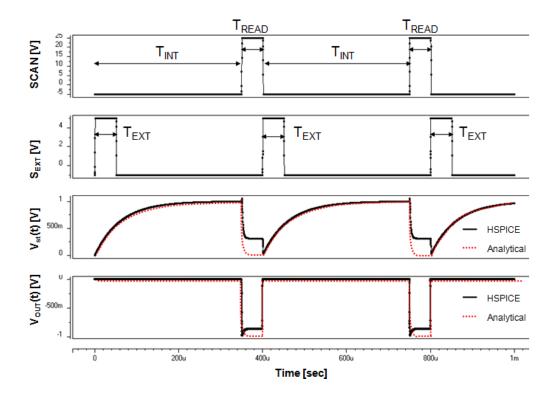

|    |                |       | Transient respon    | se and dy                               | ynamic ran                              | ge of fabr        | ricated       | PPS      | 110      |

|    | 6.5            | .3    | Comparison bety     | veen exp                                | erimental a                             | nd simula         | ated res      | sults    | 111      |

|    | 6.6            | Coı   | nclusion            |                                         |                                         |                   |               |          | 113      |

|    |                |       |                     |                                         |                                         |                   |               |          |          |

| 7. | -50 un         | n nix | el pitch 128 x 12   | 28 a-Si:                                | H TFT PI                                | 'S Imag           | er            | <b>.</b> | 116      |

|    | 7.1    | Introduction                                                          |

|----|--------|-----------------------------------------------------------------------|

|    | 7.2    | Fabrication of 50 µm pixel pitch 128 x 128 a-Si:H TFT PPS array 117   |

|    | 7.3    | Electrical characteristics of the fabricated switch a-Si:H TFTs 123   |

|    | 7.4    | Organic photodiode structure and its expected opto-electronic         |

|    |        | properties                                                            |

|    | 7.5    | Integration of the organic photodiode with the a-Si:H TFT PPS array . |

|    |        |                                                                       |

|    | 7.6    | Expected opto-electronic properties of the fabricated 128 x 128 PPS   |

|    |        | imager                                                                |

|    | 7.7    | Conclusion                                                            |

| 8. | Conc   | lusions and Future Work134                                            |

|    | 8.1    | Conclusions                                                           |

|    | 8.2    | Recommendations for future work                                       |

| Аp | pendix | -List of Publications138                                              |

# **List of Tables**

| Table 2.1 Extracted parameters of fork TFT; case (1) where source is applied on U-                 |

|----------------------------------------------------------------------------------------------------|

| shaped electrode and case (2) where source is applied on rod-shaped electrode.                     |

| Geometrical factor a) $W_{eff0}/L$ b) $f_{g1}$ and c) $f_{g2}$ is used to extract the parameter 25 |

| Table 3.1 The specification of the LWL system for different write modes                            |

| Table 3.2 Summary of the extracted TFT ( $W/L = 50/5$ ) parameters                                 |

| Table 3.3 Properties of BK-7 optical material                                                      |

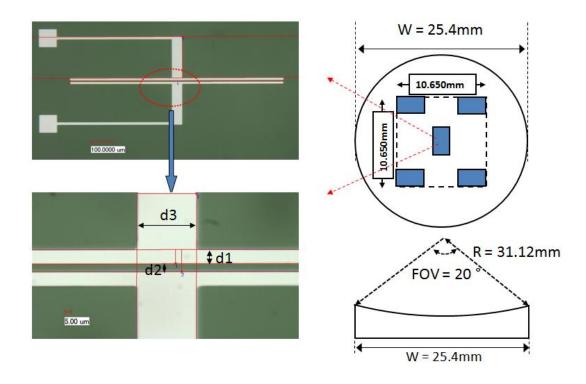

| Table 3.4 Summarized discrepancy of dimension between measured structure (d1,d2, and               |

| d3) and its electronic design. 54                                                                  |

| Table 3.5 Specification of our proposed LWL system for a substrate with FOV of 120°                |

| (design III)57                                                                                     |

| Table 4.1 Properties of BK-7 optical materials                                                     |

| Table 4.2 The feasibility of photoresist spin-coating on various substrates; * used in this        |

| work; ** alternative resist coating method needs to be investigated 65                             |

| Table 4.3 Variation of the extracted parameters for all fabricated a-Si:H TFTs                     |

| Table 5.1 Extracted electrical parameters of a-Si:H TFT ( $W/L = 50/10$ ) fabricated on a          |

| spherical surface                                                                                  |

| Table 7.1 Descriptions of the eight photo-masks                                                    |

| Table 7.2 Extracted electrical parameters of the fabricated switching TFT ( $W/L = 40/5$ )         |

| for both grounded and floated light-shield metal layer                                             |

# **List of Figures**

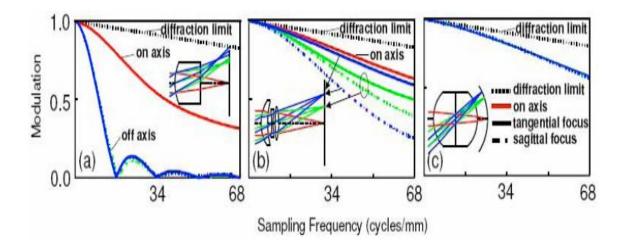

| Figure 1.1 Modulation transfer functions (MTFs) of (a) a simple plano-convex lens with               |

|------------------------------------------------------------------------------------------------------|

| planar FPA, (b) Cooke triplet lens with planar FPA, (c) a ball-shaped lens with                      |

| curved FPA (Adopt from [13])                                                                         |

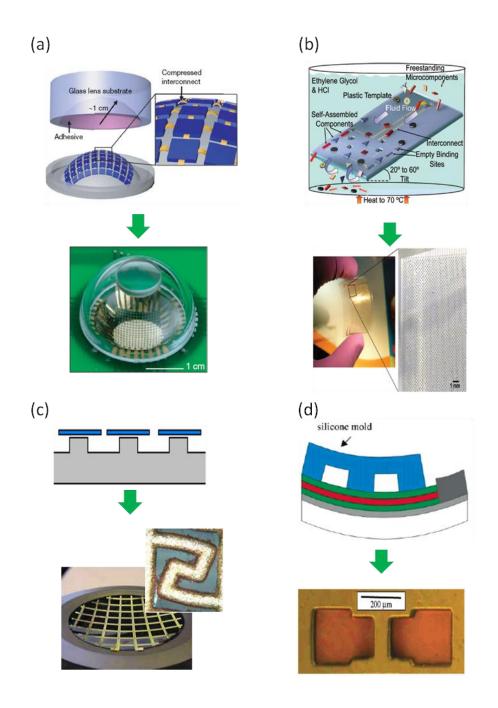

| Figure 1.2 Various approaches proposed to realize functional devices on non-planar                   |

| surfaces: (a) transfer-based fabrication [15] (b) Self-assembly [20] (c)                             |

| Interconnection of devices tiles [21] (d) Contact patterning method [24] 5                           |

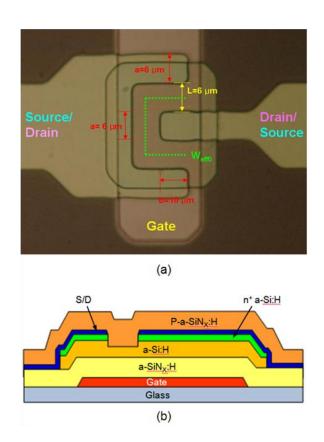

| Figure 2.1 The fork TFT: (a) optical photograph of top view and (b) schematic of cross-              |

| sectional view                                                                                       |

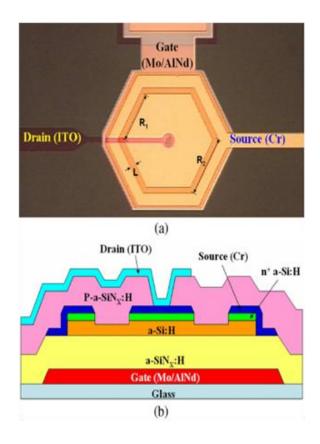

| Figure 2.2 The HEX TFT: (a) optical photograph of top view and (b) schematic of cross-               |

| section view                                                                                         |

| Figure 2.3 Transfer characteristics of fork a-Si:H TFT for various $V_{DS}$                          |

| Figure 2.4 Output characteristics of fork a-Si:H TFT for various $V_{GS}$                            |

| Figure 2.5 The schematic top views of depletion regions in fork a-Si:H TFT; case (1)                 |

| where source is applied on U-shaped electrode and case (2) where source is                           |

| applied on rod-shaped electrode                                                                      |

| Figure 2.6 Measured (open symbol) and calculated (closed symbol) output characteristics              |

| of fork a-Si:H TFTs. (a) $a=6~\mu m$ and $b$ =10 $\mu m.$ (b) $a=6~\mu m$ and $b=6~\mu m.$ . 21      |

| Figure 2.7 Transfer characteristics of fork a-Si:H TFT. Solid lines used for extraction of           |

| the threshold voltage and mobility are also shown (10-90% method used) 24                            |

| Figure 2.8 Source-drain bias connection dependence of threshold voltage shift ( $\Delta V_{th}$ ) of |

| fork TFT for various stress current densities; (dash-line) linear fitting results 27                 |

| Figure 2.9 The photographs of multiple HEX-TFTs (e.g. HEX-4 and HEX-8 TFTs).                         |

| Dashed lines show the cutting lines to separate and measure individual HEX-                          |

| TFT unit                                                                                             |

| Figure 2.10 The recovery of the CTS-induced stress after thermal annealing. The transfer               |

|--------------------------------------------------------------------------------------------------------|

| characteristics are restored to the initial state after the annealing. The inset                       |

| shows the threshold voltage shift as a function of stress time. Squares and circles                    |

| represent the CTS results of the initial and annealed TFTs, respectively 29                            |

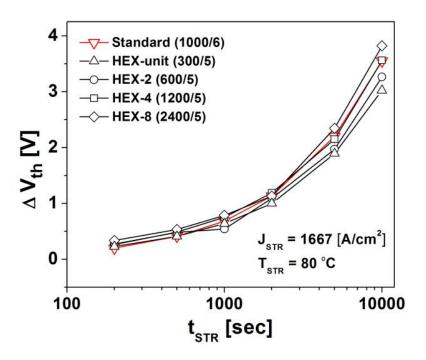

| Figure 2.11 Threshold voltage shifts of the single HEXT-TFT, HEX-2, HEX-4, and                         |

| HEX-8 as a function of stress time in a semi-log scale. The result of standard                         |

| TFT is shown for comparison                                                                            |

| Figure 2.12 CTS-induced threshold voltage shift as a function of integer N of HEX- $2^N$ . 32          |

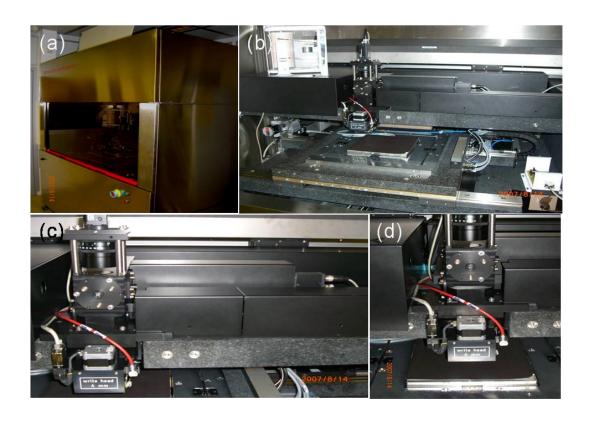

| Figure 3.1 Whole view of DWL 4000 System used in this work                                             |

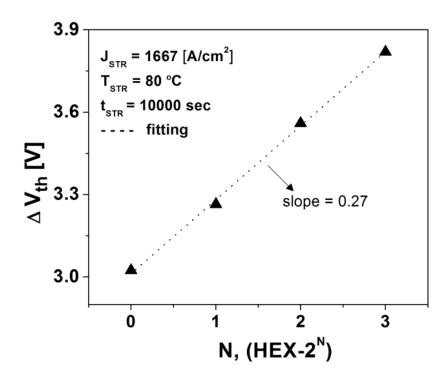

| Figure 3.2 The illustration of the optical design and writing strategy. The substrate moves            |

| in the x-y plane during the exposure (Adopt from [8])                                                  |

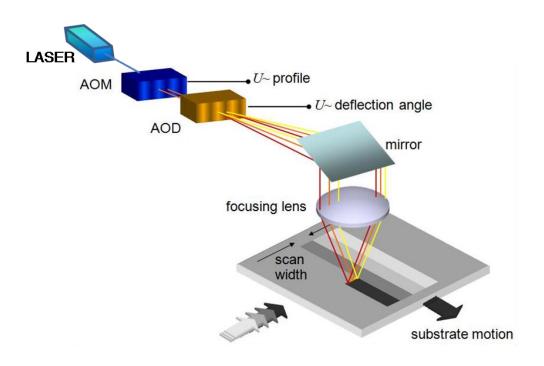

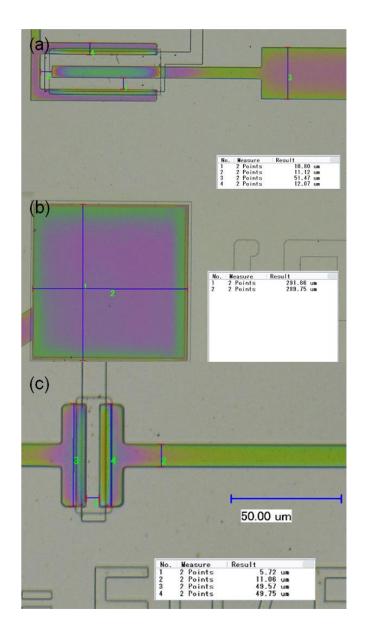

| Figure 3.3 (a) Optical microscope images of fabricated a-Si:H TFT ( $W/L = 50/5$ ) using               |

| LWL (b) A schematic of cross section view (c) Alignment marks (resist not                              |

| removed for a clear picture) (d) Example of alignment mark used for                                    |

| calculation of alignment error                                                                         |

| Figure 3.4 Examples of exposed structures using LWL after photoresist development: (a)                 |

| interdigitated TFT ( $W/L = 200/10$ ), (b) contact pad, and (c) normal TFT ( $W/L$                     |

| =50/5)                                                                                                 |

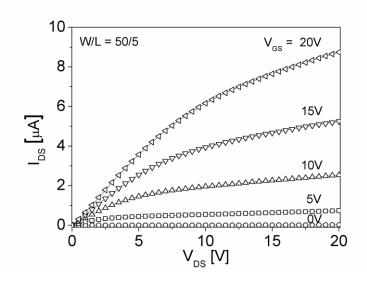

| Figure 3.5 Output characteristics of fabricated a-Si:H TFT using LWL process ( $W/L$ =                 |

| 50/5)                                                                                                  |

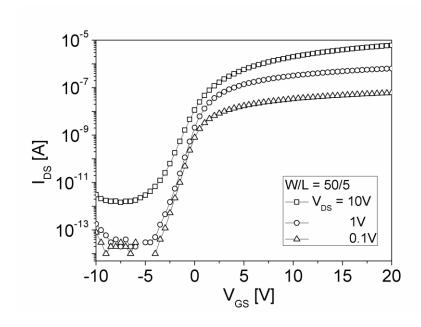

| Figure 3.6 Transfer characteristics of fabricated a-Si:H TFT using LWL process in                      |

| saturation regime. Inset shows the result in a log scale                                               |

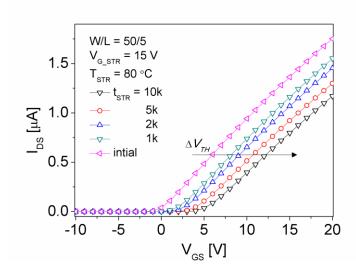

| Figure 3.7 The change of the fabricated TFT transfer characteristics at $V_{DS} = 1$ V for $t_{STR} =$ |

| 10 <sup>4</sup> sec under BTS condition                                                                |

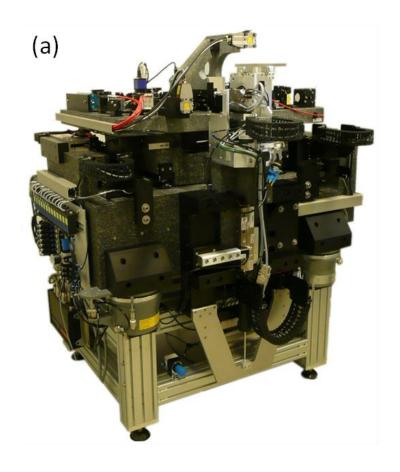

| Figure 3.8 The modified Heidelberg laser write lithography system (a) general view of                  |

| LWL system (b) main functional components (c) optics plate (d) write head &                            |

| substrate table                                                                                        |

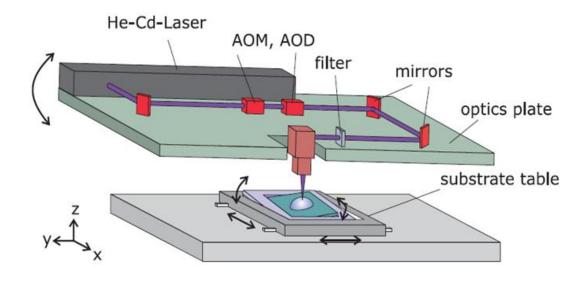

| Figure 3.9 Illustration of a main function part of the modified LWL systems [10] 46                    |

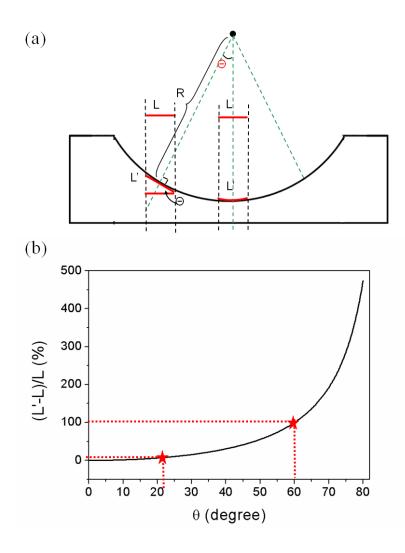

| Figure 3.10 (a) Schematics of a customized substrate (b) Expected extent of the                        |

| dimensional deformation vs. the degree; for FOV of 33.5 °, ~2 %; for FOV of                            |

| 40.5°, ~ 6%; and for <i>FOV</i> of 120°, ~100%                                                         |

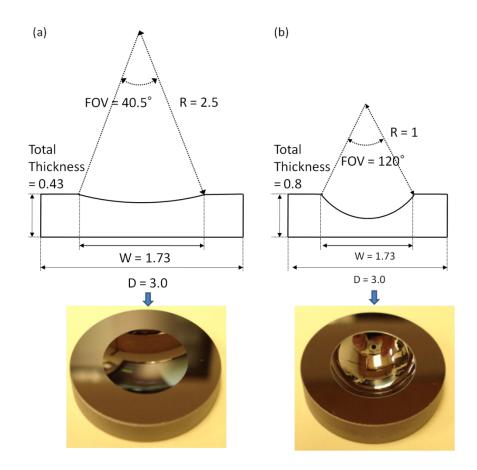

| Figure 3.11 Customized BK-7 concave glass substrates with $FOV$ of (a) 40.5 ° and (b)         |

|-----------------------------------------------------------------------------------------------|

| $120^\circ;2000\mbox{\normalfont\AA}$ Cr was deposited for a clear picture. Unit is [cm]      |

| Figure 3.12 Stitching problem after photoresist development caused structure variation.52     |

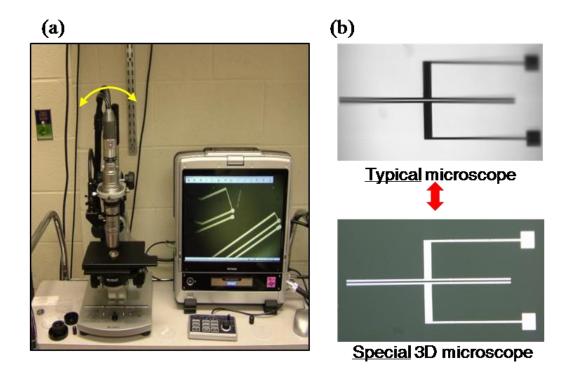

| Figure 3.13 (a) Photography of Keyence VHX-600 microscope (b) comparison of 3D                |

| microscope to typical microscope providing blurred image due to losing focus.                 |

| 53                                                                                            |

| Figure 3.14 Pictures of test structure and its location over the curved surface; illustration |

| of top and cross section view of the substrate                                                |

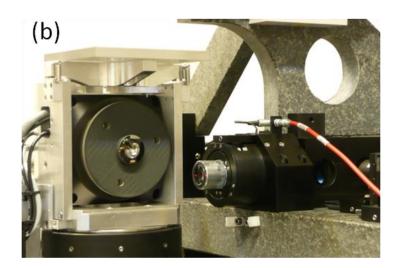

| Figure 3.15 (a) System overview of our proposed LWL system for $FOV$ up to 120 $^{\circ}$ (b) |

| Substrate chuck and write head 56                                                             |

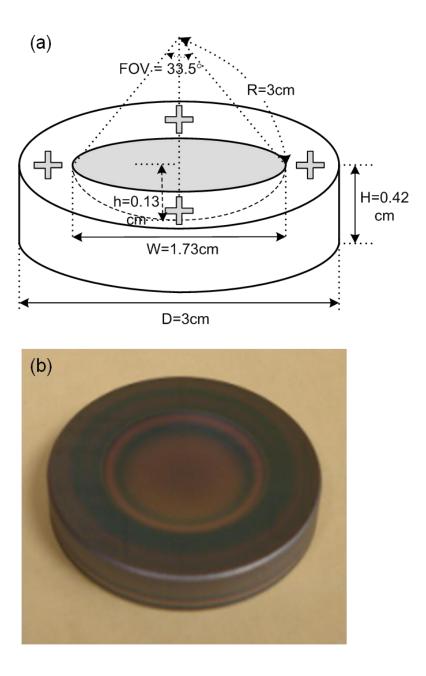

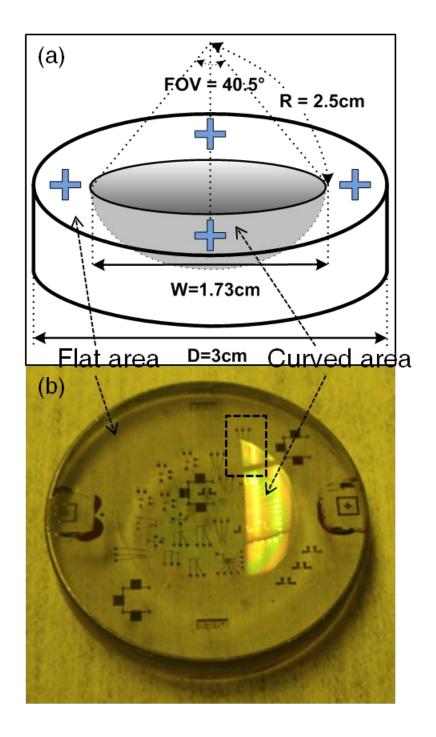

| Figure 4.1 (a) an illustration of the customized concave glass substrate; crosses represent   |

| alignment marks on the flat area. (b) a picture of customized substrate coated                |

| with thin-film materials. 62                                                                  |

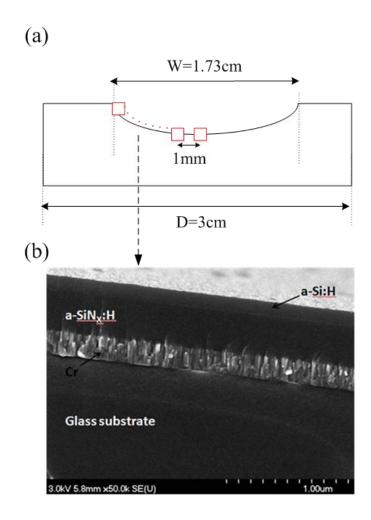

| Figure 4.2 (a) Illustration of the method used to get cross-sectional images of the curved    |

| surface. (b) Scanning Electronic Microscope (SEM) image captured in the                       |

| middle of curved area                                                                         |

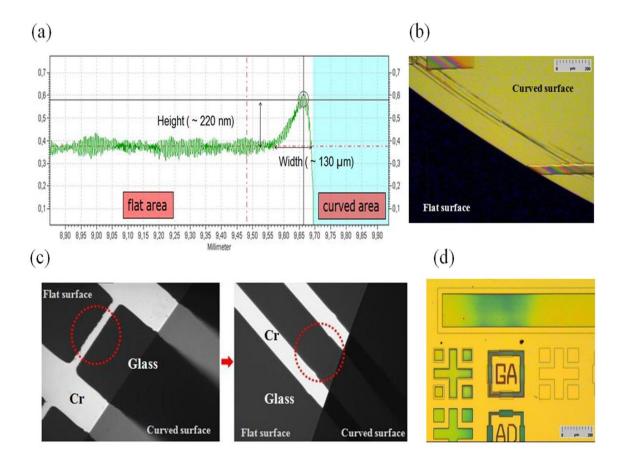

| Figure 4.3 (a) Thickness profile of the spin-coated photoresist over the transition area.     |

| Measured height and width of the edge-bead shown. (b) Distortion and                          |

| additional connection of patterns due to edge-bead formation over the transition              |

| area between a curved and flat area. (c) Additional connection (red circle area)              |

| formed by edge-bead of the photoresist was removed by the local double                        |

| exposure (d) Optical microscope image of the alignment marks after Gate                       |

| electrode to Active island layer exposure; Photoresist was not removed to                     |

| capture clear images                                                                          |

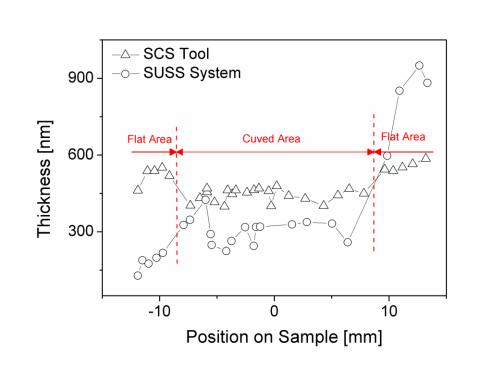

| Figure 4.4 Thickness distribution of spray-coated photoresist (AZ1505) across the             |

| substrate III                                                                                 |

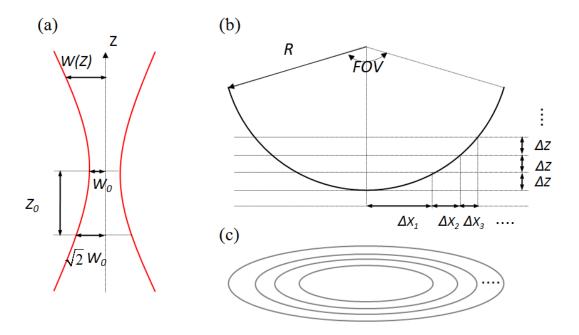

| Figure 4.5 (a) Gaussian beam width $w(z)$ as a function of the axial distance $z$ . (b)       |

| Geometry of circular subfields for spherical surface. (c) Illustration of the                 |

| decomposition of design into the subfields                                                    |

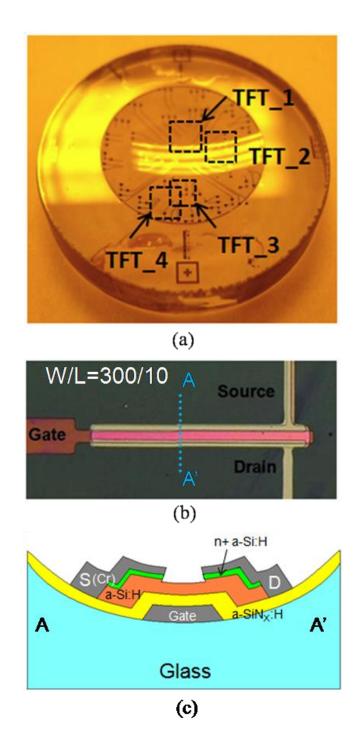

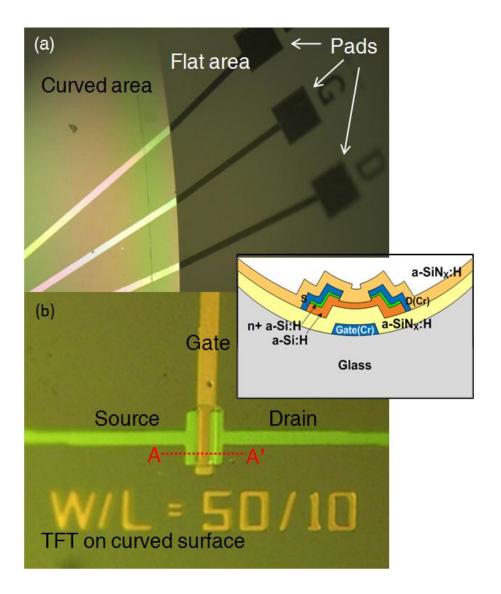

| Figure 4.6 (a) Photograph of the fabricated substrate. Dashed squares show the measured       |

| a-Si:H TFTs. (b) Optical microscope image of the fabricated a-Si:H TFT                        |

| (W/L=300/10) from the edge of curved surface. (c) Schematic of cross section                                        |

|---------------------------------------------------------------------------------------------------------------------|

| view of fabricated TFT. The substrate curvature is exaggerated                                                      |

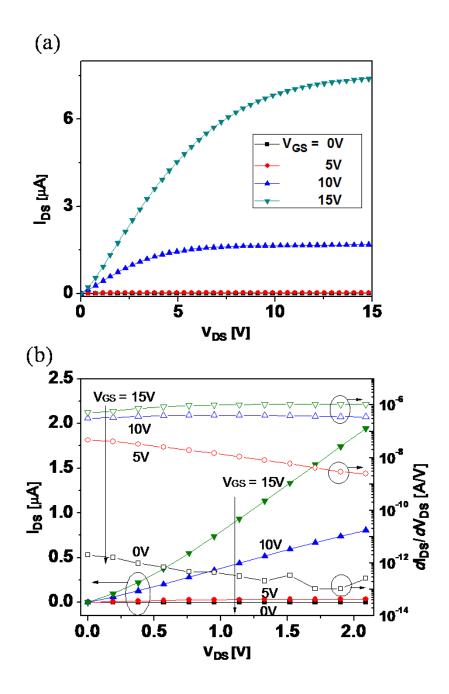

| Figure 4.7 Electrical properties of the fabricated a-Si:H TFT (W/L=300/10, 'TFT_2') or                              |

| a curved surface. (a) Output characteristics. (b) Output characteristics and outpu                                  |

| conductance in low $V_{DS}$ bias region (0 ~ 2V)                                                                    |

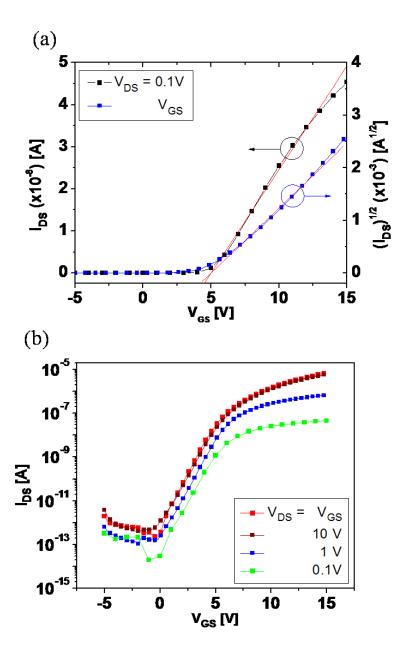

| Figure 4.8 Electrical properties of the fabricated a-Si:H TFT (W/L=300/10, 'TFT_2') or                              |

| a curved surface. (a) Transfer characteristics with fitting lines used for extraction                               |

| of threshold voltage and mobility. (b) Transfer characteristics in a semi-log scale                                 |

| 75                                                                                                                  |

| Figure 5.1(a) Illustration of the customized BK-7 concave glass substrate; crosses                                  |

| represent alignment marks placed on the flat area. (b) Photograph of the                                            |

| fabricated devices and circuits on the substrate. A dashed-box indicates the                                        |

| location of the a-Si:H TFT studied in this chapter                                                                  |

| Figure 5.2 Optical microscope image of one of the fabricated a-Si:H TFTs. (a) The                                   |

| contact pads are placed on the flat area, and metal interconnect lines over the                                     |

| transition area leading to the fabricated device can be seen. (b) Enlarged image                                    |

| of the a-Si:H TFT ( $W/L = 50/10$ ). The blurred image is induced by substrate                                      |

| curvature. The inset illustrates a cross-section view of the fabricated TFT 85                                      |

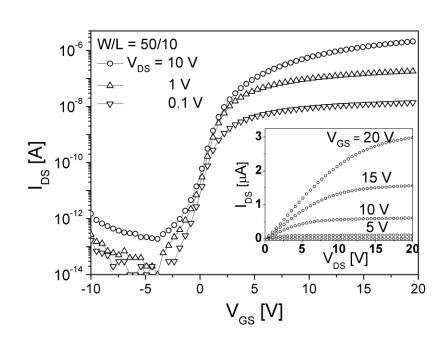

| Figure 5.3 Transfer and output characteristics of the fabricated a-Si:H TFT ( $W/L = 50/10$ )                       |

| for various $V_{DS}$ (= 0.1 V, 1 V, and 10 V) and $V_{GS}$ =(0 V, 5 V, 10 V, 15 V, 20 V)                            |

| respectively87                                                                                                      |

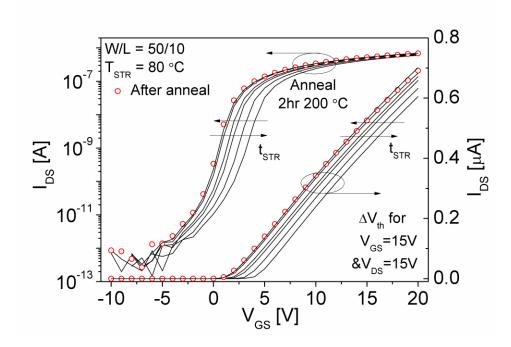

| Figure 5.4 Evolution of the transfer characteristics of the a-Si:H TFT fabricated on a                              |

| spherical surface for BTS ( $V_{GS} = 15 \text{ V}$ and $V_{DS} = 15 \text{ V}$ ) and its recovery to the           |

| initial state after thermal annealing                                                                               |

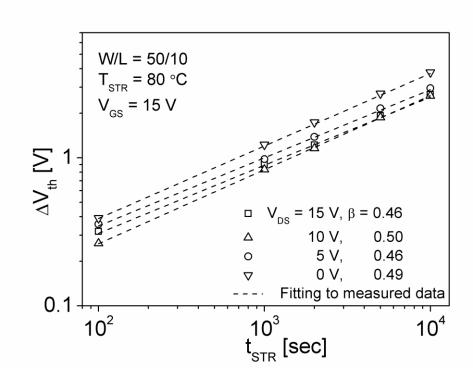

| Figure 5.5 Threshold voltage shift $(\Delta V_{th})$ as a function of the stress time $(t_{STR})$ for               |

| different stress bias of $V_{DS}$ bias; $V_{GS}$ was kept to 15 V. The stretched-exponentia                         |

| exponent $(\beta)$ is extracted and summarized for each $V_{DS}$ bias. Dashed lines are the                         |

| linear fit to the experimental data                                                                                 |

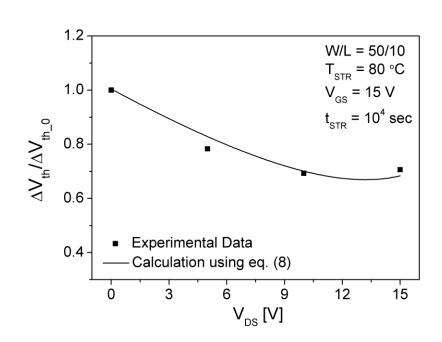

| Figure 5.6 $\Delta V_{th}$ normalized to its maximum value ( $\Delta V_{th\_0}$ at $V_{DS} = 0$ V) as a function of |

| $V_{DS}$ bias; experimental data from Fig. 5.5 at $t_{STR} = 10^4$ sec. The solid line shows                        |

| the calculation result of eq. (8) for the same $V_{DS}$ range (0 V ~ 15 V) using                                                   |

|------------------------------------------------------------------------------------------------------------------------------------|

| MATLAB 90                                                                                                                          |

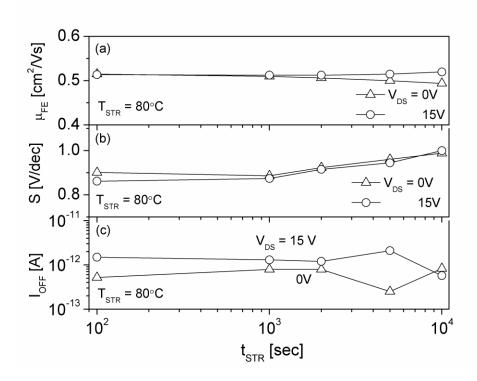

| Figure 5.7 (a) $\mu_{FE}$ (b) S and (c) $I_{OFF}$ as a function of stress time ( $t_{STR}$ ) of the a-Si:H TFT                     |

| (W/L = 50/10) fabricated on a spherical surface for BTS conditions of both i)                                                      |

| $V_{GS} = 15 \text{ V}$ , $V_{DS} = 0 \text{ V}$ and ii) $V_{GS} = 15 \text{ V}$ , $V_{DS} = 15 \text{ V}$ BTS conditions. Symbols |

| represent the measured data and lines are for aid of eye                                                                           |

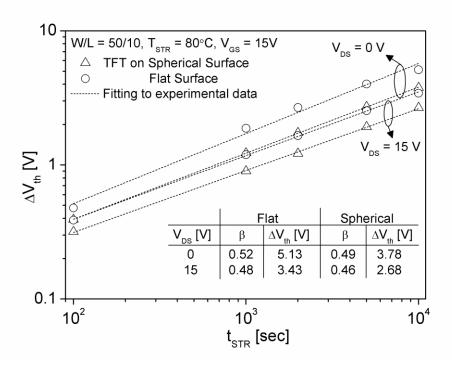

| Figure 5.8 $\Delta V_{th}$ versus stress time ( $t_{STR}$ ) of the a-Si:H TFTs fabricated on both flat and                         |

| spherical surfaces for different BTS conditions of both i) $V_{GS} = 15 \text{ V}$ , $V_{DS} = 0 \text{ V}$                        |

| and ii) $V_{GS} = 15$ V, $V_{DS} = 15$ V. The corresponding final $\Delta V_{th}$ and stretched-                                   |

| exponential exponent $(\beta)$ are summarized in the inset. Symbols represent the                                                  |

| measured data, and dashed lines are the linear fit to the experimental data 93                                                     |

| Figure 6.1 Schematic of passive pixel sensor circuit                                                                               |

| Figure 6.2 The circuit diagram of PPS connected to the external charge amplifier. The                                              |

| gray box indicates the organic photodiode which is not integrated in this                                                          |

| experiment98                                                                                                                       |

| Figure 6.3 Calculation results of analytical solution by MATLAB                                                                    |

| Figure 6.4 HSPICE simulation results                                                                                               |

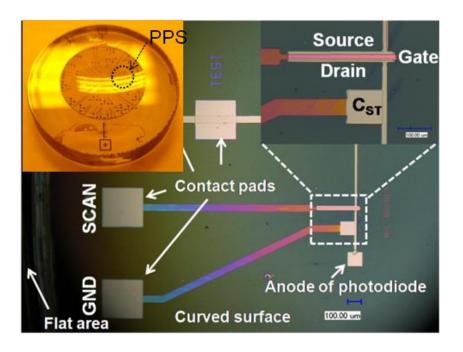

| Figure 6.5 Photograph of the fabricated substrate and optical micrograph of the pixel                                              |

| sensor circuit at the edge of the curved surface. (Inset) Detailed micrograph of                                                   |

| the a-Si:H TFT and $C_{ST}$ . A dashed-circle indicates a location of the PPS studied                                              |

| in this chapter                                                                                                                    |

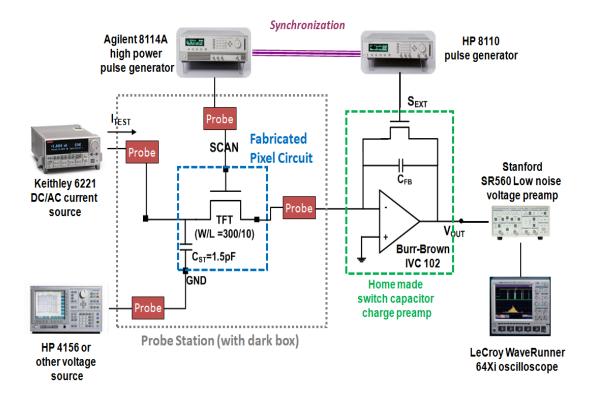

| Figure 6.6 The experimental set-up for PPS AC testing                                                                              |

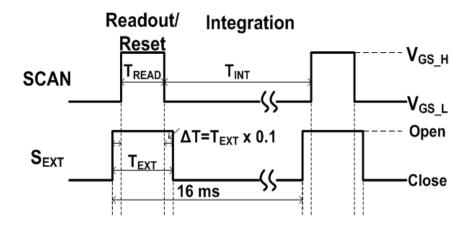

| Figure 6.7 Schematic drawing of the driving waveforms to SCAN and $S_{\text{EXT}}$                                                 |

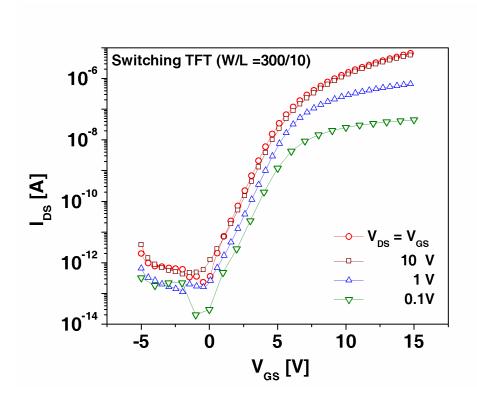

| Figure 6.8 Transfer characteristics of the switching TFT for various $V_{DS}$                                                      |

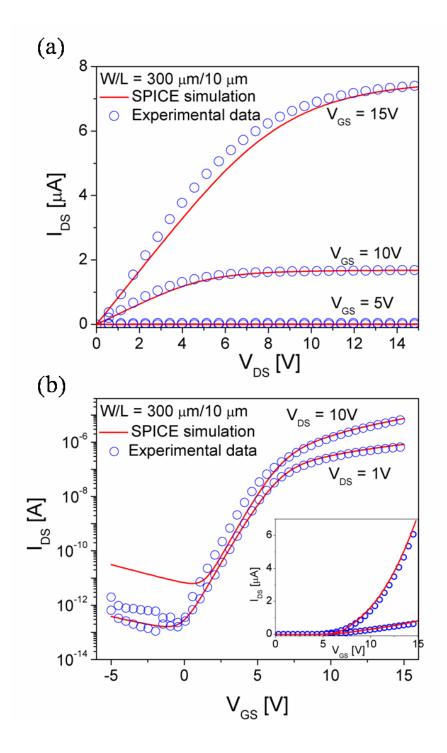

| Figure 6.9 Measured and simulated (a) output and (b) transfer characteristics of the                                               |

| switching TFT. (Inset) transfer characteristics in linear scale                                                                    |

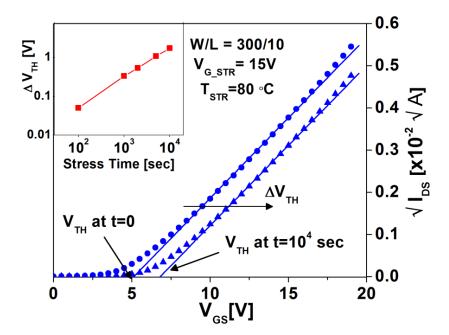

| Figure 6.10 The change of TFT switch transfer characteristics at saturation operation                                              |

| regime for BTS ( $V_{G\_STR} = 15$ V, $V_{DS} = 0$ V, $T_{STR} = 80$ °C. (Inset) $\Delta V_{TH}$ as a                              |

| function of stress time                                                                                                            |

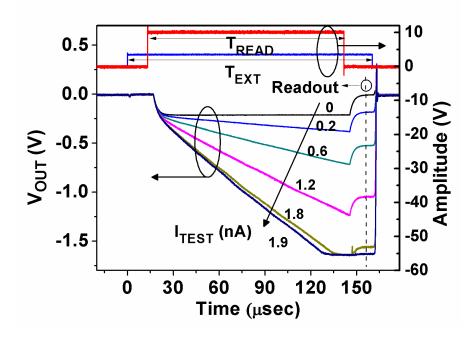

| Figure 6.11 Oscilloscope traces of $V_{OUT}$ for different $I_{TEST}$ 111                                                          |

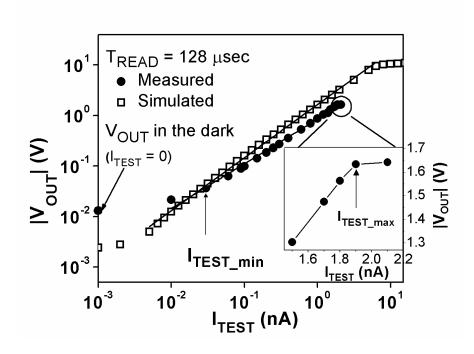

| Figure 6.12 Solid circles show the linearity plot of the measured $V_{OUT}$ vs. $I_{TEST}$ by                           |

|-------------------------------------------------------------------------------------------------------------------------|

| sampling $V_{OUT}$ at 158 $\mu s.$ (Inset) Non-linearity is shown at high values of $I_{TEST}$                          |

| Squares show the simulated results                                                                                      |

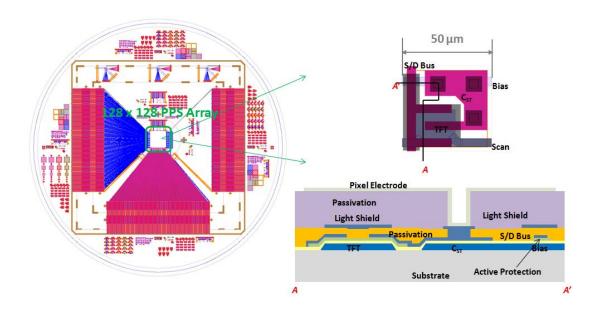

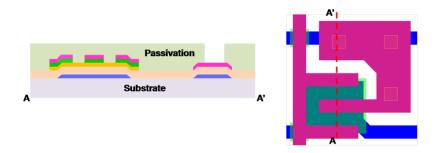

| Figure 7.1 Whole view of the mask design (left) and enlarged single pixel from 128 x 128                                |

| PPS array with its cross section view (right)                                                                           |

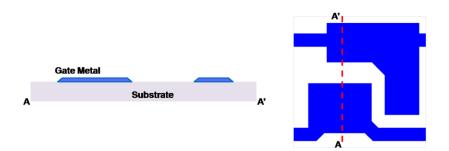

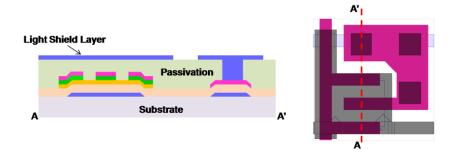

| Figure 7.2 Mask #1 (Gate Metallization): Sputtered Chromium, 2000 Å, and wet-etch                                       |

| method (CR-14) used                                                                                                     |

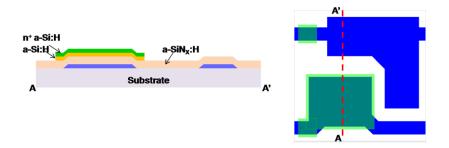

| Figure 7.3 Mask #2 (Active Island Formation): Tri-layer of a-SiN $_{\rm x}$ (4000 Å) / a-Si:H                           |

| (1700 Å) / $n^+$ a-Si:H (700Å) by PECVD, and active island formation using RIE                                          |

| $(SF_6/O_2)$                                                                                                            |

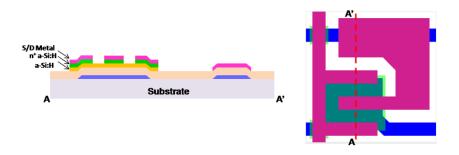

| Figure 7.4 Mask #4 (Source/Drain Metallization): Sputtered Cr (2000 Å), and back-                                       |

| channel etch using RIE (SF <sub>6</sub> /O <sub>2</sub> ).                                                              |

| Figure 7.5 Mask #5 (Contact Via): Passivation using a-SiN <sub>X</sub> :H (4000 Å) by PECVD, and                        |

| via definition by RIE (CF <sub>4</sub> /O <sub>2</sub> )                                                                |

| Figure 7.6 Mask #6 (Light Shield Metallization): Sputtered Cr (2000 Å), and wet-etch                                    |

| method (CR-14) used                                                                                                     |

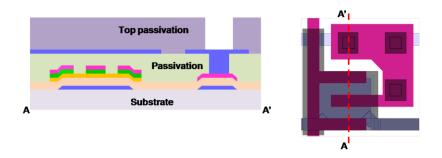

| Figure 7.7 Mask #7 (Shield Layer Via): Top passivation using a-SiN $_{\rm X}$ :H (6000 Å) by                            |

| PECVD, and via definition by RIE (CF <sub>4</sub> /O <sub>2</sub> ) used                                                |

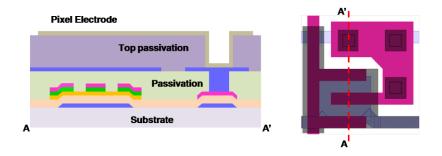

| Figure 7.8 Mask #8 (Pixel Electrode Patterning): Sputtered Cr (1500 Å), and wet-etch                                    |

| method (CR-14) used                                                                                                     |

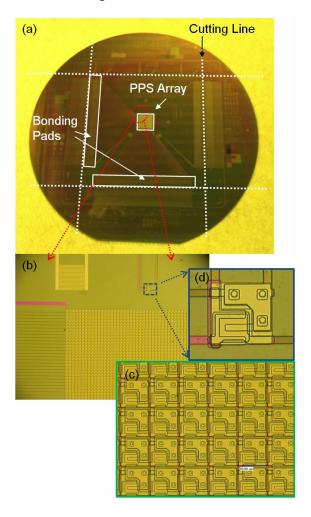

| Figure 7.9 (a) Fabricated 128x128 PPS array on a 4" Silicon wafer. White dash-lines                                     |

| indicate the cutting line for dicing (b) Photograph from the upper left corner                                          |

| near the PPS array (from Red circle) (c) Enlarged photo of the part of the PPS                                          |

| array (d) Photograph of a PCM device                                                                                    |

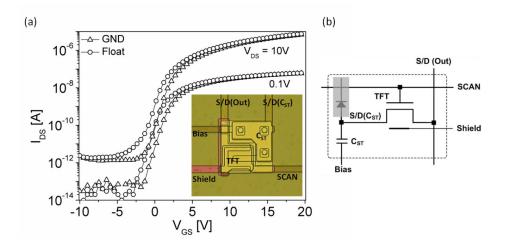

| Figure 7.10 (a) Transfer characteristics of the fabricated switching TFT ( $W/L = 40/5$ ) in                            |

| semi-log scale. Inset shows the fabricated PCM device (b) Schematic of the                                              |

| PCM device; OPD indicated by gray-box is not integrated                                                                 |

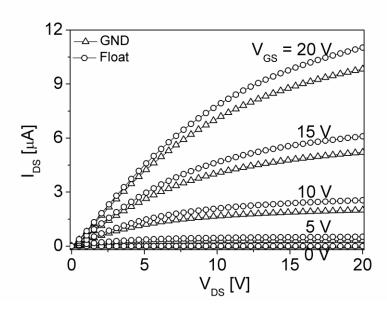

| Figure 7.11 Output characteristics of the fabricated switching TFT ( $W/L = 40/5$ ) for                                 |

| various $V_{GS}$ bias                                                                                                   |

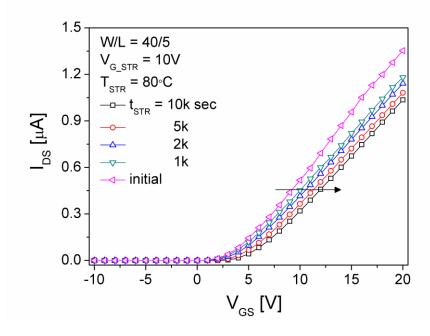

| Figure 7.12 Evolution of the transfer characteristics of the fabricated switching TFT in                                |

| linear operation regime for BTS ( $V_{G,STR} = 10 \text{ V}$ , $V_{DS} = 0 \text{ V}$ , $T_{STR} = 80 \text{ °C}$ ) 125 |

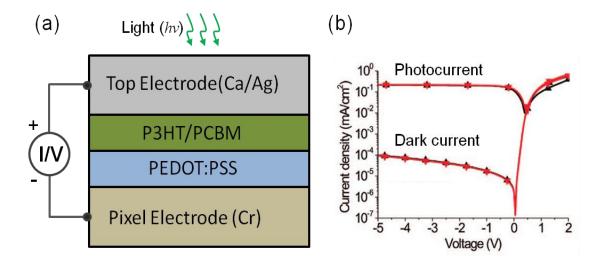

| Figure | 7.13 (a) The layer stack of a bulk heterojunction organic photodiode (OPD) | (b) |

|--------|----------------------------------------------------------------------------|-----|

|        | Expected I-V characteristics of OPD to be fabricated using spray-coat      | ing |

|        | (adopted from [10])                                                        | 127 |

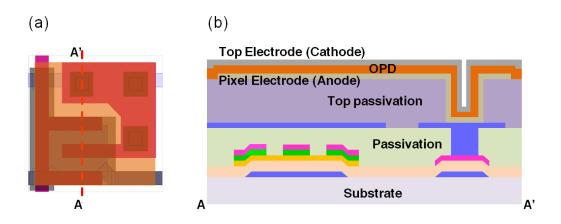

| Figure | 7.14 Illustration of top (a) and cross section (b) view of a pixel after O | PD  |

|        | integration1                                                               | 128 |

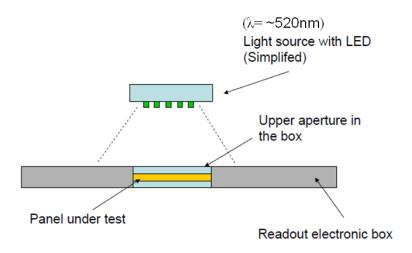

| Figure | 7.15 A schematic of the experimental setup for measurements                | 130 |

## **Chapter 1**

## Introduction

#### 1.1 Motivation/Overview

Recently there has been growing interest in solid-state image sensors due to enormous demands for mobile-imaging, digital and video cameras, surveillance, and medical imaging applications. Charge-coupled devices (CCDs), invented 1969, dominated the market due to a great quality of images. In addition to a high cost, the CCDs have a major drawback: incompatibility with the complementary metal oxide semiconductor (CMOS) technology [1]. So the recent advances of CMOS processing drive the development of image sensor in combination with the CMOS technologies. Today's CMOS image sensor is based on the work done from the mid 1980s at VLSI Vision Ltd. and the Jet Propulsion Lab (JPL) [1]. Until the early 1990s, the passive pixel sensor (PPS) was the first choice due to the feature size limitation of CMOS technologies [2]. In mid-1990s active pixel sensor (APS) technology became mature, and APS architecture becomes the key of CMOS image sensor with a high speed, less image lag, and a low power-consumption in comparison to CCDs [3]. Today this technology has been adopted in most of commercial products requiring compact and light-weight image sensors.

For a large area application such as security and medical imaging, the hydrogenated amorphous silicon (a-Si:H) thin-film transistor (TFT) flat panel imagers based on a passive pixel sensor (PPS) concept have been used [4, 5]. Indeed a-Si:H TFT is a well proven technology for fabricating electronics over a large area that is widely used for flat panel displays and x-ray

sensors [5-7]. Although it is possible to realize a large area high performance imager by tiling a number of CCDs and/or CMOS image sensors [8], the cost benefit of a large area a-Si:H TFT fabrication process makes a-Si:H TFT flat panel imager much more attractive than other approaches. So far, all the current state-of-the-art image sensor technologies have been developed on flat surfaces because CMOS and TFT technology are developed either for a rigid silicon wafer or glass substrate.

Image sensors on flat surfaces have a planar focal plane array (FPA); FPA is an array of light-sensing pixels at the area where light is focused (focal plane). The planar FPA induces optical aberrations, which are deviations of the performance of an optical system from the prediction of optics [9], consequently leading to a distorted and blurred image compared to an original image. To correct this problem, additional optical elements and shaped lenses are necessary, resulting in the complicated and expensive optical system. Recently, there has been increasing research activities on unique advantages of image sensor to be fabricated on a spherical surface: a wide field-of-view (FOV), low optical aberrations with less optical components in the system, compact, and light weight [10-13], resulting in a lower cost. The low optical aberrations are attributed to that the surfaces of a spherical imager as well as ball-shaped lens are spherical and symmetric to the center of an optical system. This allows that all points on the imager are on-axis points without additional lenses, consequently contributing to simplify the optical system [14].

Figure 1.1 compares the performance of three camera systems that consists of different shaped-lenses and curved or planar FPAs in modulation-transfer-function (MTF) plots. MTF represents how accurately the lens transfers contrast of the object to the image produced by the lens; basically, the higher MTF number, the more accurate image. In Figure 1.1 (a-c), MTFs of diffraction limited systems (black dotted lines), image points on axis (red), tangential image point (solid lines) at 0.4 field (green) and 0.7 field (blue) and satittal image points (dashed dots) at both 0.4 and 0.7 fields are shown [13].

Figure 1.1 Modulation transfer functions (MTFs) of (a) a simple plano-convex lens with planar FPA, (b) Cooke triplet lens with planar FPA, (c) a ball-shaped lens with curved FPA (Adopt from [13]).

Aforementioned advantages demand the implementation of electronic and optoelectronic systems on non-planar or hemispherical surfaces. As illustrated in Figure 1.2, therefore, various approaches have been proposed to realize functional devices on those surfaces: a) transfer-based fabrications, b) self-assembly, c) interconnection of device tiles, and d) contact patterning methods.

- a. Transfer-based fabrication: i) devices are fabricated on flexible substrates and then transferred by deformation onto curved substrates [15, 16]. ii) contact-transfer printing has been applied to transfer only functional devices, not the entire flexible substrate [17].

- b. Self-assembly: functional devices are fabricated and prepared as individual components. Solder-based or complementary shape recognition assembly with the aid of capillary and/or gravitational force is used to integrate the components onto flexible substrates [18-20].

- c. Interconnection of device tiles: standard fabrication process is conducted on silicon wafer. The processed wafer is diced by dry-etching on the back side, and the formed "tiles" are bridged by metal leads. Finally the wafer of the tiles is curved using an elastomeric mold [21].

- d. Contact patterning method: soft-lithography is a representative example. First step is to build patterned stamps and molds as pattern transfer elements. A printing method with the prepared stamps/molds is used to form patterns on curved surfaces. It has advantages of being adaptable to substrate shape and generating conformal contact with the contour of curved substrates [22-24].

Although the proposed methods have demonstrated feasibility of the fabrication of functional devices on non-planar surfaces, they are not desirable to realize complex device structures and circuits for high-resolution pixel arrays with various components. These strategies are limited by the following: difficulty with the preparation of transferable functional devices or individual components (a, b) due to the limitation of process temperature and strain associated with local deformation; lack of scaling capability (a, c, d); poor registration accuracy and layer-to-layer alignment accuracy (a, d); difficulty with interconnection to readout electronics (a, b). The pixel circuit's dimensional changes with the curvature should be considered in the fabrication of the hemispherical image.

Figure 1.2 Various approaches proposed to realize functional devices on non-planar surfaces: (a) transfer-based fabrication [15] (b) Self-assembly [20] (c) Interconnection of devices tiles [21] (d) Contact patterning method [24].

The standard photolithography obviously cannot be used for non-planar surfaces because of the substrate curvature. To circumvent aforementioned difficulties and limitations, we need a direct fabrication method based on non-contact patterning. The maskless laser-write lithography (LWL) can be an alternative approach; the LWL is a direct fabrication method free from the stress and/or deformation issues which are inevitably involved in the transfer-based fabrication; the LWL can provide a submicron feature size with a very accurate registration and alignment capability. With extensive modification, the capability of LWL process on curved substrates has been demonstrated at a single-level mask step [25, 26], and can be extended for multi-level alignment and process. Therefore, it can be a very attractive and promising approach to fabricate high-performance functional devices and circuits on a non-planar surface.

### 1.2 Organization of Dissertation

This dissertation commences in **chapter 2** by introducing and discussing electrical properties and instability of advanced a-Si:H TFT structures for sensor application. The asymmetric electrical properties and instability of fork TFTs are investigated in depth. The instability of single and multiple HEX-TFTs is discussed, and their relationship is established. In **chapter 3**, we demonstrate the feasibility of using the LWL system with accurate level-to-level alignment in the fabrication of a-Si:H TFTs on a planar surface. Furthermore we describe what modification should be made for the expansion of the proposed LWL method into non-planar fabrication processing. We evaluate the modified LWL system in structuring on a curved surface. In **chapter 4**, we successfully demonstrate the fabrication of a-Si:H TFTs on a curved surface. The extensively modified LWL system is used, and the fabrication steps are described in detail. The fabricated TFTs show good enough electrical performance for application such as high-resolution and large-array devices. In **chapter 5**, electrical stability of a-Si:H TFTs fabricated on a curved

surface with enhanced field of view is studied in depth under various and prolonged biastemperature stress. Furthermore we compare the obtained results with a-Si:H TFT fabricated on a flat surface using the same fabrication steps. In **chapter 6**, we fabricate a-Si:H TFT passive pixel sensor (PPS) circuits on a curved surface, and characterize their electrical instability and properties. SPICE model is developed and used for a comparison between measured and simulated data. In **chapter 7**, 50 µm pitch 128 x 128 a-Si:H TFT PPS is fabricated, and mask design and fabrication process are described in detail. Electrical characteristics and instability of the a-Si:H TFT pixel switch are characterized and discussed. Lastly expected opto-electronic properties of the organic photodiode to be integrated and PPS imager are elaborated. My dissertation is concluded and future research works are recommended for realizing a-Si:H TFT hemispherical imager in **chapter 8**.

#### **References**

- [1] A. El Gamal, and H. Eltoukhy, "CMOS image sensors," *IEEE Circuits Devices Mag.* 21 May/Jun pp. 6-20, 2005.

- [2] P. Denyer, D. Renshaw, G. Wang, M. Lu, and S. Anderson, "On-chip CMOS sensors for VLSI imaging systems," *Proc. VLSI 91*, pp.157-166, 1991.

- [3] E. R. Fossum, "Active pixel sensor: are CCD's dinosaurs?" *Proc. SPIE*, vol. 1900, pp.2-14, 1993.

- [4] R.A. Street, X.D. Wu, R. Weisfield, S. Ready, R. Apte, M. Nguyen, and P. Nylen, "Two dimensional amorphous silicon image sensor arrays," *Proc. Mater. Res. Soc. Symp.*, vol. 377, pp. 757-766, 1995.

- [5] L.E. Antonuk, Y. El-Mohri, A. Hall, K. Jee, M. Maolinbay, S.C. Nassif, X. Rong, J.H. Siewerdsen, and Q. Zhao, "A large-area 97 μm pitch, indirect-detection, active matrix flat-panel imager," *Proc. SPIE*, vol. 3336, pp. 2-13, 1998.

- [6] R.L. Weisfield, R.A. Street, R.B. Apte, and A. Moor, "Improved page-size 127 μm pixel amorphous-silicon image sensor for x-ray diagnostic medical imaging applications," *Proc.* SPIE, vol. 3032, pp. 14-21, 1997.

- [7] R.L. Weisfield, M.A. Hartney, R.A. Stree, R.B. Apte, "New amorphous-silicon image sensor for X-ray diagnostic medical imaging applications," *Proc. SPIE*, vol. 3336, pp. 444-452, 1998.

- [8] K.E. Spartiotis, R. Orava, T. Schulman, J. Pyyhtia, M. Sarakinos, B. Sanghera, A. Epenetos, I. Sunni, J. Salonen, L. Gronberg, P. Magander, D. Allison, and M. Myers, "Novel direct digital modular x-ray device and system," *Proc. SPIE*, vol. 336, pp. 529-536, 1998.

- [9] R. Guenther, *Modern Optics* (John Wiley & Sons Inc., Cambridge, 1990).

- [10] L. Lee and R. Szema, "Inspirations from biological optics for advanced photonic system," *Science*, vol. 310, pp. 1148-1150, 2005.

- [11] P.K. Swain, D.J. Channin, G.C. Taylor, S.A. Lipp and D.S. Mark, "Curved CCDs and their application with astronomical telescopes and stereo panoramic cameras," *Proc. SPIE*, vol. 5301, pp. 109-129, 2004.

- [12] M.R. Ackermann, J.T. McGraw, and P.C. Zimmer, "Are curved focal planes necessary for wide-field survey telescopes?" *Proc. SPIE*, vol. 5499, pp. 281-301, 2004.

- [13] S.B. Rim, P.B. Catrysse, R. Dinyari, K. Huang, and P. Peumans, "The optical advantages of curved focal plane arrays," *Opt. Express*, vol. 16, pp. 4965-4971. 2008.

- [14] J.M. Rogers, "Curved focal surfaces: design optimization through symmetry, not complexity," *Phonics Tech Briefs Online*, Apr, 2003.

- [15] H.C. Ko, M. Stoykovich, J. Song, V. Malyarchuk, W.M. Choi, C. Yu, J. Geddes III, J. Xiao, S. Wang, Y. Huang and J. Rogers, "A hemispherical electronic eye camera based on compressible silicon optoelectronics," *Nature*, vol. 454, pp. 748 753, 2008.

- [16] P.I. Hsu, R. Bhattacharya, H. Gleskova, M. Huang, Z. Xi, Z. Suo, S. Wagner and J.C. Sturm, "Thin-film transistor circuits on large-area spherical surfaces," *Appl. Phys. Lett.* vol. 81, pp. 1723-1725, 2002.

- [17] M. Meitl, Z. Zhu, V. Kumar, K.J. Lee, X. Feng, Y. Y. Huang, I. Adesida, R. Nuzzo and J.A. Rogers, "Transfer printing by kinetic control of adhesion to an elastomeric stamp," *Nature Mater.*, vol. 5, pp. 33-38, 2006.

- [18] H.O. Jacobs, A.R. Tao, A. Schwartz, D.H. Gracias and G.M. Whitesides, "Fabrication of a cylindrical display by patterned assembly," *Science*, vol. 296, pp. 323-325, 2002.

- [19] W. Zheng, P. Buhlmann and H.O. Jacobs, "Sequential shape-and-solder-directed self-assembly of functional Microsystems," *Proc. Natl. Acad. Sci.*, vol. 101, pp. 12814-12817, 2004.

- [20] S. Stauth and B.A. Parviz, "Self-assembled single-crystal silicon circuits on plastic," *Proc. Natl. Acad. Sci.*, vol. 103, pp. 13922-13927, 2006.

- [21] L. Wang, D.G. Ast, P. Bhargava and A.T. Zenhnder, "Curved silicon electronics," *Proc. Mater. Res. Soc. Symp.*, vol. 769, pp. H2.8.1-H2.8.9, 2003.

- [22] J. Rogers, "Techniques and applications for non-planar lithography," *Proc. Mater. Res. Soc. Symp.*, vol. 739, pp. H1.2.1- H1.2.8, 2003.

- [23] M.K. Erhardt and R.G. Nuzzo, "Fabrication of Pt-Si schottky diodes using soft lithographic patterning and selective chemical vapor deposition," *Langmuir*, vol. 15, pp. 2188-2193, 1999.

- [24] M.K. Erhardt, H.-C. Jin, J. Abelson, and R.G. Nuzzo, "Low-temperature fabrication of Si thin-film transistor microstructures by soft lithographic patterning on curved and planar substrates," Chem. Mater. vol 12, pp. 3306-3315, 2000.

- [25] Y. Xie, Z. Lu, F. Li, J. Zhao and Z. Weng, "Lithographic fabrication of large diffractive optical elements on a concave lens surface," *Opt. Express*, vol. 10, pp. 1043-1047, 2002.

- [26] D. Radtke and U.D. Zeitner, "Laser-lithography on non-planar surfaces," *Opt. Express*, vol. 15, pp. 1167- 1174, 2007.

## Chapter 2

# Advanced a-Si:H Thin-Film Transistor Structures for Sensor Application

#### 2.1 Introduction

Hydrogenated amorphous silicon (a-Si:H) thin-film transistors (TFTs) have been extensively used in pixel circuits for large-area flat-panel displays and x-ray imagers due to excellent spatial uniformity and low fabrication cost [1, 2]. To use such devices for analog amplifiers, switches, and active-matrix organic light-emitting diodes (AM-OLEDs), a higher drain current and/or better electrical stability under prolonged bias stress are required [3,4]. For given channel length of a standard TFT, a higher drain current can be achieved by increasing TFT channel width using advanced TFT structures; fork, Corbino, and hexagonal (HEX) a-Si:H TFT [5-7]. *Lee et. al* proposed Corbino and hexagonal (HEX) a-Si:H TFTs to achieve large channel width without scarifying device electrical stability [6,7].

Such device designs provide a larger pixel aperture ratio (e.g. less pixel area occupation) and smaller parasitic gate-to-source capacitance compared to a standard TFT's for given channel width; in other words, they can provide more space for a storage capacitor and larger gate-to-drain capacitance, which are comprising and leading to a larger pixel capacitance. Furthermore, it is known that TFTs with the asymmetric source-drain electrode have better electrical stability (e.g. less threshold voltage shift) compared to the standard TFT for the same channel width to length (*W/L*) ratio at proper bias conditions [8]. These are promising characteristics for a high-resolution

sensor array application, requiring larger pixel capacitance to accumulate more signal charges and less threshold voltage shift.

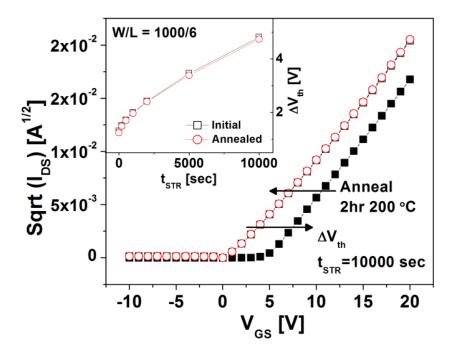

With aforementioned advantages, it is essential to study electrical properties and to evaluate electrical instability of fork and HEX-TFTs in depth. In this chapter, we present asymmetric electrical properties and instability of fork a-Si:H TFT depending on drain bias polarity. We also report on geometrical effects of TFT on the extraction of key device electrical parameters. Then we study in detail current-temperature-stress (CTS) induced electrical instability of single and multiple HEX-TFTs. We measure threshold voltage shift ( $\Delta V_{th}$ ) of single HEX-TFTs and investigate their contribution to overall  $\Delta V_{th}$  of multiple HEX-TFTs. Asymmetric electrical properties of HEX-TFTs were described by H.Lee~et.~al. elsewhere in details [7].

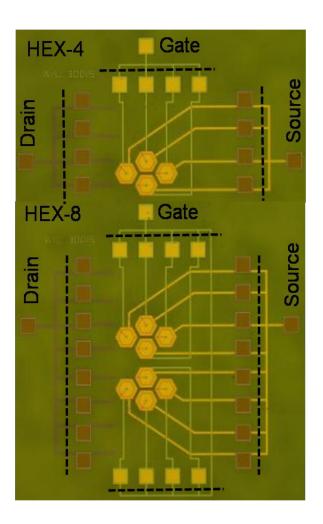

#### 2.2 Fabrication of Fork and Hexagonal a-Si:H TFT

The fork and HEX a-Si:H TFTs were fabricated using the normal AM-LCD 5-photomask process steps (Figure 2.1 and 2.2). More specifically, on the Corning Eagle2000 glass substrate, bi-layer of molybdenum (Mo, 500Å) and aluminum-neodymium alloy (AlNd, 2000Å) was deposited by a sputtering method. The Mo/AlNd gate electrode was then patterned by wet-etching (Mask #1). Following gate electrode definition, hydrogenated amorphous silicon nitride (a-SiN<sub>X</sub>:H, 4000Å)/a-Si:H (1700Å)/phosphor-doped a-Si:H (n<sup>+</sup> a-Si:H, 300Å) tri-layer was deposited by plasma-enhanced chemical vapor deposition (PECVD) at 350 ℃ to form gate insulator and active channel layer, respectively. After defining the device active island by reactive ion etching (RIE) (Mask #2), a chromium (Cr, 1200Å) layer was deposited by sputtering, and source/drain (S/D) electrodes were patterned by wet-etching (Mask #3). Using S/D metal and photo resist as masks, the back-channel-etching by RIE was performed. Then, we deposited a-SiN<sub>X</sub>:H (3000Å) as a

passivation (PVX) layer by PECVD at 300  $^{\circ}$ C. To realize an electrical contact to electrodes (source/drain and gate), vias were formed through the PVX layer by RIE (Mask #4). After contact vias definition, ITO (500Å) was deposited by a sputtering method at room temperature, and then pixel electrodes and probing pads were patterned by wet-etching (Mask #5). As a final step, the thermal annealing was performed for an hour at 235  $^{\circ}$ C.

Figure 2.1 The fork TFT: (a) optical photograph of top view and (b) schematic of cross-sectional view.

Figure 2.2 The HEX TFT: (a) optical photograph of top view and (b) schematic of cross-section view.

#### 2.3 Electrical Properties and Instability of Fork a-Si:H TFT

#### 2.3.1 Experimental results

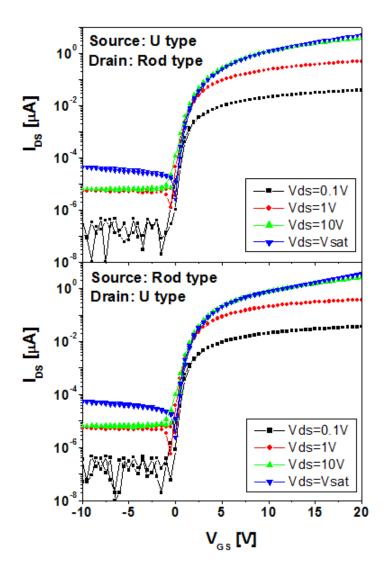

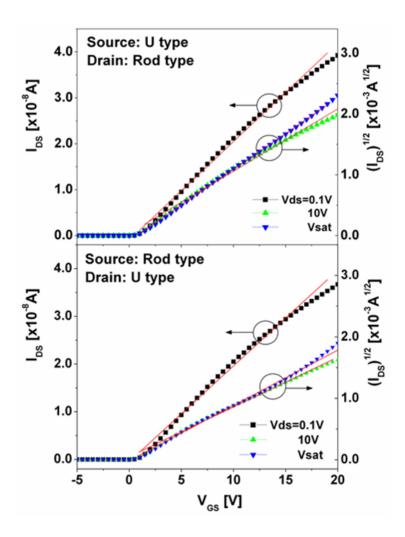

To characterize the electronic properties of fork a-Si:H TFT, we first measured the transfer characteristics of fork a-Si:H TFT; we swept the gate bias from 25 to 0 V, and swept again from 0 to 25 V for various drain voltages (0.1, 1, 10, and 20 V). As shown in Figure 2.3, at low drain voltage ( $V_{DS}$ <1V), the ON-currents are identical for both cases. However, at high  $V_{DS}$  (> 10V), the ON-currents for case (1) are higher than for case (2). Therefore, regardless of gate bias and direction of drain bias applied, the ON-currents would be the same for a low drain bias. However,

when we apply a high drain bias, the ON-current levels can be increased significantly depending on the drain-bias direction. However, at the same time, as the drain bias is increased from 0.1 to 10V, the OFF-currents for both case (1) and (2) showed identical behavior regardless of drain biases; they increased from  $\sim 10^{-13}$  to  $\sim 10^{-12}$  A. During gate bias sweeping, no significant hysteresis ( $\Delta V_{GS}$ ) in current-voltage characteristics was observed for both cases; at  $V_{DS}$ =10V and  $I_{DS}$ =0.1nA, both cases showed  $\Delta V_{GS}$ = 0.5V  $_{case(1)}$  and 0.46V  $_{case(2)}$ .

Figure 2.3 Transfer characteristics of fork a-Si:H TFT for various  $V_{\text{DS}}$ .

Figure 2.4 Output characteristics of fork a-Si:H TFT for various V<sub>GS</sub>.

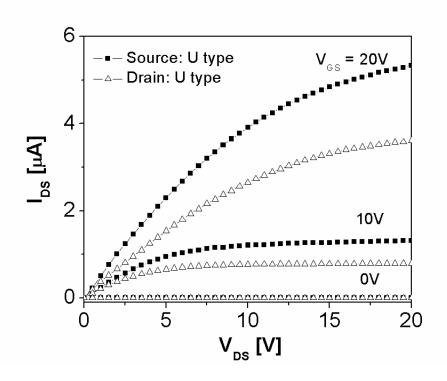

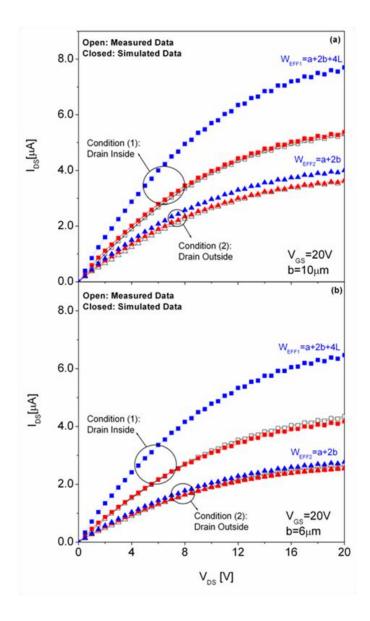

Next, we measured output characteristics (Figure 2.4) by applying the drain bias under following conditions: (1) ground was applied on the outer U-shaped source electrode and drain voltage was applied on the inner rod-shaped drain electrode; (2) drain voltage was applied on the outer U-shaped drain electrode and ground was applied on the inner rod-shaped source electrode. We swept the drain bias from 0 to 20 V for various gate voltages (0, 10, and 20 V). As shown in the Figure 2.4, at  $V_{DS}$ =20 V and  $V_{GS}$ =20 V, the output current for case (1) (= 5.3  $\mu$ A) is 1.5 times higher than for case (2) (= 3.6  $\mu$ A).

#### 2.3.2 Discussion of fork a-Si:H TFT geometry effect

The asymmetric behaviors of fork a-Si:H TFT described above can be explained as follow. As the gate bias increases, a channel is formed in the active a-Si:H layer at the interface with the gate insulator. At low  $V_{DS}$  (~1V), since the channel is not affected by the drain voltage, the whole channel remains as the accumulation layer. Hence, effectively the shape and length of the channel would be the same for both drain bias polarities, and we can define the device effective width  $W_{eff0}$  (= a + 2b + 2L) as the peripheral line of the middle of the channel between source and drain electrodes as shown in Figure 2.1(a), where a is the width of rod electrode, b is the overlapping distance between source and drain electrode, and L is the channel length. This effective width can be used in both cases to extract the device field-effect mobility at low  $V_{DS}$  (linear regime) based on the ideal MOSFET model. The drain current is assumed to be constant at distance y from the drain electrode and can be expressed as  $I_{DS} = W_{eff0}J_y$ , where the current density  $J_y$  is a function of electric field  $E_y$  and potential  $V_y$ :  $J_y = \sigma E_y = \sigma dV_y/dy$ . The resulting differential equation for the potential is expressed as

$$dV = \frac{I_{DS}}{W_{eff0}\sigma}dy \tag{2.1}$$

where the conductivity  $\sigma = \mu_{FE}C_{OX}[(V_{GS}-V_{TH})-V_y]$ ,  $C_{OX}$  is the oxide capacitance,  $\mu_{FE}$  is the field-effect mobility,  $V_{GS}$  is the gate bias, and  $V_{TH}$  is the threshold voltage of TFT. The integration of (2.1) from 0 to L yields the potential drop between the source and drain electrodes as

$$\int_{0}^{V_{DS}} [(V_{GS} - V_{TH}) - V_{y}] dV_{y} = \frac{I_{DS}}{W_{eff \, 0} \mu_{FE} C_{OX}} \int_{0}^{L} dy$$

(2.2)

Hence, the drain current for both-bias polarity can be expressed as

$$I_{DS} = \frac{W_{eff0}C_{OX}\mu_{FE}}{L} \left[ (V_{GS} - V_{TH})V_{DS} - V_{DS}^2 / 2 \right]$$

(2.3)

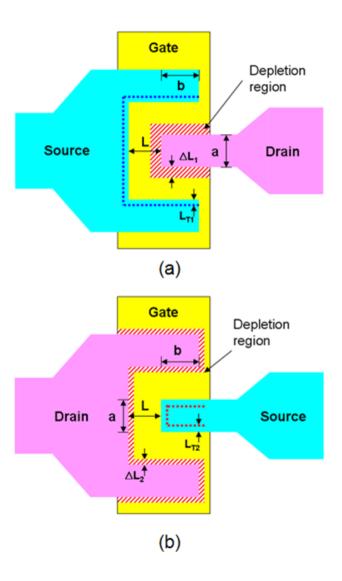

However, output and transfer characteristics at high  $V_{DS}$  (>10V) are quite different from those measured at a low  $V_{DS}$ . As discussed above, at high  $V_{DS}$ , ON-current is higher for drain bias

condition (1) than drain bias condition (2). Assuming the device is ideal crystalline silicon MOSFET and field-effect mobility remains identical for both conditions, the current flowing through TFT can only be strongly dependant on the value of channel width and length. Therefore, at high  $V_{DS}$ , we need to define different geometrical factor  $f_g$  for each drain bias condition to accommodate for differences in device electrical properties. When TFT is operating in the saturation regime at high  $V_{DS}$ , we can assume the channel depletion region at the drain electrode would be increased by a certain value. This change is referred to as channel length modulation factor ( $\Delta L$ ). However, in fork a-Si:H TFT, due to the unique device geometry, we can expect that  $\Delta L$  would be different depending on the drain bias condition; the position of drain and source electrodes [9]. If the drain bias fully depletes the channel by  $\Delta L$  from the edge of drain electrode, the electric field at the depletion region edge of drain electrode can be expressed by the gauss' law; the charge contained in a volume ( $\rho$ ) equals to the permittivity ( $\epsilon_{a-Si}$ ) of a-Si:H times the electric field emanating from the volume:

$$\oint \rho dV = \varepsilon_{a-Si} E \tag{2.4}$$

If the drain bias creates the same number of the depletion-region charge per unit volume  $(Q_d)$  for both drain bias conditions, the electric field for each condition can be expressed by,

$$E_{1} \cong \frac{Q_{d} \times x_{i} \times (a + 2\Delta L_{1}) \times (b + \Delta L_{1})}{\varepsilon_{a-Si}}$$

(2.5a)

$$E_2 \cong \frac{Q_d \times x_i \times [2(a+2\Delta L_2) \times (b+\Delta L_2) + (a+2L-2\Delta L_2)\Delta L_2]}{\varepsilon_{a-Si}}$$

(2.5b)

where  $x_i$  is the depletion width of drain depletion region and  $W_R$  is the width of the outer ring electrode. Therefore, if the electric field at drain depletion region would be same for both conditions ( $E_1=E_2$ ), since the size of drain electrode is larger for condition (2) than for condition

(1), the depletion region at drain side for condition (1) is expected to be larger than for condition (2) ( $\Delta L_1 > \Delta L_2$ ) as shown in Figure 2.5 (a) and (b). It should be noted that due to the unique bottom-gate fork TFT structure, the formed channel is expected to extend even below the source electrode as shown in Figure 2.5.

Figure 2.5 The schematic top views of depletion regions in fork a-Si:H TFT; case (1) where source is applied on U-shaped electrode and case (2) where source is applied on rod-shaped electrode.

However, it is well known that in a-Si:H TFT, the drain current does not flow through the whole source electrode length but is rather limited to a specific length, so-called TFT characteristic length ( $L_T$ ) [10] near the electrode edge. Therefore, the characteristic length for each drain bias condition can be defined as  $L_{T1}$  and  $L_{T2}$ , respectively. To estimate  $L_{T1}$  and  $L_{T2}$ , we measured the channel resistance ( $r_{ch}$ ) and source/drain contact resistance ( $R_{S/D}$ ) for four fork TFTs with different channel lengths for each drain bias condition. From the measurements, TFT characteristic length ( $=R_{S/D}/r_{ch}$ ) was calculated as 1.5  $\mu$ m ( $=L_{T2}$ ) and 1.0  $\mu$ m ( $=L_{T1}$ ) at  $V_{GS}=15V$ , respectively. From the experimental results, we can speculate that  $L_{T2}$  is larger than  $L_{T1}$  because the size of the electrode acting as an electron source is smaller for drain bias condition (2) than for drain bias condition (1).

Based on these assumptions, to derive the equation for the drain current in the saturation regime, the same methodology was applied here as one used for derivation of eq. (2.1); the integration of eq. (2.2) from  $\Delta L_1$  to  $L+L_{T1}$  for drain bias condition (1) and from  $-L_{T2}$  to  $L-\Delta L_2$  for drain bias condition (2) yields the potential drop between the source and drain electrodes for each case, respectively. At the same time, the effective channel width also changes due to different depletion regions for different bias conditions. It should be noted that electrons are assumed to move along the shortest path, the channel length (L) only, not at the corner of U-shape electrode for both bias condition (1) and (2).

$$\int_{0}^{V_{DS}} [(V_{GS} - V_{TH}) - V_{y}] dV_{y} = \frac{I_{DS}}{W_{eff 1} \mu_{FE} C_{OX}} \int_{\Delta L_{1}}^{L+L_{T1}} dy,$$

(2.6a)

where

$$W_{eff1} = a + 2\Delta L_1 + 2(b + \Delta L_1)$$

.

$$\int_{0}^{V_{DS}} [(V_{GS} - V_{TH}) - V_{y}] dV_{y} = \frac{I_{DS}}{W_{eff2} \mu_{FE} C_{OX}} \int_{-L_{E2}}^{L - \Delta L_{2}} dy,$$

(2.6b)

where

$$W_{eff 2} = a + 2(b + \Delta L_2)$$

.

To find the values for  $\Delta L_1$  and  $\Delta L_2$  and corresponding equations for the asymmetric drain current, we do the asymmetric current calculation of fork a-Si:H TFT based on the standard TFT with the same length as reference width (W) = 20  $\mu$ m and length (L) = 6  $\mu$ m. Output drain current of conventional standard TFT was measured at  $V_{GS}$ =20V, and then normalized with its width over length ratio (W/2L), to be used as a reference value for the current calculation. Since both fork and standard a-Si:H TFT have been fabricated over the same substrate at the same time, we expect that their normalized electrical properties are equivalent and only geometries are different. Using normalized output drain current of standard TFT, we calculated the output drain current of fork TFT for each bias condition, by multiplying the normalized standard TFT characteristic by geometric factors defined in eq. (2.7) (output current of fork TFT= normalized output current of standard TFT  $\times$  geometrical factor). By fitting several different values of  $\Delta L_1$  and  $\Delta L_2$  onto integrations above, we could find proper values for the channel length modulation factors empirically as  $\Delta L_1 = L/4$  for condition (1) and  $\Delta L_2 = L/10$  for condition (2), respectively. Hence, since  $V_{DS} = (V_{GS} - V_{TH})$  in the saturation regime, the drain current for each condition can be expressed with corresponding geometrical factor  $f_{g1}$  and  $f_{g2}$ .

$$I_{DS}^{Condition (1)} = f_{g1} \mu_{FE} C_{OX} (V_{GS} - V_{TH})^2$$

, where  $f_{g1} = \frac{a + 2\Delta L_1 + 2(b + \Delta L_1)}{L + L_{T1} - \Delta L_1}$  (2.7a)

$$I_{DS}^{Condition (2)} = f_{g2} \mu_{FE} C_{OX} (V_{GS} - V_{TH})^2$$

, where  $f_{g2} = \frac{a + 2(b + \Delta L_2)}{L + L_{T2} - \Delta L_2}$  (2.7b)

As shown in eq. (2.7), in the saturation regime, values of geometrical factor can have direct impact on drain current values. When a and b in eq. (2.7) are replaced with the actual measured values (a=6  $\mu$ m and b=10  $\mu$ m), the geometrical factor in condition (1) turns out to be larger than

in condition (2) by about 1.5 times. Therefore, the ON-current for drain bias condition (1) is expected to be larger than for drain bias condition (2) by the difference in the geometrical factors.

Figure 2.6 Measured (open symbol) and calculated (closed symbol) output characteristics of fork a-Si:H TFTs. (a)  $a=6~\mu m$  and  $b=10~\mu m$ . (b)  $a=6~\mu m$  and  $b=6~\mu m$ .

As shown in the Figure 2.6, we could exactly match the measured output drain current of Fork TFT for each drain bias condition. It should be noted that when the intuitive channel width  $(W_{EFF1}=a+2b+4L)$  for condition (1) and  $W_{EFF2}=a+2b$  for condition (2)) is used as the circumference of source electrode instead of the geometrical factors given by eq. (2.7), the calculated drain current values are much larger than experimental values, Figure 2.6 (a). To validate these equations of geometrical factor, we measured another set of Fork TFT with different dimensions;  $a=6\mu m$  and  $b=6\mu m$  for smaller fork TFT. Again, the standard TFT is normalized by W/2L to be used as a reference for the calculated drain current. As shown in Figure 2.6 (b), though there is a little deviation observed for drain bias condition (1), the measured output drain current of fork TFT could only be exactly matched when the normalized drain current of standard TFT is multiplied for each bias condition by the defined geometrical factor as defined in eq. (2.7). Again, when the intuitive channel width  $(W_{EFF1}=a+2b+4L)$  for condition (1) and  $W_{EFF2}=a+2b$  for condition (2)) is used instead of the geometrical factor, the calculated output drain current of fork TFT shows huge difference from the measured values especially for bias condition (1).

The OFF-current in a-Si:H TFT is originated from carriers generated in the depletion region on drain side (at high  $V_{DS}$ ) when negative gate bias is applied. Under  $V_{GS}$ <0, the a-Si:H is fully depleted and hole accumulation will take place near the a-Si:H / a-SiN<sub>X</sub>:H interface creating a hole current. The current level is limited by the  $n^+$ -a-Si:H source/drain contact regions (these are hole blocking contacts). If we assume that two quasi  $n^+$ -p junctions are formed between the drain and source  $n^+$ -regions and hole (p) conduction channel, the drain  $n^+$ -p junction is under reverse bias ( $V_{DS}$ >0), which is similar to a  $n^+$ -p junction in the OFF-state. Indeed, in a regular  $n^+$ -p junction, the OFF-current is carried by minority carrier generated in depletion region. The OFF-current ( $J_g$ ) in this region can be limited by the generation rate of carriers and the depletion width  $x_i$  as shown in following equation:

$$J_g = \frac{qn_i x_i}{2\tau_o},\tag{2.8}$$

where q is electron charge,  $n_i$  is the maximum generation rate, and  $\tau_0$  is the life time of excess carrier in the depletion region. If we assume that the width of the depletion region and the generation rate are identical for both drain bias conditions at high  $V_{DS}$ , the OFF-current can depend only on the volume of the depletion region (= the area of drain electrode × the depletion width,  $x_i$ ) for each bias condition. Therefore, since the area of drain electrode is larger in drain bias condition (2) and in drain bias condition (1), the OFF-current of condition (2) is expected to be higher than for condition (1). For image sensor application, drain bias condition (1) is more promising because the OFF-current limits the lowest detectable signal level of image sensor. So the lower OFF-current is, the better.

# 2.3.3 Fork TFT parameters extraction

From TFT data shown in Figures 2.3, 2.4, and 2.7, we can extract sub-threshold slope (S), threshold voltage, and field-effect mobility values. We chose the center position (at  $I_{DS} = 10^{-10} A$ ) in the transfer curve of log ( $I_{DS}$ ) vs.  $V_{GS}$ , and use the linear fitting by taking two log ( $I_{D}$ ) values around the center point to extract S-value. Field-effect mobility ( $\mu_{FE}$ ) and threshold voltage can be calculated as follow: from the transfer curve of  $I_{D}$  vs.  $V_{GS}$ , we chose a specific value of  $I_{D}$  at  $V_{GS}$ =15V. By taking 10 and 90% of this selected  $I_{D}$  value, we define the fitting range in  $I_{D}$  vs.  $V_{GS}$  experimental characteristics. From the slope and x-axis intercept of the calculated curve, the field-effect mobility and threshold voltage have been extracted using eq. (2.3) and (2.7) with different geometrical factors. Calculated device parameters are summarized in Table 1 for linear (low  $V_{DS}$ ) and saturation (high  $V_{DS}$ ) region, respectively.

Figure 2.7 Transfer characteristics of fork a-Si:H TFT. Solid lines used for extraction of the threshold voltage and mobility are also shown (10-90% method used).

For the comparison, we also calculated field-effect mobility ( $\mu_{FE}$ ) and threshold voltage by using the maximum slope method which is usually used for crystalline silicon devices. The field-effect mobility is calculated from transconductance maximum ( $g_m$ ) value using following equations:

$$\mu_{Linear} = \frac{L \cdot g_{m-Linear}}{W_{eff \, 0} C_{OX} V_{DS}},\tag{2.9a}$$

$$\mu_{Saturation} = \frac{g_{m-Saturation}^2}{f_{g1,2}C_{oX}},$$

(2.9b)

where  $g_{m\text{-linear}}$  is the maximum transconductace at  $V_{DS}$ =0.1V, and  $g_{m\text{-saturation}}$  is the maximum transconductance at  $V_{DS}$ = $V_{SAT}$ . From the  $V_{GS}$  value of the maximum  $g_m$  as a reference, two closest points are chosen for straight line fitting through the three points on the transfer curve of  $I_D$ - $V_{GS}$ . The threshold voltage can be estimated from x-axis intercept of this extrapolated line for each drain bias condition. Resulting extracted parameters are summarized in Table 2.1. It is clear from this table that those two calculation methods provide very similar mobility and threshold voltage values for fork a-Si:H TFTs (within experimental error).

| TFT Parameter                   | $ m V_{DS} =$           | 0.1V                    | $V_{DS} = V_{sat}$      |                         |  |

|---------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--|

| Case                            | (1)                     | (2)                     | (1)                     | (2)                     |  |

| S [mV/Dec]                      | 386                     | 375                     | 485                     | 494                     |  |

| V <sub>th</sub> [V]             | 0.73                    | 0.66                    | 0.61                    | 0.84                    |  |

| $I_{OFF}$ at $V_{GS} = -5V [A]$ | 1.00 x10 <sup>-13</sup> | 3.00 x10 <sup>-13</sup> | 3.59 x10 <sup>-11</sup> | 3.77 x10 <sup>-11</sup> |  |

| $\mu_{FE} [cm^2/V \cdot s]$     | 0.32 <sup>a)</sup>      | 0.34 <sup>a)</sup>      | 0.35 <sup>b)</sup>      | 0.39 <sup>c)</sup>      |  |

Table 2.1 Extracted parameters of fork TFT; case (1) where source is applied on U-shaped electrode and case (2) where source is applied on rod-shaped electrode. Geometrical factor a)  $W_{eff0}/L$  b)  $f_{g1}$  and c)  $f_{g2}$  is used to extract the parameter

#### 2.3.4 Electrical instability of fork a-Si:H TFT

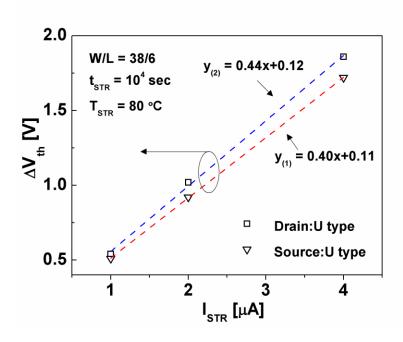

The electrical instability of fork TFT as a switch in sensor application is important in that it affects ON-state resistance ( $R_{ON}$ ), charge transfer time and eventually degrades the switching capability. To evaluate electrical instability of fork TFT, a series of current temperature stress (CTS) measurements of fork TFTs were performed by using a semiconductor parameter analyzer (HP 4156A) under an accelerated stress condition by setting the stress temperature ( $T_{STR}$ ) at 80 °C. During the CTS measurements, we connected the gate and drain bias together and continuously applied the current through the drain to the TFTs. Source of the TFT was grounded. So the TFTs operated in the saturation regime. We applied various drain current values:  $I_{STR}$  of 1, 2, and 4  $\mu$ A corresponds to  $J_{STR}$  of 263, 527, and 1053 A/cm², respectively. The total stress time ( $t_{STR}$ ) was 10,000 sec, and we only interrupted the applied stress for 60 sec to measure the transfer characteristics. We measured and collected results for both case (1) and (2).