## Probabilistic Analysis for Modeling and Simulating Digital Circuits

by

Chien-Chih Yu

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2012

**Doctoral Committee:**

Professor John P. Hayes, Chair Professor Todd M. Austin Professor Marios C. Papaefthymiou Assistant Professor Mariel Lavieri-Rodriguez © Chien-Chih Yu All rights reserved 2012 To Mom and My Sister

#### ACKNOWLEDGEMENTS

I wish to thank all the people who helped me with my research and life at the University of Michigan. I would like to thank my academic advisor Professor John Hayes not only for his advice on research but also for his firm and continuous financial support. I would also like to thank Professor Lavieri for her feedback on my research, and Professors Austin and Papaefthymiou for serving on my Thesis Committee.

I am grateful to Dr. Kenneth Zick for providing a unique opportunity to participate a satellite circuit design project at the USC Information Science Institute. I also thank Armin Alaghi with whom I collaborated. I could not have finished my last research task without his brilliant observations and ideas. I would like to thank people who helped to improve my writing skill including Professors Rod Johnson and Elizabeth Hildinger, and Jin Hu. I would like to thank Stella Hu who gave great help when I was looking for jobs.

I am also grateful to the National Science Foundation for supporting my Ph. D. studies.

I would like to acknowledge my classmates and friends including Kai-hui Chang, Smita Krishnaswamy, Sungsoon Cho, Ramashis Das, Dae Young Lee, MingChi Hsu, Andrea Pellegrini, Cheng Zhuo, Po-Chun Hsu, Rita Tsai, Wei-Ling Chiang, Cheng Zhuo, Te-Hsuan Chen, Ada Lin, Emily Yeh, and many others in America and in Taiwan.

Finally, I would thank my mom and sister. I could not have completed the entire doctoral program without their encouragement and support.

# TABLE OF CONTENTS

| DEDICATION.          |                                                     | ii |  |  |  |  |

|----------------------|-----------------------------------------------------|----|--|--|--|--|

| ACKNOWLEDGEMENTS iii |                                                     |    |  |  |  |  |

| LIST OF FIGUE        | RES                                                 | vi |  |  |  |  |

| LIST OF TABL         | ES                                                  | ix |  |  |  |  |

| PREFACE              |                                                     | X  |  |  |  |  |

| CHAPTER 1 In         | ntroduction                                         | 1  |  |  |  |  |

| 1.1                  | Background                                          | 2  |  |  |  |  |

| 1.2                  | Signal Probability Analysis                         | 14 |  |  |  |  |

| 1.3                  | Soft Error Modeling and Analysis                    | 19 |  |  |  |  |

| 1.4                  | Probabilistic Transfer Matrices                     |    |  |  |  |  |

| 1.5                  | Thesis Outline                                      |    |  |  |  |  |

| CHAPTER 2 C          | Circuit Sampling for Signal Probability Calculation |    |  |  |  |  |

| 2.1                  | Background                                          |    |  |  |  |  |

| 2.2                  | Prior Work                                          |    |  |  |  |  |

| 2.3                  | Signal Redundancy                                   |    |  |  |  |  |

| 2.4                  | Sampling Concepts                                   |    |  |  |  |  |

| 2.5                  | Variable Ordering                                   |    |  |  |  |  |

| 2.6                  | Sample Space Reduction                              |    |  |  |  |  |

| 2.7                  | Implementation Issues                               |    |  |  |  |  |

| 2.8                  | Experimental Results                                | 51 |  |  |  |  |

| 2.9                  | Case Study                                          | 56 |  |  |  |  |

| 2.10                 | Summary                                             | 57 |  |  |  |  |

| CHAPTER 3 T          | rigonometry-based Probability Modeling              | 59 |  |  |  |  |

| 3.1                  | Background                                          | 60 |  |  |  |  |

| 3.2                  | Unconditional Error Representation                  | 64 |  |  |  |  |

| 3.3                  | 3.3 Trigonometric Representation of Probability     |    |  |  |  |  |

|                      | 3.3.1 Trigonometric Signal Probability              | 66 |  |  |  |  |

|                      | 3.3.2 Trigonometric Error Model                     | 67 |  |  |  |  |

| 3.4          | Probabilistic Calculation Algorithm         | 71  |  |  |  |

|--------------|---------------------------------------------|-----|--|--|--|

|              | 3.4.1 Correlation Handling                  | 71  |  |  |  |

|              | 3.4.2 Signal Probability Estimation         | 73  |  |  |  |

| 3.5          | Simulation Results                          | 75  |  |  |  |

| 3.6          | Summary                                     |     |  |  |  |

| CHAPTER 4 So | oft-Error Estimation in Sequential Circuits | 80  |  |  |  |

| 4.1          | Prior Work                                  | 81  |  |  |  |

| 4.2          | SER Measurement in Sequential Circuits      | 83  |  |  |  |

| 4.3          | PTM-Based Analysis                          | 85  |  |  |  |

| 4.4          | Circuit Partitioning                        |     |  |  |  |

| 4.5          | Fault Simulation-based PTM construction     |     |  |  |  |

| 4.6          | Probabilistic Calculation Method            |     |  |  |  |

| 4.7          | SER Estimation                              |     |  |  |  |

| 4.8          | Summary                                     | 100 |  |  |  |

| CHAPTER 5 Co | onclusions and Future Work                  | 102 |  |  |  |

| 5.1          | Summary of Contributions                    | 103 |  |  |  |

| 5.2          | Future Work                                 | 105 |  |  |  |

|              | 5.2.1 Sampling with Implication             | 105 |  |  |  |

|              | 5.2.2 Soft-Error Estimation Using Sampling  | 107 |  |  |  |

|              | 5.2.3 PTM Construction Using Learning       | 109 |  |  |  |

| BIBLIOGRAPH  | Y                                           |     |  |  |  |

# LIST OF FIGURES

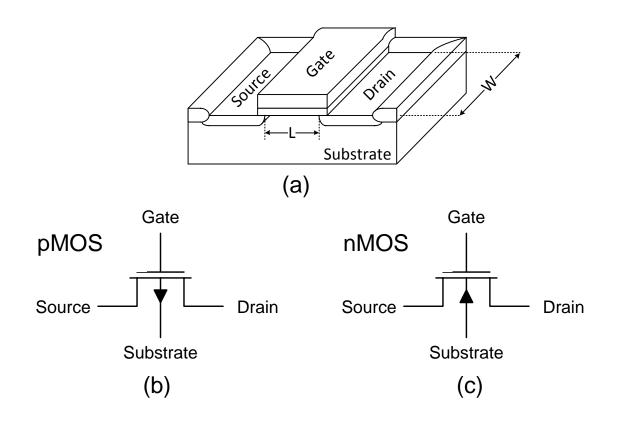

| Figure 1.1. (a) Structure of a transistor; <i>L</i> and <i>W</i> denote the length and width of the gate, (b) pMOS symbol and (c) nMOS symbol                                       | 3   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

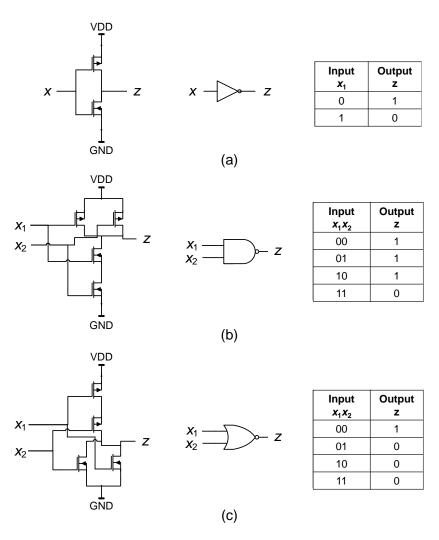

| Figure 1.2. Transistor schematic, circuit symbol, and truth table of (a) an inverter,<br>(b) a two-input NAND gate, and (c) a two-input NOR gate                                    | . 5 |

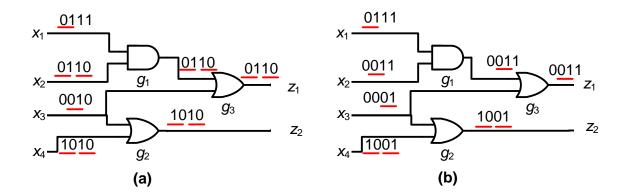

| Figure 1.3. Switching activities caused by different input sequence orders; signal transitions are underlined.                                                                      | 7   |

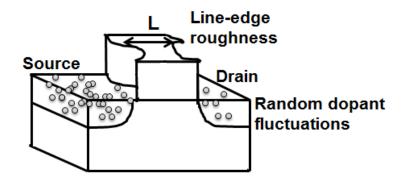

| Figure 1.4 Impact of the LER and RDF phenomena on a transistor                                                                                                                      | . 8 |

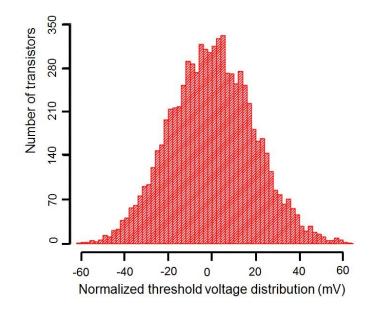

| Figure 1.5. Threshold voltage variation of the IBM 65-nm silicon-on-isolator process; results are measured among 8,000 devices [4]                                                  | . 8 |

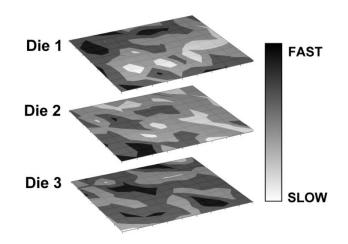

| Figure 1.6. Delay profiles for three different 65-nm 80-core microprocessor chips [24].                                                                                             | 9   |

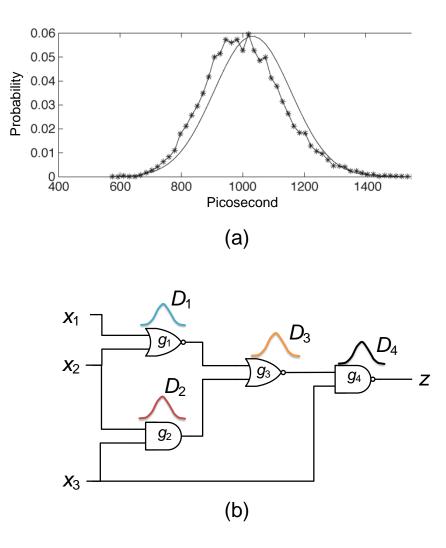

| Figure 1.7. (a) Gate delay distribution. (b) Illustration of statistical timing analysis;<br>the delay of each gate $g_i$ is modeled by a random variable $D_i$                     | 10  |

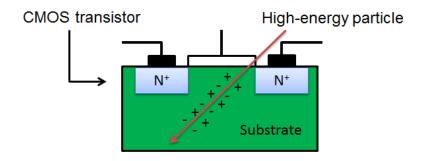

| Figure 1.8 A soft error in a transistor caused by a high-energy particle                                                                                                            | 12  |

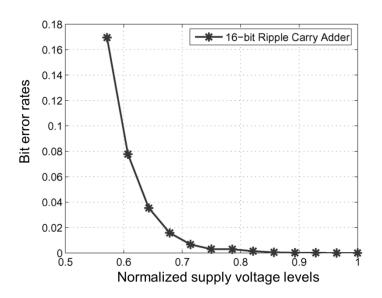

| Figure 1.9. Bit error rates for different voltage overscaling levels in a 16-bit<br>ripple-carry-adder using IBM 130 nm-process parameters; normal<br>supply voltage is 1.35v [60]. | 13  |

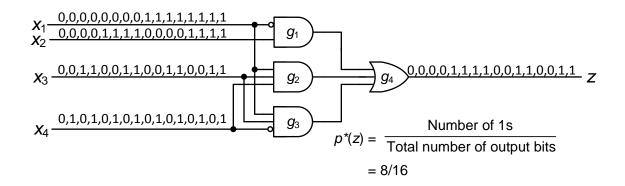

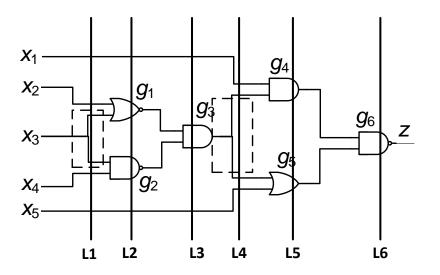

| Figure 1.10 Signal probability estimation via exhaustive simulation                                                                                                                 | 15  |

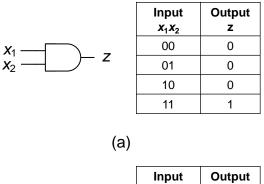

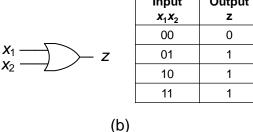

| Figure 1.11. Circuit symbol and truth table of (a) a two-input AND and (b) a two-input OR gates.                                                                                    | 16  |

| Figure 1.12. Signal probability estimation for a five-input circuit via (a) MC sampling and (b) probabilistic analysis.                                                             | 17  |

| Figure 1.13 Two circuits with fanout-reconvergence structures marked with red bold lines.                                                                                           | 18  |

| Figure 1.14 (a) Two-input AND gate, and its behavior with (b) a conditional gate error model, and (c) an unconditional gate error model                                             | 19  |

| Figure 1.15 Illustration of three masking effects: (a) logical, (b) electrical, and (c) temporal.                                                                                   | 22  |

| Figure 1.16. (a) Two-input AND gate, and (b) its PTM representation with a conditional error model.                                                                                 | 24  |

| Figure 1.17. (a) Two-input AND gate, (b) its gate PTM with unconditional error $p_{err}$ , and (c) its ADD representation                                                           | 25  |

|                                                                                                                                                                                     |     |

| Figure 1.18. (a) Three-input circuit, (b) its circuit PTM for $p_{err} = 0.1$ , and (c) the corresponding ADD                                               | 26 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1. Four-input circuit (copy of Figure 1.13(b))                                                                                                     | 32 |

| Figure 2.2. Circuit illustrating signal probability estimation via sampling; (copy of Figure 1.10).                                                         | 35 |

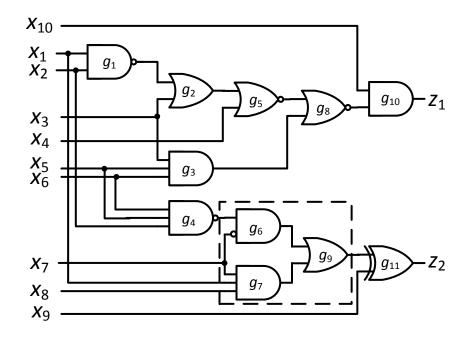

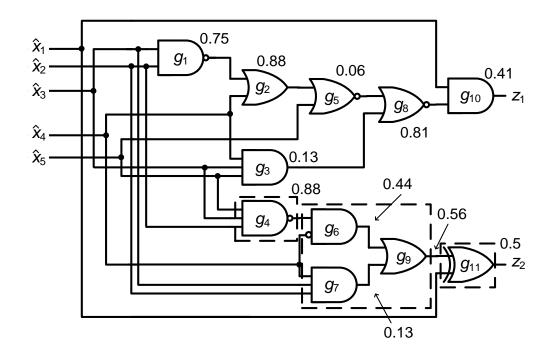

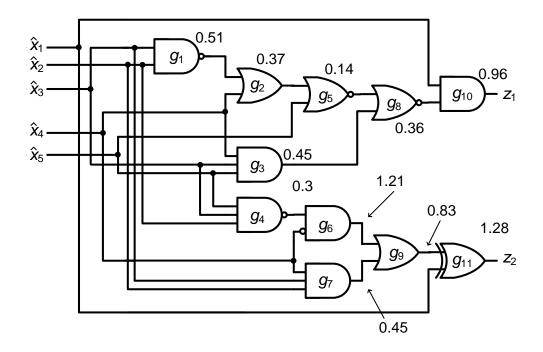

| Figure 2.3. Ten-input, two-output circuit; a multiplexer-like structure formed by $g_6$ , $g_7$ and $g_8$ is highlighted.                                   | 36 |

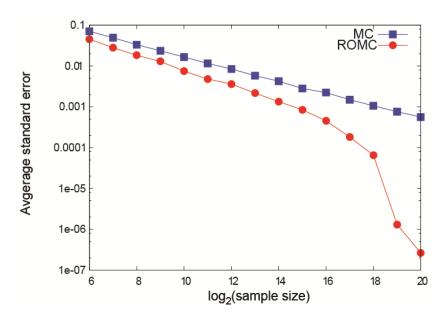

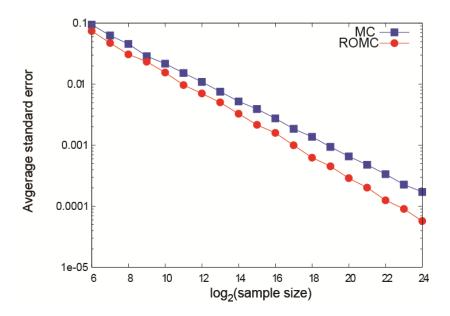

| Figure 2.4. Accuracy comparison between ROMC and a typical MC calculation of the average output signal probability for the circuit in Figure 2.3            | 37 |

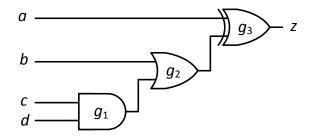

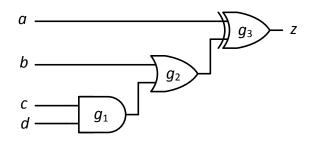

| Figure 2.5. Variable ordering; <i>a</i> and <i>b</i> are more observable than <i>c</i> and <i>d</i>                                                         | 44 |

| Figure 2.6. Five-input circuit obtained from Figure 2.3 by connecting compatible primary inputs; the supergates of $z_2$ are marked by dotted lines         | 47 |

| Figure 2.7. Pseudo-code for the ROMC simulation algorithm.                                                                                                  | 49 |

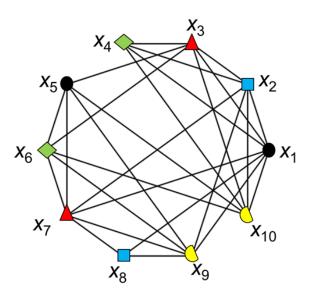

| Figure 2.8. Conflict graph for the circuit in Figure 2.3; primary inputs with the same color labels are compatible and can share samples                    | 51 |

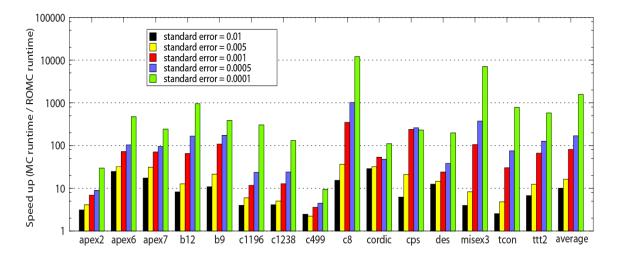

| Figure 2.9. Speed-up of ROMC over MC for the benchmark circuits at five accuracy levels defined by standard error.                                          | 52 |

| Figure 2.10. Comparison between MC and ROMC for C1196.                                                                                                      | 54 |

| Figure 2.11. Comparison between MC and ROMC for C499.                                                                                                       | 55 |

| Figure 2.12. Power consumption of the five-input circuit in Figure 2.6.                                                                                     | 57 |

| Figure 3.1. Illustration of the FE method; an on-path is denoted by red bold lines                                                                          | 63 |

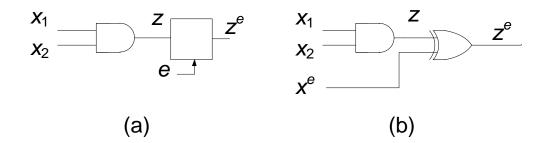

| Figure 3.2. (a) Two-input AND gate, and (b) its behavior with an unconditional error model.                                                                 | 65 |

| Figure 3.3. (a) Two-input AND gate with unconditional error <i>e</i> ; (b) Using a two-input XOR gate to model the error.                                   | 66 |

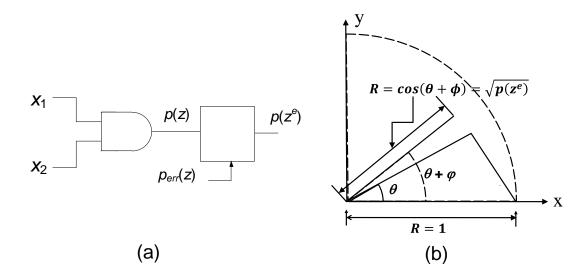

| Figure 3.4. (a) Two-input AND gate with an unconditional error; (b) its trigonometric probability representation.                                           | 68 |

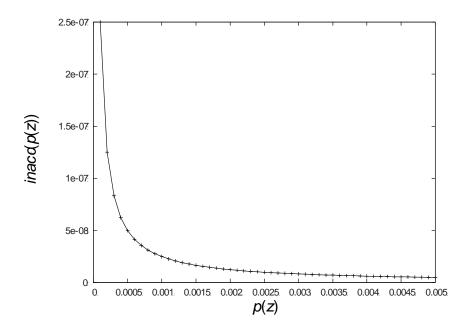

| Figure 3.5. Computational inaccuracy <i>inacc</i> ( $p(z^e)$ ) for $p(z) = 10^{-4}$ to $5 \times 10^{-3}$ with gate-error probability $p_{err} = 10^{-5}$ . | 70 |

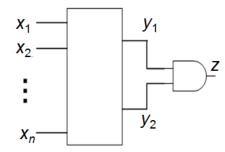

| Figure 3.6. Single-output circuit with <i>n</i> inputs.                                                                                                     | 71 |

| Figure 3.7. TPC probability estimation algorithm.                                                                                                           | 75 |

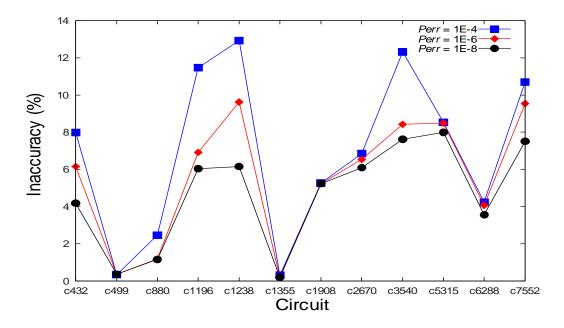

| Figure 3.8. Average computational error of the TPC method for various gate-error probabilities.                                                             | 77 |

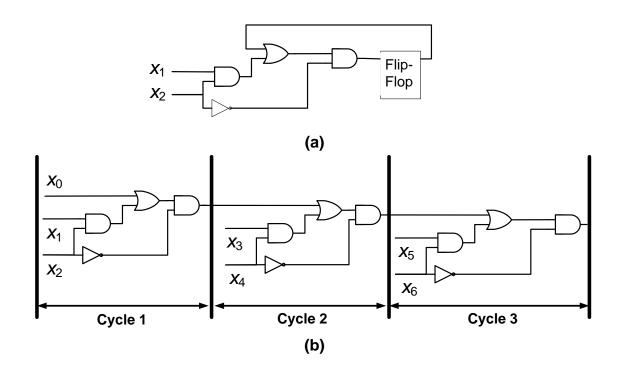

| Figure 4.1. Illustration of the time-frame expansion technique: (a) original sequential circuit and (b) expanded circuit with three time frames             | 82 |

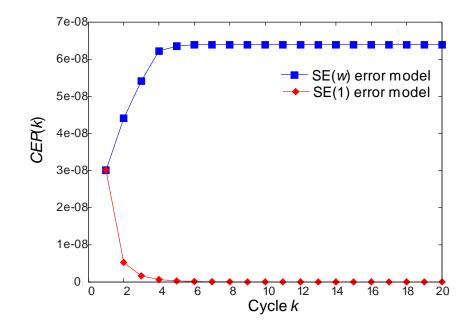

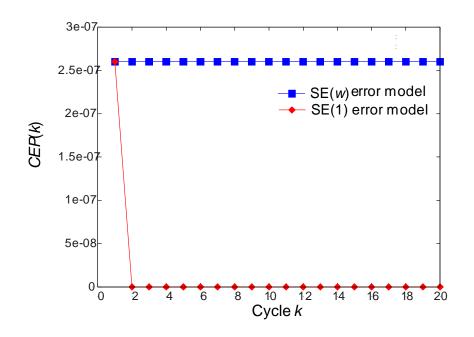

| Figure 4.2. Circuit error probabilities for the S298 benchmark assuming a gate-<br>error probability of 10 <sup>-7</sup> .                                  | 85 |

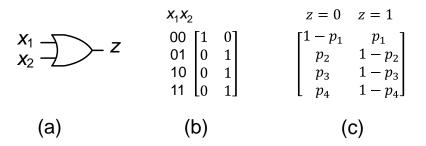

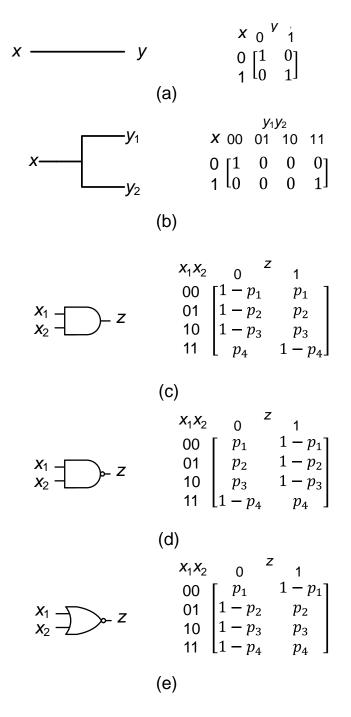

| Figure 4.3. (a) Two-input OR gate, (b) its ITM, and (c) a PTM with various error probabilities for each input vector                                | 86  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

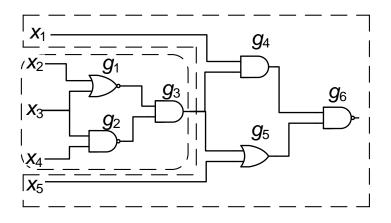

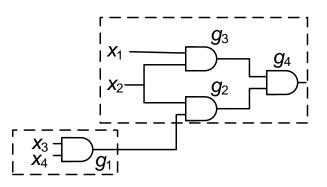

| Figure 4.4. Circuit <i>C</i> demonstrating PTM construction; dashed lines enclose fanout gates                                                      | 87  |

| Figure 4.5. Gate PTMs of (a) a single wire, (b) a fanout node, (c) a two-input AND, (d) a two-input NAND, and (e) a two-input NOR gate              | 88  |

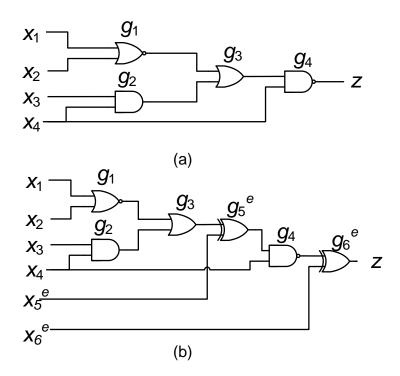

| Figure 4.6. The circuit of Figure 4.4 with its two supergates marked by dashed lines                                                                | 91  |

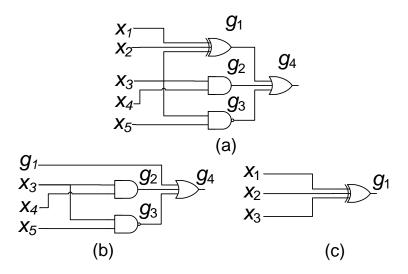

| Figure 4.7. (a) Original circuit consisting of a single supergate; (b-c) the two sub-<br>circuits resulting from cone clustering with $r_{max} = 4$ | 92  |

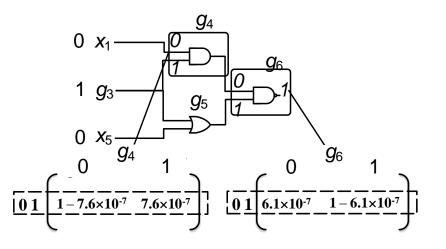

| Figure 4.8. Supergate of $g_6$ with input vector (0, 1, 0) and critical gates $g_4$ and $g_6$                                                       | 95  |

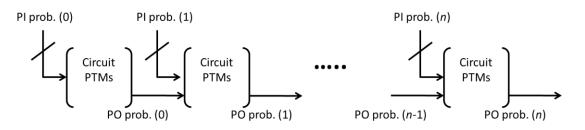

| Figure 4.9. Probabilistic estimation procedure for $n + 1$ cycles; note that the same circuit PTMs are used for every cycle                         | 96  |

| Figure 4.10. Probability estimation algorithm used in SAMPLE.                                                                                       | 96  |

| Figure 4.11. Circuit error probabilities for the S1238 benchmark assuming a gate-<br>error probability of 10 <sup>-7</sup> .                        | 99  |

| Figure 5.1. Four-input circuit                                                                                                                      | 106 |

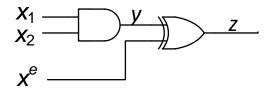

| Figure 5.2. XOR-extended circuit for a two-input AND gate.                                                                                          | 108 |

| Figure 5.3. (a) Four-input circuit; (b) its XOR-extended circuit for simulating soft errors occurring at $g_3$ and $g_4$                            | 109 |

| Figure 5.4. Four-input circuit; its two supergates are marked with dashed lines                                                                     | 110 |

# LIST OF TABLES

| Table 1.1. Technology trends in CMOS manufacturing [65].                                                                                          | 4  |

|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.1 Signal probability calculation rules for an <i>n</i> -input elementary gate $z(x_1, x_2,, x_n)$ with independent inputs.                | 31 |

| Table 2.2. Performance of compatibility and observability determination for selected benchmark circuits including the largest benchmark circuits. | 53 |

| Table 3.1. Performance of TPC and MC for gate-error probability 10-8 with selected ISCAS-85 benchmarks (including the largest ones)               | 76 |

| Table 3.2. Runtime comparison between the TPC and SP methods for reliability estimation.                                                          | 78 |

| Table 4.1. Performance results for the ISCAS-89 benchmark circuits (including the largest circuits).                                              | 98 |

## PREFACE

Due to the rapid progress of their manufacturing technologies, integrated circuit (ICs) can now contain billions of transistors and operate at gigahertz frequencies. This great complexity has forced engineers to rely on electronic design automation (EDA) software tools to design, verify and test new ICs. Traditional EDA tools are deterministic in nature and try to explicitly address all a circuit's operating modes by examining very large input signal sets and computing their output responses. However, beyond some point, such methods must be replaced by random sampling of the inputs, an approach that is inherently probabilistic. Manufacturing process variations and soft errors caused by environmental disturbances also call for statistical approaches to gauge their impact. Hence, there is an increasing need for probabilistic characterizations of IC behavior that can be easily incorporated into EDA tools, and can be used in situations where traditional deterministic approaches are ineffective.

The goal of this dissertation is to develop ways to significantly improve the quality of the probabilistic analysis techniques required for EDA. The accuracy and scalability of these techniques is greatly affected by several factors, including the probability models employed and the handling of correlations among signals. To address such issues, we develop novel and efficient ways to sample logic circuit behavior, model the impact of soft errors, and estimate circuit reliability. First, we present a methodology for sampling input signals that improves accuracy and runtime by prioritizing the sample variables and compressing the sample space. Then, we introduce a trigonometry-based technique for efficiently analyzing soft errors by mapping signal probabilities into angles. Finally, a reliability estimation method is described that uses probabilistic transfer matrices to calculate signal and error probability distributions in sequential circuits. Unlike previous techniques, its memory usage grows slowly even when simulating very large circuits over many clock cycles. Extensive simulation studies are presented in support of all the foregoing results.

The contributions of this dissertation identify features of probabilistic, error-inducing phenomena that can lead to significant improvements in circuit quality. They also reduce the computational overhead for probabilistic calculations which are essential for many EDA tasks.

# CHAPTER 1 Introduction

In the semiconductor industry, the cost of designing and manufacturing integrated circuits (ICs), including financial investment, time-to-market, and human resources heavily depends heavily on the effectiveness of electronic design automation (EDA) tools. EDA refers to the use of software-implemented techniques for accelerating the design and manufacturing processes, and for improving the quality of IC-based products. EDA tools have been widely adopted for implementing routine design steps, for validating circuit functionality, for analyzing performance features such as delay and power consumption, for generating layout data, and for testing product quality.

Traditional EDA methods employ deterministic approaches, which assume that the circuit's entire structure and behavior are definite and fully predictable. However, IC complexity has reached a point where circuits contain billions of transistors and can perform billions of calculations per second. This complexity poses some new challenges for EDA. For example, random sampling is increasingly necessary to estimate important aspects of IC behavior. Furthermore, ICs are becoming sensitive to non-deterministic effects such as imperfect manufacturing processes and environmental disturbances. Hence, conventional deterministic approaches are becoming less effective for many EDA tasks.

Unlike deterministic approaches, probabilistic analysis views a circuit from a statistical perspective, and provides a natural way both to describe and simulate non-deterministic effects. It models the properties of devices and signals in terms of probabilities, and measures their characteristics using statistical techniques such as sampling and averaging. Probabilistic analysis has been applied to several areas of EDA, such as the estimation of reliability [61], testability [46], and power [47]. Recently, probabilistic analysis has also been used for measuring the impact of manufacturing variations in ICs [21][38][41], and for analyzing the vulnerability of ICs to soft errors resulting from decreasing noise margins [19][67].

In this chapter, we provide an overview of the role of probabilistic analysis in EDA. We review the basic concepts of probabilistic analysis, study several existing probabilitybased applications, and address the problems and limitations of existing methods. We then summarize the major contributions of this dissertation.

### 1.1 Background

Integrated circuit (IC) technology was invented in the late 1950s [42]. After 50 years of steady development, ICs now are widely used in personal computers, mobile phones, cars, and so on. Not only are they deeply integrated into our daily life, but they also have changed the way modern society operates. For instance, supercomputers containing vast numbers of ICs are used for weather and environmental forecasting, geological surveys in the energy industry, and structure analyses of proteins in the pharmaceutical industry [55].

Virtually all ICs are manufactured with complementary metal-oxide-semiconductor (CMOS) process technology, where the fundamental components are switching devices called transistors. The structure of a typical transistor is shown in Figure 1.1(a). There are four parts to a transistor: the gate, the substrate, and two terminals called the source and drain. The length *L* of a transistor's gate is a key parameter that is often referred to as the "feature size" of a particular CMOS manufacturing technology "node" in the industry. For instance, a  $0.25 - \mu m$  ( $0.25 \times 10^{-6}$  meter) CMOS manufacturing technology indicates one that is capable of producing transistors whose gate lengths are around 0.25  $\mu m$ .

Figure 1.1. (a) Structure of a transistor; *L* and *W* denote the length and width of the gate, (b) pMOS symbol and (c) nMOS symbol.

In 1965, Gordon Moore of Intel predicted that the number of transistors in an IC would double about every 24 months, an insightful observation now referred to as Moore's Law [42]. Continuing developments in CMOS process technology suggest that Moore's Law will extend into the next decade [30][65], as shown in Table 1.1.

| Year                          | 2006 | 2008 | 2010 | 2012 | 2014 |

|-------------------------------|------|------|------|------|------|

| Feature size (nm)             | 65   | 45   | 32   | 22   | 16   |

| Supply voltage                | 1.2  | 1.0  | 0.9  | 0.8  | 0.7  |

| Gate count (10 <sup>9</sup> ) | 4    | 8    | 16   | 32   | 64   |

Table 1.1. Technology trends in CMOS manufacturing [65].

With modern process technologies, engineers can design ICs that are much more complex in terms of transistor count and operation speed than ever before. In 1997, for instance, Intel's Pentium II microprocessors were manufactured with a 0.25-µm CMOS technology; they contained 7.5 million transistors, and operated at 200 MHz. In 2012, Intel's Core i7 microprocessors manufactured with a 28-nm technology, contain over 1.7 billion transistors, and operate at 3 GHz. This represents an improvement of about three orders of magnitude in transistor density and computational capacity.

Two types of transistors are used in logic circuits, namely are n-type and p-type metal-oxide-silicon (MOS) transistors, i.e., nMOS and pMOS transistors, as shown in Figures 1.1(b) and (c). A transistor's current in a conducting channel between the source and drain is controlled by the voltage applied to the transistor's gate terminal. An important electrical parameter that characterizes a transistor's behavior is its threshold voltage Vt. For an nMOS (pMOS) transistor, if the voltage between its gate and source Vgs is higher (lower) than its threshold voltage, i.e., Vgs > Vtn (Vgs < Vtp), then the channel between the source and drain begins to conduct. We say a transistor is ON if its

channel is conducting; otherwise, it is OFF. Clearly, transistors can be used as switches, and their ON and OFF states are usually referred to as 1 and 0 in logic circuits.

In addition, pMOS and nMOS transistors can be used for forming the basic components (gates) used in logic circuits. There are five types of elementary gates, namely inverter, NAND, NOR, AND and OR gates, each of which implements a specific Boolean function. Figure 1.2 shows the circuit structures, graphic symbols, and the functions of an inverter, and two-input NAND and NOR gates. AND and OR gates are typically formed by combining NAND or NOR gates with inverters.

Figure 1.2. Transistor schematic, circuit symbol, and truth table of (a) an inverter, (b) a two-input NAND gate, and (c) a two-input NOR gate.

Integrated circuits can be viewed at several levels of abstraction such as the transistor, logic, register-transfer, and system levels [62], We will generally only consider the logic level, where the IC is modeled as a large set of interconnected gates that process the logic signals 0 and 1. This level has the advantage of being relatively independent of electrical and other physical details. However, it may entail special (indirect or non-deterministic) methods to analyze properties of interest such as power consumption.

Consider, for example, the task of analyzing a circuit's power consumption. A CMOS gate's maximum power consumption occurs when a signal at the gate changes from 0 to 1 or from 1 to 0. In general, a gate's dynamic power consumption is proportional to its *switching activity*, which indicates how frequently the gate's output signal changes value [22][47][58].

Figures 1.3(a) and (b) show a circuit assigned two different but similar four-bit input sequences: the number of 1s and 0s in the corresponding sequences are the same. However, the total numbers of transitions at  $g_1$ ,  $g_2$ , and  $g_3$  in Figures 1.3(a) and (b) are 6 and 4, respectively, and hence the power consumption in Figure 1.3(a) is higher by about 33% than that in Figure 1.3(b), assuming all gates have the same power consumption characteristics. Hence, the order of the applied inputs needs to be taken into consideration for accurately measuring the circuit power consumption with deterministic simulations. The total number of possible cases that exists in this small circuit is  $16! = 2.09 \times 10^{13}$ . As can be seen, measuring the power consumption by explicitly enumerating all possible cases is infeasible.

Figure 1.3. Switching activities caused by different input sequence orders; signal transitions are underlined.

Instead of exhaustively simulating circuits with all possible input sequences, Wu et al. [64] show that a circuit's power consumption can be accurately calculated by randomly sampling the switching activities of its individual gates. We will show in detail in Chapter 2 how to estimate a circuit's power consumption by probabilistic analysis of switching activities.

Deterministic approaches are inadequate for simulating the non-deterministic effects caused by process variations. These are phenomena where semiconductor fabrication processes are unable to produce identical transistors when a transistor's size shrinks below the scale of a few hundreds atoms. Performance features, such as delay and power consumption can vary from transistor to transistor, even in the same chip.

For instance, when CMOS technology is scaled to below 65 nm, precisely controlling the shape and doping concentrations of transistors during manufacture becomes difficult. The resulting process variations not only reduce manufacturing yield, but also affect circuit characteristics such as leakage current, threshold voltage, and power consumption. For instance, a major problem of 65-nm manufacturing technology is random dopant fluctuation (RDF) where the number of dopant atoms is unevenly implanted in a transistor [6]. Another source of process variation is line-edge roughness (LER), resulting from imperfect etching processes. In 65-nm CMOS technology, forming uniform shapes for individual transistors by etching is very difficult, because the etching process cannot be precisely controlled [44]. A consequence of the LER problem is an increase in the variance of channel length among transistors.

Figure 1.4 Impact of the LER and RDF phenomena on a transistor.

Figure 1.5. Threshold voltage variation of the IBM 65-nm silicon-on-isolator process; results are measured among 8,000 devices [4].

Figure 1.4 illustrates the impact of RDF and LER on a single transistor. Such manufacturing problems make the threshold voltages and leakage currents of individual transistors different from each other. This, in turn, affects the electrical characteristics such as threshold voltage of logic gates. Figure 1.5 shows threshold voltages of transistors in the same wafer spread across 120 mV, which is a broad range. As the result, individual chips can have unique electrical characteristics that affect their delay characteristics and power consumption. Figure 1.6 illustrates the differences in gate delay caused by process variations among three individual Intel microprocessor chips.

Figure 1.6. Delay profiles for three different 65-nm 80-core microprocessor chips [24].

Identifying the longest paths in an IC and evaluating their delays are important tasks for circuit design and testing [43][50]. Traditional timing analysis methods determine the longest delays from a circuit's structure, and they assume the delays of each gate type are the same. However, these deterministic methods are increasingly unable to capture the complete timing behavior of paths and gates caused by process variations. A technique called statistical timing analysis [21][38][41] has been developed to deal with the aforementioned problems. Unlike static timing analysis methods, which model gate delays as constants, the statistical approach treats gate delays as random variables. The effects of process variations on delay are described in terms of the variances of the random variables. For a path of interest, its delay may be estimated by propagating delay variables along the path, as depicted in Figure 1.7. Probability-based timing analysis is being gradually adopted by industry [17][63].

Figure 1.7. (a) Gate delay distribution. (b) Illustration of statistical timing analysis; the delay of each gate  $g_i$  is modeled by a random variable  $D_i$ .

Recently, concern about soft errors has been increasing. Probabilistic analysis of soft errors raises issues and problems different from those mentioned so far. When transistors are manufactured at the nanometer scale, they are very sensitive to any manufacturing or electrical fluctuations, such as small process defects and unexpected voltage drops, and devices can temporarily malfunction. In other words, the behavior of a circuit is no longer fully predictable even if it has no manufacturing defects. Thus, circuit behavior is characterized by some degree of uncertainty because of the unpredictable occurrence of soft errors.

There are three major sources of soft errors: high-energy particles due to cosmic radiation, process variation, and voltage overscaling. Cosmic rays are composed of various subatomic particles such as neutrons originating from outer space [36]. The energy density of cosmic rays increases with altitude. For instance, the energy density at 30,000 feet, a typical flight altitude for commercial airplanes, is two orders of magnitude higher than the energy density at sea level [71].

When a high-energy particle hits a transistor, the state of the transistor may be temporarily changed. Such particle strikes are called *single-event upsets* (SEUs), see Figure 1.8. SEUs may lead to (soft) errors in circuits, or even to catastrophic system failures if they are successfully propagated to primary outputs or are stored by memory elements. For example, in 2008, a Qantas A330 airplane suddenly went out of control, and plunged downwards resulting in serious injuries to a flight attendant and several passengers. After examining the flight recorder, the Australian Transport Safety Bureau concluded the accident resulted from high energy neutron strikes to the aircraft's control computers [9].

Figure 1.8 A soft error in a transistor caused by a high-energy particle.

Even though the energy density of cosmic rays at ground level is relatively low, the threshold energy for generating SEUs on a transistor has been decreasing with falling supply voltage and transistor size. Therefore, the impact SEUs on ICs can no longer be ignored [23]. Ando et al. [6] designed a series of experiments to test the susceptibility of 65-nm SPARC microprocessors to soft errors. Their experimental results show that without adequate hardware protection mechanisms, *e.g.*, error-correcting codes (ECCs), a system failure caused by soft errors will be observed every two and a half months. This failure rate is unacceptable, particularly for systems designed for critical applications, such as data centers and vehicle control.

Process variations are another source of soft errors because the threshold voltages of gates can be spread across a broad range, as shown in Figure 1.5. For instance, if a circuit is operated at a fixed supply voltage, then gates with high threshold voltages may not fully turn on, or work more slowly than expected. If such gates lie along critical paths, then incorrect results can easily be produced.

Finally, if a circuit's supply voltage is lower than a critical value, say the threshold voltage, the circuit can malfunction because some transistors no longer switch on or off correctly. Problems of this kind caused by insufficient supply voltages are called voltage overscaling. If circuits work at minimal voltage levels, noise margins cannot compensate for even slight voltage fluctuations, and voltage-overscaling problems result [12]. ICs designed for portable devices, such as mobile phones and laptops are especially prone to this issue. Their error rates (error probabilities) can grow dramatically with small decreases in supply voltage, as shown in Figure 1.9 [60].

Figure 1.9. Bit error rates for different voltage overscaling levels in a 16-bit ripple-carryadder using IBM 130 nm-process parameters; normal supply voltage is 1.35v [60].

We have illustrated several limitations of deterministic approaches for simulating typical EDA tasks and newly-arising non-deterministic effects. Unlike deterministic approaches, probabilistic analysis deals with these issues by modeling a circuit's characteristics with probabilities, and analyzing the circuit's statistical behavior. Probabilistic analysis usually provides *average* results based on statistical estimates. Such results can be treated as a circuit's representative behavior, which is very useful for designers. Exact probability calculation methods [48] also suffer from high computational complexity, but many heuristics have been proposed for mitigating the computational overhead, while making the calculation inaccuracies manageable.

Our work aims at improving the applicability of probabilistic analysis in two areas: signal probability calculation and soft error analysis. We propose three novel and powerful methods for improving accuracy as well as efficiency for general circuit sampling, signal probability representation, and reliability estimation in sequential circuits.

### **1.2 Signal Probability Analysis**

In this section, we define signal probability for logic circuits, discuss its basic calculation rules, and explain signal correlation, which is an important factor affecting calculation efficiency and accuracy.

The signal probability p(s) of a logic signal s indicates the likelihood that 1 rather than 0 can be observed on s. Signal probability is determined experimentally by applying N input vectors to an n-input circuit, either physically or by simulation, and counting the number k of 1s produced on s, in which case, p(s) = k/N. If the applied vectors are randomly generated, such simulation procedures for obtaining signal probabilities are referred to as Monte Carlo (MC) sampling, and the total number of applied samples (input vectors) is called the sample size. The number p(s) is considered to be *exact* if it equals  $p^*(s)$ , where  $p^*(s)$  is defined as the signal probability obtained when  $N = 2^n$ , and the applied vectors are all different, i.e., when the simulation is exhaustive. Clearly,  $p^*(s)$  is the fraction of 1s in the truth table for *s*. Consider the four-input circuit of Figure 1.10. If it is simulated with all 16 different input vectors as shown, then we obtain *z*'s exact signal probability  $p^*(z) = 0.5$ .

Figure 1.10 Signal probability estimation via exhaustive simulation.

Another approach for obtaining signal probabilities is probabilistic analysis. Consider the two-input AND gate  $g_{and}$  as shown in Figure 1.11(a) with inputs  $x_1$  and  $x_2$ . Its exact output signal probability can be expressed as  $p^*(g_{and}) = p^*(x_1) \times p^*(x_2) = 0.25$ because the probability of the AND gate being 1 is the probability of all its two inputs being 1. Similarly, for a two-input OR gate  $g_{or}$  in Figure 1.11(b), its probability of outputting 0 is the probability of all its inputs being 0, which can be expressed as  $1 - p^*(g_{or}) = (1 - p^*(x_1)) \times (1 - p^*(x_2))$ . Hence, this OR gate's exact output signal probability is given by  $p^*(g_{or}) = 1 - (1 - p^*(x_1)) \times (1 - p^*(x_2)) = 0.75$ .

Figure 1.11. Circuit symbol and truth table of (a) a two-input AND and (b) a two-input OR gates.

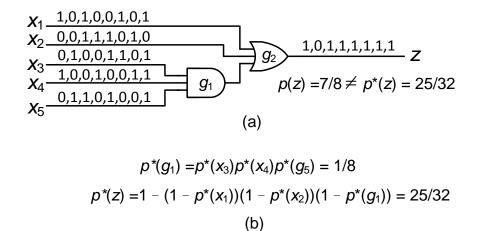

Figure 1.12 illustrates how to calculate signal probabilities via two different approaches. In Figure 1.12(a), the circuit output signal probability p(z) is estimated by MC sampling. The circuit is simulated with eight input vectors selected randomly from 32 possibilities, and p(z) is calculated as the fraction of 1s in *z*'s output sequence, which is 7/8. If p(z) in is evaluated by the first four samples shown, then p(z) becomes 3/4, which is less accurate than the estimated result from eight samples. In the MC method, higher accuracy is achieved by applying more samples (input vectors). To be effective, however, MC must achieve a proper balance between computational effort and accuracy. Too few samples provide insufficient accuracy, while too many lead to excessive runtimes.

Figure 1.12. Signal probability estimation for a five-input circuit via (a) MC sampling and (b) probabilistic analysis.

Figure 1.12(b) shows how p(z) is evaluated using probabilistic analysis. Here the circuit is traversed from primary inputs to primary output, and the signal probabilities of the individual gates are calculated. For instance,  $p^*(g_1)$  is first calculated from the signal probabilities of its input signals,  $p^*(x_3)$ ,  $p^*(x_4)$ , and  $p^*(x_5)$ . Then,  $p^*(z) = p^*(g_2)$  is obtained from  $p^*(x_1)$ ,  $p^*(x_2)$ , and  $p^*(g_1)$ . In this case, the exact output signal probabilities can be obtained using probabilistic analysis because the structure of this circuit is relatively simple. In general, the computational overhead and accuracy of probabilistic analysis is strongly affected by circuit structure.

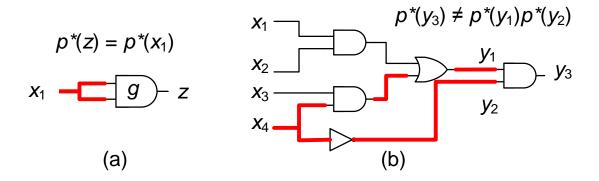

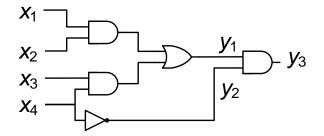

If a gate's inputs that are controlled by one or more common primary inputs, then these inputs should not be treated as separate independent signals. Instead, they should be considered together to avoid calculation inaccuracy. Such dependency among signals is called *correlation*. A major challenge of probabilistic analysis is how to handle correlation among signal probabilities. We next discuss what signal correlation is and how it affects probabilistic calculations. Consider the two-input AND gate depicted in Figure 1.13(a) whose two input signals are tied together. The exact output signal probability,  $p^*(g) = p^*(x_1) = 0.5 \neq p^*(x_1) \times$  $p^*(x_1)$ . This is because in this case the two input signals originate from the same source, and the probability that g has two different input values is zero. Now consider another case depicted in Figure 1.13(b). Here,  $p^*(y_3)$  cannot be directly calculated from its local inputs; *i.e.*  $p^*(y_3) \neq p^*(y_1) \times p^*(y_2)$  because both  $y_1$  and  $y_2$  are controlled by  $x_4$ . Signal correlation problems of this kind are caused by fanout-reconvergence structures, which are shown with bold lines in Figure 1.13. From a statistical viewpoint, exact signal probabilities are signal probabilities where all correlations are accurately accounted for. This requires global calculations that encompass all fanout structures. However, the complexity of analyzing these structures in a circuit is exponential in circuit size [51], which implies that determination of exact signal probabilities tends to be intractable.

A key advantage of using MC sampling for calculating signal probabilities is that all signal correlations associated with the applied samples are automatically accounted for. By increasing the number of samples, the calculated probabilities can be made as close to the exact values as desired.

Figure 1.13 Two circuits with fanout-reconvergence structures marked with red bold lines.

### **1.3** Soft Error Modeling and Analysis

The effect of soft errors on a logic gate is generally described in terms of its *gate-error probability*, which indicates how likely an incorrect value will be generated by the gate due to soft errors. Such error probabilities are typically very small. Several studies indicate that the probabilities of an erroneous bit in one month of operation for 90-nm FPGAs and 65-nm DRAMs are  $1.38 \times 10^{-10}$  and  $8.25 \times 10^{-10}$ , respectively [30] [37].

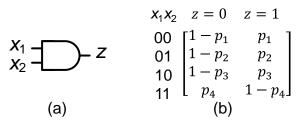

Two error types, which we refer to as conditional and unconditional, have been used in probabilistic methods to model the soft-error behavior of gates or other components. These have not always been clearly distinguished in the past. A *conditional* error model allows the error probability to vary with respect to different input vectors, while an *unconditional* error model requires the error probability to be constant, and therefore independent of the input vectors. Thus, unconditional models ignore correlations among a gate's inputs.

|                                                  | Input     | Output probabilities      |              | Input     | Output probabilities       |                            |

|--------------------------------------------------|-----------|---------------------------|--------------|-----------|----------------------------|----------------------------|

|                                                  | $x_1 x_2$ | <i>z</i> = 0              | <i>z</i> = 1 | $x_1 x_2$ | <i>z</i> = 0               | <i>z</i> = 1               |

| $X_1 - \sum_{z \in Z} Z_{z}$                     | 00        | 1 – <i>p</i> <sub>1</sub> | $p_1$        | 00        | 1 – <i>p<sub>err</sub></i> | $p_{err}$                  |

| $\mathbf{x}_2$ - $\mathbf{x}_2$ - $\mathbf{x}_2$ | 01        | 1 – <i>p</i> <sub>2</sub> | $p_2$        | 01        | 1 – p <sub>err</sub>       | $p_{err}$                  |

|                                                  | 10        | 1 – <i>p</i> <sub>3</sub> | $p_3$        | 10        | 1 – <i>p<sub>err</sub></i> | $p_{err}$                  |

|                                                  | 11        | $ ho_4$                   | $1 - p_4$    | 11        | p <sub>err</sub>           | 1 – <i>p<sub>err</sub></i> |

| (a)                                              | (b)       |                           |              |           | (c)                        |                            |

Figure 1.14 (a) Two-input AND gate, and its behavior with (b) a conditional gate error model, and (c) an unconditional gate error model.

Figure 1.14 illustrates the two error models for a two-input AND gate. The table in Figure 1.14(b) shows an example of a conditional error. For a gate g with output z, the conditional output probability of z associated with a particular input vector v is denoted by p(z|v). For example,  $p(z|x_1'x_2) = p(z|01) = p_1$  in Figure 1.14(b). Figure 1.14(c) defines an unconditional error model for the two-input AND gate. In this case, the error probabilities associated with all input vectors are the same, namely  $p_{err}$ . In general, a conditional error model for an *n*-input gate g can employ up to  $2^n$  distinct probability values to simulate a soft error. On the other hand, the unconditional model needs only one error probability value  $p_{err}$ . A conditional error model can simulate more complicated situations, while an unconditional one has much better scalability.

The parameter  $p_{err}$  is the probability that g outputs an incorrect value, which may be 0 or 1. The corresponding signal probability, denoted by  $p(g^e)$  is the probability of g outputting 1 when it is subject to errors. In the other words, p(g) and  $p(g^e)$  represent g's signal probabilities in the error-free and erroneous cases, respectively. For the two-input AND gate of Figure 1.14

$$p(g^{e}) = 0.25(p_{err} + p_{err} + p_{err} + (1 - p_{err})) = 0.25(1 + 2p_{err})$$

So, if  $p_{err} = 0.1$ , then  $p(g^e) = 0.3$ . We will show how to calculate the erroneous signal probabilities of individual gates later in Chapters 3 and 4.

We now explain how soft-error effects are measured. The *soft-error rate* (SER) is typically used for this purpose, and is defined in terms of gate vulnerability and circuit reliability. The *vulnerability* of a particular gate g represents how easily an erroneous value can be produced by g and can be propagated to the primary outputs. The *reliability*  of a circuit C indicates how likely an incorrect output caused by g will be observed at the primary outputs.

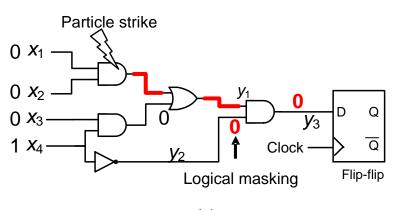

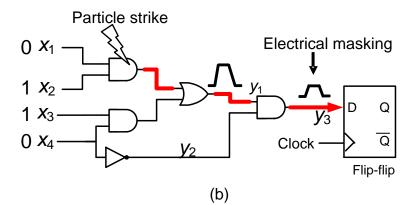

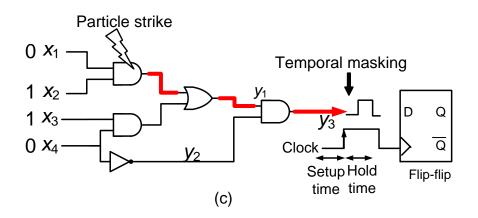

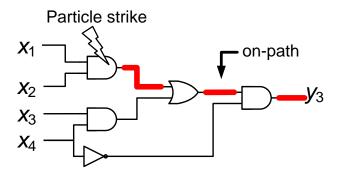

Whether or not an incorrect value (an error) can propagate to the primary outputs is determined by three masking effects: logic, electrical and temporal [45].

- *Logic masking*: all possible propagation paths of an erroneous signal to primary outputs are blocked by the circuit's connectivity, functionality or a combination of both.

- *Electrical masking*: the strength (voltage amplitude) of an erroneous signal gradually attenuates as the erroneous signal propagates, and the error eventually disappears before reaching a primary output.

- *Temporal masking*: An error signal is not stored by a memory element because the erroneous signal fails to satisfy the timing constraints, *e.g.*, the setup or hold times, of the memory element.

Figure 1.15 illustrates the three masking effects mentioned above. Suppose  $x_1x_2x_3x_4 =$  0001, making  $y_1y_2 = 00$ . If the value of  $y_1$  is flipped to 1 by a soft error, then  $y_1$ 's erroneous value will be blocked by  $y_2$ , as shown in Figure 1.15(a). In addition, observe that  $x_3$  is a redundant signal because  $y_3 = x_1x_2x_4'$ . Therefore, no erroneous value generated at  $x_3$  can propagate to the primary output. In Figure 1.15(b) an error successfully propagates to the primary output because no other signal can block the erroneous signal in this case. However, the erroneous signal's strength is decreasing as it propagates from  $y_1$  to  $y_3$ . If the signal strength falls below a threshold voltage, then an error cannot be captured and stored by the flip-flop (memory element). Finally, Figure 1.15(c) shows how an error fails to be stored by the flip-flop when it does not meet the flip-flop's timing

constraints, even though its signal strength does not greatly attenuate before it reaches the flip-flop. To be captured by the flip-flop an error should arrive before the setup time, and keep its logic value stable over the duration of the setup and hold times.

(a)

Figure 1.15 Illustration of three masking effects: (a) logical, (b) electrical, and (c) temporal.

Since our research focuses on evaluating SERs at the logic level, we only consider the logical masking effect because the electrical and temporal masking effects must generally be simulated at the transistor level with considerable computational effort, and are difficult to handle at the logic level.

We next introduce probabilistic transfer matrices (PTMs), which can efficiently represent a circuit's probabilistic behavior described by either conditional or unconditional error models.

### **1.4 Probabilistic Transfer Matrices**

Many probabilistic techniques have been developed for representing and estimating the SERs in logic circuits, such as the PTM approach [34], Bayesian networks (BNs) [48], and probabilistic decision diagrams (PDDs) [1]. We use the PTM approach because not only is it capable of simulating circuits with many different error models, but it also can provide accurate SER results due to the way it handles correlations. We will review and compare these probabilistic techniques later in Chapter 3.

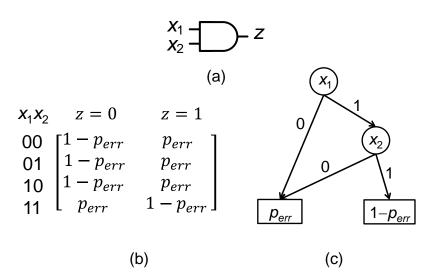

Krishnaswamy et al. were the first to propose PTMs for circuit reliability analysis [34]. PTMs can explicitly include the probability of every input-output combination associated with a logic gate or a combinational circuit. Hence, they provide a general way to represent conditional errors. Figure 1.16 shows the gate PTM for a two-input AND gate whose probabilistic behavior is described in Figure 1.14(b).

Figure 1.16. (a) Two-input AND gate, and (b) its PTM representation with a conditional error model.

Each PTM entry is a conditional probability associated with a corresponding input vector. For example in Figure 1.16(b), the probabilities of z being 1 associated with inputs  $x_1x_2 = 01$  and 10 are  $p(z|x_1'x_2) = p_2$  and  $p(z|x_1x_2') = p_3$ , respectively. To reduce memory usage, matrices can be stored in the form of algebraic decision diagrams (ADDs) [10]. Like reduced ordered binary decision diagrams (ROBDDs) [16], ADDs have multiple terminal nodes to represent signal probability values, and provide a compact and canonical way to represent the probabilistic behavior associated with individual input vectors for a gate or an entire circuit.

Again, we use a two-input AND gate to illustrate the use of ADDs to reduce memory needs. Suppose the AND gate's error behavior is described by the unconditional error probability  $p_{err}$ . Figure 1.17(c) shows an ADD representation of the AND gate's PTM. A path from node  $x_1$  to a terminal node represents a complete or partial input assignment u, and the linked terminal indicates the output probability of being 1 associated with u. For instance, the path between node  $x_1$  and terminal  $p_{err}$  indicates  $p(z|x_1') = p_{err}$ , without considering  $x_2$ 's value. If  $x_1 = 1$ , the ADD needs to use  $x_2$ 's value to determine the output probability. The path between nodes  $x_1$ ,  $x_2$  and terminal  $1 - p_{err}$  represents  $p(z|x_1x_2) = 1 - p_{err}$ .

Figure 1.17. (a) Two-input AND gate, (b) its gate PTM with unconditional error  $p_{err}$ , and (c) its ADD representation.

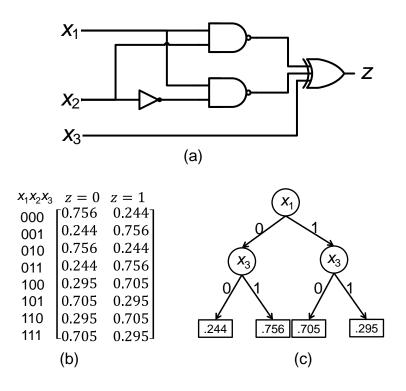

For a combinational circuit *C*, the basic PTM construction algorithm first generates a level PTM for each circuit level, and then merges level PTMs to form a circuit PTM. The signal probabilities of the primary outputs can then be obtained from the circuit PTM by matrix operations. All correlations among signals are implicitly accounted for when generating the circuit PTM. Hence, the SER of a circuit can be accurately computed from the circuit PTM by comparing the differences between the error-free and erroneous versions of the circuit's output signal probabilities.

Figure 1.18 shows a three-input circuit, its PTM, and the corresponding ADD, assuming an unconditional gate-error probability  $p_{err} = 0.1$ . Like a gate PTM, the circuit PTM represents *z*'s signal probabilities associated with all possible input vectors. This ADD form is more compact because it has only seven nodes, whereas the PTM contains 16 entries.

Figure 1.18. (a) Three-input circuit, (b) its circuit PTM for  $p_{err} = 0.1$ , and (c) the corresponding ADD.

Although the basic PTM algorithm handles the general conditional error model and accounts for all signal correlations, its practical use is limited to relatively small circuits, as the effort of accurately handling and preserving signal correlations can be huge. In addition, since circuit PTMs only store the conditional probabilities of primary outputs with respect to primary inputs, evaluating signal probabilities for individual gates of a circuit can be difficult. Like ROBDDs [16], the size of the ADDs representing PTMs highly depends on the variable ordering, and determining the best order is an NP-hard problem [34]. In Chapter 4, we develop a novel way to simplify the PTM construction process by combining circuit partitioning with a fast fault simulation technique.

### 1.5 Thesis Outline

We have illustrated the need for probabilistic analysis in various EDA areas, and have discussed the challenges to applying this approach. This dissertation focuses on two particular issues: (1) providing a general circuit sampling methodology that can generate more accurate signal probabilities than Monte Carlo sampling, and (2) establishing a framework for efficiently and accurately evaluating soft-error effects in logic circuits.

As discussed above, MC plays an important role in probabilistic analysis. It can estimate signal probabilities and provide a gold reference for validating the effectiveness of EDA heuristics. However, MC requires many samples to achieve high accuracy, particularly in large circuits. In Chapter 2, we propose the use of partial signal redundancy and observability to solve this scalability problem. We examine the degree of redundancy in individual signals by analyzing a circuit's structure. This helps to identify unnecessary samples and arrange sample sequences effectively.

Chapter 3 introduces a novel trigonometric model that unifies the representation of signal and unconditional error probabilities in combinational circuits. This unification reduces the computational complexity by mapping multiplications in probabilistic calculations into angular rotations (additions) within trigonometric operations.

In Chapter 4, we develop a PTM-based probabilistic calculation method for SER that is able to simulate a sequential circuit without excessive circuit duplication. We partition the circuit in a way that guarantees that the size of the resultant PTMs is manageable, and apply a fault simulation technique that accounts for signal correlation and masking effects. Since the time-frame expansion technique is not used, our method requires no additional memory when simulating sequential circuits. This property makes our

27

approach capable of tracing the accumulated error effects in a sequential circuit over many simulation cycles.

Finally, we summarize our key contributions and discuss several possible research topics as extensions of this work.

## **CHAPTER 2**

#### **Circuit Sampling for Signal Probability Calculation**

In this chapter, we introduce a new circuit sampling methodology for calculating signal probability in error-free combinational circuits. As stated in Chapter 1, MC (Monte Carlo) sampling is a general method of signal probability estimation; however, it has the disadvantage that the sample size grows rapidly with increasing accuracy levels. To improve the scalability of MC, we apply the concept of signal redundancy to circuit sampling. We prioritize primary inputs, and compress the sample space by analyzing the degree of redundancy and observability of individual signals. Our simulation results show that the proposed sampling method can improve the simulation efficiency by from one to three orders of magnitude, even in large benchmark circuits. A paper based on this work has been accepted for presentation at the 2012 International Conference on Computer-Aided Design [69].

# 2.1 Background

As noted in the preceding chapter, signal probabilities are basic to non-deterministic analysis, and MC is a natural way to calculate signal probabilities in logic circuits. In fact, MC is a widely-used technique in EDA that serves several purposes. It is used as an evaluation method when analytical approaches are infeasible, and it often serves to validate heuristic problem-solving techniques. For example, Sauer et al. present a SATbased timing analysis technique whose results are "validated by comparison to an exact (Monte Carlo) simulation approach" [52]. Other EDA tasks commonly validated by MC include testability and power estimation [58], circuit synthesis [18], and design verification [57]. In some cases, MC is central to the main solution methodology [70].

However, conventional MC suffers from high simulation complexity particularly in large circuits due to the many samples that need to be applied. In statistics, the simulation efficiency of MC for specific functions can sometimes be enhanced by using the properties of the target functions [27]. Recently, several sampling methods for analog circuits have been proposed [31][56] for improving sample accuracy. For instance, Singhee and Rutenbar apply a quasi-Monte Carlo (QMC) technique [56] for simulating the process variation effects. However, these algorithms cannot be directly applied to digital circuits, because analog circuits are modeled by continuous functions, while digital circuits are described by Boolean functions with discrete binary values.

In this chapter, we will introduce a general sampling methodology aimed at signal probability analysis for logic circuits. Prior work on logic circuit sampling just generates random samples without considering the functionality and connectivity of the target circuit. Our proposed method can provide more accurate results by removing unnecessary samples, and by arranging the samples based on the degree of importance of the input signals.

In the next section, we briefly review several representative probability calculation methods to clarify the advantages and limitations of prior work, and the need for developing new probability calculation techniques, such as sampling in logic circuits.

30

### 2.2 Prior Work

As mentioned in Chapter 1, Parker and McCluskey proposed a method [46] that can calculate exact signal probabilities for logic circuits. Given a circuit C, the Parker-McCluskey method traverses C from primary inputs to primary outputs, and calculates the signal probabilities of C's individual gates using the rules shown in Table 2.1.

Gate typeProbability calculation rulePrimary input  $x_i$  $p^*(x_i) = 0.5$ NOT $p^*(z) = 1 - p^*(x)$ AND $p^*(z) = \prod_{i=1}^n p^*(x_i)$ NAND $p^*(z) = 1 - \prod_{i=1}^n p^*(x_i)$ OR $p^*(z) = 1 - \prod_{i=1}^n (1 - p^*(x_i))$ NOR $p^*(z) = \prod_{i=1}^n (1 - p^*(x_i))$

Table 2.1 Signal probability calculation rules for an *n*-input elementary gate  $z(x_1, x_2, ..., x_n)$  with independent inputs.

If a gate g's inputs are not independently controllable from the primary inputs of *C*, then the signal probability of g's output cannot be directly calculated from g's inputs alone. To account for correlations, the Parker-McCluskey method calculates g's signal probability in terms of the signal probabilities of *C*'s primary inputs. In other words, if g's Boolean function is  $f(g) = f(x_1, x_2, ..., x_m)$ , then p(g) is expressed in terms of  $p(x_1)$ ,  $p(x_2), ..., p(x_m)$ , and correlations among gate g can be accounted for when p(g) is accurately expressed with  $p(x_i)$ .

Consider the circuit in Figure 1.13(b), which is copied in Figure 2.1. The exact output signal probability  $p(y_3)$  is expressed as

$$p^{*}(y_{3}) = (1 - (1 - p^{*}(x_{1})p^{*}(x_{2}))(1 - p^{*}(x_{3})p^{*}(x_{4})))(1 - p^{*}(x_{4}))$$

which can be simplified to

$$p^{*}(y_{3}) = p^{*}(x_{1})p^{*}(x_{2})(1 - p^{*}(x_{4})) = 0.125$$

It is worth noting that in this case,  $x_3$  is a redundant signal because the Boolean function  $y_3 = x_1 x_2 x_4'$  is independent of  $x_3$ . Hence  $p^*(x_3)$  is irrelevant to  $p^*(y_3)$ .

Figure 2.1. Four-input circuit (copy of Figure 1.13(b)).

Although the Parker-McCluskey method can compute exact signal probabilities, the complexity of completely accounting for all signal correlations makes it exponential in circuit size [46], and therefore impractical for large circuits.

Several heuristic approaches have been developed to reduce the complexity of handling signal correlations. We review three representative heuristic calculation approaches, namely the controllability/observability program (COP) [14], the correlation coefficient method (CCM) [25], and the Boolean approximation method (BAM) [58]. These address the signal-correlation problem by only considering correlations at individual topological levels, or by ignoring cases considered to have insignificant impact. We discuss these three heuristics because they have been adopted in several different application areas, including testability [14], switching activity [59], and reliability analysis [19][68]. Their accuracy is measured by comparing their signal probability results to the results generated by MC simulation [14][25][58].

Brglez developed a fast probability calculation method COP [14] that ignores correlation. COP therefore assumes all gate inputs in a circuit are independent, which can lead to huge calculation inaccuracy [25]. Again, taking the circuit in Figure 2.1 as an example,  $y_3$ 's exact signal probability and its signal probability from the COP method are 0.125 and 0.21875, respectively, making the calculation inaccuracy 75%.

Ercolani et al. [25] developed the CCM method, which calculates signal probabilities by only considering correlations within a single topological level. Given a circuit *C*, CCM first levelizes *C*, and then accounts for signal correlations among each pair of signals at the same level. This method reduces the computational complexity of handling correlation from exponential to quadratic. In the case of Figure 2.1, the total number of correlation cases that need to be enumerated is  $\binom{4}{2} + \binom{3}{2} = 9$ . CCM is exact for circuits with simple structures, such as the circuit in Figure 2.1, even though it does not account for all possible correlations.

The complexity of the signal correlation problem can be further reduced by carefully analyzing circuit structure. In Figure 2.1, for example,  $x_4$  is the only cause of this problem because its signal probability can propagate to the primary output along different paths. Uchino et al. [58] have proposed another approach called BAM that estimates a gate's correlations associated with individual primary inputs. In the Figure 2.1 case, while CCM accounts for the correlations of every pair of signals at each level, BAM recognizes  $x_4$  is the only signal with multiple branches, and then only considers correlation when evaluating  $p(y_3)$ . This is because  $y_3$  is the only signal affected by  $x_4$  via multiple paths. In this case, like CCM, BAM yields the exact signal probabilities. It is worth noting that unlike COP and CCM, Uchino et al. [58] not only derive the complexity of BAM, but also provide an analytical upper bound of its calculation inaccuracy. Such information is crucial when we need to make a fair comparison among multiple heuristic approaches.

Although the foregoing heuristics provide fast signal probability estimation, their calculation accuracy varies from circuit to circuit. In addition, some methods [14][25] are not based on well-defined mathematical models, but are just ad-hoc solutions. Hence, measuring the quality of these methods e.g., identifying analytical bounds on their calculation inaccuracy, is difficult or even impossible.

Unlike the aforementioned heuristic approaches, MC sampling is a well-studied statistical technique whose simulation accuracy is manageable and is fully determined by the number of applied samples. Since MC can provide highly accurate results if necessary, it is suitable for validating the performance of heuristics. In the next section, we study the use of signal redundancy for simplifying the sampling complexity in logic circuits.

### 2.3 Signal Redundancy

We now propose ways to exploit a circuit's redundancy properties to speed up signal probability estimation. To illustrate, consider the circuit in Figure 1.10, which is copied in Figure 2.2, and realizes  $z(x_1, x_2, x_3, x_4) = x_1'x_2 + x_1x_3$ . Input  $x_4$  is *redundant* in the usual sense that z is independent of  $x_4$ , a fact that can be exploited to reduce sampling effort. While exhaustive simulation of a four-input circuit requires 16 samples, the *full* redundancy of  $x_4$  reduces the circuit to a three-input one that can be exhaustively simulated with only 8 samples. The sample input vectors shown on the figure apply all possible combinations to the non-redundant inputs  $x_1$ ,  $x_2$  and  $x_3$ , so the simulated value of p(z) is exact.

Figure 2.2. Circuit illustrating signal probability estimation via sampling; (copy of Figure 1.10).

Of course, fully redundant inputs such as  $x_4$  in the above example rarely occur in practice. We address a new type of *partial redundancy* where independence on input variables is conditional on specific values applied to other variables. For instance, *z* in Figure 2.2 becomes independent of  $x_2$  and  $x_3$ , when  $x_1 = 1$  and 0, respectively. Hence,  $x_2$ and  $x_3$  can be considered partially redundant with respect to  $x_1$ . Most of a circuit's primary inputs are partially redundant; however, the degree of their redundancy varies widely. Some inputs become redundant much more often than others. We will show how such partial redundancies can be exploited to speed up simulation.

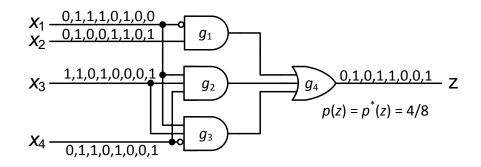

We propose an extension to the MC approach we call *Reduced-Ordered Monte Carlo* (ROMC), which has better performance than conventional MC. It incorporates two main techniques to improve the quality of circuit simulation. The first technique orders and prioritizes the primary inputs according to their *observability*. For instance, consider the problem of estimating the signal probability of  $z_1$  in Figure 2.3. Some primary inputs such as  $x_{10}$  are more observable at  $z_1$  than others, and some, such as  $x_2$ , are difficult to observe. Low-observability primary inputs tend to become partially redundant due to other primary input assignments, while high-observability primary inputs are unlikely to become redundant. The concepts of observability and redundancy discussed here are loosely related to the influence property of Boolean functions [33], and observability as used in the testing context [15]. We employ the SCOAP testability measurement heuristic [15] to quickly find the most observable primary inputs.

Figure 2.3. Ten-input, two-output circuit; a multiplexer-like structure formed by  $g_6$ ,  $g_7$  and  $g_8$  is highlighted.

The second technique involves finding *compatible* primary inputs, which have the property that only one of the primary inputs can affect certain primary outputs at any time. This relation among input variables can also be interpreted as a kind of partial redundancy. For example,  $x_4$  and  $x_5$  in Figure 2.3 are compatible primary inputs with respect to primary output  $z_1$ . If  $x_3 = 1$  (0), then  $z_1$  becomes independent of  $x_4$  ( $x_5$ ). So both  $x_4$  and  $x_5$  are partially redundant primary inputs associated with  $x_3$ , and they do not affect

output  $z_1$  at the same time. Such behavior resembles that of a multiplexer, whose control (select) signals ensure that only one data input  $D_i$  is connected to the multiplexer's output at a time; the others are effectively masked. The data inputs  $\{D_i\}$  are viewed here as compatible. More generally, we find compatibility relations among the inputs of multiplexer-like structures. One such structure is marked by dashed lines in Figure 2.3, where  $x_1$  and  $x_8$  are compatible with respect to  $x_2$ ,  $x_5$  and  $x_6$ . We will show that compatible primary inputs can share resources, such as input samples or randomness sources that drive the samples. This can lead to large efficiency gains in signal probability estimation.

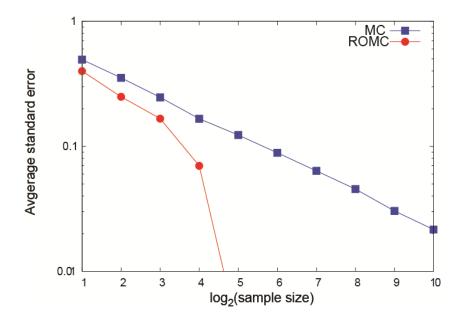

Figure 2.4. Accuracy comparison between ROMC and a typical MC calculation of the average output signal probability for the circuit in Figure 2.3.

Figure 2.4 illustrates the accuracy improvement from applying ROMC to the circuit in Figure 2.3. Here, accuracy is measured in terms of standard error [27], and refers to the difference between the exact probability  $p^*(z)$  and the probability p(z) estimated by the

simulation for various sample sizes; the errors are averaged over the two outputs  $z_1$  and  $z_2$ . For a given accuracy level, ROMC is significantly faster than MC because it achieves the required accuracy with fewer samples. Furthermore, in this case, ROMC can produce exact signal probabilities with only 32 samples.

#### 2.4 Sampling Concepts

This section reviews some basic concepts that are needed later. First, we formalize the signal probability estimation problem introduced in the previous section, and then discuss some basic properties of MC simulation. Lastly, we review the Boole-Shannon expansion.

We formulate signal probability computation in general terms, so that it applies to many different EDA situations. The *signal probability estimation problem* may be stated as follows. Given a combinational circuit *C* (including the pseudo-combinational equivalent of a sequential circuit) with *n* primary input and *m* primary output signals, as well as a set of *N* sample input sequences, calculate the (average) signal probabilities of the primary outputs. Figure 2.2 illustrates this for n = 4, m = 1 and N = 8. We make the usual assumption [25][58] that each primary input  $x_i$  has signal probability  $p(x_i) = 0.5$  and is independent of all other primary inputs. This means that their joint probability distribution is the product of their individual distributions, and captures the informal notion of "random" sampling.

Consider a *n*-input, single-output circuit *C* that implements the Boolean function  $z(x_1,x_2,...,x_n)$ , where the primary inputs have the same signal probability  $p(x_i) = 0.5$  and are all independent. The signal probability estimation problem for *C* is to determine  $p^*(z)$ .

Since it is usually not feasible to find the exact value of  $p^*(z)$  if *C* is large, we aim to find an *estimator* probability p(z) that provides a good estimate of  $p^*(z)$ . For a given estimator p(z), a bias  $\beta$  and a variance var[p(z)] are defined as follows [27]:

$$\beta = E[p(z) - p^{*}(z)]$$

(2.1)

$$var[p(z)] = E[(p(z) - p^*(z) - \beta)^2]$$

(2.2)

where E[X] denotes the expected value of X. The square root of the variance of an estimator is its *standard error*. It is usually desirable for an estimator to have  $\beta = 0$ , in which case it is called *unbiased*, and to have a small variance [27]. An unbiased estimator with variance zero is exact, that is,  $p(z) = p^*(z)$ .

MC is a method of estimating  $p^*(z)$  by applying N uniform and independent random samples to the primary inputs and collecting N samples at the output z. Let z(i) denote the  $i^{\text{th}}$  value of z associated with the  $i^{\text{th}}$  sample. The estimator p(z) can be defined as

$$p(z) = (1/N)\sum_i z(i)$$

It can be shown that p(z) in this case is unbiased [27] and that the variance of the estimation is

$$var[p(z)] = (1/N) p^{*}(z) (1 - p^{*}(z))$$

(2.3)

So the variance and the standard error of an MC simulation can be reduced by increasing the sample size *N*. However, reducing the standard error by a factor of *k* requires the sample size to be increased by factor of  $k^2$  making it impractical if the desired error level is low. Consequently, many techniques for variance reduction without increasing *N* have been proposed [27][49]. The method proposed in this dissertation can be seen as another variance reduction technique.

Although the input samples for MC are usually assumed to be independent, which allows samples to be repeated, it is also possible to use MC with non-repeating samples [49]. We call the former *MC with sample replacement* (MCW) and the latter *MC without sample replacement* (MCWO). Like MCW, MCWO is an unbiased estimation method, but its variance follows that of a hypergeometric distribution [49]. For an MCWO estimator p(z)

$$E[p(z)] = p^{*}(z)$$

$$var[p(z)] = (1/N)p^{*}(z)(1 - p^{*}(z)) (2^{n} - N)/(2^{n} - 1)$$

Recall that *n* denotes the number of the primary inputs in *C*. For a fixed sample size *N*, if the number of primary inputs *n* is reduced by some number, then the variance will definitely become smaller. The change can be significant if *N* is comparable to  $2^n$ . This is not true in the case of MCW since its variance is independent of *n*. This fact turns out to be important in our proposed method since we aim at reducing the sample space of the MC, and can benefit from it only if we use non-repeating samples.

Finally, we summarize the Boole-Shannon expansion and provide a compact version for later use. An *n*-variable Boolean function F(X) can be expanded around any variable  $x_i$  according to the following formula [26]

$$F(x_1, x_2, ..., x_i, ..., x_n) = x_i' \cdot F_{xi'} + x_i \cdot F_{xi}$$

where  $F_{xi'} = F(x_1, x_2, ..., 0, ..., x_n)$  and  $F_{xi} = F(x_1, x_2, ..., 1, ..., x_n)$  denote the negative and positive *cofactors* of *F*, respectively, with respect to  $x_i$ .

For example, consider the function generated by  $g_8$  in Figure 2.3. It can be expanded around  $x_3$  thus:

$$g_8(x_1, x_2, x_3, x_4, x_5, x_6) = x_3'((x_1x_2)' + x_4) + x_3(x_5x_6)'$$

The negative and positive cofactors are  $(x_1x_2)' + x_4$  and  $(x_5x_6)'$ , respectively. The variable  $x_4$  ( $x_5$ ) does not appear in the positive (negative) cofactor due to partial redundancy; the value of  $x_3$  always blocks the propagation path from  $x_4$  ( $x_5$ ) to  $g_8$ .

As this example suggests, Boole-Shannon expansions and cofactors provide a tool for describing signal compatibility. We can also express signal probabilities in terms of cofactors:

$$p^*(F) = \frac{1}{2^k} \sum_{0}^{2^k - 1} p^*(F_i)$$

(2.4)

It is also useful to define the Boole-Shannon expansion with respect to a product of k variables  $X_k \subseteq X$ . In this case, we are dealing with cube cofactors [26] such as  $F_{x1'x2'...xk'}$  and  $F_{x1x2...xk}$ . With this notation, cofactors are awkward to write, so we denote  $F_{x1'x2'...xk'}$  by  $F_0$ ,  $F_{x1'x2'...xk}$  by  $F_1$ , and  $F_{x1x2...xk}$  by  $F_{2^{k-1}}$ . The cube expansion around  $X_k$  can then be expressed compactly as

$$F(X) = x_1' x_2' \dots x_k' F_0 + x_1' x_2' \dots x_k F_1 + \dots + x_1 x_2 \dots x_k F_{2^{k-1}}$$

(2.5)

#### 2.5 Variable Ordering

As discussed in Section 2.3, fully redundant primary inputs can be exploited to reduce the sample size for simulation, simply by not wasting samples on them. Similarly, the partially redundant, or less observable, primary inputs that become redundant frequently can be ignored in favor of more observable ones. (Of course, we cannot ignore them completely like redundant primary inputs.)

Accordingly, we propose the following sampling approach. Suppose we want to use  $N = 2^k$  samples to estimate the signal probability p(F) of function F with an n-member input set X. Select k variables  $X_k = x_1, x_2, ..., x_k \subseteq X$  that are more observable than the

others. Generate *N* samples that include every possible value of  $X_k$  exactly once, and assign random values to the remaining n - k variables. The following samples illustrate this for k = 3 and n = 9

| $x_1 x_2 x_3$ | $x_4 x_5 x_6 x_7 x_8 x_9$ |

|---------------|---------------------------|

| 0 0 0         | 0 1 0 1 1 0               |

| 0 0 1         | 1 0 1 1 0 1               |

| 0 1 0         | 0 1 0 1 1 1               |

| 0 1 1         | 0 1 1 1 0 0               |

| 1 0 0         | 1 1 1 0 1 0               |

| 1 0 1         | 1 0 1 1 1 0               |

| 1 1 0         | 1 0 0 1 0 1               |

| 1 1 1         | 1 1 0 1 0 0               |