# Applications of Semiconductor Nanowires for Nanoelectronics and Nanoelectromechanical Systems

by

Wayne Y. Fung

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosphy (Electrical Engineering) in The University of Michigan 2012

#### **Doctoral Committee:**

Associate Professor Wei Lu, Chair Professor L. Jay Guo Associate Professor Cagliyan Kurdak Assistant Professor Zhaohui Zhong Copyright Wayne Y. Fung 2012

### **Dedication**

To my parents

#### Acknowledgements

This work would not have been possible without the support of many people. First of all I would like to thank my advisor, Prof. Wei Lu, for his patient guidance and unfailing support over the years. Second, I would like to thank my thesis committee members for their helpful discussions: Prof. Zhaohui Zhong, Prof. L. Jay Guo, and Prof. Cagliyan Kurdak. I am also grateful to them for research assistance (e.g. Prof. Kurdak generously allowed me to use his NPGS electron-beam lithography system). Third, I would like thank my fellow group members: Lin Chen, Siddharth Gaba, Ting Chang, Patrick Sheridan, Shinhyun Choi, Jiantao Zhou, Chao Du, Dr. Yuchano Yang, and Dr. Taeho Moon. In particular, I am grateful to Lin Chen with whom I had a very fruitful and enjoyable collaboration for the vertical Ge nanowire research. Fourth, I would like to thank former group member Seok-Youl Choi with whom I had a very fruitful and enjoyable collaboration for the Al-catalyzed Si nanowire research. Fifth, I gratefully acknowledge the technical support of the Lurie Nanofabrication Facility (LNF) staff and the Electron Microbeam Analysis Laboratory (EMAL) staff. In particular, I would like to acknowledge the following LNF staff members for their special assistance: Dennis Schweiger, Brian VanDerElzen, Matt Oonk, Pilar Herrera-Fierro, Greg Allion, Russ Clifford, Tony Sebastian, David Sebastian. I would also like to acknowledge EMAL staff members Dr. Kai Sun and Dr. Haiping Sun for their special assistance.

Finally I am utterly grateful to my parents, Dr. Daniel Fung and Kam Lee, for their unconditional love and support. Love you mom and bob!

## **Table of Contents**

| Dedicationii                                                            |

|-------------------------------------------------------------------------|

| Acknowledgementsiii                                                     |

| List of Figuresix                                                       |

| Chapter 1 Overview                                                      |

| Chapter 2 Growth of Si, Ge, and Ge/Si core/shell nanowires: toward CMOS |

| integration12                                                           |

| 2.1: Introduction                                                       |

| 2.2: Overview of the nanowire growth process                            |

| 2.3: Growth and electrical properties of Al-catalyzed Si nanowires16    |

| 2.3.1: Growth of small-diameter nanowires with high yield18             |

| 2.3.2: Recovery of semiconductor behavior at small diameter22           |

| 2.3.3: Possible mechanisms of carrier concentration reduction26         |

| 2.4: Vertical integration of Ge nanowires on Si for high-performance    |

| nanoelectronics                                                         |

| 2.4.1: Material system: Ge/Si core/shell nanowires31                    |

| 2.4.2. Vertical epitaxial growth of Ge panowires on Si (111)            |

| 2.4.3: Ge buffer layer for nanowire location control and high growth            |

|---------------------------------------------------------------------------------|

| yield39                                                                         |

| 2.4.4: Post-growth Au catalyst removal42                                        |

| 2.5: Summary43                                                                  |

| Chapter 3 Toward Ge nanowire-based vertical tunnel field-effect transistors for |

| hybrid nanowire-CMOS systems44                                                  |

| 3.1: Introduction44                                                             |

| 3.1.1: Subthreshold non-scaling in CMOS44                                       |

| 3.1.2: The tunnel field-effect transistor46                                     |

| 3.1.3: TFET using a vertical Ge NW grown on Si48                                |

| 3.1.4: Chapter overview52                                                       |

| 3.2: Esaki tunnel diodes based on vertical Si-Ge nanowire heterojunctions53     |

| 3.2.1: Vertical diode fabrication54                                             |

| 3.2.2: High performance at room temperature56                                   |

| 3.2.3: Temperature dependence indicates low-defect density57                    |

| 3.3: Prospects for ultrasharp vertical nanowire-based Si-Ge heterojunctions     |

| for tunnel field-effect transistor applications62                               |

| 3.3.1: Vertical growth of Ge nanowires on Si nanopillars for optimal            |

| vertical FET gate alignment63                                                   |

| 3.3.2: Sub-eutectic growth of vertical epitaxial Ge nanowires on Si for             |

|-------------------------------------------------------------------------------------|

| ultrasharp heterojunctions65                                                        |

| 3.4: Prospects for vertical junctionless field-effect transistors based on Ge/Si    |

| core/shell nanowires67                                                              |

| 3.4.1: Introduction to junctionless FET68                                           |

| 3.4.2: Device proposal and preliminary electrical measurements70                    |

| 3.4.3: Fabrication developments73                                                   |

| 3.5: Summary75                                                                      |

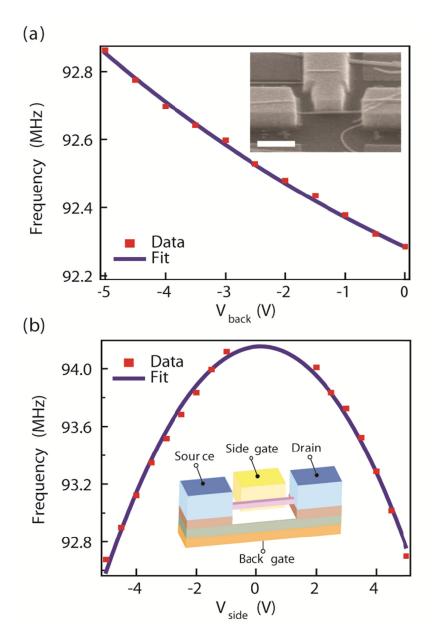

| Chapter 4 Radio frequency nanowire resonators and <i>in situ</i> frequency tuning76 |

| 4.1: Introduction                                                                   |

| 4.2: Device fabrication80                                                           |

| 4.3: Electrical actuation/detection setup83                                         |

| 4.4: High Q achieved at room temperature and size scaling84                         |

| 4.5: Nonlinear operation85                                                          |

| 4.6: In situ frequency tuning87                                                     |

| 4.6.1: Discussion of tuning mechanisms89                                            |

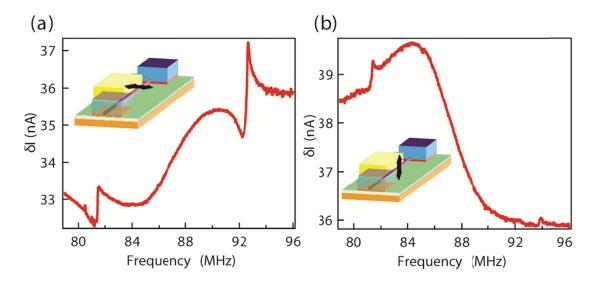

| 4.7: Selective actuation of different vibrational modes91                           |

| 4.8: Summary92                                                                      |

| Chapter 5 Conclusion94                                                              |

| 5.1: Nanowire growth techniques for hybrid nanowire-CMOS systems94                  |

| 5.2: Toward a Ge nanowire-based vertical tunnel FET | 96  |

|-----------------------------------------------------|-----|

| 5.3: Nanowire-based NEMS                            | 97  |

| 5.4: Final remark                                   | 98  |

| References                                          | 100 |

# **List of Figures**

| FIG. 1 Example of semiconductor nanowires                                           |

|-------------------------------------------------------------------------------------|

| FIG. 2 Trend in transistor geometry toward a gate-all-around structure              |

| FIG. 3 Trend in power density in CMOS technology                                    |

| FIG. 4 Technology scaling trends of power supply voltage $V_{dd}$                   |

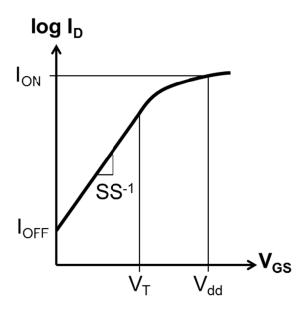

| FIG. 5 Qualitative transfer characteristics of a conventional MOSFET                |

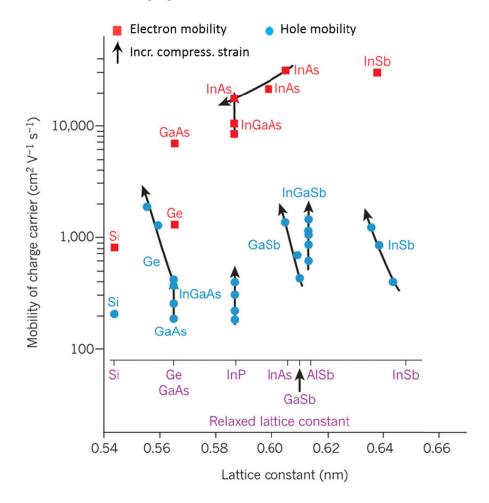

| FIG. 6 Reported III-V, Si, and Ge room-temperature mobilities of electrons (red     |

| squares) and holes (blue circles) as a function of lattice constant                 |

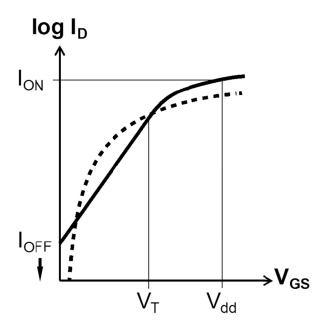

| FIG. 7 Qualitative transfer characteristics comparing MOSFET (solid line) and TFET  |

| (dashed line)                                                                       |

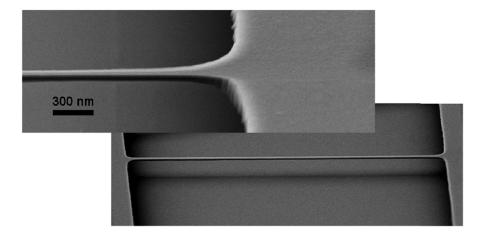

| FIG. 8 Example of a doubly clamped nanomechanical beam resonator                    |

| FIG. 9 Example binary alloy phase diagram illustrating the VLS process for nanowire |

| growth15                                                                            |

| FIG. 10                                                                             |

| (a) Schematic of the Al–Si binary phase diagram                                     |

| (b) SEM image of Al-catalyzed Si nanowires                                          |

| (c) Diameter distribution of Al-catalyzed Si NWs grown at 520 $^{\circ}\mathrm{C}$  |

| (d) Same as (c) but with 75 Torr SiH <sub>4</sub> partial pressure                                |

|---------------------------------------------------------------------------------------------------|

| FIG. 11                                                                                           |

| (a) Transfer curve ( $I_{DS}$ - $V_{GS}$ ) at $V_{DS}$ = $-0.1$ V for a device with diameter = 23 |

| nm.                                                                                               |

| (b) Family of $I_{DS}$ - $V_{DS}$ curves for the same device in (a)                               |

| (c) Family of $I_{DS}$ - $V_{DS}$ curves for another device with diameter = 40 nm                 |

| (d) Family of $I_{DS}$ - $V_{DS}$ curves for another device with diameter = 80 nm                 |

| FIG. 12                                                                                           |

| (a) Measured carrier concentration (squares) vs nanowire diameter shown in semilog plot           |

| (b) Measured field-effect mobility vs nanowire diameter                                           |

| FIG. 13 and diagram and schematic showing the surface depletion region (dark                      |

| annular region) due to trapped holes at the surface of a p-type nanowire2                         |

| FIG. 14 Schematic comparing strain relaxation in a thin-film geometry vs. a nanowir               |

| geometry3                                                                                         |

| (a) Strain relaxation in thin film showing a dislocation defect beyond the                        |

| critical thickness                                                                                |

| (b) Coherent radial strain relaxation in a nanowire                                               |

| FIG. 15 Ge/S core/shell nanowire                                                                  |

| (a) Schematic and band diagram showing the presence of a degenerate hole                          |

| gas.                                                                                              |

| (b) HRTEM image of a nanowire showing a 10 nm Ge core and 2 nm Si shell.   |

|----------------------------------------------------------------------------|

| FIG. 16                                                                    |

| (a) Output curves for a laterally configured back-gated FET with a Ge/Si   |

| core/shell nanowire. with 20 nm core diameter and 1 $\mu m$ channel length |

| (b) Transfer curves for a laterally configured back-gated FET with a Ge/Si |

| core/shell nanowire with 20 nm core diameter and 1 $\mu m$ channel length  |

| (c) Output curves for a similar device with Ge 10 nm core diameter         |

| (d) Transfer curves for a similar device with Ge 10 nm core diameter       |

| FIG. 17                                                                    |

| (a) SEM image of a vertical Ge nanowire (20 nm in diameter) epitaxially    |

| grown on a Si substrate                                                    |

| (b) Low magnification image of the epitaxial Ge NW growth.                 |

| FIG. 18                                                                    |

| (a) SEM image showing kinking during nanowire nucleation                   |

| (b) SEM image showing tapered nanowires                                    |

| FIG. 19 SEM image showing high yield vertical growth41                     |

| FIG. 20 Au catalyst removed from vertical Ge nanowire                      |

| FIG. 2145                                                                  |

| (a-b) Band diagrams showing the operation of a conventional n-type FET in  |

|                                                                            |

| the (a) ON state and (b) OFF state.                                        |

| (c-d) Corresponding band diagrams showing the operation of a n-type TFET                            |

|-----------------------------------------------------------------------------------------------------|

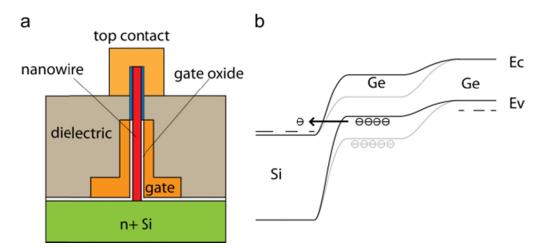

| FIG. 22                                                                                             |

| (a) Schematic of a vertical TFET having an n+ Si source and a Ge nanowire channel                   |

| (b) The corresponding band diagram                                                                  |

| FIG. 23 First order calculations of the proposed TFET saturation current (ON                        |

| current) as a function of gate voltage51                                                            |

| (a) Comparison with a Si-based TFET shows improvement in ON current                                 |

| when replacing the channel with smaller band gap material Ge                                        |

| (b) With varying nanowire diameter                                                                  |

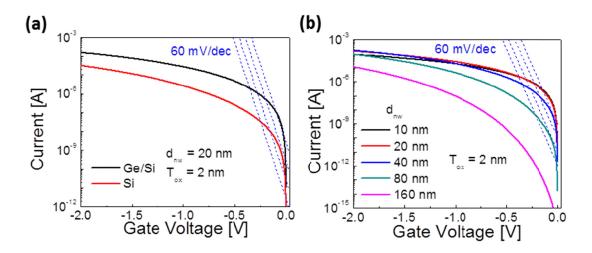

| FIG. 2456                                                                                           |

| (a) Schematic of the cross section of the completed vertical Esaki diode structure                  |

| (b) Equilibrium band diagram of the Si-Ge heterojunction                                            |

| (c) Current-voltage characteristic of the selected device showing a PVR of 2.75 at room temperature |

| •                                                                                                   |

| (d) Expanded semi-logarithmic plot of the voltage sweep shown in (c)                                |

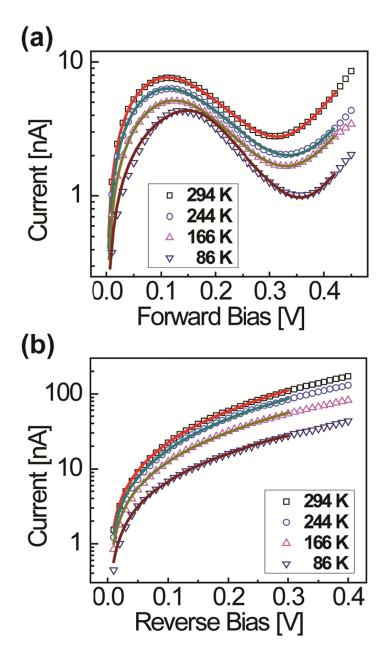

| FIG. 25 Temperature dependence (down to 86K) of the current-voltage                                 |

| characteristics of the device shown in Fig. 24                                                      |

| (a) Forward bias                                                                                    |

| (b) Reverse bias                                                                                    |

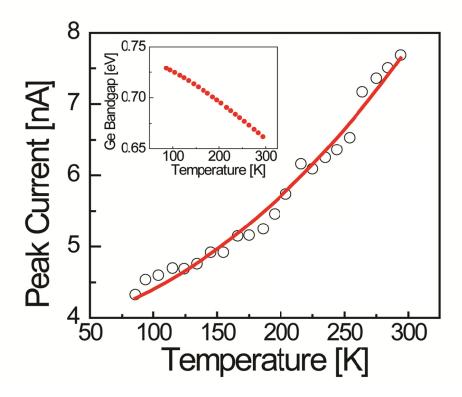

| FIG. 26 Measured peak current $I_p$ vs temperature                                  |

|-------------------------------------------------------------------------------------|

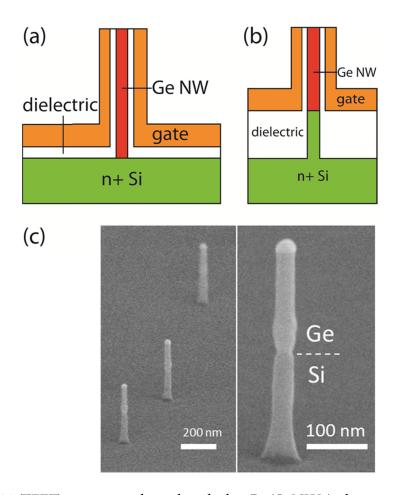

| FIG. 27                                                                             |

| (a) TFET gate is misaligned with the Ge/Si NW/substrate junction                    |

| (b) By first etching a Si nanopillar, the geometry allows optimal gate              |

| alignment for control of the tunnel junction                                        |

| (c) SEM image of vertical Ge nanowires (diameter 30 nm) grown epitaxially           |

| on Si nanopillars                                                                   |

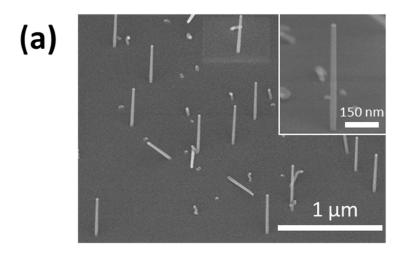

| FIG. 28                                                                             |

| (a) SEM image (taken at $45^{\circ}$ viewing angle) of vertical Ge nanowires (20 nm |

| in diameter) nucleated on Si (111) at 320 °C                                        |

| (b) High resolution TEM image showing a sharp Ge/Si heterojunction at the           |

| interface of a Ge nanowire grown on a Si nanopillar at 320 $^{\circ}\mathrm{C}$     |

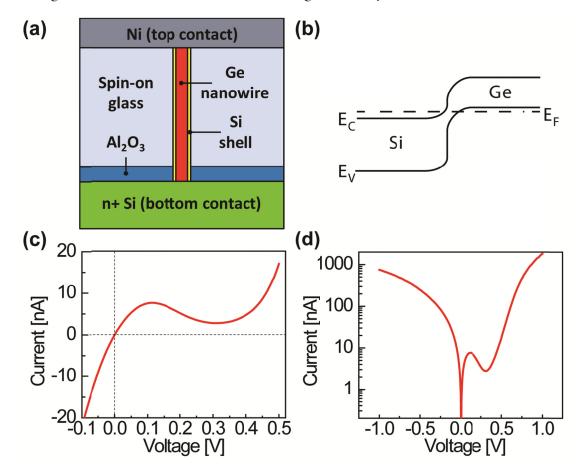

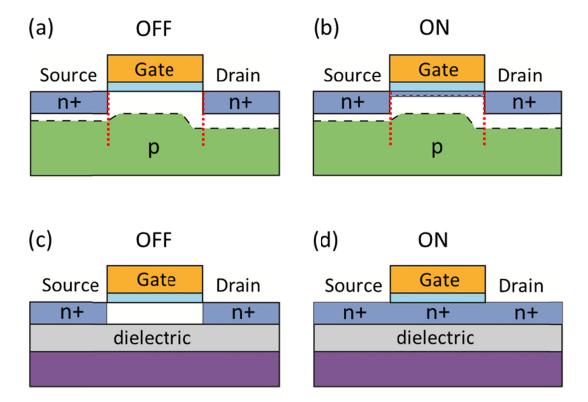

| FIG. 29 Schematics comparing the operation of the conventional MOSFET and the       |

| junctionless FET69                                                                  |

| (a) Conventional MOSFET OFF state                                                   |

| (b) ) Conventional MOSFET ON state                                                  |

| (c) Junctionless FET OFF state                                                      |

| (d) ) Junctionless FET ON state                                                     |

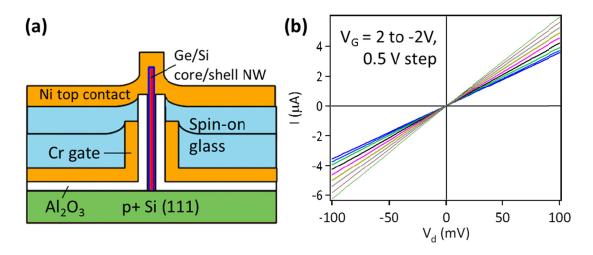

| FIG. 3071                                                                           |

| (a) Device schematic of preliminary design of vertical junctionless FET             |

| (b) Output curves of fabricated device showing high ON-current density                  |

|-----------------------------------------------------------------------------------------|

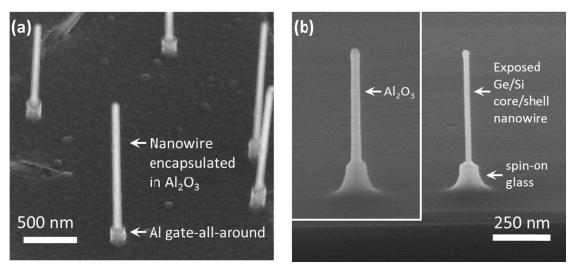

| FIG. 31 Fabrication techniques for vertical FET structures74                            |

| (a) Cylindrical Al gates around vertical nanowires (20 nm diameter)                     |

| encapsulated in 25 nm ${\rm Al_2O_3}$                                                   |

| (b) Controlled wet etching of $\mathrm{Al_2O_3}$ using spin-on glass as an etch mask to |

| expose a Si/Ge core/shell vertical nanowire for gate dielectric deposition              |

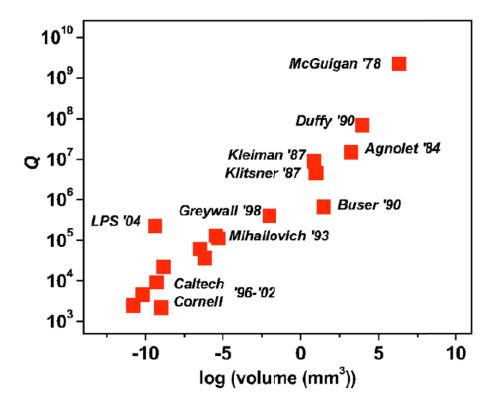

| FIG. 32 Maximum reported Q factors in mechanical resonators varying in size from        |

| the macroscale to nanoscale                                                             |

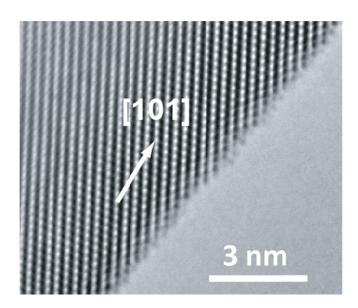

| FIG. 33 HRTEM image of a $SnO_2$ nanowire showing a smooth surface80                    |

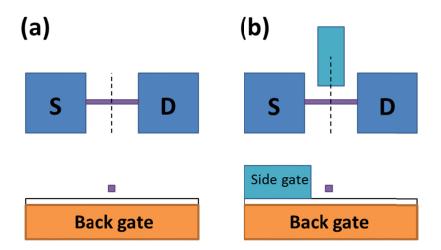

| FIG. 34 Schematics of two configurations of doubly clamped nanowire resonator $81$      |

| (a) Substrate is used as global back gate                                               |

| (b) With local side gate                                                                |

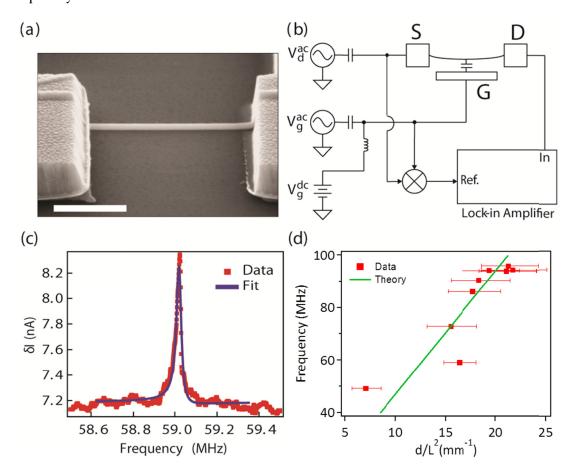

| FIG. 3582                                                                               |

| (a) SEM image of a representative doubly clamped nanowire resonator                     |

| (b) Schematic of the double-source method                                               |

| (c) Electrical readout from a typical device along with a Lorentzian fit                |

| (d) Plot of $f_0$ vs geometry factor $d/L^2$ for nine devices                           |

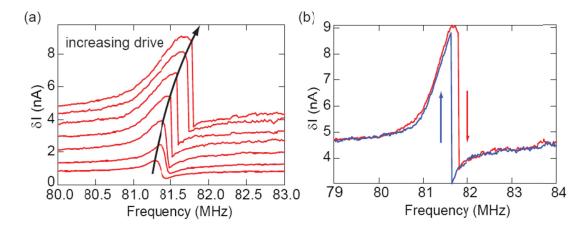

| FIG. 36 Nonlinear response of a back-gated device                                       |

| (a) Family of response curves as the ac gate drive $V_g^{ac}$ is increased from 60 to   |

| $350~\mathrm{mV}_\mathrm{pp}$                                                           |

#### **Chapter 1**

#### Overview

Until the past few years, the tremendous success of complementary metal oxide semiconductor (CMOS) technology since its invention in the 1960s was the result of shrinking the size of transistors through the use of top-down lithographic techniques. Owing to the excellent natural interface between silicon and silicon dioxide, no major changes to the device design were needed, in spite of the existence of high mobility materials such as germanium and III-V compounds. However, this top-down paradigm of transistor size scaling is now being seriously challenged due to a number of practical and fundamental problems as the device size approaches the few-nanometer scale [1-3]. As the device size shrinks, the device characteristics become increasingly sensitive to dimensional variations. For example, simulations of a double-gate metal-oxide-semiconductor field-effect transistor (MOSFET) [3] predict that for a device with channel length 5 nm and channel thickness 2 nm, either a 0.2 nm variation in the length or a 0.1 nm variation in the thickness would result in a 50 mV shift in the threshold voltage. It is very difficult to control the device dimensions with such precision, and the increasing costs associated with lithography equipment and operating facilities needed for traditional manufacturing may create an economic barrier to continued scaling. Hence the bottom-up growth of functional

nanoscale materials, in which at least one critical device dimension (e.g. channel thickness) is defined via a chemical synthesis process with near-atomic-scale precision, may be an attractive alternative to traditional top-down techniques. Such materials, including molecules[4-8], graphene[9-13], carbon nanotubes[14-17], and semiconductor nanowires (NW) [18-20], have attracted much interest with the expectation that they may be able to complement or replace CMOS in the future.

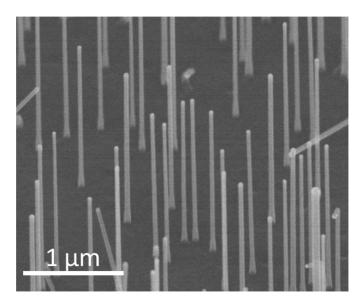

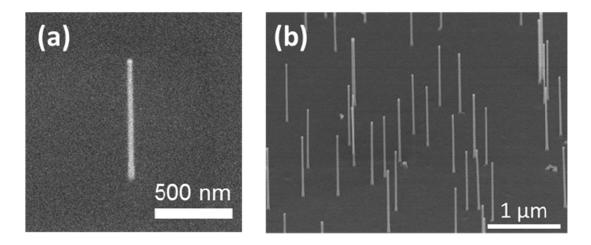

FIG. 1. Example of semiconductor nanowires. Shown here are vertical Ge nanowires epitaxially grown on Si.

In particular, semiconductor nanowires hold much technological promise. These are single-crystals with diameters of a few nanometers and lengths up to tens of micrometers, typically grown through a vapor-liquid-solid or a vapor-solid-solid process mediated by nanoparticles[18] (Fig. 1). They can be prepared with reproducible electronic properties in high yield. Recent developments in nanowire growth have led to the demonstration of a wide range of nanowire structures with

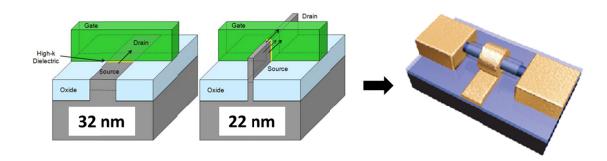

precise control of composition, morphology and electrical properties, including group IV[21, 22], III-V[23] and II-VI[24] core/shell[25], superlattice[26] and branched[27] nanowires. In addition, their crystalline structure and smooth surfaces help reduce scattering and typically result in better characteristics compared with nanofabricated samples of similar size. They are especially interesting in light of another trend in the semiconductor industry: in addition to size scaling, recently there has been a gradual transition from a planar device structure to a tri-gate structure, for increased gate coupling to the transistor channel (Fig. 2). For example, in 2012 Intel introduced a tri-gate structure into its high-volume production at the 22 nm node. Following this development, the next evolutionary step would be the introduction of a gate-all-around (GAA) structure, in which the channel is completely surrounded by the gate. The nanowire geometry is especially suited for the GAA structure.

FIG. 2. Trend in transistor geometry toward a gate-all-around structure. Shown here are Intel's 32 nm planar geometry (2010) and Intel's 22 nm tri-gate geometry (2012).

This thesis explores the technological potential of semiconductor nanowires. To date, most efforts have focused on Si nanowires, since CMOS is based on silicon. One requirement for the integration of Si nanowires with CMOS is that the nanowire growth process should be CMOS-compatible. To this end, in Ch. 2.3 we explore Si nanowire growth using CMOS-compatible Al as catalyst (in particular we demonstrate small diameter nanowires that retain their semiconducting behavior).

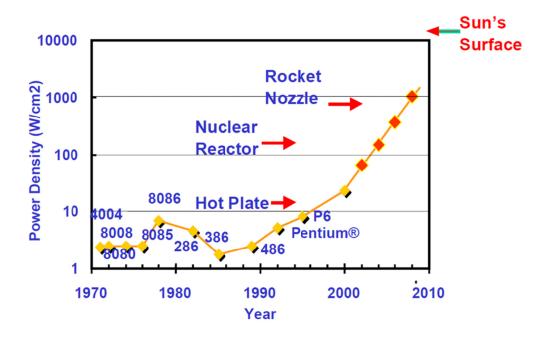

FIG. 3. Trend in power density in CMOS technology. Adapted from Ref.[28].

One fundamental challenge that CMOS technology faces today is power dissipation. As shown in Fig. 3, the power density has increased at a near-exponential rate toward the air-cooling limit of  $\sim 100~\rm W/cm^2$  [28]. Today's chips hover near this limit; for example, both of Intel's 32 nm and 22 nm microprocessors have a power density of  $\sim 40$ -50 W/cm². Power density cannot increase much further without incurring substantial packaging and cooling costs that are impractical for most

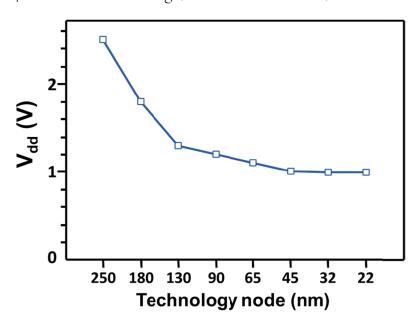

applications. From a device perspective, the situation may be elucidated by examining the trend in the power supply voltage  $V_{dd}$ , shown in Fig. 4. As this figure shows, the supply voltage  $V_{dd}$  has bottomed out at  $\sim 1$  V starting from the 65 nm node. Dynamic power dissipation is roughly proportional to  $V_{dd}^2$ , while static power dissipation is proportional to  $V_{dd}$ , so it would be desirable to reduce  $V_{dd}$ . However, in a conventional MOSFET the ON current  $I_{ON} \propto \mu (V_{dd} - V_T)^2$ , where  $\mu$  is the channel mobility and  $V_T$  is the threshold voltage, would also decrease, which would increase

FIG. 4. Technology scaling trends of power supply voltage  $V_{dd}$ . Adapted from Ref. [29].

the gate delay and compromise switching speed. One could maintain high  $I_{ON}$  by reducing  $V_T$ , but this would result in an exponential increase in the OFF current  $I_{OFF}$ , which would increase static power dissipation. The exponential dependence of  $I_{OFF}$  on  $V_T$  is given by  $I_{OFF} \propto \exp\left(-qV_T/kT\right) = 10^{-V_T/SS}$ , where q is the electronic charge, k is

the Boltzmann constant, and T is the temperature. SS is a figure of merit (defined by the equation) called the subthreshold swing, and it measures the gate voltage swing needed to reduce the current by a factor of 10. Fig. 5 shows the relationship of  $I_{ON}$ ,  $I_{OFF}$ ,  $V_T$ ,  $V_{dd}$ , and SS in a conventional MOSFET.

FIG. 5. Qualitative transfer characteristics of a conventional MOSFET.

This thesis touches on two ways to address the power dissipation problem. One possible solution is to maintain high  $I_{ON}$  by increasing  $\mu$ , that is, by forming the transistor channel out of a high mobility material in which charge carriers travel at a much higher velocity than in silicon. This would allow a reduction in  $V_{dd}$  without a loss of performance. Rather than developing a completely new non-Si-based technology, however, it would be much more cost-effective to integrate the new materials on Si and complement traditional CMOS technology in an evolutionary manner. The ideal channel material should have equally high electron and hole

mobilities, since CMOS requires n-channel and p-channel FETs with reasonably matched performance. But Fig. 6 shows that at present no such material exists. While III-V compound semiconductors have very high electron mobilities, at any lattice constant there is a large gap between electron and hole mobilities [30].

FIG. 6. Reported III-V, Si, and Ge room-temperature mobilities of electrons (red squares) and holes (blue circles) as a function of lattice constant, measured from inversion layers and quantum wells. Black arrows point toward increasing biaxial compressive strain. Relaxed lattice constants are shown on the scale. It is seen that Ge has a high hole mobility and a smaller Si-lattice mismatch than that of III-V materials. Adapted from Ref. [30].

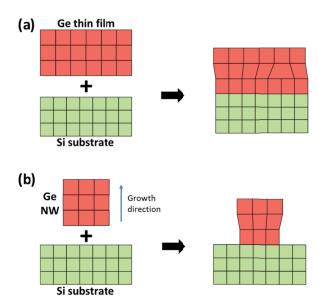

Compressive biaxial strain (increasing along the black arrows in Fig. 6) plays a large role in bridging this gap, but it seems that, at the moment, the leading contender for the p-channel FET is Ge, which has a high hole mobility (even when compared with III-V materials), and whose technology is more mature than III-V technology. It also happens that Ge has a smaller lattice mismatch with Si than almost any III-V material, making the integration on a Si substrate a little easier. Still, the 4.2% lattice mismatch between Ge and Si poses a significant challenge for integration. To this end, the nanowire geometry may be able to relax strain coherently and allow the formation of low-defect Si-Ge interfaces. Hence in Ch. 2.4 we develop the vertical epitaxial growth of Ge nanowires on Si. Also, in Ch. 3 we investigate the prospects for vertical transistors using a vertical Ge nanowire as the channel (we focus on the tunnel FET and touch on the junctionless FET along the way).

FIG. 7. Qualitative transfer characteristics comparing MOSFET (solid line) and TFET (dashed line). The TFET is capable of much lower OFF current.

Another route toward reducing power dissipation is to reduce  $I_{OFF}$ . In a conventional MOSFET, SS has an inherent thermodynamic lower bound of 60 mV/decade at room temperature. To this end, an alternative device concept, the tunnel field-effect transistor (TFET), has been proposed to circumvent this limit (Fig. 6). While the current conduction mechanism in a conventional MOSFET is thermionic emission over a potential barrier, a TFET uses quantum-mechanical bandto-band tunneling to bring charge carriers into the device channel. Thus in a TFET very low OFF currents are possible. This would allow a reduction of  $V_T$  (and hence a reduction in  $V_{dd}$ ). However, Si-based TFETs suffer from low ON currents owing to its large band gap. Ge has a smaller band gap and thus may offer higher ON currents. To this end, in Ch. 3 we explore the use of vertical Ge nanowires grown on Si for the construction of a p-channel TFET. In addition, the nanowire geometry offers several attractive features when used as the channel of a TFET, including excellent gate coupling, scalability, and the coherent relaxation of strain for creating defectfree tunnel heterojunctions on Si.

While much effort in nanowire research is aimed at creating high performance electronic devices, the technological promise of semiconductor nanowires extends beyond their electronic properties: exploiting their mechanical degrees freedom will be a key to unlocking their full potential. Nanoelectromechanical systems (NEMS) is an emerging field in which nanoscale structures are mechanically manipulated with electrical actuation. In particular, nanoscale resonators have the potential for important applications in ultrasensitive mass and force sensing, and quantum measurement [31-38] (Fig. 8). Here nanowire-based mechanical resonators

potentially can obtain ultrahigh quality factors by suppressing acoustic energy losses intrinsic to a bulk crystal, minimize surface losses owing to their atomically smooth surfaces, and minimize losses due to bulk impurities and crystal defects owing to their small size and excellent material quality. To this end, in Ch. 4, we investigate a doubly clamped nanowire mechanical resonator.

FIG. 8. Example of a doubly clamped nanomechanical beam resonator, made from silicon nitride. Adapted from Ref.[39].

To summarize the contents of this thesis, Chapter 2 focuses on nanowire CMOS-compatible growth techniques with an eye toward hybrid nanowire-CMOS systems. Chapter 3 examines the prospects for a Ge nanowire-based vertical tunnel field-effect transistor. We demonstrate high performance Esaki diodes constructed from Ge/Si core/shell nanowires and discuss the junctionless field-effect transistor concept. Chapter 4 demonstrates doubly clamped, Very-High Frequency (VHF) nanowire resonators with a dual-gate configuration that allows integrated electrical actuation/detection, *in situ* frequency tuning and selective actuation of different

vibrational modes. Finally in Chapter 5, we make some concluding remarks and discuss the future work to be done.

#### Chapter 2

# Growth of Si, Ge, and Ge/Si core/shell nanowires: toward CMOS integration

#### 2.1: Introduction

Over the last five decades, reducing the size of complementary metal—oxide—semiconductor (CMOS) field-effect transistors (FETs) has enabled extraordinary improvements in the switching speed, density, functionality and cost of microprocessors. But now, due to this aggressive device scaling, CMOS technology faces serious challenges[1-3]. As discussed in Ch. 1, semiconductor nanowires can help address some of these challenges. They can enable control of channel thicknesses with near-atomic-scale precision, and the nanowire geometry is ideally suited for the gate-all-around structure toward which the semiconductor industry is moving. Since nanowires are grown from the bottom-up, they represent a radical break from traditional top-down manufacturing methods. The traditional technology, which is implemented in semiconductor fabrication plants and developed over decades and billions of dollars, is quite mature and it would not make economic sense to replace it with entirely new technology. Instead, semiconductor nanowires can be used for

special high performance devices to complement traditional devices on the same chip.

Realizing such a hybrid nanowire-CMOS system would require careful consideration of whether the nanowire growth process could disturb the properties of the CMOS devices. When considering the CMOS-compatibility of the growth process, it is useful to look at two components: thermal budget and materials. The thermal budget used for fabricating nanowire-based devices depends on whether metal diffusion is a concern. For example, if the nanowire growth occurs during the back-end-of-line (BEOL) portion of the fabrication process, which begins with the first metal interconnect layer, then the thermal budget would be highly constrained. To prevent metal diffusion, a general rule of thumb is that the process temperature should not exceed  $\sim$ 450 °C [40], although the time t spent at the process temperature also influences diffusion (with a diffusion length evolving roughly as  $\sqrt{Dt}$ , where D is the diffusion coefficient whose temperature dependence follows a thermally activated Arrhenius equation). On the other hand, if the nanowires are grown during the front-end-of-line (FEOL) portion of fabrication, and prior to gate metal deposition, much higher growth temperatures could be tolerated.

Material compatibility means that any new materials introduced into the process should not contaminate the existing CMOS devices. Throughout most of the history of CMOS, there had been only a handful of CMOS-compatible materials: Si and its oxides and nitrides, dopants, and Al-based metals. Recently, there has been a trend in the industry to introduce more materials: SiGe, Cu-based metals, high-k dielectrics (e.g. HfO<sub>2</sub>, ZrO<sub>2</sub>), and low-k dielectrics (e.g. carbon-doped oxide). The

list is expanding (e.g. high mobility III-V materials are being considered). In any effort to introduce a new material, it is important to consider whether the material could be a contamination risk, and if so, whether the process can be designed to mitigate the risk.

In this chapter, we explore nanowire growth strategies that aim toward CMOS integration and strive to remain CMOS-compatible. To this end, after some additional background in Ch. 2.2, in Ch. 2.3 we discuss our progress in Si nanowire growth, by replacing the Au catalyst with Al, which is CMOS-compatible. In Ch. 2.4, we discuss progress toward the vertical integration of Ge, a technologically important material, on a Si substrate (which is envisioned to contain CMOS devices in the future), while maintaining a low thermal budget.

#### 2.2: Overview of the nanowire growth process

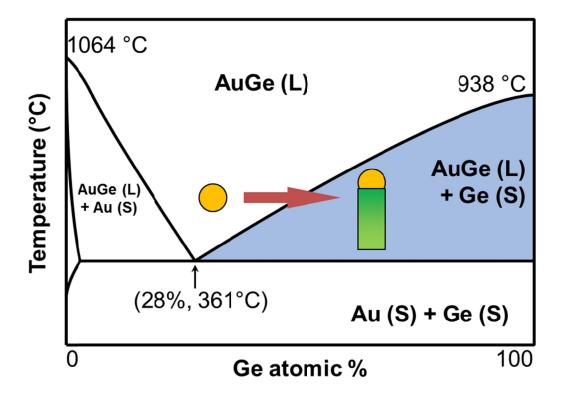

Semiconductor nanowires are generally synthesized by employing metal nanoclusters as catalysts via a vapor-liquid-solid (VLS) or a vapor-solid-solid (VSS) process, the former being more widely used than the latter. We now illustrate the VLS process using as an example the growth of a Ge nanowire with a Au nanoparticle as the catalyst (the main process used in Ch. 2.4 and Ch. 3; the Al-Si system discussed in the Ch. 2.3 behaves similarly - see Fig. 10(a)). Fig. 9 depicts the binary alloy phase diagram for the Au-Ge system. The process begins with a metal nanoparticle (Au) in the presence of a vapor phase containing the semiconductor

FIG. 9. Example binary alloy phase diagram illustrating the VLS process for nanowire growth. Here the Au-Ge system for the growth of Ge nanowires using Au as the catalyst. The eutectic point is located at 28 % Ge content and 361 °C.

material (GeH<sub>4</sub>). As the temperature is increased, the metal nanoparticle helps catalyze the decomposition of the vapor phase material, releasing the semiconductor material (Ge). The metal nanoparticle acts as a sink for this material, and an alloy of the metal and semiconductor material is formed (AuGe). The alloy melts (the liquid L region in Fig. 9), which speeds up further incorporation of semiconductor material into the alloy droplet (due to increased diffusion coefficient). The minimum temperature at which melting is possible is called the eutectic temperature (361 °C for AuGe); hence the temperature should be increased to a user-defined nucleation

temperature above this value. Eventually the alloy becomes supersaturated with the semiconductor material (shaded region in Fig. 6), at which point a crystalline semiconductor phase (c-Ge) precipitates out of the alloy. This latter phase constitutes the growing nanowire; nanowire nucleation has occurred. The continued precipitation of the solid semiconductor at the solid-liquid interface leads to nanowire elongation, with the alloy droplet riding on top. In the VSS process, this sequence of events is similar except that the metal nanocluster remains in the solid state. In this case, the diffusion of semiconductor material through the nanocluster is much slower[41].

The nanowires used in Chapter 4 (nanoelectromechanical devices) are crystalline metal oxide ( $SnO_2$ ) nanowires. These are grown using a vapor-phase, metal-catalyzed process, very similar to VLS. First, vapor phase Sn is generated from heating a Sn source metal. Then the vapor condenses at a Au nanocluster, and from the nanocluster a  $SnO_2$  nanowire is nucleated. However, the exact mechanism of metal oxide nanowire growth is still under debate in the literature. Since Chapter 4 focuses on the nanoelectromechanical device properties rather than potential CMOS integration, for further details we refer the reader to Chapter 2 of Ref. [42].

#### 2.3: Growth and electrical properties of Al-catalyzed Si nanowires

One requirement for the integration of nanowires with CMOS is that the nanowire growth process should be CMOS-compatible. In this section we address one of the CMOS integration issues, namely, the material contamination risk posed by the catalyst material used in the nanowire growth process. Currently the most

widely used catalyst material is Au. For example, the SnO<sub>2</sub> and Ge nanowires we use in Ch. 2.4, Ch. 3, and Ch. 4 are grown using Au as the catalyst. Furthermore, Au is often the catalyst for the growth of Si nanowires[43, 44], which have been widely studied due to the fact that CMOS technology is based on silicon. However, Au forms deep trap levels inside the Si band gap, and poses a potential contamination problem for processing. This is particularly an issue for hybrid nanowire-CMOS systems. Even though several studies have found that the influence of Au residing in the nanowire bulk is negligible [45-47], alternative catalyst materials may still be preferred. To date, Fe and Cu were reported as catalysts for Si nanowire growth with limited success [48, 49]. Ni as a catalyst[50] was also studied. However, due to the high eutectic temperature (964 °C) of Ni–Si alloy, a high synthesis temperature was required. Recently Al-catalyzed Si nanowire growth has attracted significant interest[51, 52]. However, the growth of Si nanowires using Al catalysts has been shown to be difficult due to the fact that Al readily reacts with ambient  $O_2$  and  $H_2O_3$ , thereby forming a surface oxide layer that prevents the continued influx of Si reactants into the catalyst[51]. In addition, Al is a shallow acceptor in Si and is therefore expected to yield p-type Si nanowires[53]. Previous studies have thus far resulted in large-diameter Si nanowires that behave as degenerately Al-doped semiconductors with minimal gate response, making them unsuitable in electronics applications[52].

In this study we demonstrate Al-catalyzed, small diameter Si nanowires grown via the VLS process, and discuss their electrical properties. Specifically, by using high  $H_2$  and  $SiH_4$  partial pressures we were able to minimize the Al oxidation effect and

successfully grew large quantities of small diameter Si nanowires with high growth rate, minimal tapering, and high aspect ratio. In addition, we observed that the effective doping level is diameter-dependent, and small diameter (d  $< \sim 25$  nm) Alcatalyzed nanowires behaved as p-type semiconductors with good gate response, while larger diameter Al-catalyzed nanowires behaved as degenerately doped semiconductors due to excessive Al-doping.

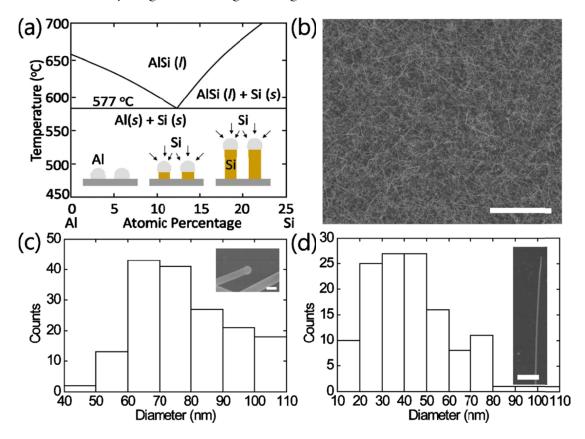

#### 2.3.1: Growth of small-diameter nanowires with high yield

Fig. 10(a) shows the Al–Si binary phase diagram employed in the VLS nanowire growth process[54]. The substrates used for nanowire growth consisted of (111) N-type Si wafers with a resistivity of 0.001–0.002  $\Omega$ -cm. The substrates were first cleaned in 1:1 H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub> to remove organic surface contamination for 20 min, and then dipped in 1 M HF for another 20 min to remove the native oxide and create a hydrogen-terminated Si surface. The subsequent de-ionized water rinse was minimized to retain as much of the hydrogen-termination as possible. The substrates were immediately transferred into the evaporator chamber to deposit 6 nm Al seed layer followed by the growth of Si nanowires in a low-pressure chemical vapor deposition (CVD) system. Once the Al-coated Si substrates were loaded into the CVD system, they were annealed at 590 °C for 5 min under 100 Torr H<sub>2</sub>. The annealing, performed at a temperature above the Al/Si eutectic temperature of 577 °C, was intended to facilitate the Al film agglomeration on the surface and the formation of liquid eutectic droplets with the Si substrate. In particular, the hydrogen-rich environment during annealing was found to be effective to remove

existing aluminum oxide on the Al surface[52, 55]. For example, we observed identical results when comparing growth from fresh Al-coated Si substrates with those that have been stored in air for up to 48 h prior to growth, showing the effectiveness of hydrogen annealing to mitigate the effect of aluminum oxide. After

FIG. 10. (a) Schematic of the Al–Si binary phase diagram. Inset: schematic of VLS growth of Si nanowires. (b) SEM image of Al-catalyzed Si nanowires. Scale bar: 25  $\mu$ m. (c) Diameter distribution of Al-catalyzed Si NWs grown at 520 °C, 100 Torr reactor pressure, and 50 Torr SiH<sub>4</sub> partial pressure. Inset: SEM image showing Al catalyst at the tip of nanowires. Scale bar: 100 nm. (d) Same as (c) but with 75 Torr SiH<sub>4</sub> partial pressure. Inset: SEM image of a single Si nanowire. Scale bar: 500 nm.

annealing, Si nanowires were grown at  $520\,^{\circ}\text{C}$  for  $30\,\text{s}$  in the same system. The SiH<sub>4</sub> partial pressure during growth ranged from  $50\,\text{to}$  75 Torr, and the total reactor pressure was kept at  $100\,\text{Torr}$  balanced by H<sub>2</sub>. The H-rich environment during growth in turn helps prevent aluminum oxide poisoning and results in long, Alcatalyzed Si nanowires.

Fig. 10(b) shows a scanning electron microscopy (SEM) image of typical Si nanowires grown on the Al-coated Si substrate at 520 °C. Higher magnification SEM image of the tip region of the nanowires shown in Fig. 10(c) inset verified the presence of metal nanoparticle at the tip of the nanowires. High density Si nanowires with large aspect ratio were obtained with minimal tapering. Compared with earlier studies, the reduced tapering is believed to be due in part to the high nanowire growth rate ( $> 5 \mu m/min$ ), which reduced the time available for vapor-solid deposition to occur[52]. Furthermore, the high growth rate suggests that the Al catalyst remains in the liquid state during the growth, even though the growth temperature is below the bulk eutectic temperature. Similar effects have been observed in the growth of Au-catalyzed Ge nanowires and can be explained by supercooling of the eutectic[56], and lowering of the eutectic temperature in the nanoparticle form[57]. Depending on the SiH<sub>4</sub> partial pressure, the as-grown Si nanowires have diameters in the range of 20–100 nm and exhibit a unimodal diameter distribution with peak range at 60–70 nm and 30–50 nm for SiH<sub>4</sub> partial pressures of 50 and 75 Torr during growth, respectively [Figs. 2.3.1(c) and (d)]. In general, we observed that higher SiH<sub>4</sub> partial pressure resulted in smaller diameter nanowires, consistent with previous studies on Au-catalyzed nanowires[43, 58].

Notably, we were able to obtain long Al-catalyzed nanowires with diameters down to 20 nm, much smaller than previously reported[51, 52]. The effect of the SiH<sub>4</sub> partial pressure is to adjust the thermodynamic conditions for nanowire growth. Growth proceeds by thermodynamically driving the transition from the vapor phase (SiH<sub>4</sub>) to the nanowire phase, which is a combination of bulk solid phase and the formation of surfaces. The transition occurs because there is a net decrease in the effective chemical potential. However, when the nanowire is made thinner, the effective chemical potential of the nanowire phase can increase due to the increased surface area-to-volume ratio which is more dominated by surface free energy. This increased chemical potential makes the nanowire phase less favorable since during the phase transition the reduction of chemical potential is less pronounced. To restore the difference in chemical potentials between the two phases, the chemical potential of the vapor phase should also increase, which is accomplished by increasing the partial pressure.

Si nanowire growth with a 10 nm Al seed layer was also tested, resulting in an increase in average nanowire diameter up to 100–120 nm. This result matched well with the recent studies by Wacaser et al.[51] showing that the average diameter increased with the Al seed layer. The finding was attributed to the AlSi alloy droplet formation during the hydrogen annealing, where thicker films agglomerated into larger droplets.

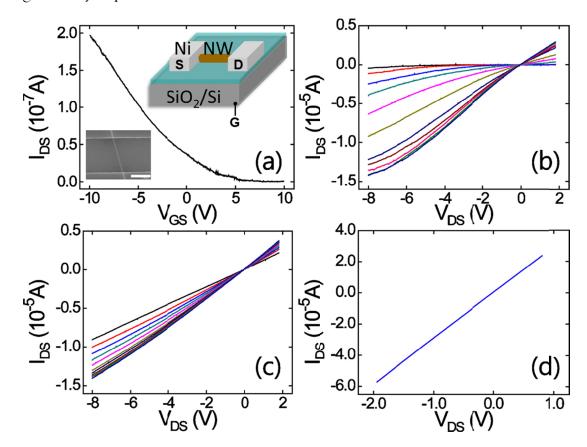

### 2.3.2: Recovery of semiconductor behavior at small diameter

After growth, the nanowires were transferred to an isopropyl alcohol solution through sonication and drop-casted to a SiO<sub>2</sub>/Si substrate (p-type,  $0.001-0.005 \Omega$ cm with a 50 nm thermal SiO<sub>2</sub> layer), and a number of device structures were fabricated and tested. Briefly, photolithography was used to define pairs of source/drain (S/D) electrodes to contact each nanowire, followed by 3 s buffered oxide etch (10:1) dip to remove the native oxide on the nanowire surface immediately before the samples was loaded into the evaporator chamber to deposit 100 nm thick Ni electrodes. Contact annealing at 320 °C for 2 min in forming gas  $(N_2/H_2, 90/10\%)$  completes the final device structure, with the p+ Si substrate serving as the back gate [Fig. 11(a), upper right inset]. All devices reported here contain only a single nanowire bridging the S/D contacts, with the electrical measurements carried out in air at room temperature. Fig. 11(a), lower left inset, shows a SEM image of such a device. Gate dependent current-voltage measurements indicate that the as-grown wires are p-type, and suggest that Al is incorporated into the Si nanowires [Fig. 11(a)]. Figs. 11(b), (c) and (d) show the family of  $I_{DS}$ - $V_{DS}$ curves for representative devices with nanowire diameter d = 23, 40, and 80 nm, respectively. Significantly, the Si nanowire device with d = 23 nm shows typical ptype semiconductor characteristics and can be turned off within a  $V_{GS}$  bias window of 10 V. However, the Si nanowire device with d = 40 nm shows reduced gate response, and cannot be turned off. Finally, Si nanowire device with d = 80 nm

completely loses its gate control, suggesting that the larger diameter nanowire is degenerately doped.

FIG. 11. (a) Transfer curve ( $I_{DS}$ - $V_{GS}$ ) at  $V_{DS} = -0.1$  V for a device with diameter = 23 nm. Upper right inset: schematic of the device. Lower left inset: SEM image of a similar device. Scale bar: 1  $\mu$ m. (b) Family of  $I_{DS}$ - $V_{DS}$  curves for the same device in (a).  $V_{GS} = 10$  to -10 in -2 V steps. (c) Family of  $I_{DS}$ - $V_{DS}$  curves for another device with diameter = 40 nm.  $V_{GS} = 10$  to -10 in -2 V steps. (d) Family of  $I_{DS}$ - $V_{DS}$  curves for another device with diameter = 80 nm.  $V_{GS} = 10$  to -10 in -10 V steps.

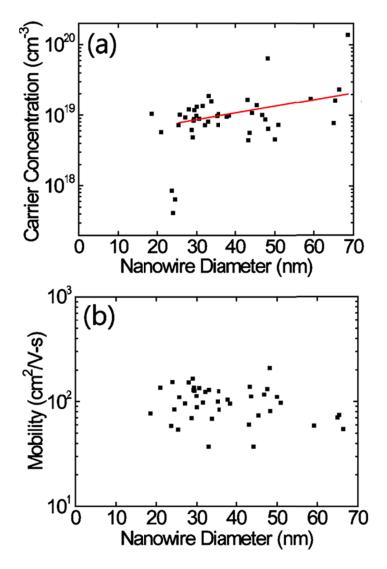

The carrier concentration can be calculated by extracting the threshold voltage  $V_T$  from the transfer curve measured in the linear ( $V_{DS} = -0.1 \text{ V}$ ) region. The carrier concentration N (at  $V_{GS} = 0$  V) was then calculated from  $N = C_g (0 - V_T)$ , where  $C_g$  is the capacitance of the back gate and can be estimated from the cylinderon-plane model,  $C_g = 2\pi\varepsilon_r \varepsilon_0 L/\cosh^{-1}[(2h+d)/d]$ , where  $\varepsilon_0$  is the vacuum dielectric constant, h = 50 nm is the thickness of the SiO<sub>2</sub> layer, and d is the lateral size of the nanowire.  $\varepsilon_r$  is the relative dielectric constant and was chosen to be 2.5, which is the average of air (1) and SiO2 (3.9)[59]. Over 70 devices have been measured. However, for devices having nanowire diameters > 70 nm the carrier concentration cannot be reliably extracted due to the lack of gate response. Fig. 12(a) plots the carrier concentration versus the nanowires diameter obtained from 43 devices with nanowire diameter  $\leq 70$  nm. Overall the carrier concentration remains high due to Al doping and a large spread of data was observed for large diameter devices due to the weak gate dependence and the associated uncertainties in extrapolating the carrier concentration data. However, linear fit [red line, Fig. 12(a)] to the data shows an overall gradual reduction of the effective doping level as the nanowire diameter is reduced. Furthermore, a substantial reduction of the carrier concentration was observed for nanowires with diameter < 25 nm, consistent with results from Figs. 11(a) and (b) and suggesting that nanowires with small diameters show semiconductor characteristics. The field-effect mobility  $\mu_{\scriptscriptstyle{fe}}$  of the devices versus diameter was plotted in Fig. 12(b) for comparison. Here the mobility  $\mu_{\rm fe}$  was estimated using the equation,  $g_m = \mu_{fe} C_g V_{ds} / L^2$  in the linear operation regime. Here,

$g_m = dI_{DS}/dV_{GS}$  is the linear-region transconductance, and L is the nanowire device channel length. Overall, the mobility remains roughly constant independent of the nanowire diameter.

FIG. 12. (a) Measured carrier concentration (squares) vs nanowire diameter shown in semilog plot. The red line is a linear fit for data obtained from nanowires with diameter  $d \ge 25$  nm. (b) Measured field-effect mobility vs nanowire diameter.

#### 2.3.3: Possible mechanisms of carrier concentration reduction

Several factors may have contributed to the observed reduction of carrier concentration at small nanowire diameters. One possibility is due to quantum confinement and the amphoteric defect model (ADM) that governs doping limits in both bulk and nanoscale semiconductors [60]. Quantum confinement shifts the valence band edge downward from its bulk value in the case of p-type doping (or the conduction band edge upward in the case of n-type doping). Meanwhile, ADM sets a limit to the attainable Fermi level. Consequently, the maximum achievable carrier concentration is suppressed with diameter reduction. However, this effect is expected to occur only for diameters < 10 nm [60, 61]. The most plausible explanations for the observed reduction in carrier concentration are surface depletion, nanoscale dielectric confinement, and/or surface segregation of dopants. These are described next.

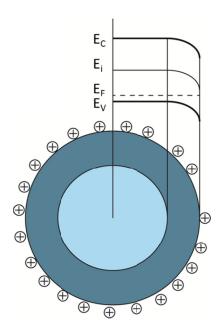

### 2.3.3.1: Surface depletion of charge carriers

One possible explanation is based on surface depletion[62]. For a p-type nanowire, trapped holes at surface states lead to a positive surface charge, which creates a depletion region at the surface (dark annular region in Fig. 13). This depletion region reduces the effective conducting cross-sectional area (light circular region), and hence reduces the effective carrier concentration. As the nanowire diameter decreases, the depletion region occupies a greater portion of the cross-sectional area. In the limiting, very small diameter case, the nanowire can become fully depleted and current can no longer flow.

FIG. 13. Band diagram and schematic showing the surface depletion region (dark annular region) due to trapped holes at the surface of a p-type nanowire.

# 2.3.3.2: Reduced dielectric screening of the impurity potential

The second possible explanation is the dielectric confinement model[63, 64]. A donor or acceptor impurity has a Coulomb potential that give rise to bound states in the energy gap. In a bulk semiconductor, the Coulomb potential is strongly screened (dielectric constant  $\mathcal{E}_r \sim 10\text{-}20$ ) which leads to a large Bohr radius (~1-5 nm) and a correspondingly small ionization energy (few hundredths of an electron volt); impurities in a bulk material are ionized at room temperature. In this case, the ionization energy  $E_d$  can be estimated [65] using the Bohr model of the atom as  $E_d = 13.6 \left( \frac{m^*_{cond}}{m_{cond}} \right) / \mathcal{E}_r^2$  [eV], where  $m_0$  is the electron rest mass and  $m^*_{cond}$  is the effective conductivity mass. In a semiconductor nanowire, however, the close proximity of the impurity atoms to the lower dielectric constant of the environment

(which is air in our measurements,  $\mathcal{E}_r \sim 1$ ) reduces the dielectric screening effect and increases the ionization energy. Therefore the activated doping level and free carrier concentration is reduced in small diameter nanowires.

### 2.3.3.3: Surface segregation of dopants

A third possible explanation is the surface segregation of dopant atoms [66, 67]. As the surface area-to-volume ratio of a nanowire increases, a greater portion of its atoms reside at the surface; these may undergo surface reconstruction since the inter-atomic forces are altered due to terminating the bulk crystal. From *ab initio* simulations it turns out that dopant atoms play a role in the reconstruction such that it is energetically favorable for them to reside at the surface. It has been shown that when the nanowire diameter is small (d < 23 nm in Ref. [66]) all dopants can be accommodated at the reconstructed surface with an intrinsic core. Once this occurs, the surface depletion (Ch. 2.3.3.1) and dielectric confinement (Ch,. 2.3.3.2) mechanisms can take effect, reducing the effective carrier concentration. As the surface-to-volume ratio decreases in larger diameter nanowires, the dopants cannot be fully accommodated at the surface and there is a transition back to bulk-doped material.

### 2.3.3.4: Summarizing remark

It is not clear at this moment which of the above three factors is dominating in our devices, but it is reasonable to suspect that all three factors should have an influence on the observed device behaviors such as the gradual reduction of effective doping level for large diameter nanowires and a sharp roll-off for small diameter (d < 25 nm) nanowires. Further experimental studies (such as the one carried out in Ref.

[66]) and theoretical studies will be needed to confirm any dominating mechanism responsible to the experimental findings. In any case, the ability to grow small-diameter, semiconducting Al-catalyzed Si nanowires could be a significant step forward for incorporating nanowires into future electronic devices/circuits.

# 2.4: Vertical integration of Ge nanowires on Si for highperformance nanoelectronics

In this section we explore the integration of Ge on a Si substrate, with the epitaxial growth of vertical Ge nanowires as our core strategy. Germanium offers both electron- and hole-mobility enhancements over Si, but is especially attractive for its high hole mobility (4X larger). Its smaller band gap (0.66 eV) enables larger tunneling currents for applications such as the tunnel FET, as well as photodetection at near-infrared wavelengths. However, the heterogeneous integration of Ge-based devices on a Si substrate has been challenging due to lattice mismatch ( $\sim$  4%) during thin film growth. To this end, the vertical nanowire geometry allows for radial strain relaxation and the growth of heterojunctions with low defect density and sharp interfaces [68-71] (Fig. 14). Thus the hybrid integration of bottom-up nanowire-based devices with traditional Si substrates offers possibilities to circumvent problems associated with conventional thin-film-based heterogeneous integration approaches.

FIG. 14. Schematic comparing strain relaxation in a thin-film geometry vs. a nanowire geometry. (a) Strain relaxation in thin film showing a dislocation defect beyond the critical thickness. (b) Coherent radial strain relaxation in a nanowire. While a coherently strained film deforms vertically, a nanowire can distribute strain both vertically and laterally, and thereby accomdate a larger lattice mismatch.

Such devices, based on epitaxially grown, vertical nanowire structures, also offer the potential to be integrated vertically on top of CMOS devices, thus further increasing device density with 3-dimensional architectures. The epitaxial growth of vertical Ge nanowires on a Si substrate holds much potential as a platform for future electronic, photonic, and NEMS technologies. For FET structures (e.g. junctionless FET, tunnel FET, floating-gate memory), the vertical nanowire geometry offers optimal gate coupling due to the small channel thickness (= nanowire diameter) and the ability to fabricate a gate-all-around (GAA) structure. In addition, since the channel length of a

vertical FET is determined by the thicknesses of deposited films, which are more easily controlled than lithographically defined lengths, very short channel lengths are readily achieved [72].

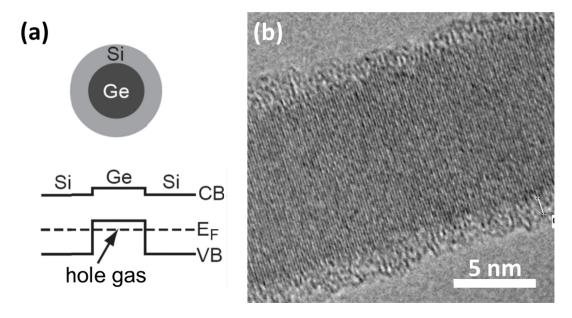

## 2.4.1: Material system: Ge/Si core/shell nanowires

The nanoscale element that serves as the device channel in our CMOS integration and device proposals of Chapter 3 is a Ge nanowire with an optional Si shell. Ge nanowires and Ge/Si heterostructures have been shown to be able to offer high carrier mobility and device performance. For example, in a Ge/Si core/shell nanowire heterostructure developed by Lu et al. consisting of a ~2 nm Si shell epitaxially grown over a ~10 nm diameter Ge nanowire, a 1D hole gas was found to be formed and confined inside the Ge core with near ballistic transport even at room temperature [22, 73] (Fig. 15(a)). In these quasi-one-dimensional devices, it is possible that mobility can degrade due to surface roughness scattering. However, this is not expected to occur until diameter  $\leq 8$  nm [74, 75]. In addition, it is known that silicon can passivate a Ge surface for reduced interface state density and higher hole mobility [76]. Furthermore, in a nanowire geometry, this passivation effect can be enhanced since the nanoscale and comparable sizes of the core and shell lead to a coherently strained Si-Ge interface to accommodate the relative large lattice mismatch between Ge and Si [77]. By integrating the nanowire channel with high-k gate dielectrics (e.g.  $HfO_2$ ) and metal gate electrodes, it has already been shown that these nanowire FETs can outperform state-of-the-art Si MOSFET devices[73]. Very short channel nanowire FETs whose performance approaches the ideal ballistic

transistor limit have also been demonstrated using the Ge/Si core/shell nanowire system[78].

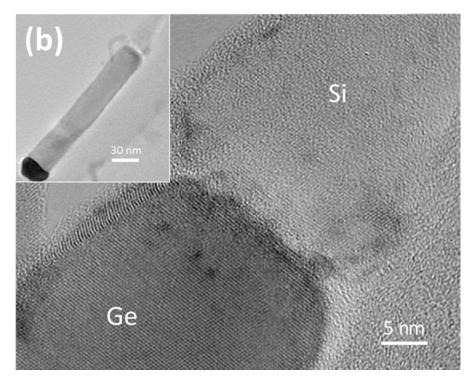

FIG. 15. Ge/Si core/shell nanowire. (a) Schematic and band diagram showing the presence of a degenerate hole gas. (b) HRTEM image of a nanowire showing a 10 nm Ge core and 2 nm Si shell.

In our group at the University of Michigan, we have developed the capability to grow Ge/Si core/shell nanowires in bulk (later in Section 2.4.2 we demonstrate controlled epitaxial growth on a Si substrate). Beginning with Au catalyst nanoparticles deposited on a  $SiO_2$ -coated Si growth substrate, Ge nanowires 10 or 20 nm in diameter (via 10- or 20-nm Au nanoparticles) were nucleated in a hot-wall tube furnace at 315 °C and 300 Torr total pressure, with gases flows of 30 sccm 10%  $GeH_4$  in  $H_2$ , and 200 sccm  $H_2$ . Then a  $\sim$ 2 nm-thick Si shell was deposited around the nanowires *in situ* at 465 °C with 20 sccm  $SiH_4$  and 5 Torr total pressure. A high-

resolution transmission electron microscopy (HRTEM) of a representative nanowire is shown in Fig. 15(b).

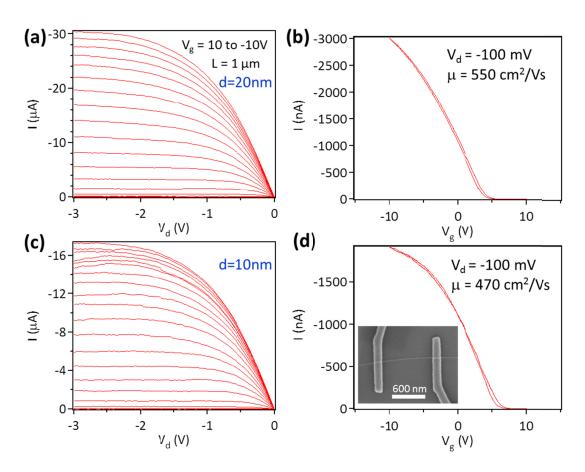

To verify the quality of our nanowires, we have configured them in lateral back-gated devices for electrical characterization. The nanowires were transferred from the growth substrate to a device substrate consisting of degenerately doped Si (which serves as the back gate) with a 50 nm-thick layer of thermal  $\mathrm{SiO}_2$  (which serves as the gate dielectric). To make source and drain metal contacts to individually selected nanowires, a standard lift-off technique was employed using PMMA (950 K), electron-beam lithography, and Ni evaporation (where just prior to evaporation the sample was dipped in buffered HF for  $\sim 2$  s to remove the native oxide coating the nanowires). To make metal contact to the Ge core, a drive-in anneal (320 °C for 10 s) was performed in forming gas (5%  $\mathrm{H}_2$  in  $\mathrm{N}_2$ ) using rapid thermal annealing. Each device contains one nanowire (inset of Fig. 16(d)).

Figs. 16 (a) and (b) show the output and transfer characteristics, respectively, of a representative device with 20 nm Ge core diameter and 1  $\mu$ m channel length. The output characteristics show long channel behavior with high ON-current density. From the transfer characteristics and using the cylinder-on-plane model for the gate capacitance (with an effective dielectric constant of 2.5, which is the average of air (1) and SiO<sub>2</sub> (3.9)[59]) the hole mobility was extracted to be 550 cm<sup>2</sup>/Vs, which is comparable to the best values reported for this nanowire material system[73]. Figs. 16 (c) and (d) show analogous data and similarly good performance for a representative device with 10 nm Ge core diameter, with an extracted hole mobility of 440 cm<sup>2</sup>/Vs.

In addition, we estimate a degenerate hole density  $N \sim 10^{19}$  cm<sup>-3</sup> from  $N = C_g \left( 0 - V_T \right)$  where  $C_g$  is the gate capacitance and  $V_T$  is the threshold voltage (estimated from the transfer curves). In Ch. 3.2 we take advantage of this modulation doping effect to demonstrate high performance vertical Esaki diodes. More generally, a high hole density is important for p-type device contacts, as well as for the development of the junctionless FET which is explored in Ch. 3.4.

FIG. 16. (a) Output and (b) transfer curves for a laterally configured back-gated FET with a Ge/Si core/shell nanowire with 20 nm core diameter and 1  $\mu$ m channel length. (c) Output and (d) transfer curves for a similar device with Ge 10 nm core diameter. Inset: SEM image of a representative device.

Thus we have demonstrated good control of the nanowire growth and produced high quality Ge/Si core/shell nanowires. We next discuss the vertical integration of this material system on Si.

### 2.4.2: Vertical epitaxial growth of Ge nanowires on Si (111)

As mentioned earlier, the vertical epitaxial growth of Ge nanowires has several advantages as a technique for integrating Ge on a Si substrate. The vertical nanowire geometry allows for radial strain relaxation for defect-free interfaces, narrow channel thickness and gate-all-around structure for better gate control, and 3-dimensional device integration for higher device density. Since Ge nanowires normally grow along the <111> direction, vertical epitaxial growth can be achieved on (111) Si substrates. Several studies have verified the feasibility of vertical growth of Ge nanowires on (111) Si using the vapor-liquid-solid (VLS) mechanism[79-81]. Our work closely follows Ref. [81] with the use of Au nanoparticles (20 nm in diameter, colloid purchased from Ted Pella, Inc.) as catalyst. Under a reducedpressure (30 Torr) atmosphere composed of 0.9% GeH<sub>4</sub> in H<sub>2</sub>, a two-step temperature profile was used, in which a high-temperature nanowire nucleation step (1 min. at 380 °C) was followed by a low-temperature nanowire elongation step (300 °C) to minimize conformal Ge deposition (which would lead to nanowire tapering). Fig. 17(a) shows a representative vertical Ge NW with diameter 20 nm and length 1-2 μm. As shown in Fig. 17(b), we can grow small-diameter (20 nm) vertical Ge NWs on Si with good vertical yield (> 80%). Next we discuss the growth technique in greater detail.

FIG. 17. (a) SEM image of a vertical Ge nanowire (20 nm in diameter) epitaxially grown on a Si substrate, taken at a 45° angle. (b) Low magnification image of the epitaxial Ge NW growth.

### 2.4.2.1: HF-addition for enabling epitaxial growth

To enable an epitaxial relationship between the nanowires and the Si substrate, the substrate should have no native oxide. This was achieved by soaking the substrate in 1 M hydrogen fluoride (HF) to create a hydrogen-terminated surface. We also added HF to the as-received Au colloid to a concentration of 0.1 M, to further promote hydrogen-termination [81]. This HF-addition also promotes the adhesion of the Au nanoparticles to the substrate. The H-terminated Si substrate is negatively charged at neutral pH and would tend to repel the as-received Au nanoparticles, which are also negatively-charged due to citrate-stabilization. The addition of HF to the Au colloid lowers the pH of the colloid to about 2, which tends to neutralize the citrate ions and hence reduce the repulsive forces at the substrate. However, the reduced citrate-stabilization tends to cause the colloid to agglomerate,

so that care should be taken to use the colloid immediately after HF-addition (we found no noticeable agglomeration if the colloid is used within 10 min). Finally, for the best results, the time the sample spends in air should be minimized (< 5 min.) after the Au nanoparticles have been deposited.

### 2.4.2.2: Pressure stabilization

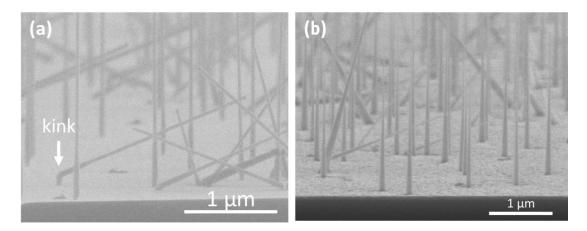

Once the sample has been loaded into the furnace, it was found that the pressure should be stabilized prior to ramping of the temperature; otherwise the nanowires would kink during the nucleation step. Fig. 18(a) shows this effect. Most of the kinked non-vertical nanowires bear the same angle with the substrate, suggesting that an epitaxial relationship with the substrate still exists[81]. Other groups have used this kinking effect to create novel device structures [82, 83], but here we wish to prevent kinking and promote vertical growth.

FIG. 18. (a) SEM image showing kinking during nanowire nucleation, taken at a 75° angle. (b) SEM image showing tapered nanowires.

### 2.4.2.3: Temperature ramp rate

Once the pressure is stable, it is also important to ramp the temperature at a sufficiently high rate to prevent ill-formed nucleation at low temperature (i.e. at less than the desired nucleation temperature). It was found that a local substrate heater capable of a ramp rate  $\sim 5$  °C/s was sufficient for producing > 80% yield of well-formed vertical epitaxial nanowires.

#### 2.4.2.4: Nanowire diameter

The nanowire diameter is governed by the diameter of the Au catalyst. We have chosen 20 nm Au nanoparticles to catalyze the growth of 20 nm-diameter nanowires. This size approaches the lower bound for growth in the <111> direction. For diameters < 15 nm, nanowires begin to exhibit different growth directions, such as <110> and <112> [77, 84], making it more difficult to achieve vertical growth on a (111) substrate. At the same time, for diameters < 10 nm, quantum confinement in the radial direction will increase the effective Ge band gap. This latter effect is undesirable for the tunnel field-effect-transistor since it negates the gains of using a small band gap material for higher tunneling drive current (See Ch. 3).

#### 2.4.2.5: Nucleation and elongation

As is typical in VLS growth[18], the nanowire length is governed by the time spent at the elongation step (growth rate is about 50-100 nm/min). The duration of the nucleation step governs the nucleation yield (the fraction of Au catalyst nanoparticles that nucleate well-formed nanowires); a longer nucleation time corresponds to a higher yield. However, the trade-off is increased nanowire tapering due to thermal decomposition of GeH<sub>4</sub> at the high nucleation temperature. Shown in

Fig. 18(b) is a growth with a high nucleation yield but also a high degree of tapering. At the preferred short nucleation time of 1 min., the nanowires have little tapering, but there is also a low nucleation yield. The reasons for the low nucleation yield are currently unclear. Ref. [85] suggests that the growth conditions (temperature and pressure) could be further optimized. During our investigations, we have also seen SEM evidence of Au catalyst droplets migrating along the Si surface [44]. At ~400 °C, the apparent velocity of droplet migration is ~0.3 nm/min. Such a migration could indicate the presence of an external (non-equilibrium) disturbance during nucleation. Finally, we have observed that the substrate surface properties can have a large influence on the nucleation yield. In particular, we found that a Ge buffer layer can enable high nucleation yields; this we discuss next.

# 2.4.3: Ge buffer layer for nanowire location control and high growth yield

For fundamental studies, it is sufficient to select one nanowire and build a device from it. However, nanowire location control is required for any effort toward array fabrication, 3D integration with lateral CMOS devices, and more complex nanoscale circuits. Ideally, the Au catalyst nanoparticles are first patterned (placement of single particles), and from each nanoparticle a vertical nanowire is grown. Several attempts have been developed to selectively deposit nanoparticles at pre-defined locations[80, 86-92]. For example, using nanoimprint lithography[90], nanosphere lithography[91, 92], or block copolymer-templated deposition[89, 93], one can form nanoparticle patterns in a periodic array and achieve controlled

nanowire or nanotube growth. Other approaches include surface patterning of charges[80, 87, 94]. For example, by patterning a substrate with positive and negative charges using self-assembled monolayers, Huang et al. were able to deposit single 20 nm Au nanoparticles at 400 predefined sites with 91% accuracy[94].

However, for vertical Ge nanowires, there are a few challenges that must be addressed before patterned growth can be realized. First, the above patterning methods often result in oxidation of the Si substrate which would destroy its epitaxial relationship with the growing nanowire. Removal of this oxide and restoration of epitaxial growth may be achieved with the use of Cl-based chemistry during growth, although a high temperature of > 800 °C is normally required which may not be desirable during device integration. Second, both the nucleation yield (the fraction of Au catalyst nanoparticles that nucleate well-formed epitaxial nanowires) and the vertical yield (the fraction of well-formed nanowires that are vertical) should be sufficiently high. As discussed in Ch. 2.4.2.5, high nucleation yield is difficult to achieve without significant tapering of the nanowires.

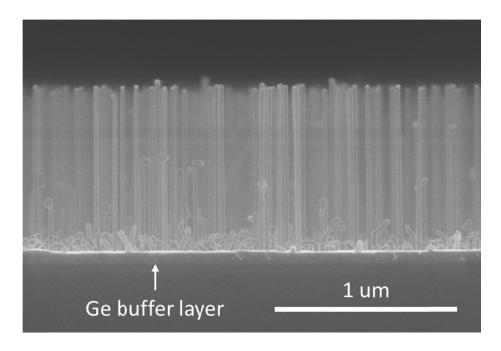

A Ge buffer layer deposited on the Si substrate prior to Au catalyst deposition can address both of the above issues[95]. The native oxide of this layer would not hinder epitaxial growth because  $GeO_x$  is much more volatile than  $SiO_2$  and hence is easily removed during nanowire growth in  $H_2$  ambient. This makes available the

FIG. 19. SEM image showing high yield vertical growth, obtained from a Ge buffer layer that was oxidized in air for  $\sim$ 12 hours.

various patterning techniques mentioned above for patterning vertical Ge nanowires. Also, since the Ge buffer layer is lattice-matched with the nanowire, high nucleation and vertical yields are possible with little nanowire tapering. We have recently demonstrated the feasibility of this approach. We first deposited a  $\sim 50$  nm-thick Ge buffer layer on a (111) Si substrate at 550 °C. Next, the sample was coated with the polyelectrolyte poly-L-lysine (which is positively charged), followed by the deposition of 20 nm Au nanoparticles (negatively charged in colloid). Finally, we grew nanowires using a nucleation step of 1 min at 380 °C. The result is that both nucleation and vertical yields are > 90 %, high enough for patterned NW growth. Fig. 19 shows that a high vertical yield can still be obtained on a Ge buffer layer that has been oxidized in air for  $\sim 12$  hours. The use of polyelectrolyte suggests that a

charge patterning technique (as in Ref. [94]) may be employed for the location control of the catalyst nanoparticles.

While the Ge buffer layer is likely full of crystal defects and hence not suitable as a device layer, it can still serve as a contact for devices. To this end, in the future the layer should be heavily doped. Also, lower deposition temperatures should be tested, since 550 °C could be too high for CMOS compatibility for BEOL integration (see Ch. 2.1). We note that it is possible that doping can also help reduce the crystallization temperature. We have demonstrated that boron-doped Ge layers of resistivity  $\sim$ 1-5 m $\Omega$ -cm can be deposited at 425 °C.

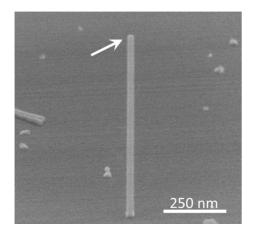

# 2.4.4: Post-growth Au catalyst removal

The Ge nanowire growths discussed above use Au nanoparticles as the catalyst. Au is a contaminant in CMOS technology because it can create deep trap levels in the band gap, which are detrimental to device performance (for example, for tunnel devices, they increase trap-assisted tunneling in the OFF state and degrade the subthreshold swing). There are a few points to note regarding the influence of Au on device performance. First, studies strongly suggest that the electrical properties, including minority carrier transport, of Au-catalyzed Ge and Si nanowires are dominated by surface states rather than bulk impurities [45, 46]; in particular, they find that the influence of Au residing in the bulk is negligible. Second, in Aucatalyzed vapor-liquid-solid growth of Si and Ge nanowires, most of the Au remains exposed at the surface and nanowire sidewalls [44, 96]. Hence the removal of the Au exposed at surfaces would largely eliminate its influence on electrical behavior.

Woodruff et al demonstrated a wet chemical etch for this purpose [81]. We have experimentally verified their result as shown in Fig. 20.

FIG. 20. Au catalyst removed from vertical Ge nanowire using a wet chemical etch (described in Ref. [81]).

# 2.5: Summary

In summary, we have developed several growth techniques. We have grown large quantities of Al-catalyzed small diameter Si nanowires with high growth rates and large aspect ratios using the VLS method. The Al doping levels in small diameter Si nanowires can be reduced so the nanowires still exhibit semiconductor characteristics. We have grown Ge/Si core/shell nanowires that exhibit hole mobilities > 450 cm²/Vs. We have achieved good control of the growth of vertical epitaxial Ge nanowires on Si with 20 nm diameter; furthermore, we have achieved nucleation and vertical yields > 90% using a Ge buffer layer. Finally we have demonstrated post-growth Au catalyst removal. These developments address several of the important problems facing hybrid nanowire-CMOS systems.

# **Chapter 3**

# Toward Ge nanowire-based vertical tunnel field-effect transistors for hybrid nanowire-CMOS systems

### 3.1: Introduction

# 3.1.1: Subthreshold non-scaling in CMOS

As discussed in Ch. 1, one of the fundamental challenges that aggressively scaled devices face is increased power dissipation due to subthreshold non-scaling. Along with transistor scaling, the supply voltage  $V_{DD}$  and the threshold  $V_T$  need to be scaled accordingly to minimize power dissipation and reduce high-field effects. However, in a conventional MOSFET, a reduction in  $V_T$  results in an exponential increase in the OFF current  $I_{OFF}$ , which would increase static power dissipation. To first order, the exponential dependence of  $I_{OFF}$  on  $V_T$  in an conventional MOSFET with ideal gate coupling is given by  $I_{OFF} \propto \exp\left(-qV_T/kT\right)$ , where q is the electronic charge, k is the Boltzmann constant, and T is the temperature. This equation illustrates a theoretical limit to the rate at which a conventional transistor can be turned off. The origin of this limit lies in the thermal injection of carriers over a barrier into the channel (Figs. 21(a) and (b)). Due to the Boltzmann distribution, some carriers always have enough energy to overcome the barrier, and furthermore

the application of a gate voltage to raise the barrier can only reduce the current at a finite limited rate. Here it is convenient to define in the subthreshold region a figure of merit called the subthreshold swing SS as  $SS = \partial V_G/\partial \log I_D$ , which measures the gate voltage swing needed to reduce the current by a factor of 10. Equating  $I_{OFF} \propto \exp\left(-qV_T/kT\right) = 10^{-V_T/SS} \text{ shows that SS has a theoretical lower limit of } kT/q \cdot \ln(10) \approx 60 \,\text{mV/decade} \text{ at room temperature. For practical devices SS is typically 60-70 mV/decade and normally degrades with extreme scaling. Fig. 5 (in$

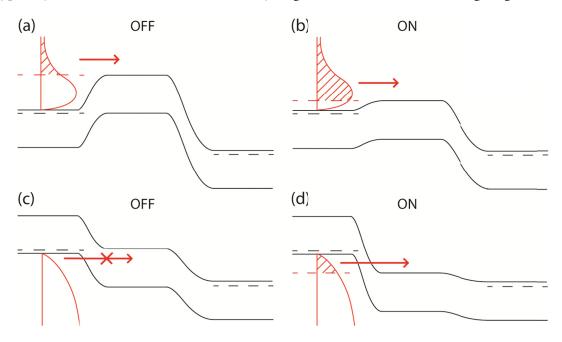

FIG. 21. (a-b) Band diagrams showing the operation of a conventional n-type FET in the (a) ON state and (b) OFF state. The turn-off process is limited by the Boltzmann distribution of carriers at the source. (c-d) Corresponding band diagrams showing the operation of a n-type TFET. The current here is determined by tunneling of electrons from the valence band in the source to the conduction band in the channel.

Ch. 1) shows the relationship of  $I_{ON}$ ,  $I_{OFF}$ ,  $V_T$ ,  $V_{dd}$ , and SS in a conventional MOSFET. To maintain acceptably low  $I_{OFF}$ , the non-scaling of SS leads to the non-scaling of  $V_T$ . To maintain acceptably high  $I_{ON}$ , the non-scaling of  $V_T$  in turn puts a restriction on  $V_{DD}$  scaling, and causes severe power dissipation (both static and dynamic) and reliability issues for aggressively scaled devices (see Ch. 1).

### 3.1.2: The tunnel field-effect transistor