# **Wireless Testing of Integrated Circuits**

by

### Dae Young Lee

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2012

#### **Doctoral Committee:**

Professor John P. Hayes, Co-Chair Assistant Professor David D. Wentzloff, Co-Chair Emeritus Professor David J. Anderson Associate Professor Michael P. Flynn © Dae Young Lee

2012

To My Family

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to thank my parents, sister, and her husband. I could only successfully finish my graduate study with their strong and constant support. I want to express my sincere gratitude and appreciation to my advisors Prof. John P. Hayes and Prof. David D. Wentzloff for their support, encouragement and guidance for these past four years. It is very special to have two advisors, and I was given a great opportunity to have a good relationship with them. I also would like to extend my sincere gratitude to my other committee members, Prof. Michael P. Flynn and Prof. David J. Anderson, for devoting their time to review this thesis and advising me with valuable suggestions.

I would like to acknowledge my colleagues for constructive and insightful discussions. I have not directly collaborated with them but I greatly appreciate their assistance. I thank Dr. Youngmin Park, Sangwook Han, Jonathan K. Brown, Seunghyun Oh, Kuo-Ken Huang, Osama Ullah Khan, Muhammad Faisal, Nathan Roberts, Elnaz Ansari, and Ryan Rogel. I also express my thank to Dr. Geonwook Yoo, Dr. Kenneth Zick, Chien-Chih Yu, Armin Alaghi, Te-Hsuan Chen, Dr. Jerry Kao, Gwanghyeon Baek, Yonghyun Shim, Dr. Junseok Heo, Yongjun Park, Hyo Gyuem Rhew, and Hyun Kum.

Excellent support from the staff is greatly appreciated. I would like to thank Joel VanLaven for his CAD tool support. I also thank Beth Stalnaker, Deborah Swartz, Melanie Caughey, Denise DuPrie, and Fran Doman for administrative support throughout

my graduate career. I wish to acknowledge the Samsung Scholarship, the Defense Advanced Research Projects Agency (DARPA), and the Alexander von Humboldt Foundation for funding this research.

## TABLE OF CONTENTS

| DEDICATION                                               | ii   |

|----------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                         | iii  |

| LIST OF FIGURES                                          | vii  |

| LIST OF TABLES                                           | xii  |

| LIST OF APPENDICES                                       | xiii |

| ABSTRACT                                                 | xiv  |

| CHAPTER                                                  |      |

| I. Introduction                                          | 1    |

| 1.1. Motivation                                          | 1    |

| 1.2. Communication technologies for wireless testing     |      |

| 1.2.1. Near-field vs. RF communication                   |      |

| 1.2.2. Inductive and capacitive coupling                 |      |

| 1.3. Related work                                        |      |

| 1.3.1. Wireless testing of digital ICs                   |      |

| 1.3.2. Wireless testing of analog ICs                    |      |

| 1.3.3. Wireless interconnect for 3D ICs                  |      |

| 1.4. Thesis outline                                      | 20   |

| II. Capacitively-Coupled Channel for Wireless Testing    | 23   |

| 2.1. Introduction                                        | 23   |

| 2.2. Coupling techniques for wireless testing            | 24   |

| 2.3. Circuit model of capacitive coupling                |      |

| 2.4. Cross-talk analysis                                 | 30   |

| 2.5. Misalignment tolerance                              |      |

| 2.6. Summary                                             | 35   |

| III. Single-Channel Capacitive Link for Wireless Testing | 37   |

| 3.1. Introduction                                        | 37   |

| 3.2. Channel modeling and modulation                    | 40  |

|---------------------------------------------------------|-----|

| 3.2.1. Capacitive channel model                         |     |

| 3.2.2. Pulse width modulation                           |     |

| 3.2.3. Estimation of pulse-width variation              | 47  |

| 3.3. Overall architecture                               |     |

| 3.3.1. PWM transmitter                                  |     |

| 3.3.2. DLL-based receiver                               |     |

| 3.3.3. Feed-forward clock selector                      | 57  |

| 3.4. Communication link measurement results             | 60  |

| 3.5. Summary                                            | 63  |

| IV. Non-Contact I/O Pad for Wafer-Level Testing         | 64  |

| 4.1. Introduction                                       | 64  |

| 4.2. Channel model for RZ signaling                     | 67  |

| 4.3. Overall architecture                               |     |

| 4.3.1. Transmitter with adjustable power                | 70  |

| 4.3.2. Receiver pre-amplifier and hysteresis comparator | 72  |

| 4.3.3. Receiver demodulator                             | 75  |

| 4.4. Electrical alignment markers                       | 78  |

| 4.5. Communication link measurement results             | 81  |

| 4.6. Summary                                            | 85  |

| V. On-Chip Wireless Voltage Measurement                 | 86  |

| 5.1. Introduction                                       | 86  |

| 5.2. Integrating ADC                                    | 90  |

| 5.3. Wireless voltage measurement architecture          | 92  |

| 5.4. Prototype implementation                           | 93  |

| 5.5. Prototype measurement results                      | 96  |

| 5.6. Summary                                            | 102 |

| VI. Contributions and Future Work                       | 104 |

| 6.1. Thesis contributions                               | 104 |

| 6.2. Suggestions for future work                        | 107 |

| APPENDICES                                              | 110 |

| BIBLIOGRAPHY                                            | 120 |

## LIST OF FIGURES

| <u>Figure</u> |                                                                                                                                 |    |

|---------------|---------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1           | (a) IC probe card [58], and (b) Advantest T7723 mixed signal test equipment [1]                                                 | 3  |

| 1.2           | Trends in (a) number of I/O pins, and (b) I/O data rates predicted in [72]                                                      | 4  |

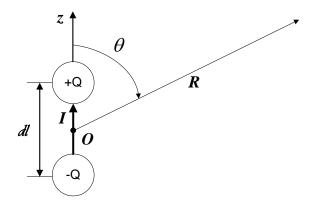

| 1.3           | Illustration of near-field and far-field solutions                                                                              | 7  |

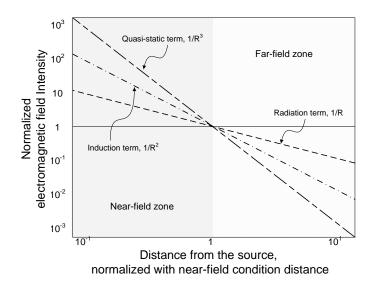

| 1.4           | Near-field and far-field boundary based on [26]                                                                                 | 8  |

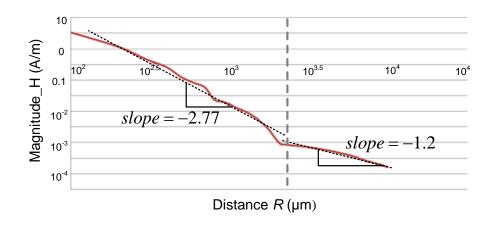

| 1.5           | Simulated magnetic field magnitude <i>H</i> as a function of distance <i>R</i> from the source                                  | 9  |

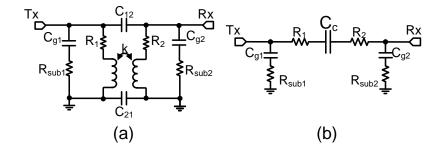

| 1.6           | Equivalent circuit models for (a) coupled inductors [50], and (b) coupled capacitors                                            | 11 |

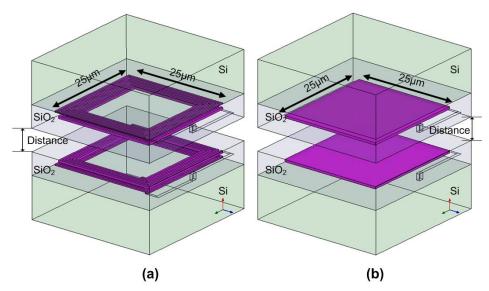

| 1.7           | 3D models of (a) on-chip inductor, and (b) on-chip capacitor                                                                    | 12 |

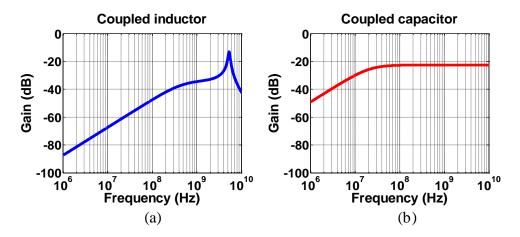

| 1.8           | Simulated frequency response with 20 µm communication distance for (a) coupled inductors, and (b) coupled capacitors            | 13 |

| 1.9           | Prototypes of wireless testing: (a) capacitive wafer-level probing [12], and (b) inductively-coupled non-contact probecard [71] | 16 |

| 1.10          | (a) Data rates, and (b) communication distance of selected prior 3D on-chip communication links                                 | 19 |

| 2.1           | Simulated coupled capacitor model with fringing capacitance                                                                     | 27 |

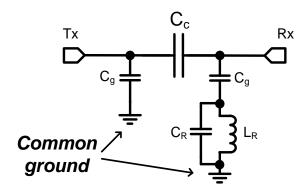

| 2.2           | More accurate on-chip capacitor model with current return paths                                                                 | 29 |

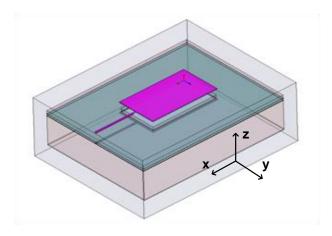

| 2.3           | On-chip 3D model of capacitive coupling                                                                                         | 29 |

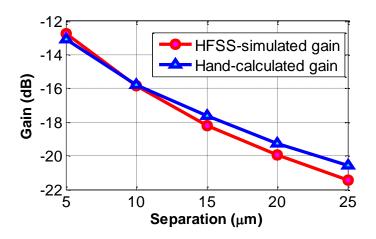

| 2.4           | Gain vs. plate separation for capacitive coupling                                                                               | 30 |

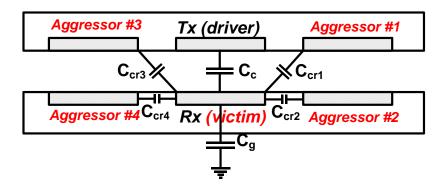

| 2.5           | Cross-talk model for on-chip capacitive coupling                                                                                | 31 |

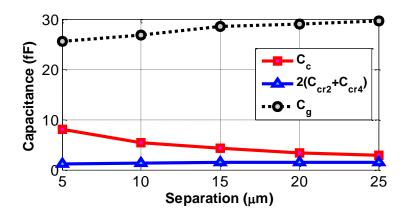

| 2.6           | Simulated capacitance vs. plate separation                                                                                      | 32 |

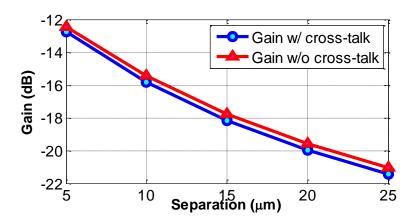

| 2.7  | Gain comparison with cross-talk effects                                                                                                                             | 3 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

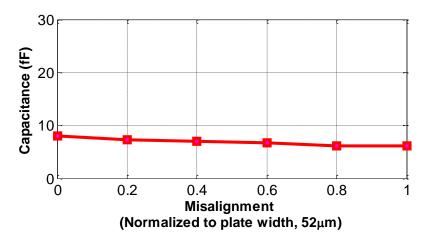

| 2.8  | Coupling capacitance vs. misalignment                                                                                                                               | 1 |

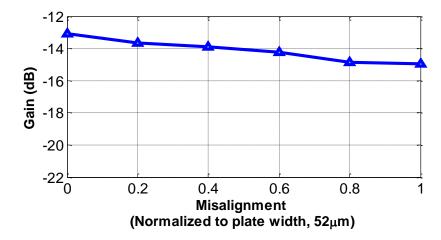

| 2.9  | Gain vs. misalignment                                                                                                                                               | 1 |

| 2.10 | Proposed wireless tester                                                                                                                                            | 5 |

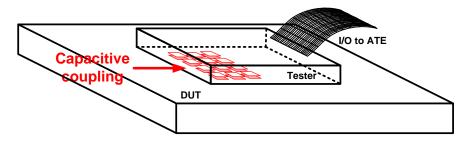

| 3.1  | Proposed capacitively-coupled wireless IC testing with bond pads compatible with standard I/O cells                                                                 | 3 |

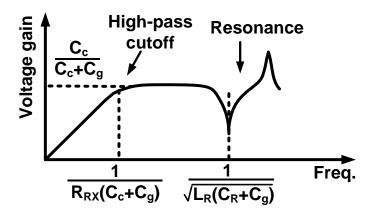

| 3.2  | Lumped circuit model of a capacitive channel between a DUT and ATE40                                                                                                | ) |

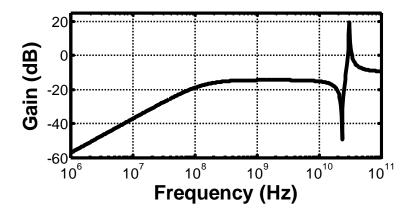

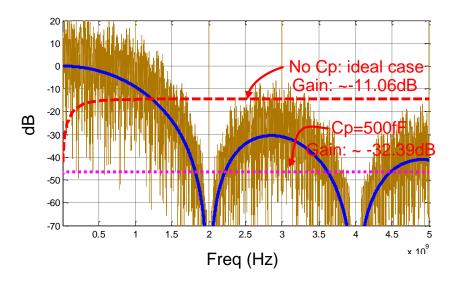

| 3.3  | Frequency response of the proposed voltage transfer model                                                                                                           | 1 |

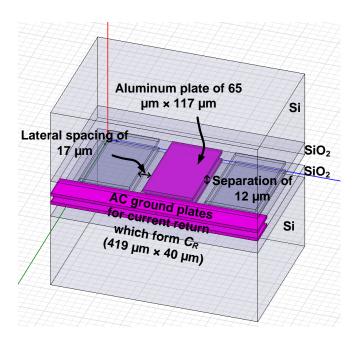

| 3.4  | 3D model for EM simulation by HFSS v11                                                                                                                              | 3 |

| 3.5  | Spice simulated frequency response of a channel with the proposed lumped model                                                                                      | 1 |

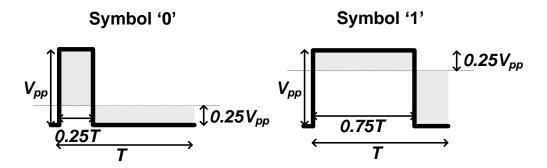

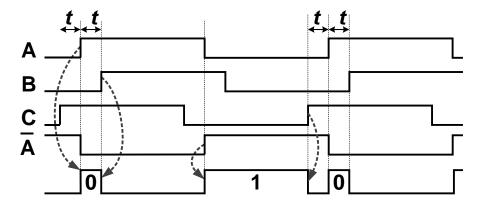

| 3.6  | PWM bit symbols for '0' and '1'                                                                                                                                     | 5 |

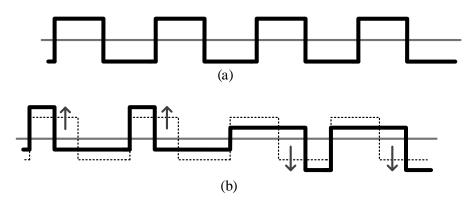

| 3.7  | Illustration of signal level fluctuation, (a) DC-balanced 50% duty-cycled signals, (b) DC-unbalanced PWM signals with '0011'                                        | 5 |

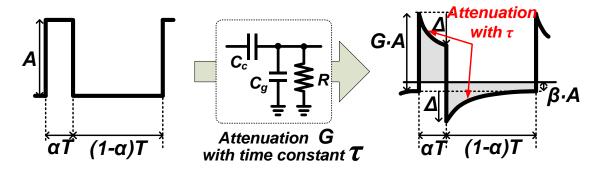

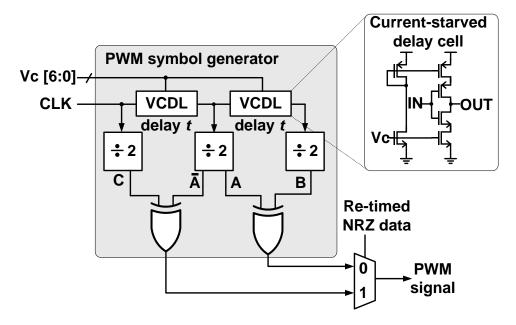

| 3.8  | PWM signals passed through a capacitive channel                                                                                                                     | 7 |

| 3.9  | DC offsets from the center level for PWM signals ( $T = 1 \text{ ns}$ , $\alpha = 0.25$ )48                                                                         | 3 |

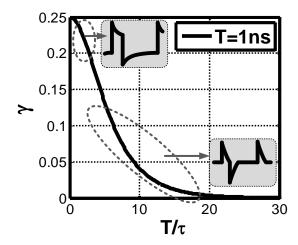

| 3.10 | Matlab simulation results of (a) the maximum pulse-width variation, and (b) the number of pulses to achieve the maximum variation ( $T = 1$ ns, $\alpha = 0.25$ )49 | ) |

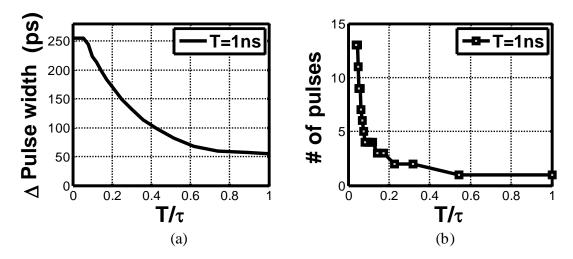

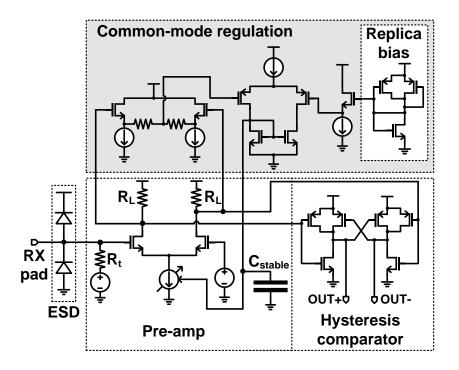

| 3.11 | PWM modulator with an XOR-based edge combiner                                                                                                                       | 1 |

| 3.12 | Symbol generation for data '010'                                                                                                                                    | 2 |

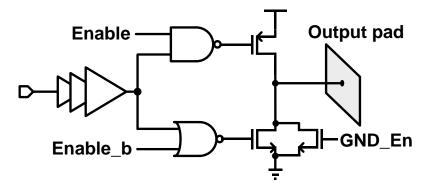

| 3.13 | Output pad driver with a tri-state inverter                                                                                                                         | 2 |

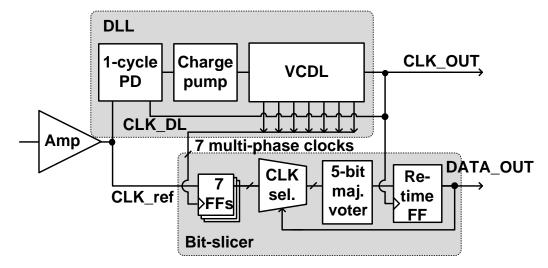

| 3.14 | Overall block diagram of the proposed DLL-based bit-slicing receiver53                                                                                              | 3 |

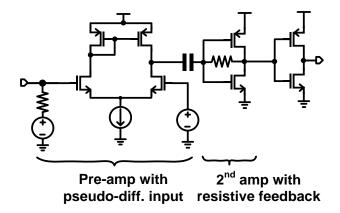

| 3.15 | Schematic of the 2-stage receiver amplifier                                                                                                                         | 3 |

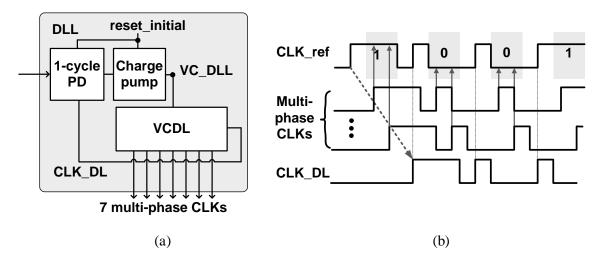

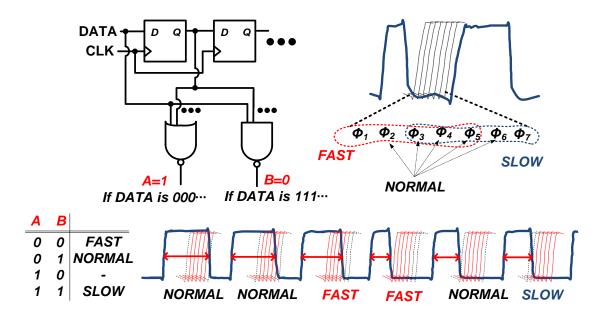

| 3.16 | (a) Block diagram of the DLL, and (b) operation of bit-slicing with multiphase clocks                                                                               | 1 |

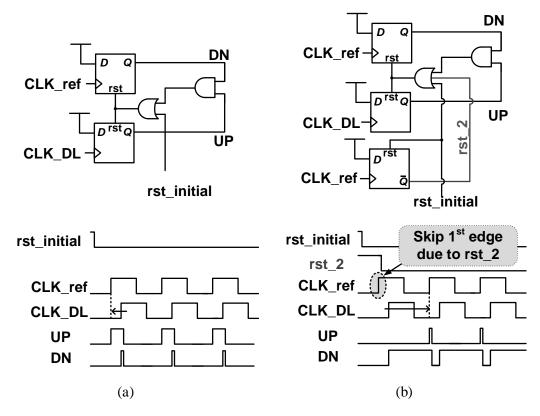

| 3.17 | Phase-locking characteristics of (a) conventional PFD, and (b) proposed 1-cycle PD                                                                                  | 5 |

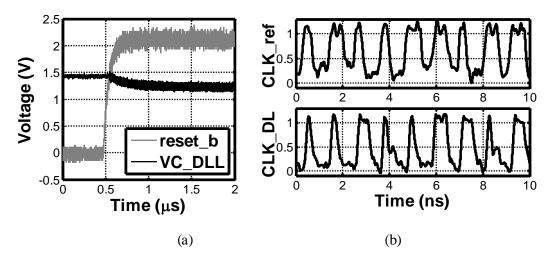

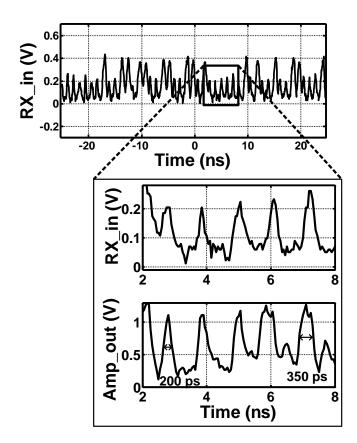

| 3.18 | Measurement results from the implemented DLL: (a) step response, and (b) in/output PWM waveforms                                                            | 57 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.19 | Feed-forward dynamic clock selector for signal-level fluctuation                                                                                            | 58 |

| 3.20 | Measured pulse-width changes due to signal level fluctuation                                                                                                | 58 |

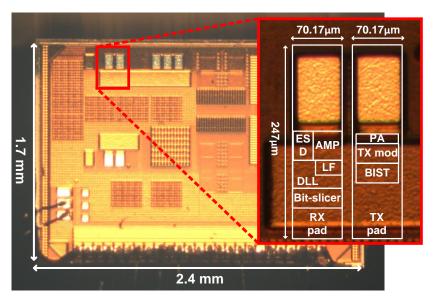

| 3.21 | Die photomicrograph of the TX and RX pads                                                                                                                   | 60 |

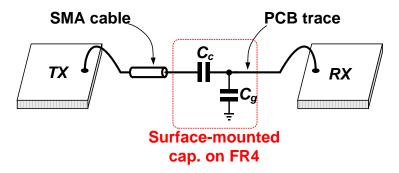

| 3.22 | Test setup for the prototype link                                                                                                                           | 61 |

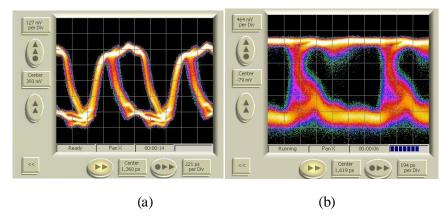

| 3.23 | Measured eye-diagram of (a) TX PWM signals, and (b) RX output                                                                                               | 61 |

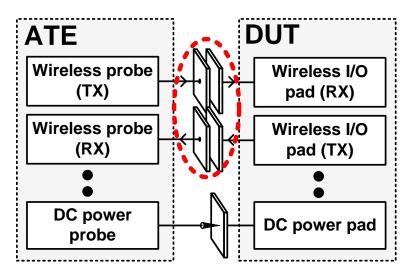

| 4.1  | Capacitively-coupled wireless testing system                                                                                                                | 67 |

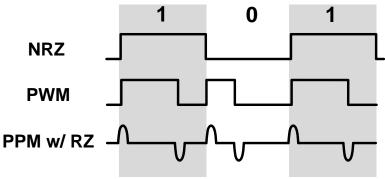

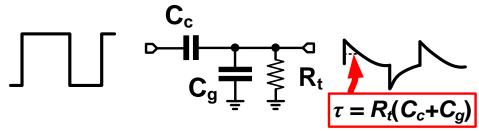

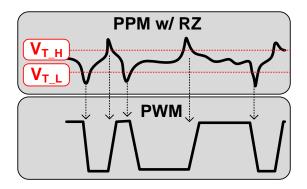

| 4.2  | PPM with RZ signaling                                                                                                                                       | 68 |

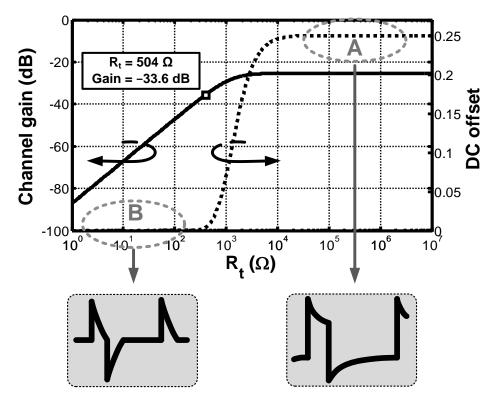

| 4.3  | Capacitive channel model with the termination resistor $R_t$                                                                                                | 68 |

| 4.4  | Channel gain and DC fluctuation factor with various $R_t$ values at 1 GHz                                                                                   | 69 |

| 4.5  | Simulated waveforms. PPM RZ signals are generated from PWM signals with a terminated capacitive channel                                                     | 70 |

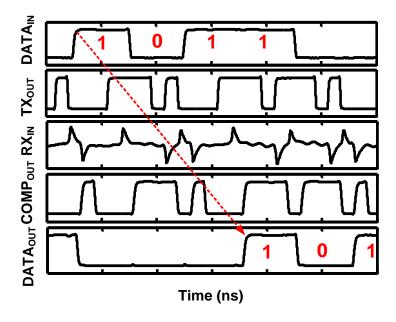

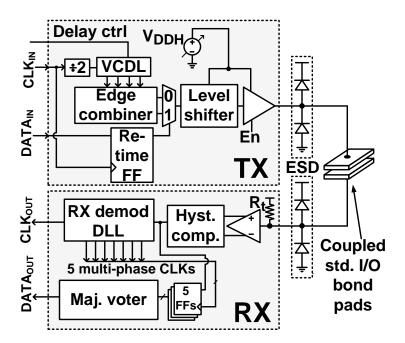

| 4.6  | Block diagram of TX and RX                                                                                                                                  | 71 |

| 4.7  | (a) Schematic of the PWM modulator, (b) TX tri-state driver with thick-oxide devices MOS_33                                                                 | 71 |

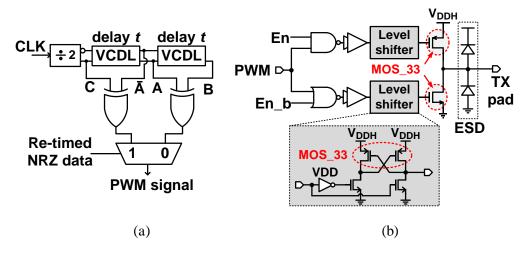

| 4.8  | Schematic of the RX amplifier with a hysteresis comparator                                                                                                  | 72 |

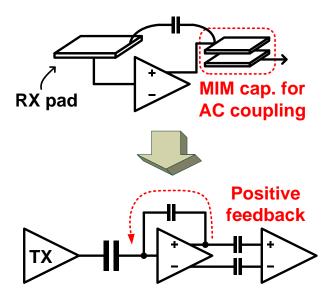

| 4.9  | Potential positive feedback from unwanted coupling between the RX pad and AC-coupling capacitor                                                             | 73 |

| 4.10 | PWM signals regenerated from PPM RZ signals with the hysteresis comparator                                                                                  |    |

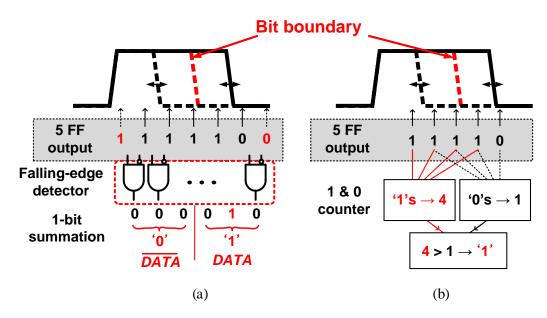

| 4.11 | Two bit-decision schemes with symbol '1': (a) falling edge detection, and (b) counter-based detector                                                        | 75 |

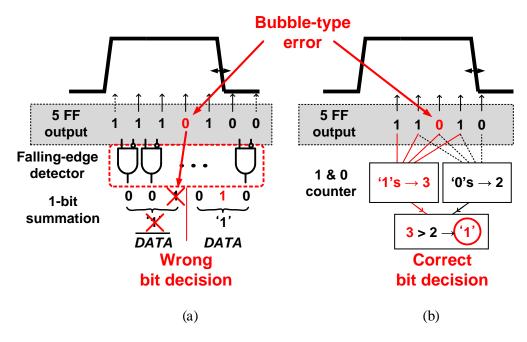

| 4.12 | Two bit-decision schemes with a bubble-type error: (a) falling edge detection makes wrong bit decision, but (b) counter-based detector suppresses the error | 76 |

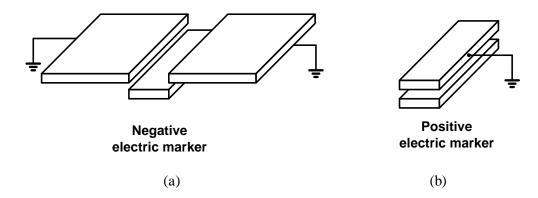

| 4.13 | Two types of electrical alignment markers: (a) negative marker, and (b) positive marker                                                                     | 77 |

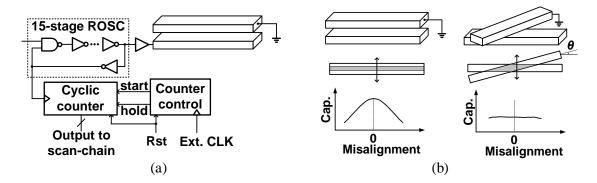

| 4.14 | (a) Schematic of capacitance measurement circuits, and (b) alignment mechanism                                                                              | 77 |

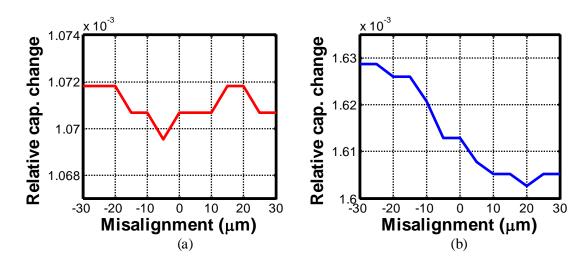

| 4.15 | Measured relative capacitance change without rotation misalignment from (a) negative <i>x</i> -marker, and (b) positive <i>y</i> -marker | 79   |

|------|------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.16 | Measured relative capacitance change with rotation misalignment from (a) negative <i>x</i> -marker, and (b) positive <i>y</i> -marker    | 79   |

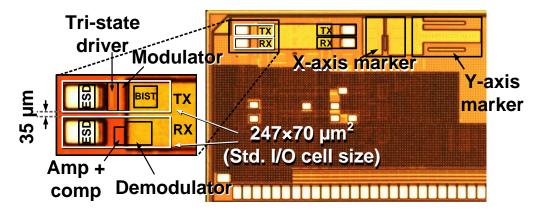

| 4.17 | Die photomicrograph of the prototype chip                                                                                                | 81   |

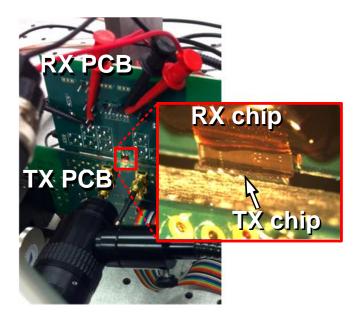

| 4.18 | Test setup with a micro-manipulator                                                                                                      | 81   |

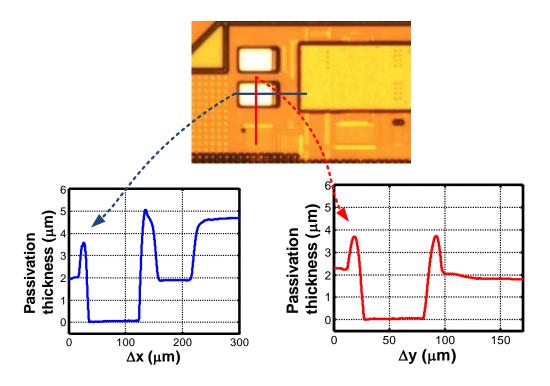

| 4.19 | Test chip surface profile measured by a Dektak 6M surface profiler                                                                       | 82   |

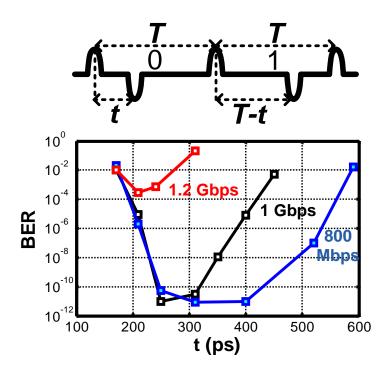

| 4.20 | Measured BER vs. minimum pulse distance $t$ ( $T = 1$ ns)                                                                                | 83   |

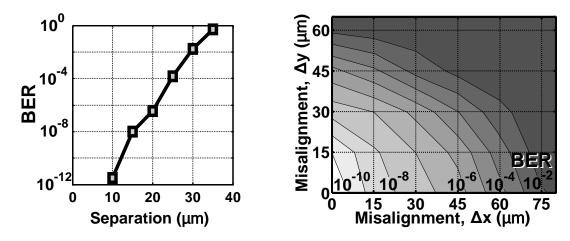

| 4.21 | Measured BER vs. (a) pad separation, and (b) x- and y-misalignment                                                                       | 84   |

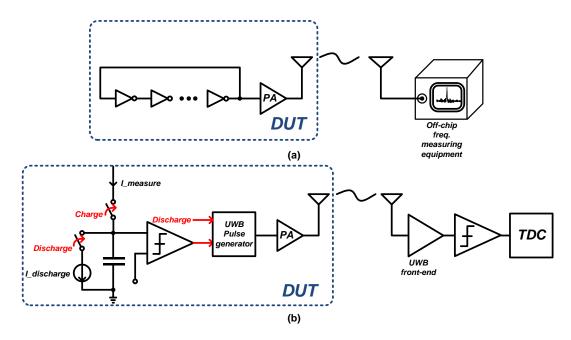

| 5.1  | Possible implementations of analog IC testing                                                                                            | 89   |

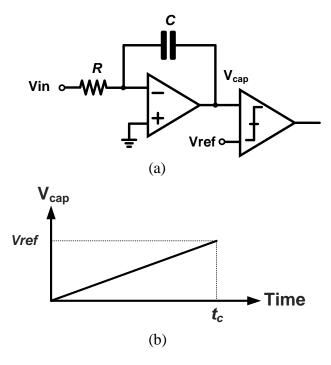

| 5.2  | (a) Schematic of a single-slope ADC, and (b) its timing diagram                                                                          | 91   |

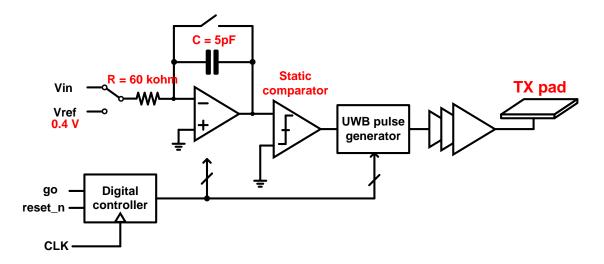

| 5.3  | Schematic of the prototype voltage measurement circuits                                                                                  | 94   |

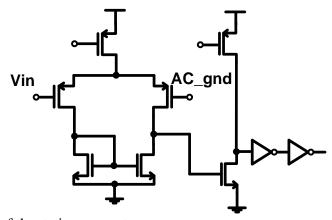

| 5.4  | Schematic of the static comparator                                                                                                       | 94   |

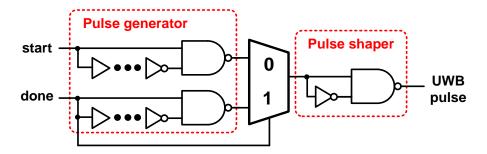

| 5.5  | Schematic of the UWB pulse generator                                                                                                     | 95   |

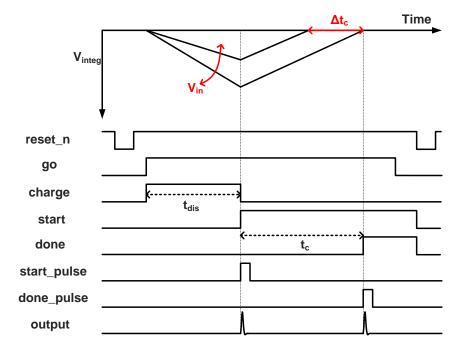

| 5.6  | Timing diagram of the prototype                                                                                                          | 95   |

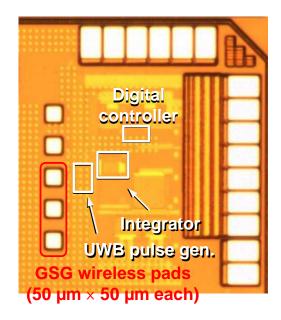

| 5.7  | Die photomicrograph of the prototype                                                                                                     | 97   |

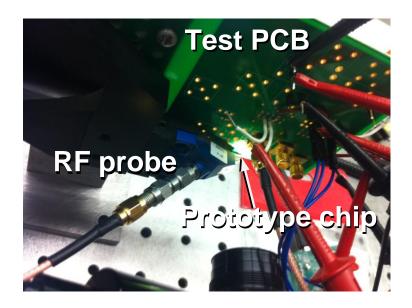

| 5.8  | Test setup                                                                                                                               | 97   |

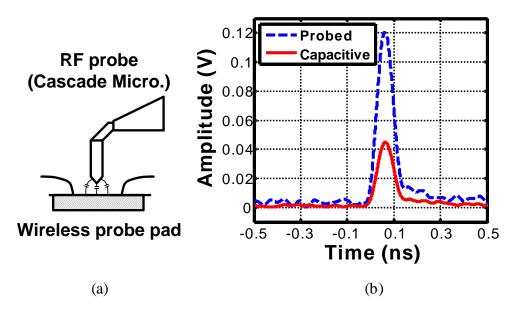

| 5.9  | (a) Capacitive coupling between a wireless probe pad and an RF probe, and (b) measured UWB pulse                                         | 98   |

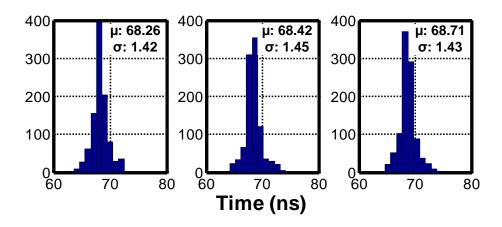

| 5.10 | Histograms of three different wireless measurement setups with $V_{in} = 600$ mV                                                         | 99   |

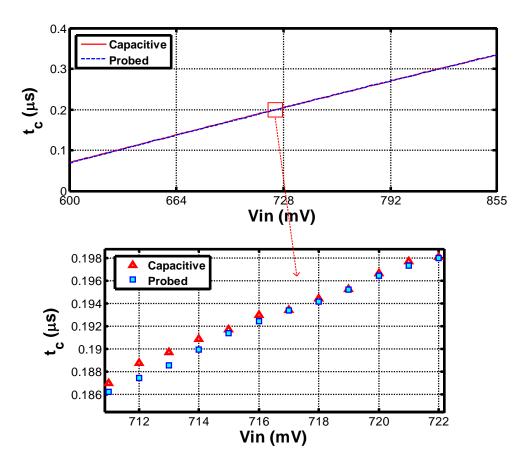

| 5.11 | Measured $t_c$ with $V_{in}$ from 600 mV to 855 mV with 1 mV step                                                                        | 99   |

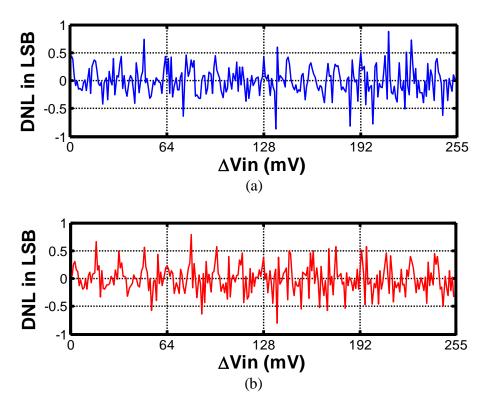

| 5.12 | Measured DNL for (a) wired setup, and (b) wireless setup                                                                                 | 101  |

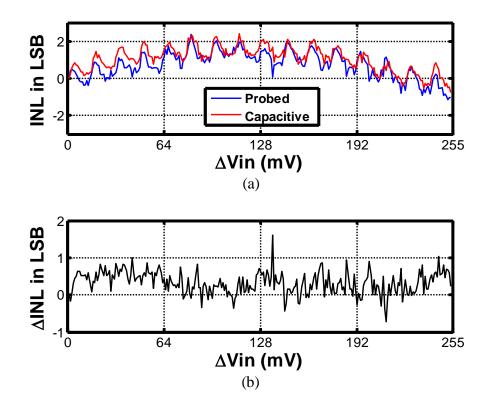

| 5.13 | (a) Measured INL, and (b) INL added by the wireless channel                                                                              | 101  |

| A.1  | Elemental electric dipole                                                                                                                | 112  |

| A.2  | Near-field and far-field boundary based on [18]                                                                                          | 114  |

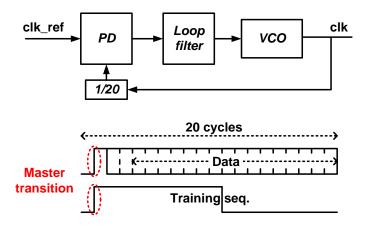

| B.1  | Illustration of 16B/20B encoding and CDR by a PLL [83]                                                                                   | .116 |

## LIST OF TABLES

| <u>l'a ble</u> |                                                                                   |

|----------------|-----------------------------------------------------------------------------------|

| 1.1            | Measurement parameters for IC testing                                             |

| 2.1            | Performance comparison of various prior chip-level wireless communication systems |

| 2.2            | Extracted passive element values from EM simulation with 10 µm separation .32     |

| 3.1            | Detailed passive element values from EM simulation with 12 µm spacing44           |

| 3.2            | Performance summary of the 1 <sup>st</sup> prototype chip62                       |

| 4.1            | Simulated coupling capacitance and oscillation frequency                          |

| 4.2            | Performance summary of the 2 <sup>nd</sup> prototype chip85                       |

## LIST OF APPENDICES

| <b>Appendix</b> |                              |     |

|-----------------|------------------------------|-----|

| A.              | Near-field basics            | 111 |

| B.              | Clock data recovery with PWM | 115 |

**ABSTRACT**

**Wireless Testing of Integrated Circuits**

by

Dae Young Lee

Co-Chairs: John P. Hayes and David D. Wentzloff

Integrated circuits (ICs) are usually tested during manufacture by means of

automatic testing equipment (ATE) employing probe cards and needles that make

repeated physical contact with the ICs under test. Such direct-contact probing is very

costly and imposes limitations on the use of ATE. For example, the probe needles must

be frequently cleaned or replaced, and some emerging technologies such as three-

dimensional ICs cannot be probed at all. As an alternative to conventional probe-card

testing, wireless testing has been proposed. It mitigates many of the foregoing problems

by replacing probe needles and contact points with wireless communication circuits.

However, wireless testing also raises new problems which are poorly understood such as:

What is the most suitable wireless communication technique to employ, and how well

does it work in practice?

xiv

This dissertation addresses the design and implementation of circuits to support wireless testing of ICs. Various wireless testing methods are investigated and evaluated with respect to their practicality. The research focuses on near-field capacitive communication because of its efficiency over the very short ranges needed during IC manufacture. A new capacitive channel model including chip separation, cross-talk, and misalignment effects is proposed and validated using electro-magnetic simulation studies to provide the intuitions for efficient antenna and circuit design. We propose a compact clock and data recovery architecture to avoid a dedicated clock channel. An analytical model which predicts the DC-level fluctuation due to the capacitive channel is presented. Based on this model, feed-forward clock selection is designed to enhance performance. A method to select proper channel termination is discussed to maximize the channel efficiency for return-to-zero signaling.

Two prototype ICs incorporating wireless testing systems were fabricated and tested with the proposed methods of testing digital circuits. Both successfully demonstrated gigahertz communication speeds with a bit-error rate less than  $10^{-11}$ . A third prototype IC containing analog voltage measurement circuits was implemented to determine the feasibility of wirelessly testing analog circuits. The fabricated prototype achieved satisfactory voltage measurement with 1 mV resolution. Our work demonstrates the validity of the proposed models and the feasibility of near-field capacitive communication for wireless testing of ICs.

### Chapter I

#### **Introduction**

In this chapter, we briefly discuss the background of wireless integrated circuit (IC) testing. Also, we review existing research on wireless testing, and discuss on-chip interconnect for three dimensional ICs (3D ICs) for comparison. Some of the material in this chapter appears in [45].

#### 1.1 Motivation

Generally, testing is proving the functional correctness of a product [4]. Testing of ICs can be regarded as a set of tasks to check the functionality of ICs. In modern IC manufacturing, testing is not limited to the final check for functionality. Rather, engineers perform multiple tests between all the major production stages to reduce overall manufacturing cost by removing defective products before each stage.

IC testing methods can be categorized by their input and output signal types as shown in Table 1.1, which include digital and analog. For digital circuits, functionality is tested with a set of digital test patterns, and the output results are collected by automatic test equipment (ATE) to match them with the desired responses (signatures). In addition, operating frequency and power consumption are measured to check the performance of

**Table 1.1** Measurement parameters for IC testing.

| Functional test                                                               |                                                                                                                                      | Characterization                                                                                                             |                                                                                       |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Digital test                                                                  | Analog test                                                                                                                          | Manufacturing steps                                                                                                          | In-field<br>monitoring                                                                |

| <ul><li>Digital outputs</li><li>Frequency</li><li>Power consumption</li></ul> | <ul> <li>Analog outputs</li> <li>Frequency</li> <li>Power     Consumption</li> <li>Gain</li> <li>Linearity</li> <li>Noise</li> </ul> | <ul> <li>Device mismatch</li> <li>V<sub>th</sub></li> <li>Temperature</li> <li>Leakage current</li> <li>Parasitic</li> </ul> | <ul><li>NBTI</li><li>Soft error</li><li>Temperature</li><li>Leakage current</li></ul> |

digital ICs. For analog circuits, various analog or continuous parameters are measured with analog test inputs to check their functionality. If the performance of a device under test (DUT) meets the desired specifications, it passes the test. Thus, analog testing can be regarded as a performance measurement rather than matching measured outputs to signatures. The parameters typically measured in analog testing are voltage, current, gain, operation frequency, mismatch, and linearity [62].

Testing is not confined to functionality checking only. Process characterization is another important test requirement for IC production. Characterization attempts to quantify the performance of a manufactured IC. It is usually applied to a new design or process technology. Using specially designed circuits, which differ from these of the final product, these circuits are designed to accurately represent key analog or digital parameters of the product.

In this thesis, we refer to characterization after manufacturing as on-line monitoring to avoid ambiguity. Dimension mismatch, threshold voltage, temperature, leakage

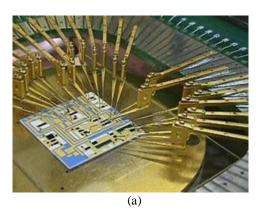

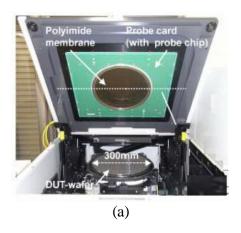

Figure 1.1 (a) IC probe card [58], and (b) Advantest T7723 mixed-signal test equipment [1].

parasitic capacitance and inductance, and doping fluctuation are measured before and after the manufacturing process. Negative bias temperature instability (NBTI) and soft-errors can be monitored later in the field.

In practice, the foregoing testing methods may be combined in various ways to ensure the functionality of the ICs. Additionally, since the overall cost can be reduced if we can find defective devices earlier, testing must be performed between the major manufacturing steps. However, recent advances in IC technology dramatically increase the density of transistors in ICs, resulting in a steady increase in IC complexity and thus an increase in testing costs [72][73]

One conventional way to reduce growing IC testing cost is the automation of testing. ATE is a general and highly automated tool for IC testing. It transmits test input patterns to the DUTs and collects responses for comparison. The ATE is usually equipped with a probe card which consists of multiple probe tips and interface circuits that form a direct electrical connection between I/O pads on the DUT and ATE, as depicted in Figure 1.1. Since probe tips make physical contacts with the DUT, they are usually designed to have sufficient elasticity so as not to deform the DUT [24][76]. The

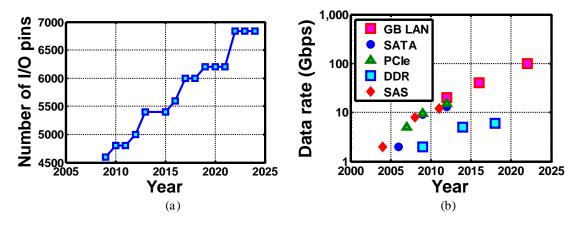

Figure 1.2 Trends in (a) number of I/O pins and (b) I/O data rate predicted in [72].

same ATE can be used for different DUTs by replacing probe cards. Analog probe cards are more complex than digital, since they must support more accurate impedance matching and higher operating frequency [77].

However, conventional probe cards and probing methods have numerous drawbacks. As chips get more highly integrated, the number of their I/O pads tends to increase, as shown in Figure 1.2. Although ball grid array (BGA) and flip-chip technology provide more pins, the number of pins is still limited. Thus, the size and pitch of the probe needles used for testing should get smaller to integrate more pins in a given area. The small size of bonding pads and solder balls causes problems in wafer-level testing [46]. For such small contact points and probe needles, even minor physical damage from contact can cause significant probe deformation. In addition, accumulated debris on the probe tips interferes with testing by increasing the resistance from probe to wafer surface. The debris can be removed with an abrasive cleaner, but that can damage the probe needles.

Increasing demand for devices with multiple chips such as system-in-packages (SIPs), multi-chip modules (MCMs), and three-dimensional ICs (3D ICs) makes testing

with direct-contact probe cards more difficult since conventionally the probe cards do not support the flexible location of contact points [2]. They are unsuitable for parallel testing of multiple dies for the same reason. Additionally, through-silicon vias (TSVs) and micro-bumps for 3D ICs are more difficult to test with conventional probe cards than standard I/O pads because of their size and pitch [6]. Wireless testing is also advantageous for 3D ICs due to the fragility of TSVs and micro-bumps [46].

The limitations of direct-contact testing mostly derive from the physical contact between the wafer and the probe needles. If we could completely replace physical contacts with wireless communication, the foregoing problems could be greatly alleviated [45]. Wireless testing supports the flexibility of contact location as well, making both SIP testing and parallel testing possible.

Wireless testing requires additional circuits and antennas on the die, which should not consume too much chip area. Additionally, the functionality of the original device should not be affected by the components added for testing. Electrical power also needs to be delivered wirelessly to completely remove wired lines during testing. However, as long as the number of signal pads is a significant fraction of the total number of I/O pads, wireless testing of signal pads with wired power can still be beneficial due to the significant reduction of the overall touch-down force. In addition, the data rate needs to be sufficiently high to support at-speed testing for state-of-the-art I/O technologies with gigahertz communication [68][72].

Wireless testing has been proposed previously [10][67]. Practical implementations can be found in [12][22][23][30][31][35][55][56][59][69][71][84][85], which analyze and demonstrate the feasibility of wireless IC testing through either

inductive or capacitive coupling. Also, the wireless technology suitable for testing can be to other applications such as chip-to-chip communication [11][14] applied [20][39][50]][70], package-to-board communication [7][24][40][41][42][87], wireless bio-medical implantable devices [3], and body area networks (BANs) [36][48][76][78][89]. These require short-range and low-power wireless communication technology, which is essential to wireless testing. A more detailed review of existing research will be presented in Section 1.3.

Our goal is to design wireless IC testing systems compatible with today's scaling trends. Non-contact probes can mitigate or even get rid of the problems related to physically contacting probe tips. These probes are used in a very short communication range down to tens of micrometer to achieve high efficiency, and their data rates are up to 1 Gbps to provide sufficient bandwidth for at-speed testing [68].

### 1.2 Communication Technologies for Wireless Testing

Three major communication methods are potentially suitable for wireless testing of ICs:

- Radio frequency (RF)

- Near field

- Optical

In this thesis, we use the term "RF communication" for far-field communication, and the term "near-field communication" only when discussing capacitive and inductive coupling by quasi-static electromagnetic field radiation. Optical communication transmits signals and power via light at very high frequencies.

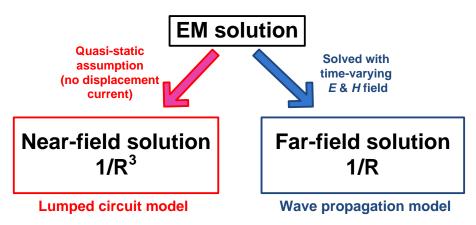

Figure 1.3 Illustration of near-field and far-field solutions.

RF is widely used today in various forms of wireless communication. There has been some research on its use for wireless testing [59]. Since RF requires integrated RF circuits for transmitters and receivers on a DUT, the size of the RF circuits and antennas is of utmost importance. Often modulation is needed to avoid interference from another channel. RF provides long communication range, but its silicon area overhead, including antenna and circuits, is considerable [16][38][59].

In contrast to RF, near-field communication does not use wave propagation. Instead, it transfers energy through a quasi-static electromagnetic field. This enables the communicating circuits to consume relatively low power, and eliminates wave propagation effects like fading, reflection and phase shifting. If the distance between the transceivers is very small, near-field communication may be more efficient than RF communication due to its weak inter-channel interference [43][45].

Optical signals, which consist of high-frequency electromagnetic fields, are relatively immune to noise and interference, so one can detect optical signals without complex modulation and amplifier circuits. However, owing to the difficulty of

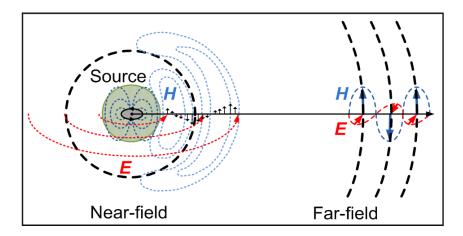

Figure 1.4 Near-field and far-field boundary based on [26].

integrating optics with conventional CMOS processes and the high cost for its fabrication, optical communication seems unsuitable for wireless testing [43][49].

Taking into account circuit size, including on-chip antennas, power consumption, compatibility with conventional CMOS process technology and the distance between transceivers, RF communication and near-field communication are the most appropriate candidates for the wireless testing application. Both can be easily fabricated with conventional CMOS technology and provide reasonable communication range for testing purposes.

#### 1.2.1 Near-Field vs. RF Communication

RF and near-field communication seem like distinct technologies, but both stem from the same fundamental electromagnetic effects, as shown in Figure 1.4. Whether to use near-field modeling or not is decided by the distance from the radiation source, and the frequency used. At a fixed frequency, most of the energy radiates through a quasi-static field near the source, but electromagnetic wave propagation is the major means of

**Figure 1.5** Simulated magnetic field magnitude *H* as a function of distance *R* from the source.

energy transfer in the far-field zone as depicted in Figure 1.4. In this section, we present the results of simulation experiments, which indicate that both near-field and RF communication co-exist by showing a gradual transition between the near field and far field. For details on near-field theory, see the Appendix A.

Figure 1.5 shows the simulated magnitude of the magnetic field H with increasing distance R from a 3D inductor used in a chip-to-chip communication transceiver circuit that we designed with IBM 0.13  $\mu$ m technology. Ansoft's HFSS v10 is used for the H field simulation. At a certain point, we observe that the slope of attenuation changes from -2.77 to -1.2, which represents approximately  $1/R^3$  attenuation in the near field and 1/R in the far field. This plot shows that even the inductor, which is used for near-field coupling in general, can generate a far-field electromagnetic wave. There are little errors due to the idealized assumption that the dimension of an inductor is infinitesimal. On the far-field side, we can see gradual changes in the slope of the H field since the expression for magnetic intensity contains all lower or higher order terms, not only  $1/R^3$  or 1/R.

The various existing wireless communication technologies require quite different antenna designs. Generally, RF antennas have a linear shape of size proportional to the wavelength of an RF carrier, which should have good directivity [8]. Capacitors and inductors used as near-field antennas are sometimes called transducers or electrodes. Since both near-field and RF communication experience a rapid drop in power with increasing distance, the communication distance plays a critical role in deciding signal strength in wireless testing. Fortunately, conventional ATE performs touch-downs on the target wafer with an accuracy measured in micrometers [44], and thus we can use very short communication distance to maximize efficiency. Because electromagnetic energy is mostly delivered by quasi-static radiation over such a short distance, the antenna should be a kind of inductor or capacitor rather than a conventional RF antenna.

For efficient RF communication, even a carrier frequency up to tens of gigahertz necessitates millimeter-sized antennas which are too large to be implemented on a chip. Moreover, due to the propagating wave characteristics of electromagnetic field such as fading, reflection and multipath degradation, the required circuit size and complexity for RF communication must be substantial [16][38][59].

### 1.2.2 Inductive and Capacitive Coupling

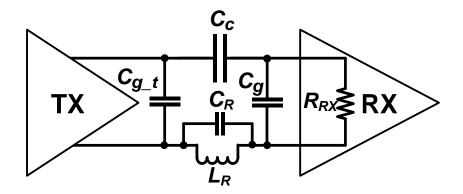

There are two main kinds of near-field phenomena: inductive coupling and capacitive coupling. Each coupling method can be seen as the dual of the other. Equivalent circuit models for an on-chip inductor [50] and a capacitor are shown in Figure 1.6.

Figure 1.6 Equivalent circuit models for (a) coupled inductors [50], and (b) coupled capacitors.

We can derive the gain of each coupled channel as follows.  $C_g$  represents the capacitance between metal and substrate. For inductive coupling, the capacitances  $C_{12}$  and  $C_{21}$  between the two inductors can be ignored because they are relatively small. Substrate resistance  $R_{sub1}$  and  $R_{sub2}$  are ignored in both cases as well. If the load impedance  $R_L$  is on the receiver node, the gain of the inductively coupled channel is as follows [50].

$$\frac{V_{Rx}}{V_{Tx}} = \frac{j\omega k \sqrt{L_1 L_2}}{1 + j\omega C_{g2} R_2} \cdot \frac{1}{R_L (1 - \omega^2 L_1 C_1) + R_1 + j\omega (C_1 R_1 R_L + L_1)}$$

(1.1)

For capacitive coupling, the corresponding equation is

$$\frac{V_{Rx}}{V_{Tx}} = \frac{j\omega R_L C_C}{1 + j\omega R_L (C_{g2} + C_C) + (R_1 + R_2) C_C (j\omega - \omega^2 R_L C_{g2})}$$

(1.2)

These analytical models give us some useful insight into the design of on-chip coupled inductors and capacitors. High gain can be achieved by a large coupling coefficient k for coupled inductors, which highly depends on the number of turns, the area of the coils, and the distance between the two inductors. For capacitive coupling, a large coupling capacitance  $C_c$  leads to high gain. Permittivity, capacitor area, and plate

Figure 1.7 3D models of (a) on-chip inductor, and (b) on-chip capacitor.

separation are factors that decide coupling capacitance. Because high-permittivity materials entail additional cost, from a design point of view inductively coupled communication provides more options to increase gain. For example, increasing the number of turns is an efficient means to get a stronger signal.

Based on the foregoing model, the coupling capacitance can be maximized by using large metal plates with small separation. The inductive coupling coefficient can be increased when larger coils with more turns and shorter separation distance are used. The coupled inductors and capacitors in Figure 1.7 are both of size 30 µm × 30 µm with 20 µm spacing, and were simulated with Ansoft's HFSS v11. For each case, the voltage gain was measured, which is the output voltage divided by the input voltage. The results of a frequency response simulation employing simple 3D on-chip models are given in Figure 1.8. As expected, inductive coupling shows a resonant peak in voltage gain, but the gain for capacitive coupling monotonically increases and has a resonant peak at a very high off-scale frequency. To maximize efficiency, it is desirable to use the resonant frequency

**Figure 1.8** Simulated frequency response with 20 μm communication distance for (a) coupled inductors, and (b) coupled capacitors.

in inductive coupling. For capacitive coupling, using a higher frequency is better in most cases.

Inductive coupling appears to have several advantages, even though the design and characterization of on-chip inductors are complicated, First, it is driven by current change, which is not limited by supply voltage and is easily provided by current-generating circuits. Therefore, the scaling down of supply voltage and physical size of devices do not diminish signal strength. Second, almost no high permeability material is used in conventional CMOS processes; only eddy currents generated by high conductivity material affect the magnetic field, and are not significant. Metal wires in a conventional CMOS process do not contribute to eddy currents, in general, due to their narrow shapes. In addition, the coupling coefficient of inductive coupling can be increased by using higher number of turns. The increased driving strength is beneficial especially for 3D IC testing since it can transmit data through the substrate with sufficient coupling coefficient.

Capacitive coupling is another option for wireless testing owing to the easy implementation of capacitors: small pieces of top-layer metal can form capacitors between a wireless probe and a device on a wafer [10][34][69]. In addition, since a capacitor performs like a short circuit at high frequency, capacitive coupling is good for applications that need a high data rate. As shown in Figure 1.8, a capacitively-coupled channel does not have a resonant peak in the frequency range below 10 GHz. A key advantage of capacitive coupling is that it enables the reuse of bond pads as antennas. This greatly relaxes area constraint of added wireless circuits.

Because of the longer communication distance of inductive coupling, it is attractive for SIP and MCM testing; it provides significantly longer communication range than capacitive coupling. For the same reason, those testing nodes can be used for on-line monitoring after production. For example, built-in-self-test (BIST) circuits and on-chip characterization circuits, which usually have poor accessibility from outside a die or package, can be accessed with inductively-coupled wireless testing nodes. For conventional wafer-level testing, capacitive coupling can be used as well, since there is no interfering material, and the communication distance can be kept as short as the passivation thickness (less than tens of micrometers). These factors relax the main drawbacks of capacitive coupling significantly in terms of signal strength. The gain of capacitive coupling is sufficiently high for such a short distance. Therefore, capacitive coupling is also attractive for wireless testing of non-stacked chips. We conclude that near-field communication via both inductive coupling and capacitive coupling is the most promising technology for wireless testing, primarily due to its small circuit area and low power consumption.

#### 1.3 Related Work

This section summarizes related research on wireless testing. Wireless functionality testing for digital and analog ICs and wireless characterization circuits is covered. Chip-to-chip communication work is also discussed, where the goal is to check the feasibility of short-range and low-power wireless communication rather than testing.

#### **1.3.1** Wireless Testing of Digital ICs

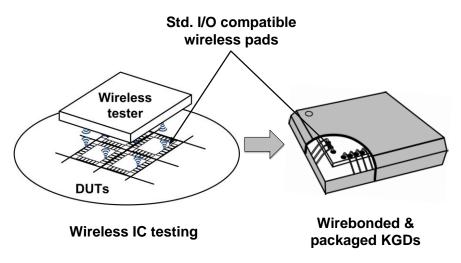

The concept of wireless testing through near-field communication was proposed in [10][67]. Salzman and Knight studied capacitive coupling as a communication channel to address the problems of testing a multi-chip package (MCP). Known good dies (KGDs) should be selected before assembly to reduce manufacturing cost. However, conventional testing methods using probe tips are not effective for MCP testing because they do not support flexible contact point location. Through capacitive coupling, MCPs can be tested before assembly without wired connections. In addition, chip-to-chip communication and wireless power transfer through capacitive coupling are proposed in [11].

Wireless wafer probing of ICs is also discussed in [10]. That work utilizes capacitive coupling as a communication channel, which leads to simpler designs in terms of the antenna structure. Since a capacitively-coupled channel can be formed with two top metal plates, it relaxes the design constraints more than inductive coupling approaches. However, follow-up research for wireless testing has not been reported and no implementation of the work is given in [10].

The more practical circuit design and implementation aspects of wireless wafer-level testing via capacitive coupling are demonstrated in [12][30][31][71]. Photographs

**Figure 1.9** Prototypes of wireless testing: (a) capacitive wafer-level probing [12], and (b) inductively-coupled non-contact probecard [71].

of two prototypes from [12] and [71] are shown in Figure 1.9. Wireless test probes were implemented on a membrane flexible circuit board (FCB) [12] and printed circuit board (PCB) [30][31]. Both show that capacitive coupling can achieve reliable gigahertz communication over a short communication range. In [69], capacitive coupling is formed between slightly shorter probe needles and standard I/O compatible on-chip pads to transmit data. Feasibility with cross-talk effects is discussed, but no bit-error rate performance is reported, and the achieved data rate is very low compared to other near-field communication work.

Sellathamby et al. proposed a method of wireless testing and presented some experimental results in [71]. They give a detailed discussion of implementing wireless wafer-level testing. Near-field communication through two coupled inductors is proposed with simulation and measurement results. Their paper [71] also contains analysis of crosstalk from adjacent channels, and channel characterization results with antenna misalignments and varying communication distance.

Moore et al. present JTAG-compatible wireless testing circuits for SIP testing in [56]. Compared to wafer-level testing, their implementation contains an extra wireless communication module for signaling between a DUT and the ATE. This wireless module collects signals from multiple dies in a SIP and serializes them for transmission to the ATE. The authors propose wireless SIP testing and present measurement results from implemented designs, but the information given about the implemented circuits is limited.

A more detailed analytical approach to channel modeling and the specification of a receiver can be found in [84]. This paper describes an ultra-wide band (UWB) transmitter and receiver using inductive coupling for wireless wafer-level testing. A transformer circuit model for an inductively-coupled channel with various design parameters such as communication range and misalignment is proposed. The circuit design includes a UWB transmitter and a low-noise amplifier (LNA) for the receiver.

In contrast to prior research, wireless testing with RF communication is studied in [22][59]. In [59], two transmitter/receiver architectures are presented: on-off keying with frequency modulation and an image rejection architecture. The communication range is much longer than others with near-field communication, but the size of the RF antenna is substantial. Also, the design requires a special IC process (InGaP/GaAs).

### 1.3.2 Wireless Testing of Analog ICs

Analog testing using wireless communication also has been proposed by several groups. Yoshida et al. describe a wireless voltage regulator using inductive coupling [85]. Although it is not yet fully developed into a complete testing system and it requires an

accurate on-chip reference voltage for each DUT, it shows the feasibility of wireless testing of analog ICs.

In [55][79], the feasibility of wireless on-chip characterization is also discussed. The simulated ring oscillator circuits generate RF signals which vary with the capacitance and resistance at the output node. By measuring the frequency of these RF signals, capacitance and resistance on the DUT can be determined. The proposed on-chip wireless characterization circuits can be purely contactless thanks to RF power transfer with a rectifier and voltage doubling circuits.

Measuring the matching of physical devices with RF signals has also been proposed [59]. Since the receiver architecture is based on symmetric circuit components, the resulting RF signal can be a good way to measure DUT process variation.

#### 1.3.3 Wireless Interconnect for 3D ICs

An application similar to wireless testing in terms of range, power consumption, and circuit size is on-chip wireless interconnect for 3D ICs. Although it has fundamental differences from wireless testing such as design symmetry between transceivers, it is helpful in understanding wireless communication technologies used in short range data transfer. Its communication range R is confined to tens of micrometers, and it consumes low power and small area. Recent work on chip-to-chip communication reveals that it can achieve data rates up to 10 GHz via near-field methods [14][15][17][20][41][42][50-54][70].

Both inductive and capacitive coupling have been proposed for chip-to-chip communication. In [51], a data transfer rate of 1 Tbps with 1,024 inductively coupled

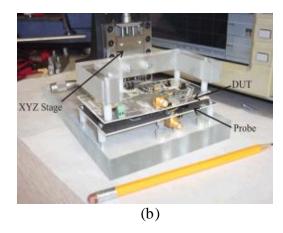

Figure 1.10 (a) Data rates, and (b) communication distance of selected prior 3D on-chip communication links.

channels and 4-phase TDMA is demonstrated. To achieve such a high data rate with very low bit-error rate (BER) less than  $10^{-12}$ , a dynamic comparator is used in the receiver, which has very high gain, but requires precise clock alignment. An extra set of transmitter, receiver, and channel circuits is used for clock transfer. Since accurate clock phase alignment is essential for a dynamic comparator, phase adjustment and clock synchronization are critical design issues with this approach. Utilizing a few large inductors with bit serialization has been proposed in [53] to reduce the area consumption. The receiver is based on an asynchronous comparator, which doesn't require a precisely aligned clock, and a 1:16 bit-serializer is used to achieve 6.4 Gbps burst mode transmission.

Other designs for capacitive coupling can be found in [15][17][20]. In [20], a partitioned mini-pad design is proposed to resolve misalignment issues, and capacitive sensor circuits are employed for misalignment measurement. A dynamic comparator is used for data recovery. More capacitive communication designs can be found in [17]. Two different designs with amplitude modulation and pulse modulation are presented and

compared. The modulated signals are recovered with a non-clocking sense amplifier. Fazzi et al. propose an asynchronous bidirectional transceiver, which achieves the highest data rate at low power consumption [15]. Their most significant performance improvement is mainly due to very close separation between two metal plates and their use of a special process technology.

Figure 1.10 compares several recent chip-to-chip communication designs in terms of data rate and communication distance. It shows that most near-field prototypes can achieve a data rate of up to 10 Gbps with less than 20  $\mu$ m communication distance. Assuming a communication distance of about 10  $\mu$ m, this result validates the conclusion that near-field communication is suitable for gigabit communication for wireless IC testing.

#### 1.4 Thesis Outline

The main contribution of this dissertation research is to demonstrate the feasibility of wireless IC testing via near-field capacitive communication, which mitigates many of the problems associated with conventional probe card based testing. Various wireless testing methods are investigated and evaluated with respect to their practicality. The research then focuses on near-field capacitive communication because of its efficiency over the very short ranges needed during IC manufacture. Several prototype chips were fabricated and tested to validate the proposed wireless methods of testing ICs.

In Chapter 2, we propose a new capacitive coupling model for wireless IC testing. We analyze the advantages and disadvantages of capacitive coupling compared to inductive coupling. Then, the more accurate lumped circuit model of capacitive coupling

is discussed. The conventional channel model of capacitive coupling only employs a capacitive voltage divider, which has high-pass characteristics. The proposed lumped model considers the separate ATE and DUT grounds and gives more accurate frequency response for capacitively-coupled channels. In addition, the effect of misalignment and cross-talk from adjacent channels is analyzed.

Chapter 3 presents a prototype capacitively-coupled communication link for wireless IC testing based on the proposed channel model. It has two unique features: first, it reuses the antenna as a bond pad after testing since the I/O bond pad is suitable for capacitive coupling due to its shape. Second, it delivers both clock and data signals at the same time through a single wireless channel. The interconnection complexity, especially at the ATE side, may cause significant timing uncertainty. The self-clocked pulse-width modulation (PWM) signals in the prototype enable a relatively simple clock and data recovery (CDR) architecture, and there is no need for an additional clock channel for retiming.

In Chapter 4, the second prototype of capacitive links is discussed. It includes the effect of electro-static discharge (ESD) protection circuits on the receiver side, and measurement results from a die-level experiment are presented. The new prototype supports adjustable transmitter power and pulse position modulation (PPM) with return-to-zero (RZ) signaling. The reduced channel gain due to the ESD protection circuits can be compensated by raised transmitter power. PPM RZ signals provide a simple CDR as well, and enable flexible symbol design with a counter-based majority voting demodulator. Electrical alignment measurement circuits are also implemented to assist fine die-level alignment.

In Chapter 5, a prototype design of analog voltage measurement circuits that use capacitive coupling is discussed. The prototype wirelessly delivers voltage measured on-chip to a tester with two UWB pulses. Due to the high accuracy of off-chip timing measuring equipment, the on-chip circuitry can be relatively compact and simple. The impact of the wireless channel on non-linearity and distortion is evaluated and compared to the wired case.

The contributions of this thesis and suggestions for future work are outlined in Chapter 6. The major contributions include a new capacitive channel model accounting for the effects of cross-talk, DC-level fluctuation, and misalignment; a compact CDR architecture for wireless IC testing; two fabricated test chips to validate our models and architecture; and a method of on-chip analog voltage measurement. Wireless power transfer for IC testing, wireless built-in-self-test (BIST) circuits, and automatic control of wireless circuits for testing ICs are suggested as topics for future research.

# **Chapter II**

# **Capacitively-Coupled Channel for Wireless Testing**

In this chapter, wireless testing of integrated circuits (ICs) via capacitive coupling is evaluated by means of several analytical models. As we have seen in the previous chapter, despite the fact that direct-contact probing is the standard testing practice in the IC industry, this approach is likely to become less effective and more costly in the future. We propose wireless testing via capacitive coupling to minimize the additional area for antennas. The material in this chapter appears in [34].

#### 2.1 Introduction

Since probe tips physically touch down on a wafer, they undergo contact point deformation and debris accumulates on the probe tips [44]. Scaling trends also make probe card testing less suitable for future ICs. As devices scale down, the size and pitch of I/O pads gradually shrink as well, requiring very small contact points. Higher I/O signal frequency is also problematic for probe-card testing. To minimize the time spent on the ATE, at-speed testing is desirable. However, scaling trends require very high I/O frequency for at-speed testing [72]. High-frequency probe tips need careful characterization for impedance matching, which is yet another cost-increasing factor.

Wireless wafer-level testing has been proposed as an alternative, where the goal is to replace physical contact points (bond pads) with wireless channels and antennas. Both digital and analog signals can be transmitted through the wireless channels. Power can also be delivered either via wireless communication or wired power lines. By reducing or eliminating physical touch-downs, many of the problems associated with direct-contact probing can be greatly alleviated.

We present several new analytical models for on-chip capacitive coupling. They can be used for channel performance prediction and antenna design. Based on these models, cross-talk and misalignment can be analyzed as well. This chapter is organized as follows. In Section 2.2, capacitive and inductive coupling are compared. Analytical models for capacitive-coupled test channels are presented in Section 2.3. Cross-talk from adjacent channels is discussed in Section 2.4. Misalignment simulation results are given in Section 2.5. Finally, Section 2.6 presents our conclusions on the feasibility of capacitively-coupled wireless testing.

# 2.2 Coupling Techniques for Wireless Testing

Wafer-level testing requires very short communication range, making it well-suited to near-field methods. As noted earlier, a wafer and a tester can be as close as a few micrometers. Near-field antennas are more efficient than the linear-shaped antennas needed for RF communication in the near-field zone. In addition, near-field communication does not suffer from wave propagation effects like reflection and multipath delay, which also require complex and power-consuming circuits.

**Table 2.1** Performance comparison of various prior chip-level wireless communication systems.

|                   | Gu <i>et al.</i> , 2007<br>ISSCC [17] | Daito <i>et al.</i> , 2010<br>ISSCC [12] | Kim <i>et al.</i> , 2010<br>3DIC [31] | Miura <i>et al.</i> , 2011<br>ISSCC [54] |

|-------------------|---------------------------------------|------------------------------------------|---------------------------------------|------------------------------------------|

| Basic technology  | Capacitive                            | Capacitive                               | Capacitive                            | Inductive                                |

| Application       | Chip-to-chip                          | IC Testing                               | IC Testing                            | Chip-to-chip                             |

| Energy/bit        | 0.27pJ/b                              | 2pJ/b                                    | 0.47pJ/b                              | 0.145pJ/b                                |

| Data rate/channel | 10Gbs/ch                              | 1Gbs/ch                                  | 15Gbs/ch                              | 1.1Gbs/ch                                |

| BER               | <10 <sup>-12</sup>                    | <10 <sup>-12</sup>                       | <10 <sup>-12</sup>                    | <10 <sup>-12</sup>                       |

| Process           | 0.18µm CMOS                           | 90nm CMOS                                | 65nm CMOS                             | 65nm CMOS                                |

| Range R           | 3µm                                   | 4µm                                      | 4µm                                   | 20µm                                     |

| Size of channel   | 2x48x18 μm²                           | 80x80 μm²                                | 80x80 μm²                             | 2x110x110 µm <sup>2</sup>                |

We decided to focus on capacitive coupling for our wireless wafer-level testing study. The antennas for capacitive communication can be formed with a simple planar shape in the top metal layer, which reduces the design complexity significantly. Also, we already have shown in Chapter 1 that the capacitive coupling provides sufficient gain with a very short communication distance. A comparison of relevant previously published work is presented in Table 2.1. Capacitive coupling can achieve very high data rate with face-to-face chip stacking because the communication distance can be shorter than 5 µm. Also, capacitive antennas can be reused for wirebonding after testing so that area consumption is minimized. Inductive coupling, on the other hand, can achieve a longer communication range, but consumes more area for coils [54]. All capacitive techniques can achieve data rates higher than 1 Gbps with very low BER due to the relatively short communication distance. Together, these examples support the case for capacitive coupling in wireless wafer-level testing.

### 2.3 Circuit Model of Capacitive Coupling

Two capacitively-coupled metal plates can be modeled by the following ideal capacitance model.

$$C = \varepsilon \frac{A}{R} \tag{2.1}$$

where A is the capacitor area, R is the plate separation, and  $\varepsilon$  is the permittivity of medium. This is a simplified model in which fringing effects along the edges of the metal plates are ignored. Thus, it is only valid when the plates are infinitesimally thin, and the separation between them is relatively small. In reality, the metal plates have a non-zero thickness that cannot be ignored in practice. This thickness contributes to fringing capacitance and increases overall capacitance between the two plates. More accurate capacitance models can be found in [47][87]. In [87], Yuan and Trick model metal plates with non-zero thickness as a combination of ideal plates and two cylindrical sidewalls. Therefore their model is only valid for when the thickness is relatively small. A capacitance model of even greater accuracy can be found in [47]. This model widens the valid thickness range by adding E-field effects from the top surface. However, compared to Yuan and Trick's model, it is an experimental model with less analytical justification.

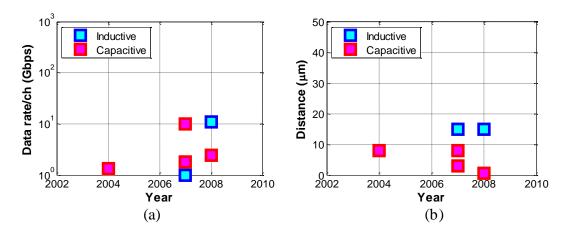

We carried out a number of simulation experiments using Ansoft's HFSS v11, an electromagnetic field solver. With an on-chip 3D model of the coupled plates, the coupling capacitance  $C_c$  was extracted. For the simulations, two on-chip 92  $\mu$ m × 52  $\mu$ m sized metal plates were placed with varying separations. The HFSS-simulated results are compared with various analytical capacitance models in Figure 2.1. All capacitance models match well for separation shorter than 10  $\mu$ m, but they become inaccurate above

Figure 2.1 Simulated coupled capacitor model with fringing capacitance.

10 µm separation. While van der Meijs and Fokkema's model [47] yields the result closest to the extracted capacitance, the ideal plate model is still comparable with a very short separation 1/10 of the size of metal plates. In addition, since the ideal model always underestimates the capacitance, it can be used for a quick estimation of the worst-case.

Another issue for on-chip capacitance modeling is the permittivity  $\varepsilon$  of the medium between the two metal plates. Since there is no blocking material between a DUT on a wafer and the tester, the medium can be modeled as vacuum with  $\varepsilon = \varepsilon_0$ . In practice, the metal plates are usually implemented with the last metal layer of the IC process. There is a passivation layer above the last metal layer, which has permittivity around 3.4. Therefore, for better accuracy, the on-chip capacitive coupling model should include the effect of the passivation layer. As for the ideal capacitance model, the vacuum model can be used as the worst-case assumption for a quick estimation. Then, a more accurate model can be used for more exact analysis.

The voltage transfer function of on-chip capacitive coupling given in (1.2) can be further simplified. If the series resistance of the metal plates is ignored, the transfer function reduces to that of a voltage divider.

$$\frac{V_{Rx}}{V_{Tx}} = \frac{C_c}{C_c + C_g} \tag{2.2}$$

Here,  $C_c$  is the coupling capacitance between the metal plates, and  $C_g$  is the capacitance to ground. As discussed, higher  $C_c$  is desirable to achieve higher voltage gain, and can be modeled with the ideal capacitance model.

The use of separate grounds for the DUT and tester are also critical in modeling. An ideal common ground is assumed for the on-chip voltage transfer function in both (1.2) and (2.2). However, in reality both chips have different grounds, and these different grounds may affect channel gain significantly. For example, if there is no closed current return path, a very large current loop will cause substantial parasitic inductance, which lowers the resonant frequency, and may render of the entire system unstable. To avoid this, AC grounds should be placed on-chip to provide current return paths for high frequency signals.

A more accurate voltage transfer function including current return paths and AC grounds can be written as follows.

$$\frac{V_{Rx}}{V_{Tx}} = \frac{s^2 L_R C_c \left(C_R + C_g\right) + C_c}{s^2 L_R \left\{C_R \left(C_c + C_g\right) + C_c C_g\right\} + C_c + C_g}$$

(2.3)

Figure 2.2 More accurate on-chip capacitor model with current return paths.

Figure 2.3 On-chip 3D model of capacitive coupling.

$L_R$  and  $C_R$  are added parasitic inductance and capacitance from the return paths and grounds.  $L_R$  is mainly determined by wirebonding inductance and off-chip signal traces.  $C_R$  can be minimized when larger AC-ground pad and shorter separation are used. The lumped circuit model is depicted in Figure 2.2. Based on this new model, we can conclude that parasitic inductance from the current return paths should be kept as small as possible, and the capacitive coupling of the AC ground should be large enough to support good current returns. Since the combination of these parasitics can cause resonance, their poles and zeros should be shifted to very high frequencies in order not to affect the

Figure 2.4 Gain vs. plate separation for capacitive coupling.

system stability. When this condition is met, the more accurate model can be approximated by the simpler voltage divider model in (2.2).

A 3D model of an on-chip capacitor with 95  $\mu$ m  $\times$  52  $\mu$ m metal plates shown in Figure 2.3 was simulated using HFSS v11. As Figure 2.4 shows, the HFSS-extracted gain matches well with the hand-calculated gain from an ideal plate model for small separation distances. For wider separation (over 15  $\mu$ m), the difference gets larger since the ideal plate model underestimates fringing effects.

#### 2.4 Cross-Talk Analysis

Although near-field radiation is only strong enough at very short range, cross-talk from adjacent channels is still a critical source of interference. The worst-case scenario of adjacent channel interference is depicted in Figure 2.5.

When a transmitter TX drives a target receiver RX, there are two possible interference sources from adjacent channels: one on the same chip and one on the other chip. Since a channel is configured for unidirectional communication, only one case is

**Figure 2.5** Cross-talk model for on-chip capacitive coupling.

possible at any time. Between the two cases, the aggressors from the same chip degrade channel gain more than those from the other chip due to large metal plate separation and small overlapping area. Most fringing capacitance is screened by the metal plates, and the distance to aggressors on the same chip is always shorter. Thus, the cross-talk capacitance  $C_{cr2}$  and  $C_{cr4}$  should be added to the voltage transfer function to estimate the effect of cross-talk.

If we assume the worst case, the cross-talk capacitance needs to be doubled due to the Miller effect. If the two coupled nodes switch in opposite directions at the same time, the effective coupling capacitance also is doubled. The voltage transfer function with cross-talk is then as follows.

$$\frac{V_{Rx}}{V_{Tx}} = \frac{s^2 L_R C_c (C_R + C_p) + C_c}{s^2 L_R \{C_R (C_c + C_p) + C_c C_p\} + C_c + C_p}$$

(2.4)

where  $C_p = C_g + 2 \cdot (C_{cr2} + C_{cr4})$  The effect of cross-talk contributes to the overall capacitance to ground, and results in reduced voltage gain.

Fortunately, the sidewalls of the metal plates used for capacitive coupling are quite small. Fringing effects from the top and bottom sides are blocked by other metal plates if other channels are relatively close. Therefore, the cross-talk capacitance from

**Table 2.2** Extracted passive element values from EM simulation with 10 μm separation.

| $C_{c}$            | 5.43 fF  |

|--------------------|----------|

| $C_{ m g}$         | 26.73 fF |

| $C_{cr2}, C_{cr4}$ | 0.35 fF  |

| $C_{\mathbf{R}}$   | 20.7 fF* |

| $L_R$              | 1 nH *   |

<sup>\*</sup> The AC-ground pad is assumed 4× larger than a coupling pad.

<sup>\*</sup> Parasitic inductance is assumed for 1-mm wire-bonding.

Figure 2.6 Simulated capacitance vs. plate separation.

an adjacent channel is expected to be relatively small compared to the coupling capacitance  $C_c$  and the parasitic capacitance to ground  $C_g$ . Extracted passive element values are shown in Table 2.2.

HFSS simulations were conducted for the same metal plates (95  $\mu$ m × 52  $\mu$ m) shown in Figure 2.3 with lateral spacing of 17  $\mu$ m, which is the minimum spacing from the design rules for I/O pads. The overall capacitance from cross-talk, 2 × ( $C_{cr2}$  +  $C_{cr4}$ ) was found to be less than 1 fF. As shown in Figure 2.6, the simulated  $C_c$  and  $C_g$  were 8 fF and 25.6 fF, respectively, at a separation of 5  $\mu$ m. As expected,  $C_g$  and  $C_{cr2}$  +  $C_{cr4}$  remain almost the same at wider separation. Both capacitance types increase with increasing separation due to less screening effect from metal plates on the other chip.

Figure 2.7 Gain comparison with cross-talk effects.

$C_c$  continuously decreases with increasing separation.

From the simulation results in Figure 2.7, we can conclude that the effect of cross-talk is not substantial in capacitive coupling. However, since the cross-talk highly depends on metal plate size and spacing, careful analysis must be done for correct channel characterization.

# 2.5 Misalignment Tolerance

Since a conventional probe card tester can touch down on a wafer with micrometer precision, misalignment of the channel plates in a capacitively-coupled tester may not be a serious problem. Nevertheless, an analysis of plate alignment is still worth doing to determine the minimum lateral spacing of different channels and reduce the potential cost of high-precision alignment. Like cross-talk, misalignment manifests itself as a change in capacitance. In most cases, misalignment greatly affects coupling capacitance, and so results in gain degradation. In contrast, the parasitic capacitance to ground remains essentially unchanged.

Figure 2.8 Coupling capacitance vs. misalignment.

Figure 2.9 Gain vs. misalignment.

The same 3D capacitor model with 5 µm separation has been used for a HFSS simulation of misalignment. The *y*-location of the top metal plate was changed from 0 µm to 50 µm. Since the width of the metal plate is assumed to be 52 µm, a *y*-direction sweep covers most cases of misalignment. Figure 2.8 shows the simulated results. As misalignment increases, the coupling capacitance becomes smaller. However, even for 50 µm misalignment, the capacitance does not decrease significantly with no overlapping of the metal plates.

Figure 2.10 Proposed wireless tester.

Compared to the results of cross-talk simulation with similarly located plates, the coupling capacitance is quite substantial. This is believed to be because of fringing effects. There is no material which screens fringing capacitance between diagonally placed plates. Thus, the top and bottom surface of the metal plates can exhibit capacitive coupling in spite of almost no overlapping area.

The effect of misalignment on channel gain is shown in Figure 2.9. Even with the maximum misalignment, the gain decreases by only 2 dB. We can therefore conclude that a capacitively-coupled channel shows good misalignment tolerance up to the size of the metal plates.

### 2.6 Summary

Wireless testing is an alternative to direct-contact testing of ICs that greatly reduces the costs associated with probe employment and wear. Due to the very short communication range required, capacitive coupling seems the most feasible wireless communication technology for this application. We have presented analytical models and simulation results that support the validity of this approach. They demonstrate that the gain of a capacitively-coupled channel can be easily predicted. Moreover, our cross-talk

and misalignment results indicate that capacitive coupling experiences relatively low adjacent channel interference, and has good misalignment tolerance. In summary, capacitively-coupled wireless testing of the kind depicted in Figure 2.10 offers an attractive alternative to conventional wafer probing.

Of course, there are other issues that need to be addressed to make wireless testing at the wafer level practical. These include tester reconfiguration, wireless power transfer, and low-power test circuits. These issues can be mitigated by various circuit techniques. For example, tester reconfiguration may be implemented using a shared channel with various multiple-access schemes such as time division multiple access (TDMA) or code division multiple access (CDMA). Wireless power transfer through capacitively-coupled channels has been proposed in [11], but the deliverable power is still very limited. Therefore, we propose a hybrid approach. The data links are based on wireless communication, but the wired power connections are assumed. Although power connections usually remain wired, it is still very beneficial to reduce the number of I/O signals requiring probe touch-down [69].

# Chapter III

# Single-Channel Capacitive Link for Wireless Testing

This chapter presents a single-channel I/O link intended for wireless integrated circuit testing via capacitive coupling. A wireless testing system with a simple CDR architecture based on the proposed capacitive channel model is presented. DC-level fluctuation from PWM is estimated from an analytical model. The measurement data from a fabricated prototype chip validate the model and its predicted performance. The material in this chapter appears in [35].

#### 3.1 Introduction

Wireless testing requires extra circuits and antennas on the die, which should not consume too much chip area. Additionally, the functionality of the original device should not be affected by the components added for testing. Electrical power also needs to be delivered wirelessly to completely remove wired lines during testing. However, as long as the number of signal pads is a significant fraction of the total number of I/O pads, wireless testing only of signal pads with wired power can still be beneficial due to the significant reduction of the touch-down force [69]. In addition, the data rate needs to be

**Figure 3.1** Proposed capacitively-coupled wireless IC testing with bond pads compatible with standard I/O cells.