# Low-Power RF Integrated Circuits for Wireless Sensor Network Synchronization and Communication

by

Jonathan Kirk Brown

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in the University of Michigan 2012

#### **Doctoral Committee:**

Assistant Professor David D. Wentzloff, Chair Professor Dennis M. Sylvester Associate Professor Michael P. Flynn Associate Professor Vineet R. Kamat

To everyone who encouraged me through the years

## Table of Contents

| Dedication                             |              | ii  |

|----------------------------------------|--------------|-----|

| List of Figures                        |              | vi  |

| List of Tables                         |              | . X |

| Chapter 1 Introduction                 |              | . 1 |

| 1.1. The Future of Computing           |              | . 1 |

| 1.1.1. Computing Trends                |              | . 1 |

| 1.1.2. Wireless Sensor Networks        |              | . 2 |

| 1.2. Wireless Sensor Nodes             |              | . 5 |

| 1.2.1. Anatomy of Conventional S       | ensor Nodes  | . 5 |

| 1.2.2. Component Trends & Chall        | enges        | . 6 |

| 1.2.3. Anatomy of Future Sensor N      | Nodes        | 15  |

| 1.3. Synchronization for Wireless Co   | mmunication  | 17  |

| 1.3.1. Sleep-Mode Power Consum         | ption        | 18  |

| 1.3.2. Timer                           |              | 18  |

| 1.3.3. Wake-Up Receiver                |              | 20  |

| 1.3.4. Clock-Harvesting Receiver.      |              | 21  |

| 1.4. Contributions of this Work        |              | 22  |

| Chapter 2 Potential Sources for a Harv | ested Clock  | 25  |

| 2.1. Attributes of an Ideal Harvested  | Clock Source | 25  |

|                                        |              |     |

| 2.2.1. NIST WWVB                       |              | 26  |

| 2.2.2. NIST WWV and WWVH               |              | 29  |

| 2.2.3. Global Time Codes               |              | 31  |

| 2.3. GSM Standard                      |              | 32  |

| 2.3.1. Broadcast Channel               |              | 33  |

| 2.3.2. Guard Period                    |              | 34  |

| 2.4. CDMA Standard                     |              | 35  |

| 2.5. Bluetooth Standard                |              | 36  |

| 2.6. ZigBee (IEEE 802.15.4) Standar    | d            | 38  |

| 2.7. Summary                           |              | 39  |

| Chapter 3 GSM-Based Clock-Harvesti     | ng Receiver  | 41  |

|                                        |              |     |

| 3.2. System Overview                   |              | 43  |

| 3.2.1. GSM-Based Synchronizatio        | n            | 43  |

| 3.2.2.           | System Operation                                           | 44 |

|------------------|------------------------------------------------------------|----|

| 3.2.3.           | System Architecture                                        | 44 |

| 3.2.4.           | Intermediate Frequency Selection                           | 45 |

| 3.3. Bai         | ndpass Filter Model                                        |    |

|                  | cuit Design                                                |    |

| 3.4.1.           |                                                            |    |

| 3.4.2.           |                                                            |    |

| 3.4.3.           | <u> </u>                                                   |    |

| 3.4.4.           | Sleep-Power Minimization                                   |    |

|                  | asurement Results                                          |    |

| Chapter 4        | CDMA-Based Clock-Harvesting Receiver                       | 63 |

| 4.1. Inti        | roduction                                                  |    |

| 4.2. Sys         | stem Overview                                              | 65 |

| 4.2.1.           | System Operation                                           | 65 |

| 4.2.2.           | System Architecture                                        |    |

| 4.2.3.           | · ·                                                        |    |

| 4.3. Cir         | cuit Design                                                |    |

| 4.3.1.           | <u> </u>                                                   |    |

| 4.3.2.           | Down-Conversion.                                           |    |

| 4.3.3.           |                                                            |    |

| 4.3.4.           |                                                            |    |

|                  | asurement Results                                          |    |

| Chapter 5        | Communication Protocol and for an Energy-Constrained Radio | 75 |

|                  | sign Constraints                                           |    |

| 5.1.1.           | Total Node Volume                                          | 75 |

| 5.1.2.           | Battery Current Draw.                                      | 77 |

| 5.1.3.           | Battery Supply Voltage                                     |    |

| 5.1.4.           | Local Oscillator.                                          |    |

| 5.1.5.           | Baseband Clock                                             |    |

| 5.1.6.           | Center Frequency                                           |    |

| 5.1.7.           | Process Technology                                         |    |

| 5.1.8.           | Sleep Timer                                                |    |

|                  | tial Design Analysis                                       |    |

|                  | oulse Radio UWB                                            |    |

|                  | mmunication Protocol.                                      |    |

| 5.4.1.           | Peak Currents                                              |    |

| 5.4.2.           | Pulse Tracking                                             |    |

| 5.4.3.           | Baseband Architecture                                      |    |

| 5.4.4.           | Modulation Schemes                                         |    |

| 5.4.4.<br>5.4.5. | Synchronization Header & Training Sequence                 |    |

| 5.4.5.<br>5.4.6. | Payload                                                    |    |

| 5.4.0.<br>5.4.7. | Start-of-Payload Identifier                                |    |

| 5.4.7.<br>5.4.8. | Data Rate                                                  |    |

| 5.4.8.<br>5.4.9. | Summary                                                    |    |

| J. <b>H.</b> J.  | Guiiiiiai y                                                | ブト |

| Chapter 6  | 10GHz Energy-Detection-Based IR-UWB Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 93  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.1. In    | troduction & Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93  |

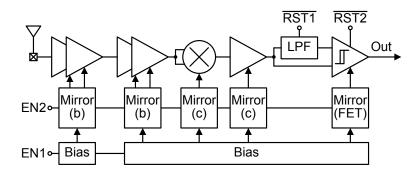

| 6.2. Sy    | ystem Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 95  |

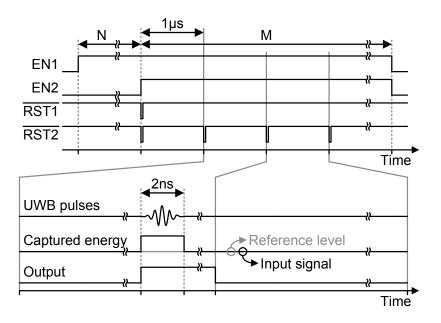

|            | ystem Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

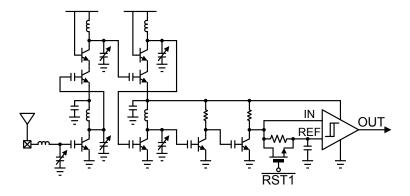

| -          | ircuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| 6.4.1.     | the state of the s |     |

| 6.4.2.     | Pulse Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98  |

| 6.4.3.     | Current Reuse & Biasing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 98  |

| 6.4.4.     | Digital Logic & Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 99  |

| 6.4.5.     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| 6.5. Si    | mulation Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| 6.6. M     | leasurement Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 103 |

| Chapter 7  | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 108 |

| References |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 111 |

# List of Figures

| Fig. 1.1. The long-term trend in computer scaling over the years [1]                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.2. Conceptual block diagram of a wireless sensor network with temperature sensing                                                                                    |

| Fig. 1.3. Examples of recent wireless sensor nodes (a) Mica Mote and (b) Fleck 3 [7] 5                                                                                      |

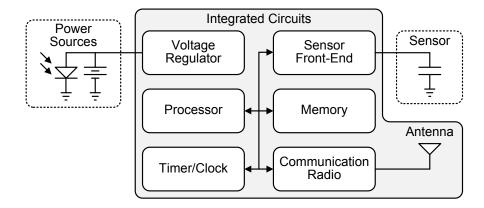

| Fig. 1.4. System block diagram of a recent wireless sensor node                                                                                                             |

| Fig. 1.5. Custom 1μAh Cymbet micro-battery setup for testing                                                                                                                |

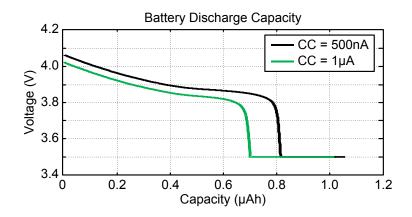

| Fig. 1.6. Measured discharge curve of the 1μAh Cymbet micro-battery                                                                                                         |

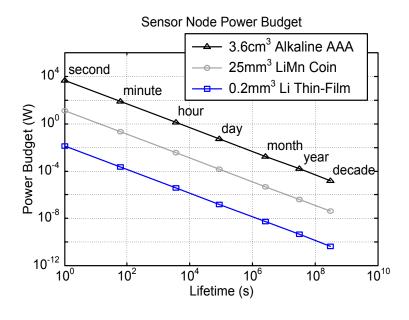

| Fig. 1.7. Power budget available vs. desired lifetime for different battery cells [30] 12                                                                                   |

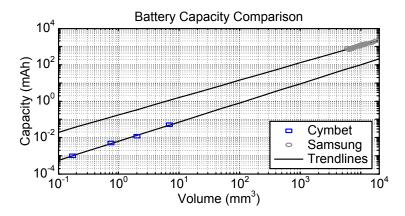

| Fig. 1.8. Li-ion capacity comparison of Cymbet micro-batteries vs. commercial prismatic batteries.                                                                          |

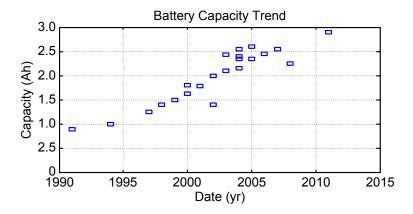

| Fig. 1.9. Long-term growth in capacity of cylindrical Li-ion batteries since the first commercial Li-ion                                                                    |

| Fig. 1.10. System block diagram of a future wireless sensor node                                                                                                            |

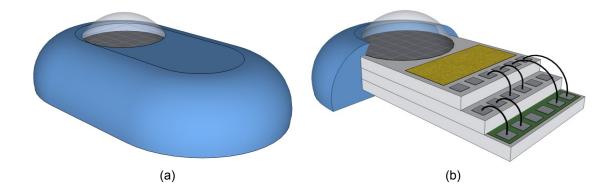

| Fig. 1.11. Conceptual system diagram of a cubic-mm sensing platform (a) encapsulated and (b) with the encapsulation cut-away.                                               |

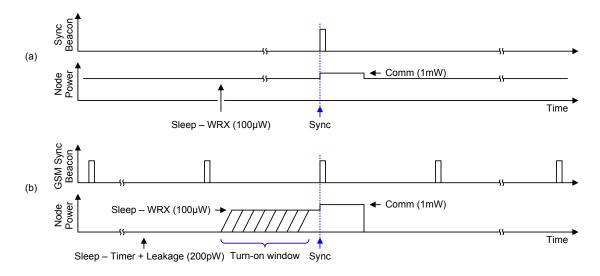

| Fig. 1.12. WSN synchronization (a) with an always-on wake-up receiver and (b) with a duty-cycled wake-up receiver.                                                          |

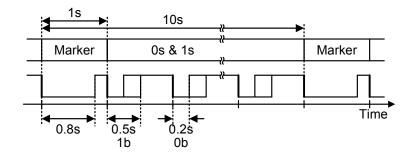

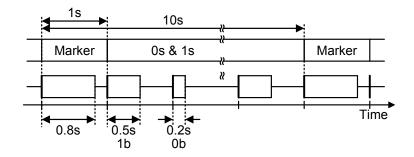

| Fig. 2.1. The pulse-width modulated time code for the WWVB radio station. Marker bits occur once every 10s with zero bits and one bits during the other seconds             |

| Fig. 2.2. The pulse-width modulated time code for the WWV and WWVH radio stations. Marker bits occur once every 10s with zero bits and one bits during the other seconds 30 |

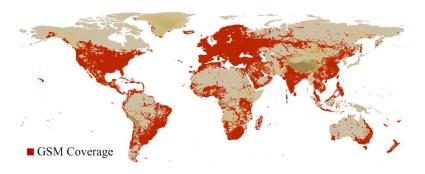

| Fig. 2.3. The 2009 Global System for Mobile Communications (GSM) worldwide coverage map, excluding 3GSM coverage [75]                                                       |

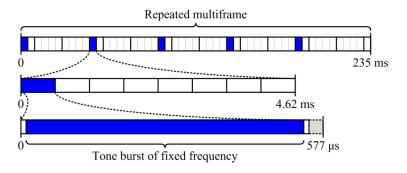

| Fig. 2.4. The organization of the broadcast control channel carrier, which consists or repeated multiframes with a tone burst generated at a fixed frequency during five of the timeslots           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

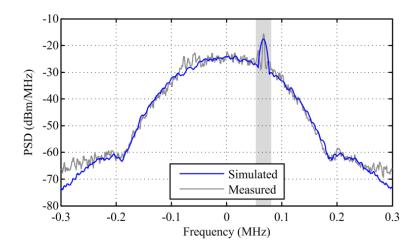

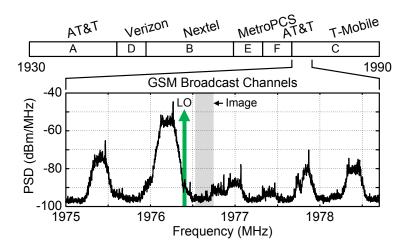

| Fig. 2.5. Power spectral density (PSD) versus frequency for simulated and measure broadcast signals. The tone generated during a frequency correction burst is indicated in the highlighted region. |

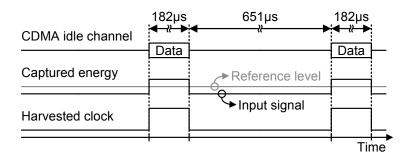

| Fig. 2.6. CDMA signaling and clock extraction vs. time. Data during idle slots in 30 CDMA standard is on-off keyed.                                                                                 |

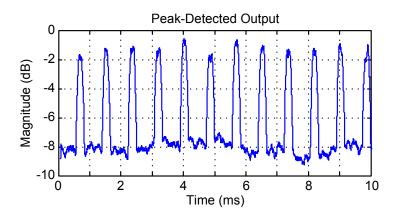

| Fig. 2.7. Measured CDMA channel from Verizon Wireless vs. time using a prototyp receiver with Matlab filtering                                                                                      |

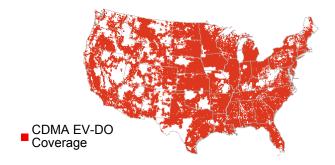

| Fig. 2.8. Verizon Wireless 3G CDMA US coverage map [76]                                                                                                                                             |

| Fig. 3.1. GSM broadcast channels (BCHs) measured in our lab. These BCHs sit in the 1900-MHz band operated by T-Mobile, and they are spaced such that they don't interfer with each other            |

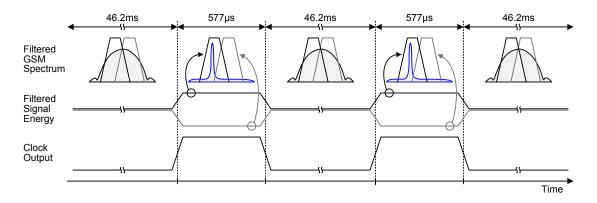

| Fig. 3.2. Operation of a broadcast channel in time                                                                                                                                                  |

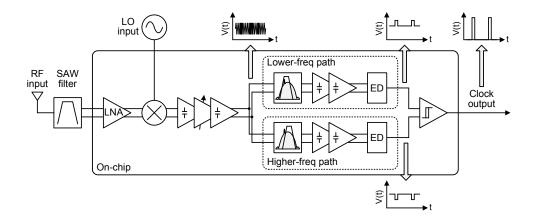

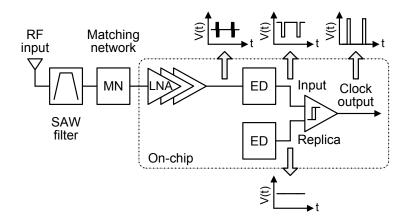

| Fig. 3.3. System block diagram of the clock-harvesting receiver                                                                                                                                     |

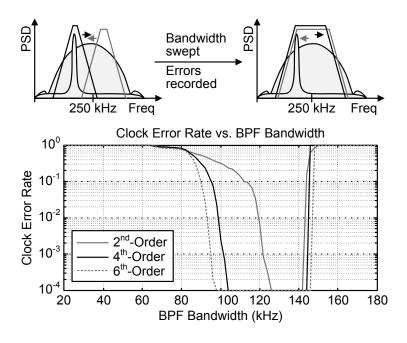

| Fig. 3.4. Simulated clock error rate versus the bandwidth of each bandpass filter 4                                                                                                                 |

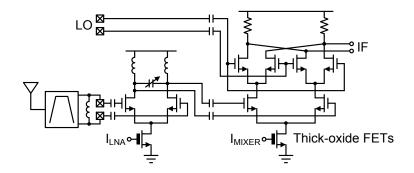

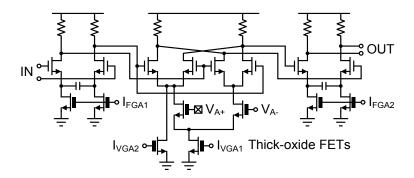

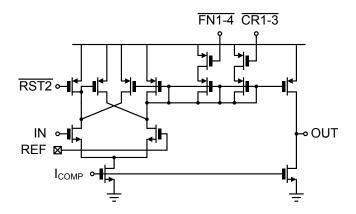

| Fig. 3.5. RF front-end, including SAW filter, LNA, and mixer                                                                                                                                        |

| Fig. 3.6. Baseband amplifiers, including two fixed-gain amplifiers and one VGA 5                                                                                                                    |

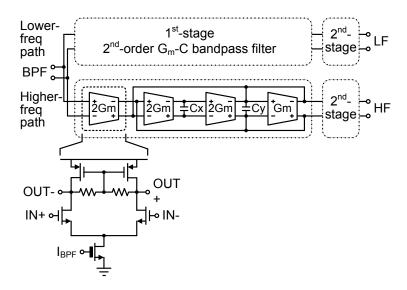

| Fig. 3.7. Two-stage bandpass filters for the lower-frequency and higher-frequency paths                                                                                                             |

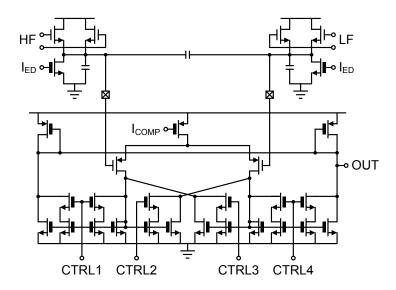

| Fig. 3.8. Envelope detectors and continuous-time comparator                                                                                                                                         |

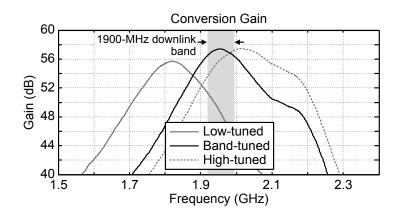

| Fig. 3.9. Conversion gain for different tunings of the varactor                                                                                                                                     |

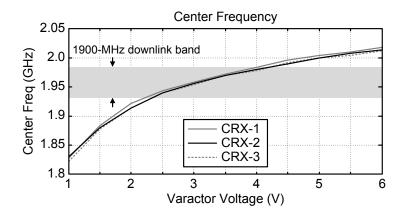

| Fig. 3.10. Center frequency across varactor voltage for multiple die                                                                                                                                |

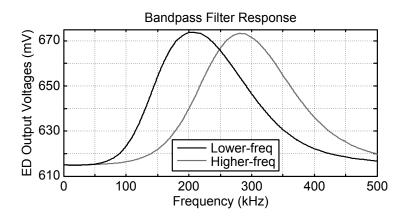

| Fig. 3.11. Magnitude response of the bandpass filters                                                                                                                                               |

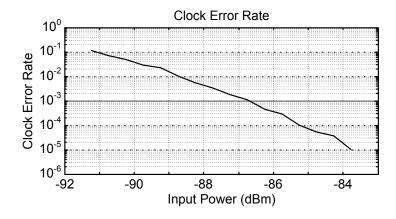

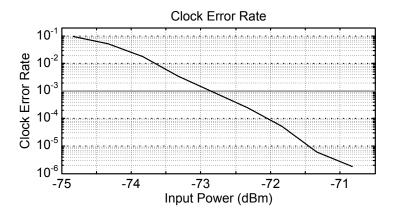

| Fig. 3.12. Clock error rate vs. input power                                                                                                                                                         |

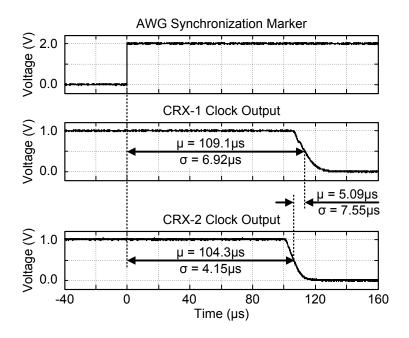

| Fig. 3.13. Delay and jitter measurements of two clock-harvesting receivers                                                                                                                          |

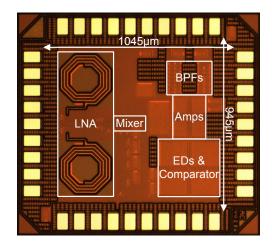

| Fig. 3.14. Die photo.                                                                                                                                                                               |

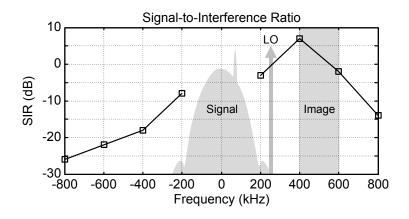

| Fig. 3.15. Signal-to-interference ratio for neighboring broadcast channels.                                                                                                                         |

| Fig. 3.16. Simultaneously harvested-clocks of two CRXs from a local GSM broadcast channel                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

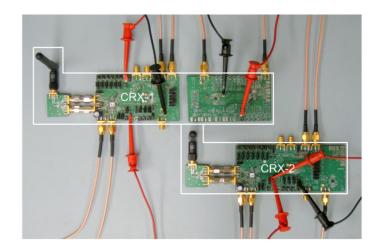

| Fig. 3.17. Setup of two CRX debug boards receiving a real GSM signal in our lab 60                                                                                                                                                                 |

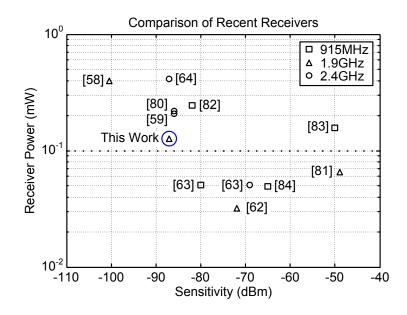

| Fig. 3.18. Comparison of power consumption vs. sensitivity of recent low-power receivers.                                                                                                                                                          |

| Fig. 4.1. Block diagram of the clock-harvesting receiver                                                                                                                                                                                           |

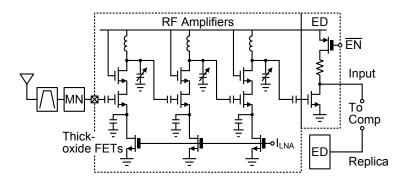

| Fig. 4.2. Schematic of the cascoded RF amplifiers and the envelope detectors. Every current path includes a thick-oxide tail FET for low leakage currents while asleep 67                                                                          |

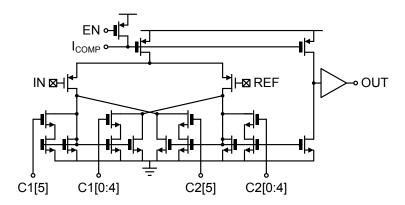

| Fig. 4.3. Schematic of the continuous-time hysteretic comparator                                                                                                                                                                                   |

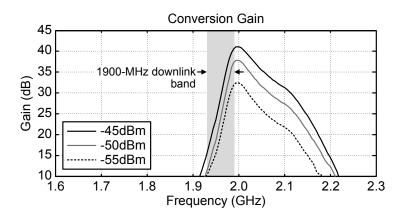

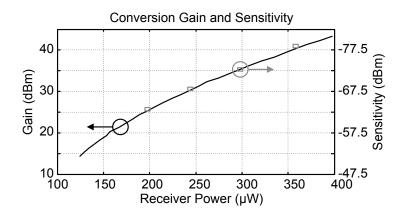

| Fig. 4.4. Conversion gain for different receive powers. 71                                                                                                                                                                                         |

| Fig. 4.5. Clock error rate vs. input power. 71                                                                                                                                                                                                     |

| Fig. 4.6. Receiver gain and sensitivity at 10 <sup>-3</sup> CER vs. active power                                                                                                                                                                   |

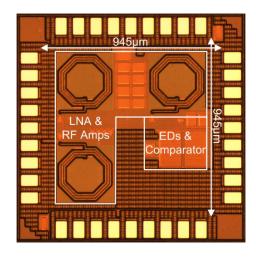

| Fig. 4.7. Die photo                                                                                                                                                                                                                                |

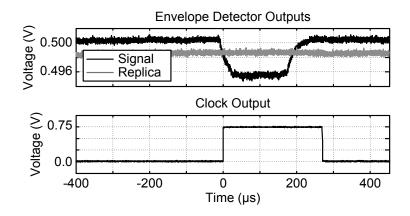

| Fig. 4.8. Harvested-clock from a 3G CDMA channel. 74                                                                                                                                                                                               |

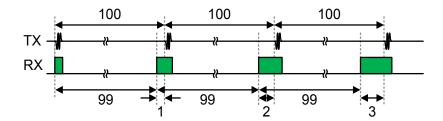

| Fig. 5.1. Bit-level turn-on time of the receiver when the receiver clock is 1% faster than the transmitter clock. The transmitted pulses are not being tracked by the receiver 85                                                                  |

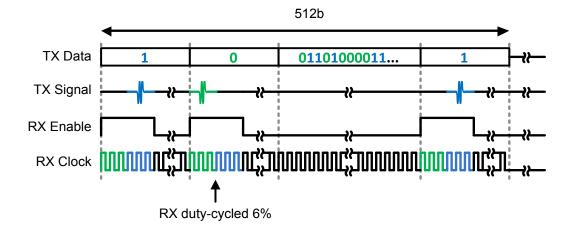

| Fig. 5.2. Bit-level turn-on time of the receiver when the receiver clock is 1% faster than the transmitter clock. The transmitted PPM pulses are being tracked by the receiver to maintain synchronization and a constant duty-cycling ratio of 6% |

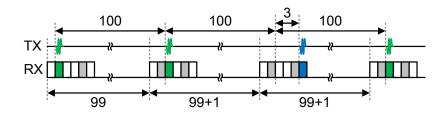

| Fig. 5.3. Pulse-position modulation divides time into two timeslots for 0-bit and 1-bit. Those timeslots are sub-divided into three bins (early, on-time, and late) for clock tracking by the receiver                                             |

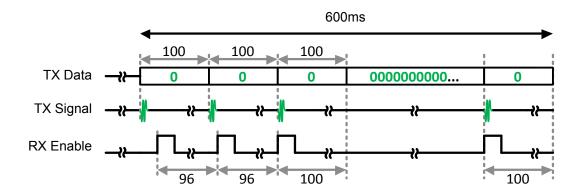

| Fig. 5.4. Synchronization header of a new communication protocol for a current-constrained radio.                                                                                                                                                  |

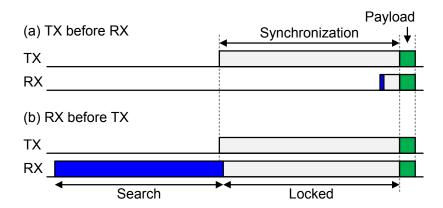

| Fig. 5.5. A complete packet with wake-up uncertainty between transmitter and receiver. In scenario (a), the transmitter wakes-up first while in scenario (b), the receiver wakes-up first.                                                         |

| Fig. 5.6. Payload of a new communication protocol for a current-constrained radio 90                                                                                                                                                               |

| Fig. 6.1. System block diagram of signal path and biasing                                                                                                                                                                                          |

| arrive, the energy is captured, which toggles the output until it is reset on the next clock edge.            |

|---------------------------------------------------------------------------------------------------------------|

| Fig. 6.3. Stacked circuit topologies along signal path                                                        |

| Fig. 6.4. Circuit topology of the latching comparator with tunable hysteresis                                 |

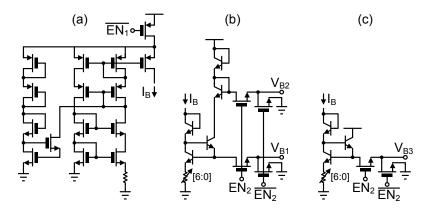

| Fig. 6.5. (a) Constant-G <sub>m</sub> bias circuit with (b)-(c) BJT mirrors                                   |

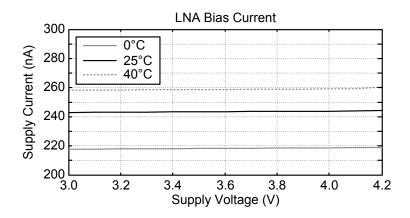

| Fig. 6.6. Bias current of the LNA over supply voltage and temperature                                         |

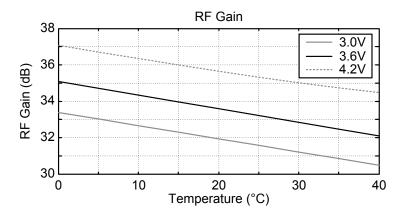

| Fig. 6.7. RF gain over temperature for several different supply voltages                                      |

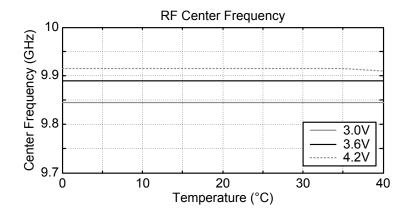

| Fig. 6.8. Center frequency of RF gain stages for several different supply voltages 102                        |

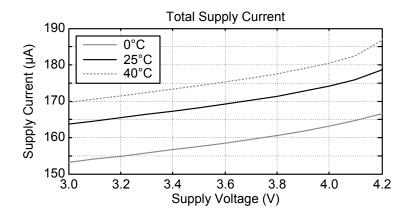

| Fig. 6.9. Total current through the receiver over supply voltage and temperature 102                          |

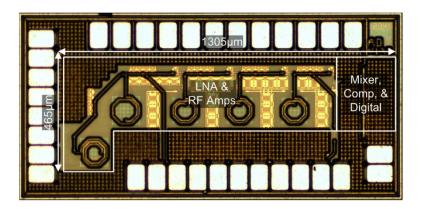

| Fig. 6.10. Die photo of the UWB receiver.                                                                     |

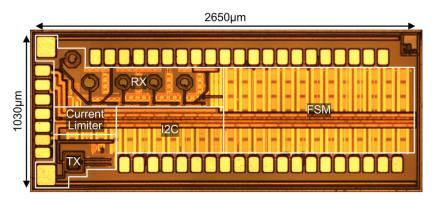

| Fig. 6.11. Die photo of the complete UWB transceiver                                                          |

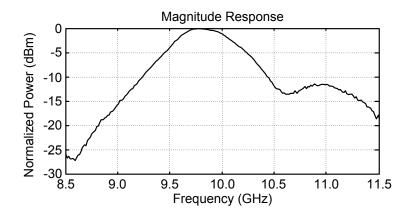

| Fig. 6.12. Magnitude response of the receiver                                                                 |

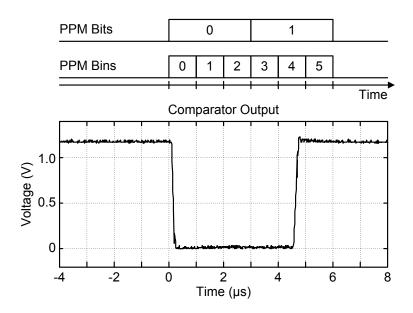

| Fig. 6.13. Output of the receiver after reset at the start of bin 0. An UWB pulse is transmitted during bin 4 |

# List of Tables

| Table 1.1. Monopole antenna length ( $\lambda/4$ ) in various frequency bands | 8   |

|-------------------------------------------------------------------------------|-----|

| Table 1.2. Power consumption comparison of sensor node components             | 15  |

| Table 2.1. Global time code services.                                         | 31  |

| Table 2.2. Summary of potential wireless standards as harvested-clocks        | 40  |

| Table 3.1. Measured receiver performance and comparison.                      | 62  |

| Table 4.1. Measured receiver performance and comparison.                      | 74  |

| Table 5.1. Comparison of BiCMOS SiGe processes.                               | 81  |

| Table 6.1. Measured receiver performance and comparison.                      | 106 |

| Table 6.2. Link budget for several different antennas.                        | 107 |

## Chapter 1

## Introduction

## 1.1. The Future of Computing

#### 1.1.1. Computing Trends

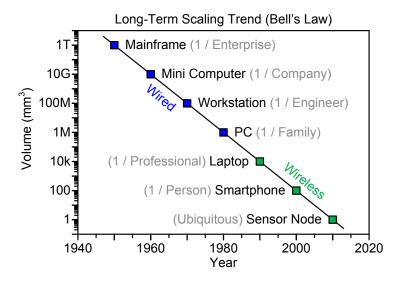

Computers today have changed dramatically from the mainframes decades ago. As computing has become increasingly ubiquitous, it is becoming difficult to remember a time when our phones weren't smart or when families shared a single computer at home. Based on Bell's Law [1], wireless sensor networks (WSNs) are perceived as the next big step in this decades-long trend toward smaller, more ubiquitous computing.

According to Bell's Law, a new class of computers will become the dominant market force approximately every decade [1]. Bell defines a computer class as a set of computers with a similar cost, programming environment, network, and user interface, where each class undergoes a standard product life cycle of growth and decline. Based on prior market trends, a new computer class has come into existence approximately every decade, and each successive class has had a 100x reduction in volume (Fig. 1.1). In addition, each successive class has resulted in a reduction in unit cost and an increase in volume of production [2].

In the 1950s, mainframes were the dominant computer class. Each mainframe consumed large rooms, and their cost limited their use to only one unit per enterprise. Mainframes were eventually overtaken by mini computers in the 1960s and then

Fig. 1.1. The long-term trend in computer scaling over the years [1].

workstations in the 1970s. By the 1980s personal computers (PCs) were entering family homes, and the 1990s saw laptops become the first wireless computer class. Today, smartphones have become the first truly personal computing class, and they fit in the palm of your hand. Assuming the trends in Bell's Law continue, then the next computer class is expected to be even smaller and more ubiquitous—the class of cubic-mm-scale wireless sensor nodes.

#### 1.1.2. Wireless Sensor Networks

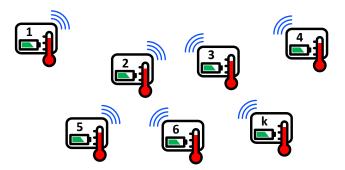

The goal of wireless sensor networks (WSNs) is straightforward—to sense the environment around them. Each node in the network is made up of components to process, sense, and communicate with other nodes in the network (Fig. 1.2). WSNs offer several advantages over wired networks, which can be costly, impractical, or obtrusive in many situations. As a result, there is significant interest in wireless sensor networks for a variety of applications [3]-[15].

Numerous surveys have been conducted in the past decade, which provide a good introduction to the application space for WSNs [3]-[8]. The surveys from [3]-[6], in

Fig. 1.2. Conceptual block diagram of a wireless sensor network with temperature sensing.

particular, give a good overview of the entire application space and highlight some of the many sensor networks that have been implemented in hardware. They also compare and contrast various testbeds and enumerate some of the challenges for realizing WSNs discussed throughout this chapter. While the applications discussed in these works vary widely, several topics have garnered particular interest, including: environmental, military, industrial, and biomedical applications. Several recently reported systems are highlighted below.

CSIRO [7] developed a WSN for the environmental tracking of livestock. The network tracks the movement of cattle, so that ranchers can better control pasture usage and also identify sick steer before disease spreads across an entire herd. The network consists of sensor node collars mounted on each steer along with several base stations placed at fixed locations around the ranch. The relative size of cattle suggests small node size is not of particular importance; however, small unit cost is important, as well as long node lifetimes of a year or more.

A long lifetime turns out to be very important for many industrial applications as well.

Among them, [9] has proposed a system to monitor pressure in an oil pipeline for signs of leakage. A sensor network is required because oil pipelines cover vast distances, making

human monitoring infeasible. Furthermore, pipelines are often located in remote regions, such that a lifetime of several years is desired. A second sensor network measures the corrosion of steel rebar used in concrete bridges [10]. Because the nodes are embedded into the concrete, a lifetime of years is essential. Volume, however, is less important, though each node must be reasonably sized to maintain the structural integrity of the bridge. A third sensor network measures the seismic activity on bridges and other structures for infrastructure health monitoring [11]. A final group has developed an in-tire pressure monitor to measure vehicle load and tire wear-out [12]. Due to the gradient forces inside the wheel well, the size of the node is restricted to a volume of approximately 1cm<sup>3</sup>. As a result, the system must be highly integrated. In addition, the node must be designed with a long lifetime because frequent access to the inside of a tire is impractical.

Based on observations from recently published patient health systems, long device lifetimes and small unit volumes are also crucial for many biomedical applications. For example, an intraocular pressure monitor was developed by [13], which measures pressure within the eye in order to diagnose glaucoma. The system is completely integrated into a 1.5mm<sup>3</sup> volume, making system integration and volume significant challenges. Finally, because the system must be implanted into the eye, a lifetime of weeks is desired. Another group has developed a highly integrated node for real-time electrocardiogram (ECG) measurements and wireless readout [14]. The main node occupies a volume on the order of 1cm<sup>3</sup>, excluding the sensor patches which must be placed across the chest. Unlike many of the other systems, an ECG only requires a lifetime of a few hours, though this ECG node has a 200hr battery life. Finally, a

Fig. 1.3. Examples of recent wireless sensor nodes (a) Mica Mote and (b) Fleck 3 [7]. glucometer was created by [15] to measure glucose from tear ducts. The node is built onto the surface of a contact lens, but the circuit core is all contained within a 1mm<sup>3</sup> volume. In this particular case, lifetime is not a problem, however, because the system rectifies a 2.4GHz signal for power. Nonetheless, the system must be low power, so that it can survive off of wirelessly rectified power. The wireless signal also must be low power to ensure patient health and safety.

While the wireless sensor networks surveyed vary widely in application, it is readily apparent that they universally benefit from longer node lifetimes, smaller unit volumes, and reduced cost. In addition, long-term deployments and small unit volumes are often necessary to satisfy the underlying feasibility of a particular application. The simultaneous desire for long lifetimes and small volumes, however, creates significant integration challenges as well as considerable energy constraints on system design. Ultimately, these challenges must be resolved in order for WSNs to be become a reality.

### 1.2. Wireless Sensor Nodes

## 1.2.1. Anatomy of Conventional Sensor Nodes

The first step toward mm-scale wireless sensor nodes is presented in [3]-[7]. The nodes are composed of multiple components on a printed circuit board (PCB) as shown in Fig. 1.3. The nodes consistently use commercial-off-the-shelf (COTS) components, and

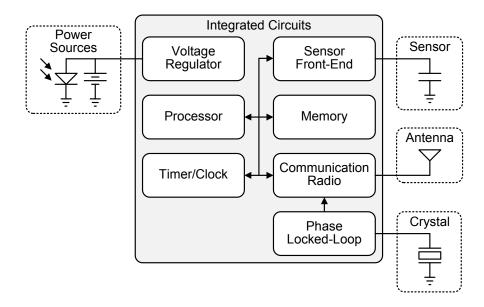

as a result, the PCBs measure several centimeters on a side. While energy usage and lifetime are a concern, they have little noticeable impact on the design other than the choice of low-power COTS components with a sleep mode. Thus, the nodes typically consist of a battery, voltage regulator, processor, sensor, and communication radio with external antenna and crystal oscillator (Fig. 1.4). The memory and clock are provided within the commercial processor, and solar cells are added to the system when long lifetimes are required for the application. Because many of these attributes mimic those found in the smartphone class of computers, these initial wireless sensor nodes constitute only the first step toward cubic-mm-scale computing.

#### 1.2.2. Component Trends & Challenges

As wireless sensor nodes continue to evolve, we must overcome the challenge of building smaller nodes that use less energy. Therefore, we must examine each component in the system and identify which components consume the most power and area. Then, we can propose solutions which will have a meaningful impact on overall system volume and lifetime. In this section, we discuss the challenges associated with the integrated circuits, antenna, oscillator, sensors, solar cells, and batteries of the system.

The most straightforward and simplest solution to reduce node volume, however, is to remove components. When removing components is impossible, component functionality can sometimes be achieved with alternative methods that require less volume or energy. Each of these design decisions, however, has trade-offs that must be analyzed.

Fig. 1.4. System block diagram of a recent wireless sensor node.

#### *Integrated Circuits*

One possible concern is the integrated circuit (IC) components. Fortunately, modern CMOS ICs, with the help of process scaling, are capable of providing the desired circuit functionality while still fitting within a cubic-mm form-factor [12]-[19]. To further reduce area requirements, several IC blocks can be integrated onto a single die to create a system-on-chip (SoC) [14],[19]. Unfortunately, the process requirements for many circuit components, such as processor and radio, differ; therefore, the one-size-fits-all approach of SoCs cannot yield the optimal system performance (i.e. minimal energy usage). In order to achieve optimal performance while maintaining small volumes, several recent integrated systems employ a stacked die approach, which provides the design freedom to select the optimal process for each layer [13],[16]-[18]. Thus, it is not the ICs that pose the greatest challenge to node scaling; it is the other components in the system, namely the antenna, oscillator, sensor, solar cell, and battery.

Table 1.1. Monopole antenna length ( $\lambda/4$ ) in various frequency bands.

| Frequency (Hz) | 434M | 915M | 2.45G | 3.1G | 10.6G | 24.1G | 61.3G |

|----------------|------|------|-------|------|-------|-------|-------|

| Band           | ISM  | ISM  | ISM   | UWB  | UWB   | ISM   | ISM   |

| Antenna (mm)   | 173  | 82   | 31    | 24   | 7     | 3     | 1     |

#### Antenna

The size of an antenna is dependent on many factors, but one of the most important factors is the operating frequency of the communication radio. For example, a basic monopole antenna sized for optimal radiation efficiency will have a length of  $l = \lambda/4$ , where  $\lambda$  is the wavelength of the wireless signal. Wavelength relates to the center frequency of the wireless channel, f, and the speed of light, c, through the expression  $\lambda = c/f$ . Therefore,  $l = \lambda/4 = c/(4f)$ , and antenna length is inversely proportional to operating frequency. Table 1.1 shows the length of the antenna at several common frequencies bands from 400MHz to 60GHz. Of these sample bands, 1mm-scale antennas only exist above 10GHz, and a  $\lambda/4$  monopole antenna is not truly 1mm long until the frequency increases to 60GHz. As a result, center frequency must be increased to 10GHz or more to satisfy volume requirements of cubic-mm systems. This result also suggests a need for higher frequency systems than commonly used in wireless communication today. Many of today's networks operate at frequencies from 850MHz to 2.4GHz. This includes commercial cellular and Wi-Fi networks, as well as many current WSNs.

Choosing to increase center frequency creates a couple of important trade-offs. First, the path loss in the wireless channel increases. As a result, more signal power is lost for a fixed communication distance. Second, the circuits that operate at these higher frequencies will consume more power. These circuits include the communication radio

and local oscillator. Therefore, reducing power consumption in both of these components is critical.

#### Local Oscillator

A local oscillator (LO) typically consists of a crystal oscillator and phase-locked loop (PLL) (Fig. 1.3), and for a number of reasons the typical LO is one block often removed from wireless sensor nodes. First, a crystal oscillator is bulky, which makes system integration difficult. The smallest commercial crystal oscillator available today is 2.0 x 1.6 x 0.8mm [20]. The bigger problem though is scaling. The size of crystal oscillators has scaled far more slowly than CMOS devices due to inherent physical properties of the crystals. In addition, crystal oscillators consume considerable power. The crystal oscillator from [20] provides a 13-52MHz oscillation frequency while consuming 3.4mW. With a 32.768kHz oscillator however, the power consumption is reduced to 3.4µW but the dimensions increase to 3.6 x 2.8 x 1.5mm [21]. A PLL adds even more power. While one recently published PLL consumes only 260µW using a 20MHz reference [22], it was designed specifically for WSNs and has a frequency accuracy of only 0.25%. Typical PLLs consume 1.2mW or more [23]-[24]. Ultimately, the combination of large volume requirements and high power consumption make PLL-based LOs undesirable for WSNs. Fortunately, alternative solutions exist.

The crystal oscillator and phase-locked loop can be replaced with a FBAR or BAW oscillator [12],[25]-[27]. FBAR oscillators in particular have been demonstrated that require relatively little area and consume less than 100µW [25]-[27]. Nonetheless, the need for an external component like a FBAR resonator can still be prohibitive in certain applications. Circuit solutions, such as LC or ring oscillators, are alternatives that

eliminate the need for external components, but clock accuracy and stability suffer [28][29]. In addition, power consumption can still be a concern, so a final option is to remove

the LO entirely. The communication radio then utilizes self-mixing to down-convert a

received signal to baseband and a pulsed oscillator to up-convert the signal for

transmission. Removing the LO does have significant repercussions, which are discussed

later, but it also results in the lowest power and smallest volume solution.

#### Sensors

The sensor is another component that can consume considerable power and area, but unfortunately, the system requirements for a sensor are highly application specific, which makes a general discussion regarding sensor design more difficult. It is safe to say that the size and power consumption of the sensor should be reduced in so far as possible. At the same time, there is no point in designing a sensor network with sensors that are unable to provide the desired measurements. As a result, sensor requirements may dictate a significant portion of the major system design decisions, like battery capacity and node volume.

Many sensors have been developed along with their read-out circuits, which satisfy the requirements of cubic-mm sensor networks. For example, an intraocular pressure monitor was developed by [13], which is completely integrated into a 1.5mm<sup>3</sup> volume and can be operated indefinitely. The contact lens for a glucose monitor from [15] is almost entirely packaging for the sensor. Meanwhile, numerous CMOS-based sensors for temperature measurement and event detection (i.e. an imager) also have been developed that meet the system requirements of cubic-mm sensor networks [30].

#### Solar Cells & Energy Harvesters

The need for solar cells or other energy harvesters is dictated by the operating environment, lifetime requirements, and power consumption of a node for a particular application. Fortunately, the area penalty of solar cells is small because they can be integrated into a die stack. Unfortunately, the power harvested from the cell is proportional to the area and efficiency of the cell. The highest reported efficiency of an unconcentrated monocrystalline silicon solar cell is 25% [31]. Assuming a cell with that efficiency and an area of 1mm<sup>2</sup>, then the solar cell will only produce 1mW of power at solar noon on a sunny day (AM1.5 or 1000W/m<sup>2</sup> of solar insolation). In this case, the solar cell is a separate die; however, for improved integration the solar cell can be integrated into a SoC, but the efficiency decreases to 10-12% [17]. In both cases, we are assuming the node will receive consistent outdoor sun, but that depends heavily on the application. It is far more likely the harvested energy per day is reduced by some scaling factor either from the node being indoors or only seeing intermittent sunlight. So while a solar cell can improve node lifetime, a very careful use case model must be developed to ensure the node has sufficient energy for sustained operation.

#### Battery

Finally, a battery is required for many applications, but the limitations in energy density of modern batteries create significant challenges for cubic-mm sensor nodes. Fortunately, millimeter-scale batteries exist (Fig. 1.5) [32]. Unfortunately, the capacity of mm-scale batteries is low because capacity scales with volume. For a 1.375 x 0.85 x 0.15mm custom lithium-ion (Li-ion) battery from Cymbet, the capacity is only 1μAh (Fig. 1.6), and the maximum discharge current is only 10μA [32]. The average power

Fig. 1.5. Custom 1µAh Cymbet micro-battery setup for testing.

Fig. 1.6. Measured discharge curve of the 1µAh Cymbet micro-battery.

Fig. 1.7. Power budget available vs. desired lifetime for different battery cells [30].

Fig. 1.8. Li-ion capacity comparison of Cymbet micro-batteries vs. commercial prismatic batteries.

consumption therefore must be 1nW or less for a one year node lifetime (Fig. 1.7)—far less than the active power of most circuits. As a result, for a node to survive a year the node either must be duty-cycled heavily or capacity must improve significantly.

We would like to increase capacity, so first we would like to know if micro-batteries perform as well as more traditional Li-ion cells. Fig. 1.8 compares the capacity of several lithium-ion prismatic cells of different volumes. Some of the cells are micro-batteries from Cymbet and have volumes of less than 1mm<sup>3</sup> [32]. The other cells come from Samsung, which manufactures batteries for cellular phones, laptop computers, and other electronics [33]. Trend lines were superimposed over the data to illustrate the battery capacity of each type of cell, and based on this data, micro-batteries have an order-of-magnitude lower unit capacity than those with larger volumes. This reduction is likely a result of packaging and the ion membrane—both of which consume a higher percentage of the total volume in a small battery. So while capacity could be improved, the nodes would remain energy-constrained.

While battery capacity has grown over the years, nodes likely will remain energyconstrained for the foreseeable future. Fig. 1.9 shows the long-term growth in battery

Fig. 1.9. Long-term growth in capacity of cylindrical Li-ion batteries since the first commercial Li-ion.

capacity for commercial Li-ion cells since their first introduction by Sony in 1991. In the past 20 years, battery capacity for cylindrical 18650 cells has only increased by a factor of three [34]-[49] while transistor count has increased by more than a factor of 1000 in the same time frame according to Moore's Law. While the increase in battery capacity has been steady, heavily duty-cycled circuit operation and harvested energy will be necessary for long-term node survival.

The exception is the few applications that don't require batteries. These systems rely on wireless power transfer from near-field coupling or RF rectification to enable the circuit elements on the node [15]. As a result, the node remains off until energy is available. These types of networks do not take measurements until requested by a user because a user serves as the aggregator. A common example is keycard access for room entry using passive RFID technology. In this example, the card reader radiates energy to the card, which provides a code to the reader before it grants access to the room. As another example, the glucometer in [15] only takes measurements when a patient or healthcare worker requests the data. In both cases, the measurements aren't automatic, and a human being is integral to the operation of the network.

Table 1.2. Power consumption comparison of sensor node components.

| Component                 | Active Power         | References               |

|---------------------------|----------------------|--------------------------|

| Processor and Memory      | 297nW                | [19]                     |

| Sensor & Sensor Front-End | Application Specific | Not Applicable           |

| High-Accuracy Timer       | 49.5mW               | [29]                     |

| Low-Accuracy Timer        | 1pW-80μW             | [50]-[56]                |

| Crystal Oscillator        | 3.4µW-3.4mW          | [20],[21]                |

| Phase-Locked Loop         | 260μW-9.1mW          | [22]-[24]                |

| FBAR Oscillator           | 22μW-89μW            | [25]-[27]                |

| Communication Radio       | 400μW-29mW           | [12],[14],[28],[58],[59] |

Unfortunately, a battery is required for many applications, and that battery has insufficient energy to operate a sensor node continuously for its desired lifetime. For a lifetime of one year, the average power available from a sub-cubic-mm battery is only 1nW (Fig. 1.7)—well below the active power consumption of most circuits. To alleviate this problem, energy usage must be reduced. The radio and oscillators easily dominate system energy usage if they are operated continuously to maintain synchronization (Table 1.2). Thus, reducing the power required to maintain synchronization between nodes can greatly improve node lifetime, making synchronization an important concern for cubic-mm WSNs [57].

## 1.2.3. Anatomy of Future Sensor Nodes

Cubic-millimeter wireless sensor nodes with long lifetimes are desired for many applications. Unfortunately, many current sensor nodes [3]-[7] have a volume of on the order of 10cm<sup>3</sup> to 100cm<sup>3</sup>, giving them many design attributes consistent with the

Fig. 1.10. System block diagram of a future wireless sensor node. smartphone class of computers. In effect, these sensor nodes are just the first step toward the smaller, more pervasive computers envisioned for wireless sensor networks.

An intermediate step has also emerged, which consists of sensor nodes with volumes on the order of 1cm<sup>3</sup> [2],[12],[14]. They are characterized by the fact that they use fewer COTS components. In addition, the volume and lifetime goals necessitate the use of application specific ICs (ASICs) optimized for low-power operation. This intermediate class of sensor nodes may be sufficient for some applications, but they would still universally benefit from system improvements made for smaller nodes.

The final step creates wireless sensor nodes which are truly a new class of computers [13],[15]-[18]. They have volumes on the order of 1mm<sup>3</sup>, dictated by the intended application. In addition, this new class of computers is heavily design-constrained, both in terms of volume and energy availability. As a result, significant design challenges must be addressed; fortunately however, the solutions also will benefit larger, less-constrained systems. Specifically, these less-constrained systems still benefit from lower costs and improved lifetimes.

Fig. 1.11. Conceptual system diagram of a cubic-mm sensing platform (a) encapsulated and (b) with the encapsulation cut-away.

Cubic-mm-scale wireless sensor nodes are highly integrated. The node still consists of many of the same components from Fig. 1.4, but several changes exist (Fig. 1.10). The future system will communicate wirelessly at a higher frequency to reduce the size of the antenna. The node will employ a stacked die configuration, including battery, solar cell, and sensor (Fig. 1.11), but the PLL and crystal oscillator will be removed to save energy and area. The battery is smaller and won't have sufficient energy to sustain continual operation for long lifetimes, so energy harvesting from a solar energy or some other energy source is necessary. In addition, everything must be duty-cycled; however with the radio duty-cycled, synchronization becomes a significant problem.

## 1.3. Synchronization for Wireless Communication

Synchronization is critical to the overall functionality and power budget of a wireless sensor network. The nodes must be on and communicating at the same time in order to be able to talk to one another. If the communication radio and timer remain on continuously they consume significant amounts of energy and will quickly drain the battery (Table 1.2). Recently reported communication radios consume at least 400µW for the receiver and more for the transmitter [12],[14],[28],[58],[59]. While solar harvesting can improve

the power budget to 10nW [13], the nodes remains severely energy-constrained. At the same time, the power budget for a one year lifetime is only 1nW (Fig. 1.7). As a result, continuous wireless communication is impractical for an energy-constrained node, and the radio must be heavily duty-cycled, spending most of its time in the off-state. Duty-cycling, however, makes synchronized communication among nodes in the network challenging while still minimizing energy usage.

#### 1.3.1. Sleep-Mode Power Consumption

The total power budget again of a sensor node is 1nW for a one year lifetime (Fig. 1.7). Therefore, the node must be heavily duty-cycled, and everything in the system needs to have a low-power sleep state. This includes the communication radio. Many of the recently published communications radios, however, don't report a sleep power [12],[28],[58],[59], and it is expected that the sleep power of these is on the order of microwatts. At the same time, it is critical to design for low leakage power in the radio because components with higher active power require better  $I_{on}/I_{off}$  current ratios. With an overall power budget of 1nW, the budget for the radio should be less than 100pW while in its sleep state. Additional power also must be given to other components in their sleep states, but the majority of the power budget must go toward maintaining synchronization.

#### 1.3.2. Timer

The traditional (and perhaps obvious) approach to reducing average power consumption is to duty-cycle the communication radio and schedule communication using a high-accuracy on-node timer. High-accuracy timers can be implemented in several different ways, but an external crystal oscillator would be one of the most accurate. Because an external crystal requires significant volume, it creates integration

challenges for future cubic-mm nodes. In addition, the power consumption of traditional crystal oscillators is high (3.4mW) [20]; however, a recent 32.768kHz crystal oscillator was published that consumes only 6nW [60]. Other than crystal oscillator, high-accuracy timers also can be implemented in CMOS [29]. To achieve high accuracy however, the circuits require significant tunability, which increases their power consumption to 49.5mW. As a result, a high-accuracy timer can be better accomplished using a 6nW crystal oscillator than with CMOS circuits alone, and duty-cycling the communication radio with a high-accuracy timer can provide significant improvement in the total synchronization energy. Using a 6nW crystal oscillator may stay within the power budget of some applications, but the average power must be reduced further for applications requiring multi-year lifetimes.

While less accurate timers are not desired, they do keep time while consuming less power and less area in CMOS. Ultimately, the goal is to maximize accuracy—in terms of rms jitter per cycle or PVT variation—for a given power consumption. Several different topologies have been proposed, but the most common are tuned ring oscillators or relaxation oscillators [50]-[53]. More importantly, several timers have been reported with sub-nanowatt power consumption [54]-[56], making one year node lifetimes possible when the nodes are heavily duty-cycled.