# **Graphene Nanoelectronics - From Synthesis to Device Applications**

by

## Seunghyun Lee

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Electrical Engineering) in The University of Michigan 2013

#### **Doctoral Committee:**

Assistant Professor Zhaohui Zhong, Chair Professor L. Jay Guo Professor Khalil Najafi Professor Steven M. Yalisove © Seunghyun Lee

To my loved ones

#### **ACKNOWLEDGEMENTS**

First of all, I would like to thank God for leading me through this journey. I thank my parents, my wife and the rest of my family for their love, support and many encouragements during my life.

I would like to express my heartfelt gratitude and appreciation to my advisor Prof. Zhaohui Zhong and Prof. Khalil Najafi for their support, encouragement and guidance throughout my graduate study. I also would like to thank my other committee members, Prof. Lingjie (Jay) Guo and Prof. Steven Yalisove for devoting their time to review this dissertation and providing valuable suggestions.

I would like to thank Dr. David Wentzloff for his guidance in analog electronics and tape out process. I am also thankful to my past and current research group members, Dr. Nanditha Dissanayake, Dr. Chung Chiang Wu, Kyunghoon Lee, Chang-Hua Liu, Girish Kulkarni, Che-Hung Liu, and Rui Li. I would like to extend my gratitude to those graduate students with whom I have not directly collaborated but whose assistance I greatly appreciate. I thank Dr. Geonwook Yoo, Gwang Hyun Baek, Kuk-Hwan Kim, Jinyoung Hwang, Hyungwon Bacc, Hui Joon Park, Jaeyong Lee, Ling Tao, Dr. Luke Lee, Daeyoung Lee, Seunghyun Oh, Yonghyun Shim, and Siddharth Gaba.

Excellent support from the Lurie nanofabrication facility staff is greatly appreciated. I would like to thank Timothy Brock, Gregory Allion, Brian Armstrong,

Russ Clifford, Pilar Herrera-Fierro, Sandrine Martin, Matthew Oonk, Brian VanDerElzen, and Nadine Wang.

I thank Lisa Vogel, Melanie Caughey, Denise Oscar, Laura Jarels, Frances Doman, Deb Swartz, and Beth Stalnaker for administrative support throughout my graduate career. I wish to acknowledge the EECS department and the National Science Foundation (NSF) for funding this research.

# TABLE OF CONTENTS

| DEDICATION                                       | ii                      |

|--------------------------------------------------|-------------------------|

| ACKNOWLEDGEMENTS                                 | iii                     |

| LIST OF FIGURES                                  | viii                    |

| LIST OF APPENDICES                               | xvii                    |

| ABSTRACT                                         | xviii                   |

| CHAPTER                                          |                         |

| I. Introduction                                  | 1                       |

| 1.1 Forward                                      | 1                       |

| 1.2 Electronic Properties of Graphene            |                         |

| 1.3 Applications in Electronics                  |                         |

| 1.4 Synthesis of Graphene                        |                         |

| 1.5 Verification of Graphene Layer Number        |                         |

| 1.6 Motivation and Goals                         |                         |

| 1.7 Thesis Organization                          |                         |

| II. Wafer Scale Homogeneous Bilayer Graphene     | Films by Chemical Vapor |

| Deposition                                       |                         |

| 2.1 Introduction                                 | 32                      |

| 2.2 Synthesis of Bilayer Graphene Films          | 33                      |

| 2.2.1 Chemical Vapor Deposition Pro              |                         |

| 2.2.2 Transfer Process                           | 34                      |

| 2.3 Optical characterization of bilayer grapher  | ne films35              |

| 2.3.1 Raman spectroscopy                         |                         |

| 2.3.2 Transmission electron microsco             | ppy 39                  |

| 2.3.3 Two dimensional Raman raster               |                         |

| 2.4 Electrical characterization of bilayer graph |                         |

| 2.4.1 Fabrication                                |                         |

| 2.4.2 Electrical measurement of band             | gap 43                  |

| 2.4.3 Yield and distribution                     | 47                      |

| 2.5 Discussion and conclusion                                        | 49    |

|----------------------------------------------------------------------|-------|

| III. Homogeneous Bilayer Graphene Film based Flexible and Transpare  | ent   |

| Conductor                                                            | 52    |

| 3.1 Introduction                                                     | 52    |

| 3.2 Preparation of bilayer graphene based transparent conductor      |       |

| 3.3 Comparison of SLG and BLG stacks                                 |       |

| 3.3.1 Raman spectroscopy and optical verification                    |       |

| 3.3.2 Transmittance measurement                                      |       |

| 3.3.3 Sheet resistance measurement                                   | 58    |

| 3.4 Comparison with other methods                                    | 60    |

| 3.5 Sheet resistance change with strain                              | 61    |

| 3.6 Uniformity of BLG stack                                          | 63    |

| 3.7 Discussion and conclusion                                        | 65    |

|                                                                      |       |

| IV. Flexible and Transparent All-Graphene Circuits for Quaternary Di | gital |

| Modulations                                                          | 66    |

| 4.1 Introduction                                                     | 66    |

| 4.2 Constellation diagram of different modulation method             |       |

| 4.3 Device fabrication and transmittance                             |       |

| 4.4 Modulation mechanism and transistor characteristics              |       |

| 4.5 Binary and quaternary modulation with a single transistor        |       |

| 4.6 Quadrature phase-shift keying with two graphene transistors      |       |

| 4.7 All-graphene modulator circuits under mechanical strain          |       |

| 4.8 Discussion and conclusion                                        |       |

|                                                                      |       |

| V. Bipolar Junction Transistor Based on Graphene Heterostructure     | 90    |

| 5.1 Introduction                                                     | 90    |

| 5.2 Motivation for graphene based bipolar transistor                 |       |

| 5.3 Bipolar transistor based on graphene heterostructure             |       |

| 5.4 Graphene - silicon junction interface                            |       |

| 5.5 Output characteristics                                           |       |

| 5.6 Comparison with metal based surface barrier transistor           |       |

| 5.7 Operating Principle                                              |       |

| 5.8 Common-emitter configured amplifier response                     |       |

| 5.9 Discussion and conclusion                                        |       |

| VI. Summary and Conclusions                                          | 113   |

| 6.1 Summary of completed work                                        | 113   |

| 6.1.1 Wafer Scale Homogeneous Bilayer Graphene Films by              |       |

| Chemical Vapor Deposition                                  | 113 |

|------------------------------------------------------------|-----|

| 6.1.2 Homogeneous Bilayer Graphene Film based Flexible     |     |

| Transparent Conductor                                      | 114 |

| 6.1.3 An All-Graphene Flexible and Transparent Circuit for |     |

| Quaternary Digital Modulation                              | 115 |

| 6.1.4 Bipolar Junction Transistor based on Graphene        |     |

| Heterostructure                                            | 116 |

| 6.2 Future Outlook and challenges                          | 116 |

| 6.2.1 Transparent conductors                               | 117 |

| 6.2.2 Analog electronics                                   | 117 |

|                                                            |     |

|                                                            |     |

|                                                            |     |

| APPENDICES                                                 | 121 |

|                                                            |     |

| BIBLIOGRAPHY                                               | 127 |

# LIST OF FIGURES

| Figure 1.1 The graphene crystal lattice                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2 The graphene crystal lattice.2 Graphene is the two dimensional building block for carbon based nanomaterials of all other dimensionalities. It can be wrapped up into 0-D fullerenes, rolled into 1-D carbon nanotubes or stacked into 3-D graphite. (adopted from [1])                             |

| Figure 1.3 A scanning electron microscopy image of mechanically exfoliated graphene and graphite. Graphene is shown as the region with the lightest color at the right edge of the sample. The rest of the darker colored areas of the sample are either few layer graphenes or thicker graphite               |

| Figure 1.4 Hexagonal crystal lattice of graphene (left) and its Brillouin zone (right). $a_1$ and $a_2$ are the lattice unit vectors, and $\delta_i$ , $i=1,2,3$ are the nearest-neighbor vectors. In its corresponding Brillouin zone, the Dirac cones are located at the K and K' points. (adopted from [6]) |

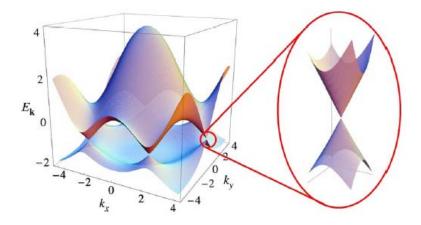

| Figure 1.5 The energy dispersions of graphene crystal lattice. The conductance band touches the valence band at the K and the K' points (i.e. the Dirac points). (adopted from [6])                                                                                                                            |

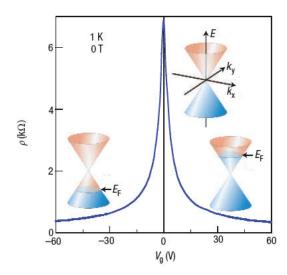

| Figure 1.6 Ambipolar electric field effect in single-layer graphene. The insets show its low-energy spectrum, indicating changes in the position of the Fermi energy $E_F$ with varying gate voltage $V_g$ . (adapted from [1])                                                                                |

| Figure 1.7 A graphene based touch screen demonstrated in ref [4]                                                                                                                                                                                                                                               |

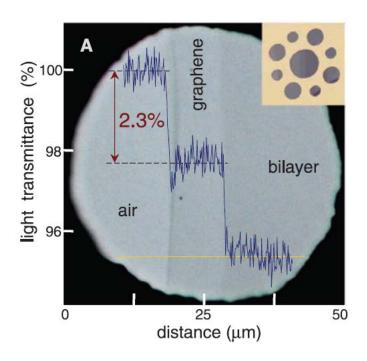

| Figure 1.8 Photograph of a 50 µm aperture partially covered by graphene and its bilayer. The line scan profile shows the intensity of transmitted white light along the yellow line. The inset is the support structure with 20, 30, and 50 µm in diameter with graphene placed over them. (adopted from [3])  |

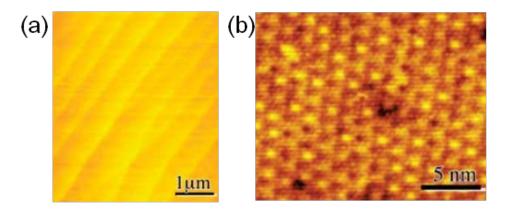

| Figure 1.9 Epitaxial graphene grown on SiC wafer. (a) AFM image of graphitized SiC. Graphite is continuous over the steps. (b) STM image of one monolayer of epitaxial graphene on SiC. (adopted from [55]                                                                                                     |

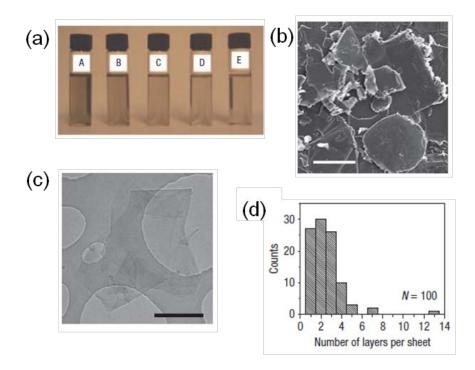

| Figure 1.10 Thin films of solution-processed graphene oxide. (a) Photographs of graphene oxide thin films on filtration membrane. (b) Films showing the different densities of the overlapped regions (darker colors) between the graphene sheets. Scale bar is 20 µm. (adopted from [38])                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.11 Optical characterization and Electron microscopy of graphite dispersions. (a) Dispersions of graphite flakes in N-methylpyrrolidone (NMP), at a range of concentrations ranging from 6 $\mu$ g/ml to 4 $\mu$ g/ml. (b) SEM image of sediment after centrifugation. Scale bar is 25 $\mu$ m. (c) Bright-field TEM images of a folded graphene sheet and multilayer graphene, both deposited from NMP. Scale bar is 500 nm. (d) Histogram of the number of flakes as a function of the number of monolayers per sheet. (adopted from [57])                                                   |

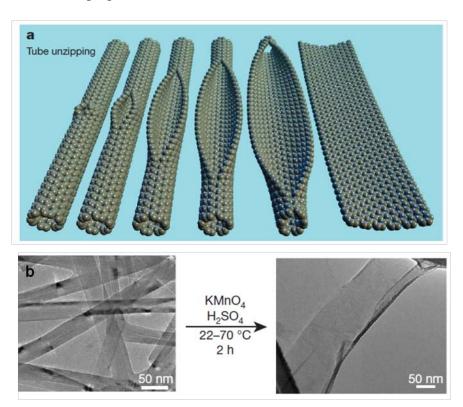

| Figure 1.12 Nanoribbon formation and imaging (a) Representation of the gradual unzipping of one wall of a carbon nanotube to form a nanoribbon. (b) TEM images depicting the transformation of multi-walled carbon nanotubes (left) into oxidized nanoribbons (right). The right-hand side of the ribbon is partly folded onto itself. The dark structures are part of the carbon imaging grid. (adopted from [59])                                                                                                                                                                                    |

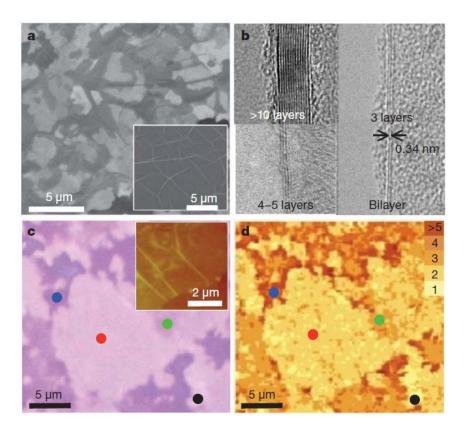

| Figure 1.13 Various spectroscopic analyses of the large-scale graphene films grown on nickel foils by CVD. (a) SEM images of as-grown graphene films on thin (300 nm) nickel layers and thick (1 mm) Ni foils (inset). (b) TEM images of graphene films of different thicknesses. (c) An optical microscope image of the graphene film transferred to a 300 nm thick silicon dioxide layer. The inset AFM image shows typical rippled structures. (d) A confocal scanning Raman image corresponding to image in (c). The number of layers is differentiated by the color contrast. (adopted from [66]) |

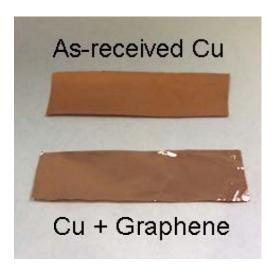

| Figure 1.14 Photos of as-received Cu foil without graphene and Cu foil covered with graphene. (adopted from [2])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

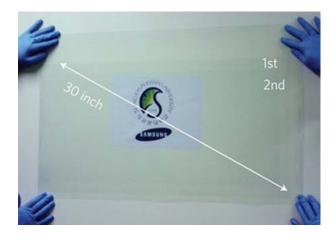

| Figure 1.15 A transparent ultralarge-area graphene film transferred on a 35-inch PET sheet. (adopted from [4])                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

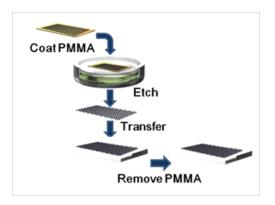

| Figure 1.16 An illustration of graphene transfer process. Graphene on top of the copper foil is coated with PMMA and the backside copper is etched using wet etchant. The graphene is transferred to an arbitrary substrate and the top PMMA is removed with acetone                                                                                                                                                                                                                                                                                                                                   |

| Figure 1.17 The CVD furnace model used in this work. The quartz tube inside the furnace is 3 inches in diameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Figure 1.18 Calculated phonon dispersion relation of graphene showing the iLO, iTO, oTO, iLA, iTA and oTA phonon branches. (Adapted from [69])                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

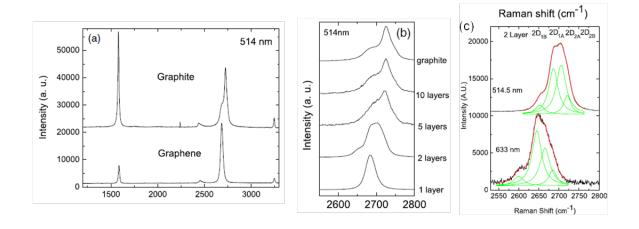

| Figure 1.19 Raman spectra of graphene with different thickness (a) Comparison o Raman spectra at 514 nm for bulk graphite and graphene. They are scaled to have simila height of the 2D peak at ~2700 cm <sup>-1</sup> . (b) Evolution of the 2D band at 514 nm with the number of layers. (c) The four components of the 2D band in bilayer (two layer graphene at 514 and 633 nm. (adapted from [68])                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

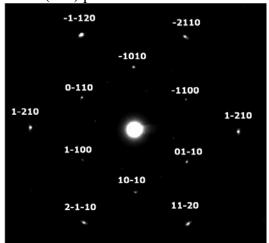

| Figure 1.20 Diffraction pattern of a bilayer graphene layer from transmission electron microscopy and its Bravais-Miller indices. Six fold symmetry is clearly observable 24                                                                                                                                                                                                                                                                                                                          |

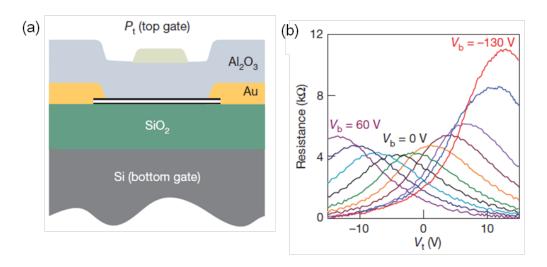

| Figure 1.21 Gate response curve of double gate graphene transistor. (a) Illustration of a cross-sectional side view of the gated device. (b) Graphene electrical resistance as a function of top gate voltage $V_t$ at different fixed bottom gate voltages $V_b$ . (adopted from [73])                                                                                                                                                                                                               |

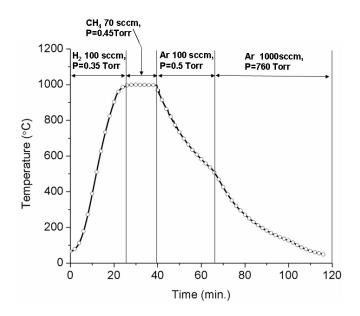

| Figure 2.1 Temperature vs. time plot of bilayer graphene growth condition. Pressure value is denoted as "P"                                                                                                                                                                                                                                                                                                                                                                                           |

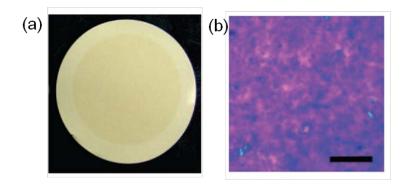

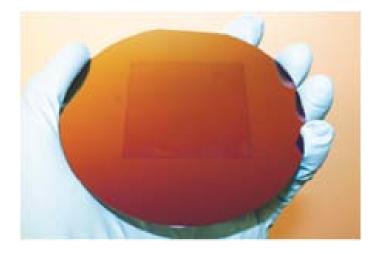

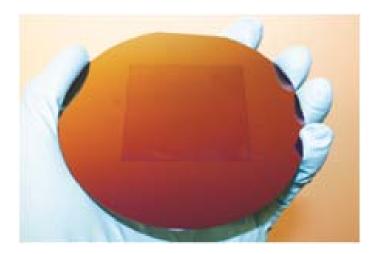

| Figure 2.2 Wafer scale homogeneous bilayer graphene film grown by CVD. Photograph of a 2 inch by 2 inch bilayer graphene film transferred onto a 4 inch Si substrate with 280nm thermal oxide.                                                                                                                                                                                                                                                                                                        |

| Figure 2.3 Optical microscopy image showing the edge of bilayer graphene film. Scale bar is $100 \ \mu m$ .                                                                                                                                                                                                                                                                                                                                                                                           |

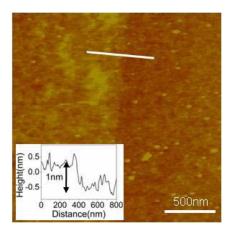

| Figure 2.4 AFM image of bilayer graphene transferred onto SiO <sub>2</sub> /Si. (Inset) Height profile obtained by taking cross section along the white line on the image. The heights of our bilayer graphene were consistently found to be between 0.89nm and 1.2nm                                                                                                                                                                                                                                 |

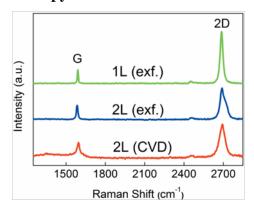

| Figure 2.5 Raman spectra taken from CVD grown bilayer graphene (red solid line) exfoliated single-layer (green solid line) and bilayer graphene (blue solid line) samples Laser excitation wavelength is 514 nm                                                                                                                                                                                                                                                                                       |

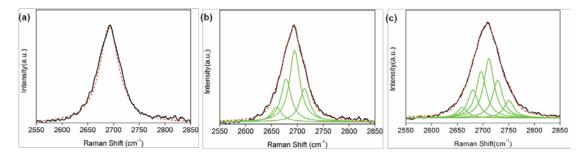

| Figure 2.6 The measured 2D Raman band of a bilayer with the FWHM of 45cm <sup>-1</sup> . (1 Single Lorentzian fit (red dash line) of the peak of Figure 2.6a clearly shows deviation from the measured 2D band. (b)The peak can be well-fitted with the sum of four single Lorentzian (green solid line) of 24cm <sup>-1</sup> FWHM. (c), The measured 2D Raman band of a trilayer with the FWHM of 62cm <sup>-1</sup> . 2D peak of trilayer are fitted with six single Lorentzian (green solid line) |

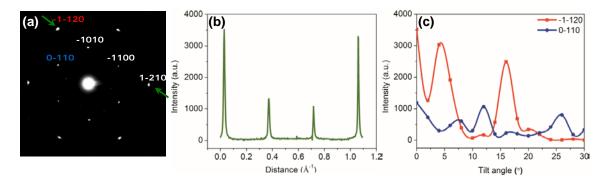

| Figure 2.7 Selected area electron diffraction pattern of bilayer graphene. (a) Normal incident diffraction pattern of bilayer graphene sample. The bilayer graphene film was transferred onto copper grid with holy carbon supporting film. The diffraction image was taken by JEOL 2010F Analytical Electron Microscope with acceleration voltage of 200 kV. (b) Profile plot of diffraction peak intensities across a line cut indicated by the green                                               |

| arrows shown in (a). (c) Diffraction peak intensities as a function of tilt angle for (0-110) (in red) and (-1-120) (in blue)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

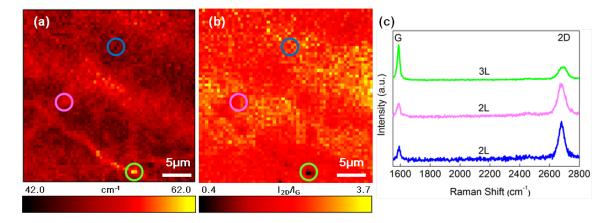

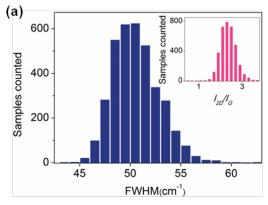

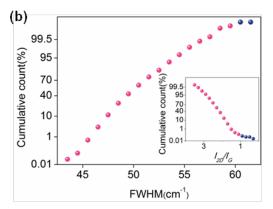

| Figure 2.8 Spatially resolved Raman spectroscopy of CVD bilayer graphene. (a) and (b) Two-dimensional color mapping of the FWHMs of Raman 2D band and $I_{2D}/I_G$ ratios over 30 $\mu$ m× 30 $\mu$ m area, respectively. (c) Raman spectra from the marked spots corresponding colored circles showing bilayer and trilayer graphene                                                                                                                                                                                                                                                                                                                     |

| Figure 2.9 . (a) Histogram of the FWHMs of Raman 2D band corresponding to area shown in Figure 2.8 (a). (Top right Inset) Histogram of $I_{2D}/I_G$ ratios for the same area. (b) Cumulative count plot of FWHMs of 2D band. Pink (blue) spheres represent the FWHM less (more) than 60 cm-1. (Inset) Cumulative count plot of $I_{2D}/I_G$ ratios. Pink (blue) spheres indicate the ratio larger (smaller) than 1. (For Raman mapping, $\lambda_{laser}$ =514 nm 500nm step size, 100x objector).                                                                                                                                                        |

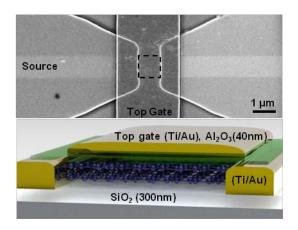

| Figure 2.10 Electrical transport studies on dual-gate bilayer graphene devices. Scanning electron microscopy image (top) and illustration (bottom) of a dual-gate bilayer device. The dashed square in the SEM image indicates the 1 µm 1 µm bilayer graphene piece underneath the top gate                                                                                                                                                                                                                                                                                                                                                               |

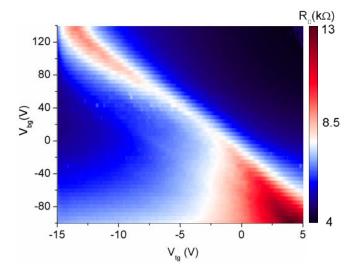

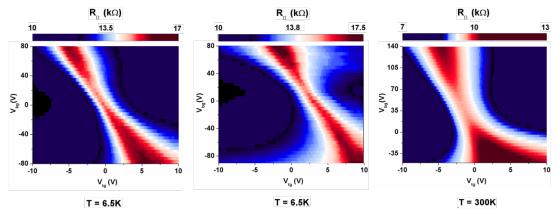

| Figure 2.11 Two dimensional color plot of square resistance $R_{\mbox{\tiny $\square$}}$ vs. top gate voltage $V_{tg}$ and back gate voltage $V_{bg}$ at temperature of 6.5K                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

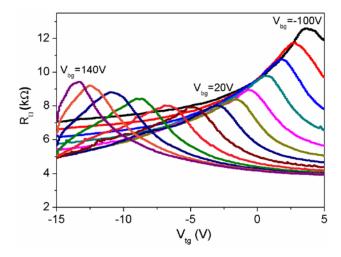

| Figure 2.12 $R_{\text{\tiny \square}}$ vs. $V_{\text{tg}}$ at different value of fixed $V_{\text{bg}}$ . The series of curves are taken from Vbg of -100V to 140V, with 20V increment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

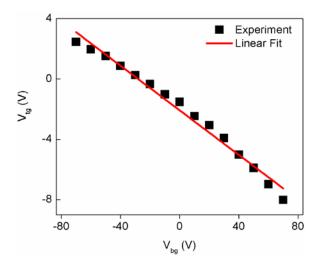

| Figure 2.13 The charge neutral points indicated as set of $(V_{tg},V_{bg})$ values at the peak square resistance $R_{\square,dirac}$ . The red line is the linear fit. The electrical measurements were carried out in a closed cycle cryogenic probe station (LakeShore, CRX-4K), using lock-in technique at 1kHz with AC excitation voltage of $100\mu V$                                                                                                                                                                                                                                                                                               |

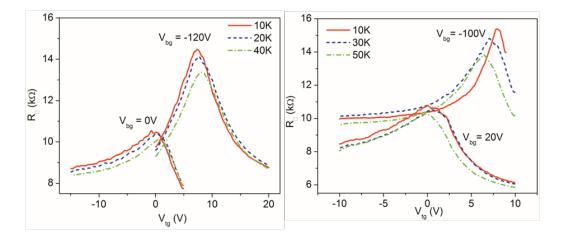

| Figure 2.15 Two dual-gate graphene devices showing temperature dependent resistance versus top gate voltage sweep at two different back gate voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Figure 2.14 Three dual-gate graphene devices showing bilayer transport behavior 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

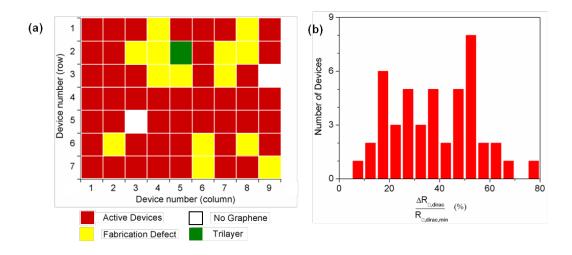

| Figure 2.16 Bilayer statistics from electrical transport measurement on dual-gate graphene devices. (a) A color-coded map of 63 devices (7 rows x 9 columns) fabricated across the same graphene film. The red squares indicate bilayer graphene confirmed by transport measurement; the yellow squares indicate devices which have fabrication defects; the white squares mark the region with no graphene; and the green square represents device with trilayer response from the transport measurement. (b) Histogram of ΔR <sub>E dirac</sub> / R <sub>E dirac min</sub> values in percentage for 46 active devices ΔR <sub>E dirac</sub> corresponds |

| to the maximum difference in $R_{\square,dirac}$ within $V_{tg}$ of $\pm 10V$ and $V_{bg}$ of $\pm 120V$ . $R_{\square,dirac,min}$ is the minimum peak resistance                                                                                                                                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

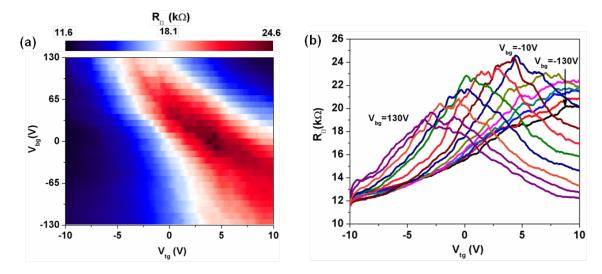

| Figure 2.17 (a) A device showing trilayer transport behaviour. The observed peak square resistance decreases as increasing field. This is distinctively different from bilayer response. (b) Horizontal section views with $R\Box$ plotted against $V_{tg}$ at fixed $V_{bg}$ from -130 to 130 V with 20V increment |

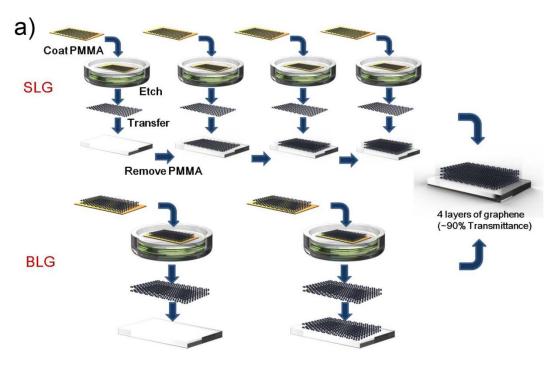

| Figure 3.1 Schematic comparison of SLG method and BLG method to synthesize 4 layers of graphene stack to achieve lower sheet resistance                                                                                                                                                                             |

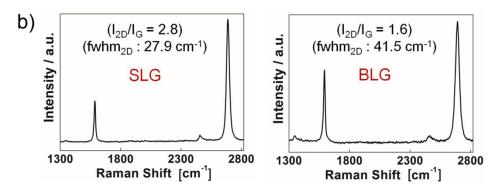

| Figure 3.2 Raman spectra taken from CVD grown SLG (left) and BLG (right) samples The average values of $I_{2D}/I_G$ and fwhm <sub>2D</sub> from 10 random areas are shown in the plot 55                                                                                                                            |

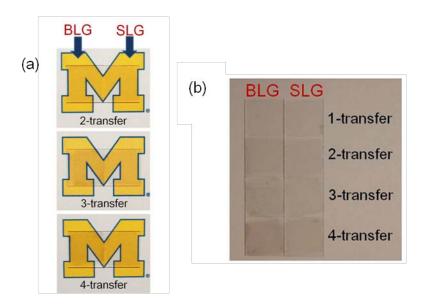

| Figure 3.3 Optical comparison of SLG and BLG graphene stacks on glass substrate for 1,2,3,4 transfers with (a) and without(b) background color                                                                                                                                                                      |

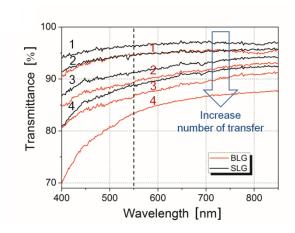

| Figure 3.4 Transmittance curve as a function of wavelength for both SLG and BLG stack after 1,2,3,4 transfers respectively. The number near each measurement line indicates the number of transfers.                                                                                                                |

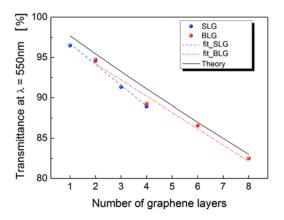

| Figure 3.5 Transmittance value at $\lambda$ =550nm as a function of graphene layers for SLG and BLG stacks and its fits.                                                                                                                                                                                            |

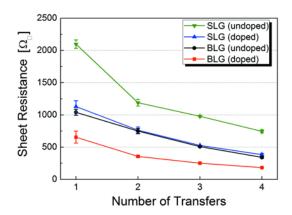

| Figure 3.6 Sheet resistance of both undoped and doped SLG,BLG stacks with different number of transfers.                                                                                                                                                                                                            |

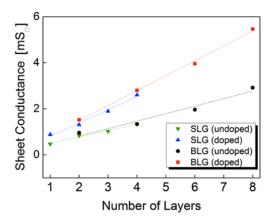

| Figure 3.7 Sheet conductance of both undoped and doped SLG,BLG stacks as a function of graphene layer number                                                                                                                                                                                                        |

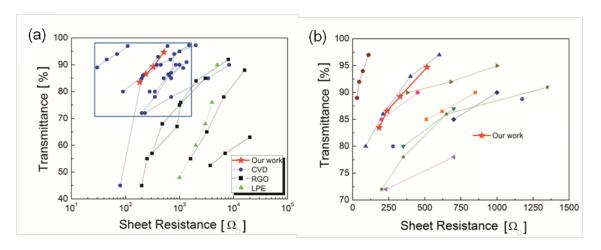

| Figure 3.8 (a),(b) Transmittance versus sheet resistance for graphene based transparent conductors grouped according to production methods in log scale (a) and only with CVD method in linear scale (b). Blue rectangle in (a) represents the range of x,y axis for (b). 60                                        |

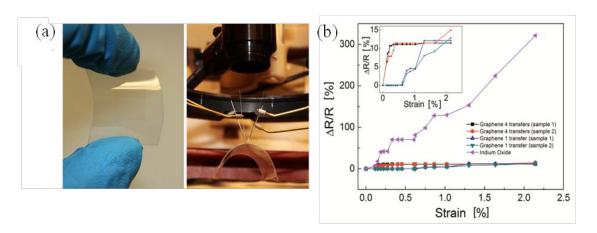

| Figure 3.9 (a) Photographs of graphene film on flexed PET substrate(left) and measurement setup of strained substrates (right). (b) Variation in resistance of stacked BLG films and indium oxide films on 200µm thick PET substrate as a function of strain values.                                                |

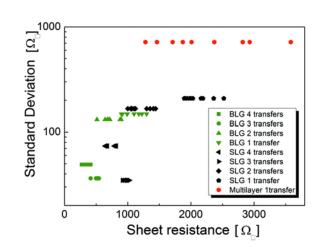

| Figure 3.10 Distribution of sheet resistance and its standard deviation values for SLG,BLG stacks and a cvd grown multilayer (MLG) sample. 10 measurements were taken on different areas of each sample                                                                                                             |

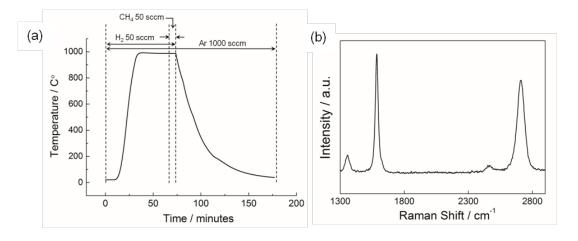

| Figure 3.11 (a) Temperature vs. time plot of multilayer graphene growth condition. Pressure is maintained to atmospheric pressure at all time except the initial purge stage. (b) Raman spectroscopy result showing typical multilayer signal                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

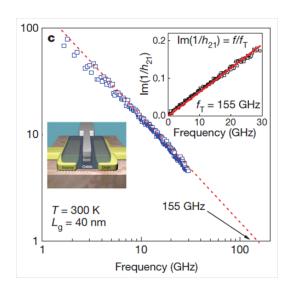

| Figure 4.1 Graphene transistor made CVD graphene with a cutoff frequency of 155 GHz. Inset is an illustration of the graphene transistor structure. (adopted from [84])                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Figure 4.2 Graphene frequency multiplier was demonstrated with just one transistor in reference [30]. This is possible by superimposing an AC signal to a DC voltage which is biased at the charge neutrality point. (adopted from [30])                                                                                                                                                                                                                                                                                                                                                   |

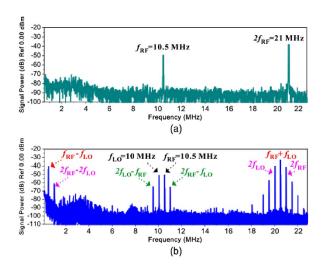

| Figure 4.3 Spectrum analysis of a graphene transistor based doubler and a mixer from reference [33]. (a) Output spectrum with single RF input $f_{RF}=10.5$ MHz without LO signal. The frequency doubling is observed. The signal power at $2f_{RF}=21$ MHz is about 10 dB higher than the signal power at $f_{RF}=10.5$ MHz without filtering. (b) Output spectrum with RF input $f_{RF}=10.5$ MHz and LO $f_{LO}=10$ MHz at equal power. The presence of strong signal power at $f_{RF}-f_{LO}=500$ kHz and $f_{RF}+f_{LO}=21.5$ MHz demonstrates mixing operations. (adopted from [33]) |

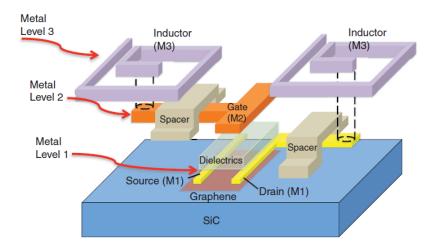

| Figure 4.4 Illustration of a graphene mixer circuit integrated with silicon carbide wafer and other passive components. (adopted from [34]). The top-gated graphene transistor and two inductors are connected to the gate and the drain of the Graphene FET. Three metals layers of the graphene IC are represented by M1, M2, and M3. A layer of 120-nm-thick SiO2 is used as the isolation spacer to electrically separate the inductors (M3) from the underlying interconnects (M1 and M2).                                                                                            |

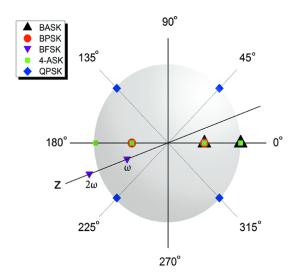

| Figure 4.5 A constellation diagram depicting five different digital modulation techniques demonstrated in this work. The z-axis, representing the frequency, is included to show the frequency modulated signals                                                                                                                                                                                                                                                                                                                                                                           |

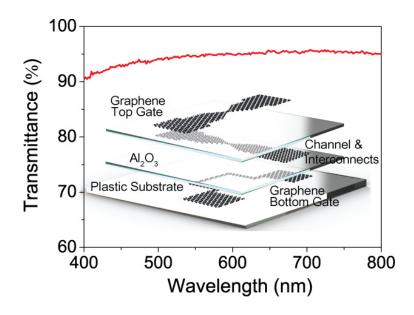

| Figure 4.6 A plot of the transmittance as a function of the wavelength and an illustration of the all-graphene transistor structure (inset)                                                                                                                                                                                                                                                                                                                                                                                                                                                |

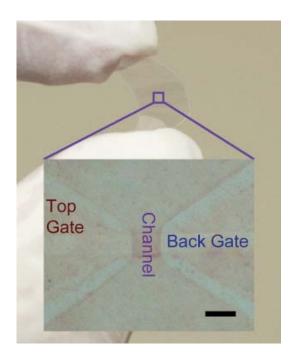

| Figure 4.7 a photograph of graphene circuit on a transparent and bendable plastic substrate, and a microscopic image of an all-graphene transistor (inset). The scale bar is $10\mu m$ .                                                                                                                                                                                                                                                                                                                                                                                                   |

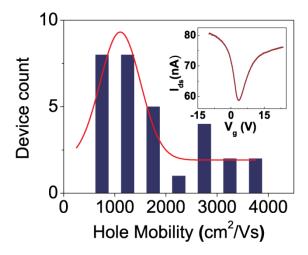

| Figure 4.8 A histogram of the hole mobility extracted from 30 transistors and its Gaussian fit (red line). The inset is a plot of the ambipolar current as a function of gate voltage for a typical all-graphene transistor. Voltage across the drain and the source is $10\text{mV}$                                                                                                                                                                                                                                                                                                      |

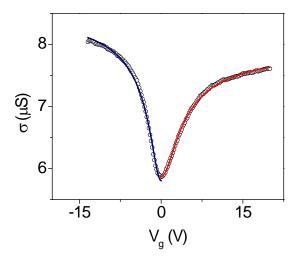

| Figure 4.9 Conductance as a function of gate voltage (round symbols) and its fittings (solid line) for a typical device. The blue and the red solid lines correspond to the fittings                                                                                                                                                                                                                                                                                                                                                                                                       |

| for hole and electron mobility respectively. See Appendix C for details on the fitting method                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

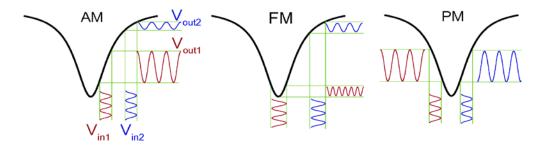

| Figure 4.10 Illustrations of amplitude, frequency, and phase modulation of a sinusoidal wave achieved by operating a single ambipolar graphene transistor at different gate biases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

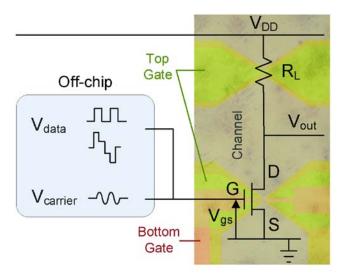

| Figure 4.11 A circuit diagram with a false-color image of graphene transistors connected in a common-source configuration. The $V_{\text{data}}$ signal is the digital data that is encoded onto the carrier signal $V_{\text{carrier}}$ . The $V_{\text{data}}$ signal is a square wave for all three binary digital modulation schemes and a four level step-like wave for the quaternary amplitude-shift keying modulation scheme.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

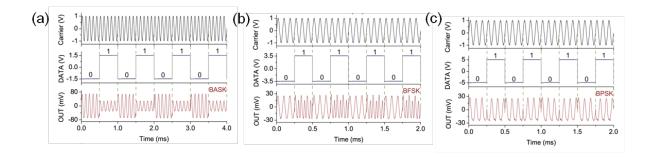

| Figure 4.12 (a) Time domain plot of the binary amplitude-shift keying. $V_{DD}$ of 1V was the power supply voltage. (b) Time domain plot of the binary frequency-shift keying at $V_{DD}$ of 1V. (c) Time domain plot of the binary phase-shift keying at $V_{DD}$ of 1V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

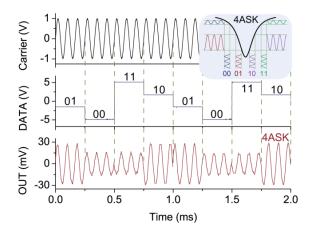

| Figure 4.13 A time domain plot of the quaternary amplitude-shift keying modulation of carrier signal. The inset is an illustration describing the four operating gate bias points used in 4-ASK. $V_{DD}$ is $1V$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

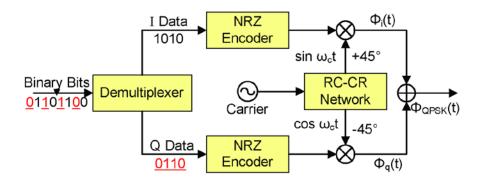

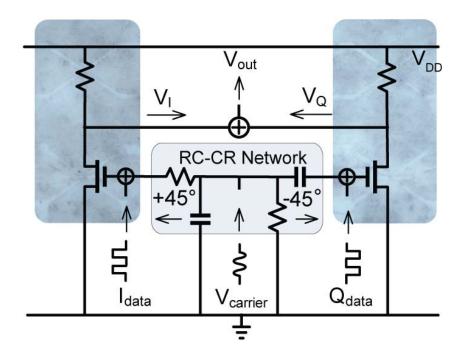

| Figure 4.14 A conceptual diagram of a conventional quadrature phase-shift keying transmitter structure. NRZ encoder is a non-return-to-zero encoder where 1 is represented by a positive voltage state and 0 is represented by a negative voltage state. RC-CR network is the resistance-capacitance-capacitance-resistance phase shift network which generates two orthogonal wave functions with 90° phase difference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 4.15 , An all-graphene circuit diagram of the quadrature phase-shift keying system using two transistors. The actual microscopic image of the all-graphene circuit under a blue filter is shown. The transistor dimension is $10\mu m \times 10\mu m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

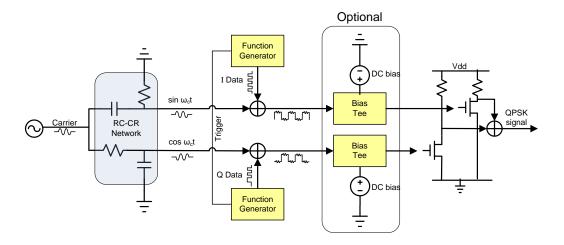

| Figure 4.16 Detailed measurement setup for quadrature phase shift-keying signal generation. A sinusoidal carrier signal is generated from a signal generator and fed to an RC-CR phase shift network. The phase of the sinusoidal signal is shifted by +45 and -45 when it passes through RC and CR structure respectively. The resulting two orthogonal functions (sin $\omega_c t$ and $\cos \omega_c t$ ) with a phase difference of 90° are summed internally in two different function generators with its respective digital data signal shown as the square wave. The two function generators are phase matched using the trigger function. If the charge neutrality point ( $V_{Dirac}$ ) is not centered at zero voltage due to environmental doping, the signal can be connected with a bias tee with a DC bias and then fed to the gate of each transistor. When the DC bias is approximately equal to $V_{Dirac}$ , the phase modulation of each transistors will be symmetric. If the Dirac point at 0 voltage, the signals can be directly inserted to the gates of each transistors without a bias tee The two |

| generated signals which are the final quadrature phase-shift keying signals were added internally and measured with an oscilloscope.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

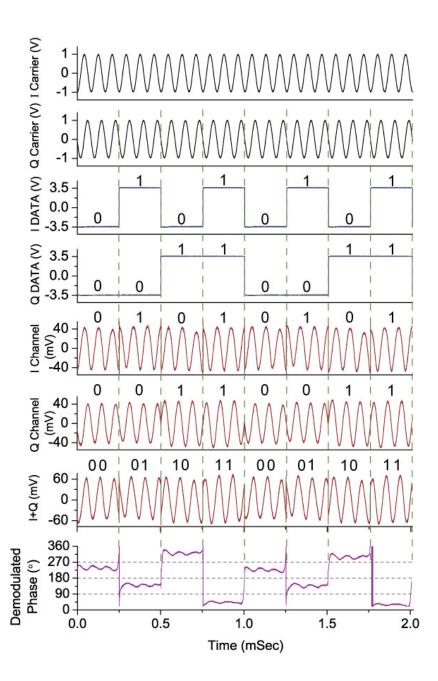

| Figure 4.17 Time domain plots of the input and output signals demonstrating quadrature phase-shift keying modulation scheme. $V_{DD}$ of 7V was the power supply voltage 84                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

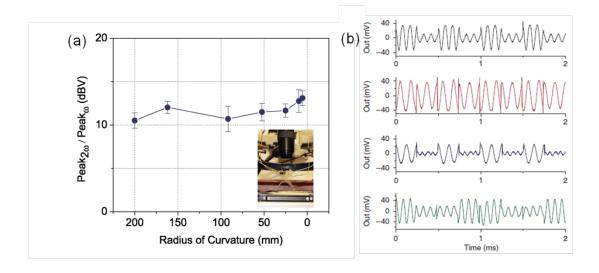

| Figure 4.18 Flexible and transparent all-graphene digital modulator circuits under mechanical strain. (a) The plot of the signal amplitude ratio of the original and the doubled frequency as a function of the curvature radius for a graphene frequency doubler. The inset is a photograph of the measurement setup. (b) Time domain plots of binary amplitude-shift keying (black), binary phase-shift keying (red), binary frequency-shift keying (blue), and quaternary amplitude-shift keying (green) schemes achieved with mechanically strained all-graphene circuits at 5.5mm radius of curvature (2.7% strain). 87 |

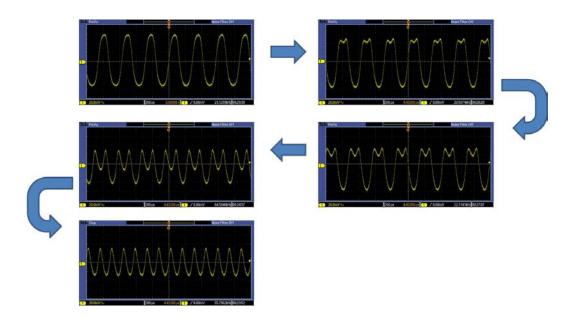

| Figure 4.19 Oscillscope images of the frequency doubling as a result of gradual gate bias shift. As the gate DC bias point shifts from the negative side (hole carrier dominated) to the Dirac point, frequency doubling due to ambipolar characteristics of graphene transistor can be observed. If the DC bias point is not exactly at the Dirac point, the output signal will show asymmetry.                                                                                                                                                                                                                             |

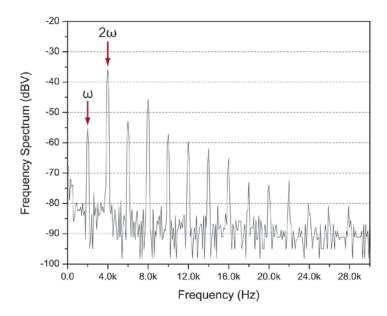

| Figure 4.20 Fast Fourier Transform (FFT) of a typical frequency doubled signal. A typical Fast Fourier Transform (FFT) of the doubled signal from a mechanically strained graphene transistor is shown. The radius of curvature was 5.5mm for this plot. The doubled frequency $(2\omega)$ term and the original frequency $(\omega)$ term has a signal amplitude difference of 20 dBV. The higher order terms also shows significantly weaker signal strength compared to the doubled frequency. The higher order terms can be filtered out in necessary.                                                                   |

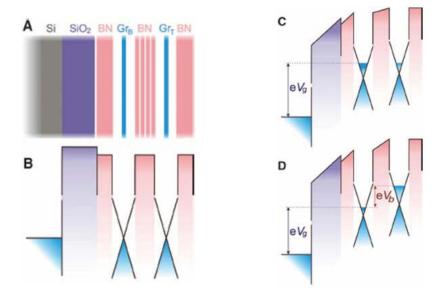

| Figure 5.1 Graphene field-effect tunneling transistor based on atomically thir dichalcogenides between two graphene electrodes. (a) Schematic structure. BN is boron nitride and Gr is graphene. (b) The corresponding band structure with no gate voltage applied. The cones illustrate graphene's Dirac-like spectrum and, the boron nitride between two graphene electrodes act as the tunnel barrier for electrons. (c) The same band structure for a finite gate voltage $V_g$ and zero bias $V_b$ . (d) Both $V_g$ and $V_b$ are finite (adopted from [125])                                                           |

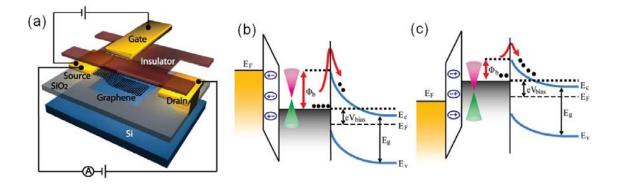

| Figure 5.2 Tunable graphene-silicon junction device (a) a schematic diagram of the device (b) Schematic band diagrams of graphene-silicon Schottky barrier with the electric field effect generated by the gate on the top of graphene. Applying negative voltage or the gate induces holes in graphene, increasing its work function and increasing the Schottky barrier height. As a result, the reverse current across the Schottky barrier decreases. (c) Positive gate voltage decreases the Schottky barrier height and increases reversed current. (adopted from [129])                                               |

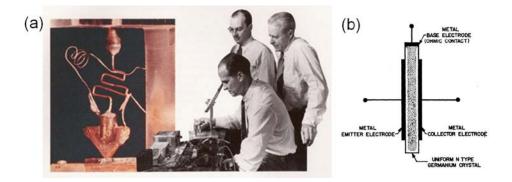

| Figure 5.3 (a) The very first transistor ("point contact transistor") invented by William Shockley, John Bardeen, and Walter Brattain in 1947. (b) The structure of the surface barrier transistor (adopted from [135])               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

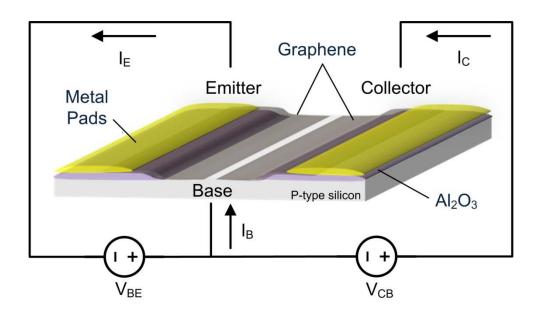

| Figure 5.4 Schematic of bipolar transistor made of graphene-silicon heterostructure 98                                                                                                                                                |

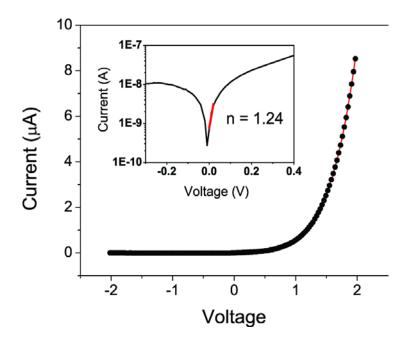

| Figure 5.5 Current versus bias voltage characteristics of diode formed by graphene on p-type silicon. The inset figure shows the current on a log scale                                                                               |

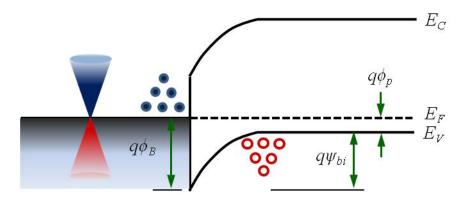

| Figure 5.6 Energy band-diagram of graphene on p-type silicon under thermal equilibrium                                                                                                                                                |

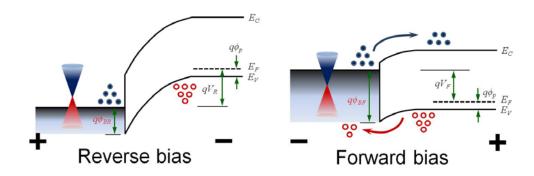

| Figure 5.7 Energy band-diagram of graphene on p-type silicon under reverse and forward bias                                                                                                                                           |

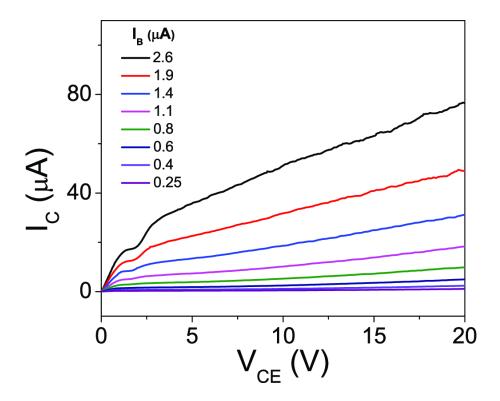

| Figure 5.8 Output characteristics of graphene bipolar transistor                                                                                                                                                                      |

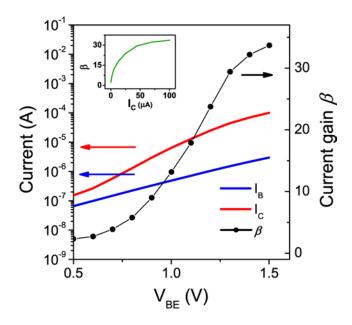

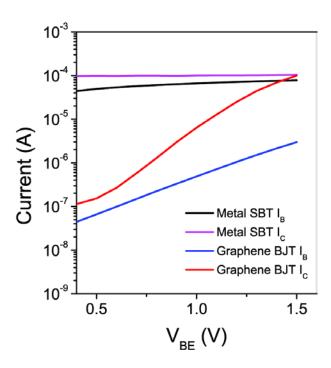

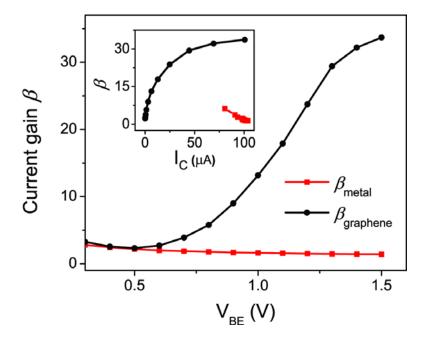

| Figure 5.9 The Gummel plot and the current gain $\beta$ as a function of base-emitter voltage $V_{BE}$ . The inset is the current gain $\beta$ as a function of the collector current                                                 |

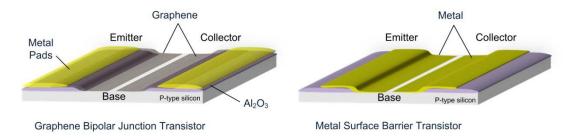

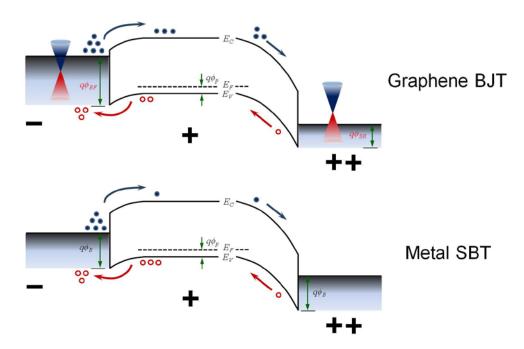

| Figure 5.10 Structural comparison between a graphene based bipolar transistor and a metal based surface barrier transistor                                                                                                            |

| Figure 5.11 The Gummel plot of graphene bipolar junction transistor (red, blue) and metal surface barrier transistor (magenta, black)                                                                                                 |

| Figure 5.12 The current gain comparison of graphene bipolar junction transistor (black) and metal surface barrier transistor (red) as a function of $V_{BE}$ and $I_{C}$ (inset)                                                      |

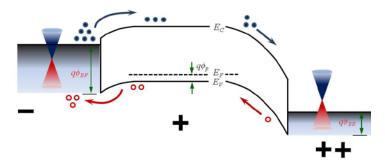

| Figure 5.13 The energy band diagram of a graphene BJT on p-type silicon biased in the normal operating condition. The junction at the left is the base-emitter junction and the junction at the right is the base-collector junction. |

| Figure 5.14 Comparison of the energy band diagram for graphene BJT and metal SBT under normal operating bias condition                                                                                                                |

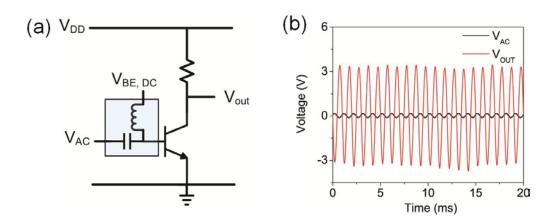

| Figure 5.15 (a) Common emitter amplifier configuration with a graphene BJT. (b) Transient response of the amplifier input and output. The voltage gain is 24.9                                                                        |

# LIST OF APPENDICES

# **Appendix**

| A. | Multilayer graphene (MLG) characterization and growth | .122 |

|----|-------------------------------------------------------|------|

| B. | Transmittance measurement                             | .123 |

| C. | Carrier Mobility Extraction.                          | .124 |

| D. | Extraction of carrier to noise ratio (C/N)            | .126 |

#### **ABSTRACT**

Nanotechnology is the pinnacle of the scientific effort to breach the dimensional limit in matter. Every now and then, this technology offers us a rare glimpse into the true potential of a common material. Graphite, a material found in pencils, has been used by humans since the 4th millennium BC. When atomic particles in graphite are confined in the two-dimensional nanoscale limit, these quasiparticles enter an exclusive domain of relativistic electron theory of the Dirac equation. This single atomic sheet of carbon atoms that provides the confinement is called *graphene*. In this thesis, we present research efforts to harness the extraordinary attributes of graphene and explore new possibilities in the field of nanoelectronics.

First, the importance of bilayer graphene and its tunable bandgap is discussed. For the first time, a rational route to synthesize wafer scale bilayer graphene is investigated using a low-pressure chemical vapor deposition (LPCVD) method. Subsequently, the existence of tunable bandgap devices are confirmed with cryogenic carrier transport measurements from dual-gate bilayer graphene transistors. We further explore the feasibility of a bilayer graphene-based, flexible, transparent conductor, and confirm the efficiency and the exceptional mechanical robustness of the material. The sheet resistance change of the graphene film at 2.14% strain is less than 15%, a 20-fold improvement over commercial indium oxide films.

Next, we report flexible and transparent all-graphene circuits for binary and quaternary digital modulations for the first time. Importantly, the entire modulator circuits are fabricated with graphene only, and this monolithic structure allows unprecedented mechanical flexibility and near-complete transparency. By exploiting the ambipolarity and the nonlinearity in graphene transistors, we achieved quadrature phase shift keying (QPSK) using just two graphene transistors, representing a drastic reduction in circuit complexity when compared with conventional silicon-based modulators.

Lastly, we address the shortcomings of small gain in conventional graphene transistors by designing the very first graphene heterostructure bipolar junction transistor. The exploitation of graphene's low density of states and tunable Fermi level leads to graphene-semiconductor junctions with higher emitter injection efficiency compared to that of a conventional Schottky junction. This property is utilized for the invention of a graphene-based bipolar junction transistor with high on/off ratio( $>10^5$ ) and current gain (>33).

## **Chapter I**

#### Introduction

#### 1.1 Foreword

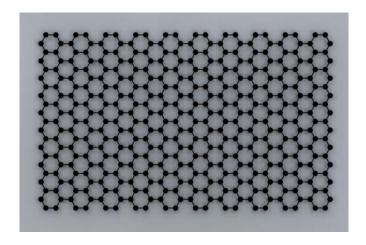

Carbon is one of the most distinctive elements in the periodic table. Carbon bonds allow an almost infinite number of carbon derivatives with other elements, forming the basis of all known organic materials. Furthermore, carbon atoms can also form very stable bonds with themselves. Carbon-carbon single bonds, double bonds, and triple bonds allow the formation of 3-D, 2-D, 1-D, and even 0-D structures. The versatility and the potential of this element has led to many theoretical and experimental studies on carbon-based nanomaterials such as zero-dimensional fullerenes and one-dimensional carbon nanotubes. The existence of a two-dimensional carbon nanosystem was not considered possible because of its inherent thermodynamic instability; as the lateral size of a two-dimensional system grows, the phonon density integrated over the 3D space available for thermal vibration diverges rapidly [1, 5]. However, in 2004, when a monolayer of graphite was exfoliated from bulk graphite, scientists were able to observe a stand-alone two-dimensional carbon nanosystem [1, 6, 7]. This was possible by removing the bulk graphite at a sufficiently low temperature such that the thermal fluctuations were unable to break the atomic bonds [5]. This single sheet of carbon that has been exfoliated from bulk graphite was named "graphene." It is an atomic thick layer

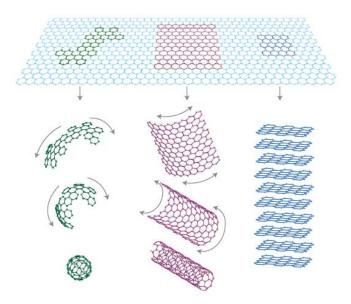

of carbon atoms tightly packed into a honeycomb crystal lattice as shown in Figure 1.1. The carbon atoms (black dots) are all  $sp^2$  hybridized (i.e. one 2s orbital hybridizes with 2px and 2py orbitals to generate three  $sp^2$  orbitals). There is one electron per carbon atom left in the 2pz orbital, and the 2pz orbitals form  $\pi$ -bonds with the neighboring 2pz orbitals. The two-dimensional graphene formed by these bonds is actually the building block of all other carbon-based nanomaterials as shown in Figure 1.2.

Figure 1.1 The graphene crystal lattice.

**Figure 1.2** Graphene is the two dimensional building block for carbon based nanomaterials of all other dimensionalities. It can be wrapped up into 0-D fullerenes, rolled into 1-D carbon nanotubes or stacked into 3-D graphite. (adopted from [1])

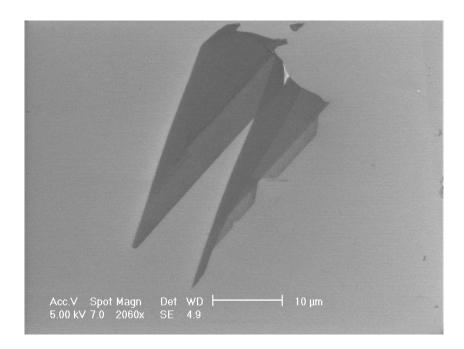

**Figure 1.3** A scanning electron microscopy image of mechanically exfoliated graphene and graphite. Graphene is shown as the region with the lightest color at the right edge of the sample. The rest of the darker colored areas of the sample are either few layer graphenes or thicker graphite.

This two-dimensional allotrope of carbon has emerged as a promising material for novel applications in electronics due to its remarkable physical and electronic properties. It is the thinnest known material but also the strongest ever measured in terms of mechanical stiffness[5]. The charge carriers exhibit extremely high carrier mobility with zero effective mass[6]. It can also sustain current density six orders of magnitude higher than that of copper and shows record thermal conductivity[5]. These astonishing properties can only be understood by studying the unique band structure and morphology of graphene, which will be explained in this chapter.

### 1.2 The electronic properties of graphene

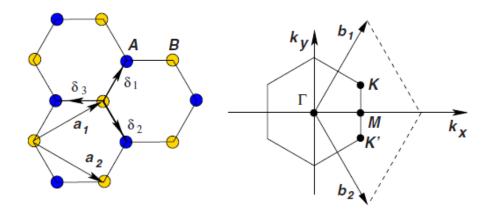

**Figure 1.4** Hexagonal crystal lattice of graphene (left) and its Brillouin zone (right).  $a_1$  and  $a_2$  are the lattice unit vectors, and  $\delta_i$ , i=1,2,3 are the nearest-neighbor vectors. In its corresponding Brillouin zone, the Dirac cones are located at the K and K' points. (adopted from [6])

Graphene atoms are arranged in a hexagonal crystal lattice as shown in Figure 1.4 (left). The structure can be understood as a triangular lattice with a basis of two atoms per unit cell (depicted as blue and yellow in Figure 1.4). The interatomic distance of two carbon atoms is  $\sim$ 1.42 Å [6].

The band structure of graphene follows simple nearest neighbor tight binding approximation [8]. Since graphene has two atoms per unit cell, the points of particular importance are K and K' points at the corners of the graphene Brillouin zone also known as the Dirac points (Figure 1.4 right). Near these points, the energy bands derived from the tight binding Hamiltonian shows linearly dependence of electron energy to the wave vector[9] as shown in the zoom-in of the Figure 1.5. The crystal structure of graphene with two sublattices allows quantum mechanical hopping between the sublattices leading to the formation of two energy bands[10], and their intersection near the edge of the

Brillouine zone results in conical energy dispersions. The bandgap of a graphene is exactly zero, with conduction band and valence band meeting at the K and K' points also known a Dirac point or a charge neutrality point.

**Figure 1.5** The energy dispersions of graphene crystal lattice. The conductance band touches the valence band at the K and the K' points (i.e. the Dirac points). (adopted from [6])

The most interesting aspect of graphene energy spectrum is that its charge carriers can be described by a Dirac spectrum for massless fermions[11, 12] rather than the usual Schrödinger equation for nonrelativistic particles.[1, 5, 6, 10, 13]. The Dirac spectrum is governed by the Dirac equation, which describes relativistic quantum particles with spin 1/2, such as the electrons. The important feature of the Dirac equation is the existence of antiparticles such as positrons[14]. Positrons are antiparticle counterpart of electrons with electric charge of +1e, spin of 1/2, and the same mass as the electrons. The fundamental property of the Dirac equations is often referred to as the charge-conjugation symmetry[14]. This term is used to describe how states at the negative energy (electrons) and the positive energy (positrons) are conjugated, being described by different components of the same spinor wave function[14].

For Dirac particles with a mass m, there is a gap between the minimum electron energy,  $E_o=mc^2$  and the maximum positron energy  $-E_o$ . In this case, the energy is linearly dependent on the k wave vector only when the energy value is much larger than  $E_o$ . However, for massless Dirac fermions, the gap is zero and the energy is linearly dependent on k at any energy. The particles in graphene are neither massless nor relativistic. However, as explained earlier from the tight binding approximation, the quasiparticles in the graphene structure exhibit a linear dispersion relations following the equation  $E=\hbar kv_F$ , as if they were massless relativistic particles (such as photons) governed by the Dirac equation[1, 5, 6, 10, 15]. (Here, the role of the speed of light c is replaced by fermi velocity  $v_F\approx c/300$ .) This means that electrons in graphene all move at a constant speed ( $\sim v_F$ ) regardless of their momentum. Because of this linear dispersion, the quasiparticles in graphene behave very differently from other semiconductor or metal with energy spectrum approximated by parabolic (i.e. free electron like) dispersion relations.

For example, although the bandgap is zero, the gate voltage can still modulate the density of states in graphene[15] and switch from low conductivity states near the Dirac point to high conductivity states elsewhere. However, because there is no bandgap, there is still a finite amount of current even at the low conductivity state near the Dirac point[6, 15] leading to high switch-off current in graphene based transistors. The minimum conductivity is also affected by defect, impurities and the substrate[15, 16].

The graphene crystal also shows exceptional electronic quality such that charge carriers can travel ballistically over submicron distance [1, 7, 17, 18]. Mobility values that are extremely high (~20,000 cm<sup>2</sup>/Vs) were reported for single-layer graphene in

several literatures. [16, 17, 19]. The mobility in these samples is limited by scattering on charged impurities [20, 21] or microscopic ripples [22, 23][3,7]. However, both source of scattering can be reduced significantly by careful sample preparation and they are not the ultimate limiting factors of carrier mobility in graphene structure[17]. It is the intrinsic scatterers such as phonons that cannot be removed at room temperature that sets the fundamental limit of mobility in graphene [16, 17, 19]. This electron-phonon scattering in graphene was found to be a very weak contribution factor to its overall resistivity [24]. For example, Chen et. al.[24] have experimentally proven that the electron-acoustic phonon scattering contributes very little ( $\sim 30\Omega$ ) to graphene's room temperature resistivity. At technologically relevant carrier density of  $1\times 10^{12}$  cm<sup>-2</sup>, they have experimentally shown that a mean free path of  $> 2\mu$ m and an intrinsic mobility value of 200,000 cm<sup>2</sup>/Vs can be reached[24].

Graphene's carrier transfer characteristics also stands out as it shows perfect ambipolar electric field effect so that its charge carrier can be tuned continuously as shown in Figure 1.6 [1]. Its low-energy spectrum is shown as insets in Figure 1.6 indicating the changes in the position of the Fermi energy  $E_F$  with respect to the changing gate voltage  $V_g$ . Positive gate voltage induce electrons while negative voltage induce holes. The concentration of electrons and holes can be as high as  $10^{13}$ cm<sup>-2</sup> [1].

**Figure 1.6** Ambipolar electric field effect in single-layer graphene. The insets show its low-energy spectrum, indicating changes in the position of the Fermi energy  $E_F$  with varying gate voltage  $V_g$ . (adapted from [1])

## 1.3 Graphene applications in electronics

During the last century, silicon-based electronics have contributed immensely to changing our world. New technologies such as portable handheld devices, biomedical apparatus, next-generation displays, and ubiquitous sensor systems were introduced as the technology matured. The industry has maintained the pace of silicon technology by following Moore's law which states that the number of transistors on a chip will double approximately every two years. However as the transistors made of silicon are scaled down, the material's limitations are becoming more apparent. International Technology Roadmap for Semiconductors (ITRS) now considers graphene to be among the candidate materials for post-silicon electronics. In this context, graphene has been proposed as an emerging material to replace silicon in high speed electronics. For example, a graphene transistor with a cutoff frequency as high as 300 GHz has been demonstrated [25]. This

achievement, which exceeds that of silicon transistor, is quite remarkable considering the fact that graphene was found only a few years ago. However, in the field of digital electronics, there is a general consensus that graphene-based transistors will not be able to replace silicon transistors in the near future[5, 26]. There are several reasons for this predicament. First, the fabrication of the integrated circuits is highly complicated, and the semiconductor fabrication plants are extremely expensive to modify. Second, scaling and other design modifications, such as three-dimensional gate structure, have provided the needed performance improvements in the past, and there has been little motivation for the manufacturers to introduce devices based on any material other than silicon. Third, and most importantly, the lack of a bandgap and a complementary structure such as CMOS in graphene transistor technology prevents sufficient turning off of the logic circuit, resulting in significant leakage current and static power dissipation. On the other hand, CMOS logic gates consist of both n- and p-type metal-oxide-semiconductor field-effect transistors (MOSFETs) that can switch between the on-state and the off-state. In the steady state, certain MOSFETs are always switched off so that no current (except a small leakage current) flows through the power source and the ground. The ability of silicon MOSFETs to switch off enables extremely low static power dissipation in CMOS logic. In a conventional FET, this requires semiconducting channels with a sizeable bandgap of at least 0.4eV [26]. It is very challenging to achieve a bandgap this large in graphene transistors, and the resulting on/off ratio of a typical graphene transistor is very low (~100) [27]. Despite graphene transistors' low on/off ratio, which limits their usage in the digital/logic applications, they are in many ways attractive in the analog/radio frequency applications. In analog circuit applications, switching off is not the major limiting factor[26]. In a small-signal amplifier, for example, the transistor is operated in the onstate and a small AC signal that needs to be amplified is superimposed onto a DC gate source bias. Also, the scaling theory predicts that field-effect transistors with a thin gate oxide and a vertically thin gate-controlled region will be robust against short-channel effects even when the gate length is very short [26]. The possibility of having channel that is just a single atomic layer thick is one of the most attractive features of graphene transistors as its extremely thin structure allows shorter scaling of channel length without the adverse short-channel effects [26]. In addition, the ambipolar carrier transport behavior of graphene transistors can be utilized to simplify circuits[28] that otherwise use a complementary structure (e.g. CMOS) having both NFETs and PFETs in a circuit. This is possible because ambipolar graphene transistor exhibits both the property of an NFET and a PFET depending on its gate bias. Adding to the fact that graphene exhibits a naturally high mobility, several pioneering works on graphene analog electronics led to the demonstration of graphene-based frequency doublers [29, 30], amplifiers [28, 31, 32], mixers[33, 34], and modulators[28, 35, 36]. Graphene analog electronics is an active field of research and further development is expected in the future[26].

Another area of interest for graphene application is flexible electronics. Although graphene is the strongest and the stiffest material yet discovered in terms of tensile strength and elastic modulus respectively, it is also extremely flexible [37]. The strength and flexibility results from its covalent sp<sup>2</sup> bonds[37]. Because of its mechanical strength combined with its unique electrical properties, graphene can be used as both the channel and electrode material for flexible electronic devices[38-41]. New applications in the

areas of flexible displays[42], wearable electronics[43] and biomedical skin-like devices[44, 45] are some examples of how graphene can be utilized.

**Figure 1.7** A graphene based touch screen demonstrated in ref [4].

**Figure 1.8** Photograph of a 50  $\mu$ m aperture partially covered by graphene and its bilayer. The line scan profile shows the intensity of transmitted white light along the yellow line. The inset is the support structure with 20, 30, and 50  $\mu$ m in diameter with graphene placed over them. (adopted from [3])

Graphene also shows interesting optical properties. For example, it can be optically visualized, despite being only a single atom thick. As shown in Figure 1.8, graphene absorbs significant amount of light per layer (2.3% per layer at wavelength of 550nm, [3]) but because it is only one atomic layer thick, the transmittance is about 97.7% and it is highly transparent. Graphene is not only transparent but also quite conductive due to its semi-metallic property. The sheet resistance of a pristine layer is about 2 k $\Omega$  to 6 k $\Omega$ [46] and the value can be as low as 125 $\Omega$  depending on the chemical doping method[4]. The sheet resistance value can lowered even more by either stacking several graphene layers[4, 47-49] or fabricating a hybrid nanowire/nanomesh structure[50] with graphene. Several research groups have demonstrated graphene layers as transparent conductive material that can compete with some of the oxide based transparent conductive material (e.g. indium tin oxide or ITO) that dominates the current market. The main advantage of graphene based transparent conductor compared to oxide based material is its mechanical flexibility. Oxide materials, in general, are very brittle and therefore are not suitable for flexible electronics application[51-53]. The usage of graphene transparent conductor will opened up some new possibilities and applications such as flexible solar cells[54], transparent & flexible displays and electronics[4], bendable touch screens[4] and some biomedical applications that requires stretchability and transparency[44].

## 1.4 Graphene synthesis

Graphene was first introduced by micromechanical exfoliation of graphite[7]. This method involves peeling off a piece of graphite by using an adhesive tape. Although