## Barrier height of Pt–InxGa1-xN ( $0 \le x \le 0.5$ ) nanowire Schottky diodes

Wei Guo, Animesh Banerjee, Meng Zhang, and Pallab Bhattacharya

Citation: Appl. Phys. Lett. 98, 183116 (2011); doi: 10.1063/1.3579143

View online: http://dx.doi.org/10.1063/1.3579143

View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v98/i18

Published by the AIP Publishing LLC.

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/

Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded

Information for Authors: http://apl.aip.org/authors

## **ADVERTISEMENT**

## Barrier height of Pt-In<sub>x</sub>Ga<sub>1-x</sub>N ( $0 \le x \le 0.5$ ) nanowire Schottky diodes

Wei Guo, Animesh Banerjee, Meng Zhang, and Pallab Bhattacharya<sup>a)</sup>

Department of Electrical Engineering and Computer Science, Center for Nanoscale Photonics and Spintronics, University of Michigan, Ann Arbor, Michigan 48109-2122, USA

(Received 4 February 2011; accepted 16 March 2011; published online 6 May 2011)

The barrier height of Schottky diodes made on  $In_xGa_{1-x}N$  nanowires have been determined from capacitance-voltage measurements. The nanowires were grown undoped on n-type (001) silicon substrates by plasma-assisted molecular beam epitaxy. The length, diameter and density of the nanowires are  $\sim 1~\mu m$ , 20 nm, and  $1\times 10^{11}~cm^{-2}$ . The Schottky contact was made on the top surface of the nanowires with Pt after planarizing with parylene. The measured barrier height  $\Phi_B$  varies from 1.4 eV (GaN) to 0.44 eV (In<sub>0.5</sub>Ga<sub>0.5</sub>N) and agrees well with the ideal barrier heights in the Schottky limit. © 2011 American Institute of Physics. [doi:10.1063/1.3579143]

One of the important material parameters of a semiconductor that needs to be characterized is the Schottky barrier height since it provides valuable information regarding the nature of the surface of the semiconductor. This is of even greater importance in nanowires, where the surface-tovolume ratio is very large. A large amount of research has been reported on nanowires, made of GaAs, InP, Si, and GaN, including their growth, structural characterization, and optical properties. Of particular interest are GaN and InGaN nanowires, <sup>1-3</sup> whose light emission is in the visible range of the spectrum and can therefore be used for the fabrication of light emitting diodes (LEDs).<sup>4,5</sup> Transmission electron microscopy (TEM) investigations indicate that the nanowires are free of extended defects such as dislocations, twins, and stacking faults.<sup>2,3</sup> The surface recombination velocity in GaN nanowires grown on silicon substrates has been reported to be  $\sim 10^3$  cm/s, two orders of magnitude smaller than that of GaAs. However, the measured and reported Schottky barrier height on bulk GaN films and GaN nanowires with Pt contacts have values ranging from 0.19 to 1.27 eV.<sup>7-12</sup> In the present study, we have measured the room temperature barrier height of Pt-In<sub>x</sub>Ga<sub>1-x</sub>N ( $0 \le x \le 0.5$ ) nanowire Schottky diodes using the capacitance-voltage (C-V) technique. Barrier heights for the ternary material are of interest since the presence of In can alter the nature of the surface. The measured barrier heights vary from 1.4 eV (GaN) to 0.44 eV  $(In_0 {}_5Ga_0 {}_5N).$

Undoped GaN nanowires with a density of  $1 \times 10^{11}$  cm<sup>-2</sup> were grown on (001) Si substrate in a Veeco plasma-assisted molecular beam epitaxy system for the fabrication of Schottky diodes. After removal of the surface oxide on the substrate with a 900 °C anneal in the growth chamber, the substrate temperature was lowered to 800 °C and a few monolayers of Ga were deposited with a Ga flux of  $1.5 \times 10^{-7}$  Torr in the absence of N. GaN nanowire growth was initiated at the same temperature at a rate of 300 nm/hr under N-rich conditions. The Ga flux was maintained at  $1.5 \times 10^{-7}$  Torr and the N flow rate was held constant at 1 SCCM (SCCM denotes cubic centimeter per minute at STP) to grow 1  $\mu$ m long nanowires. To grow (In)GaN nanowires, 300 nm of Si-doped n-type GaN nanowire was first grown

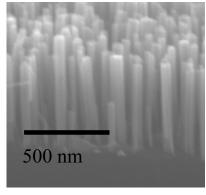

under the conditions outlined above. The growth temperature was then lowered to 550 °C. The Ga flux was held constant at  $1\times10^{-7}$  Torr and the In flux was varied from  $3.5\times10^{-8}$  to  $2.5\times10^{-7}$  Torr to grow 1  $\mu$ m undoped (In)GaN nanowires with different In compositions. The bandgap energies and indium compositions were obtained from photoluminescence and energy dispersive X-Ray (EDX) measurements, respectively. A cross-sectional scanning electron microscope (SEM) image of an  $In_{0.3}Ga_{0.7}N$  nanowire sample grown on (001) Si is shown in Fig. 1.

The process of fabrication of nanowire Schottky diodes is described in some detail, since it is important in the context of device performance. The native oxide on the nanowire bundle on (001) Si is first removed by dipping in HCl. The nanowires are planarized by coating them with a parylene ( $n_r$ =1.66) insulating layer. The nanowire-parylene composite is dry etched to form a mesa. The tips of the nanowires are exposed above the parylene surface, which is confirmed by SEM measurements. These exposed tips are cleaned again in HCl and passivated with (NH<sub>4</sub>)<sub>2</sub>S. A 300 nm thick Pt layer of area  $7.9 \times 10^{-3}$  cm<sup>-2</sup> is selectively deposited by photolithography and electron beam evaporation. Finally, an Al Ohmic contact was formed on the top surface of the n-type Si substrate, after removing the native oxide with an etch in HF.

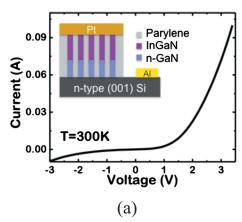

Figure 2(a) depicts the measured current-voltage (I-V) characteristics of a typical GaN nanowire Schottky diode, which is schematically shown in the inset. A turn-on voltage

FIG. 1. Cross-sectional SEM image of an  $\rm In_{0.3}Ga_{0.7}N$  nanowire sample grown on (001) Si. The nanowires have an areal density of  $1-2\times 10^{11}~\rm cm^{-2}$ .

<sup>&</sup>lt;sup>a)</sup>Electronic mail: pkb@eecs.umich.edu. Tel.: 734-763-6678. FAX: 734-763-9324.

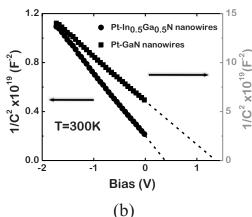

FIG. 2. (Color online) (a) Measured room temperature current-voltage (I-V) characteristics of a Pt–GaN nanowire Schottky diode. The inset schematically shows the device structure; (b) measured  $1/C^2$  vs V plots of GaN and  $In_{0.5}Ga_{0.5}N$  nanowire Schottky diodes at room temperature.

of 1.5 V, a diode series resistance of 15  $\Omega$  and a low reverse leakage current of  $\sim 10^{-5}$  A are derived from the characteristics. Figure 2(b) shows the measured room temperature C-V characteristics of a GaN and an  $In_{0.5}Ga_{0.5}N$  nanowire Schottky diode. The dependence of junction capacitance on bias voltage in a Schottky diode is described by the following:

$$\frac{1}{C^2} = \frac{2}{q N_d \varepsilon_s \varepsilon_o A^2} \left( V_{bi} - V_A - \frac{KT}{q} \right), \tag{1}$$

where  $N_d$  is the carrier concentration in the nanowires,  $\varepsilon_s$  is the static dielectric constant of  $In_xGa_{1-x}N$  (varies from  $\varepsilon_s$  = 8.9 to 8.4 for alloys with x=0 to 0.5), A is the area of the Schottky contact (A=2.4×10<sup>-3</sup> cm² with 30% nanowire filling factor),  $V_{bi}$  is the built-in voltage and  $V_A$  is the applied bias voltage. The nanowires are found to be n-type and from the slope of the  $1/C^2$  vs.  $V_A$  curves the carrier concentration  $N_d$  is derived from Eq. (1) and listed in Table I. The Schottky barrier height  $\Phi_B$  is derived from the equation:

$$\Phi_{\rm B} = qV_{\rm bi} + \left| \frac{E_{\rm g}}{2} - kT \ln \left( \frac{N_{\rm d}}{n_{\rm i}} \right) \right| \tag{2}$$

where  $E_g$  is the energy band gap of  $In_xGa_{1-x}N$  obtained from PL measurements,  $n_i$  is the intrinsic carrier concentration and  $V_{bi}$  is obtained from the  $1/C^2$ - $V_A$  plots. It should be noted that a constant capacitance  $C_P$ , due to the parylene enclosed between the Pt electrode and n-type Si, appears in parallel with the depletion layer capacitance in the nanowires. The value of  $C_P$  is estimated to be 11.6 pF and is included in

TABLE I. Values of barrier heights  $\Phi_B$  and carrier concentration  $N_D$  obtained from C-V measurements on  $Pt\text{-}In_xGa_{1-x}N$  nanowire Schottky diodes. Calculated values of  $\Phi_{B0}$  in the Schottky limit are also listed for comparison.

|                                       | E <sub>g</sub> (eV) | Measured, $\Phi_B$ (eV) | Calculated, $\Phi_{B0}$ (eV) | N <sub>D</sub> (cm <sup>-3</sup> ) |

|---------------------------------------|---------------------|-------------------------|------------------------------|------------------------------------|

| GaN                                   | 3.4                 | 1.40                    | $1.06 \pm 0.4$               | $8.5 \times 10^{16}$               |

| $In_{0.3}Ga_{0.7}N$                   | 2.4                 | 0.74                    | $0.48 \pm 0.4$               | $2.3 \times 10^{17}$               |

| $In_{0.48}Ga_{0.52}N$                 | 1.9                 | 0.45                    | $0.13 \pm 0.4$               | $8.0 \times 10^{17}$               |

| In <sub>0.5</sub> Ga <sub>0.5</sub> N | 1.8                 | 0.44                    | $0.09 \pm 0.4$               | $7.8 \times 10^{17}$               |

the calculations. The  $C_p$  is calculated from  $C_p = \varepsilon \times \varepsilon_r A(1 - \alpha)/d$ , where  $\varepsilon_r$  is the relative dielectric constant of parylene  $(\varepsilon_r = 3.1)$ , A is the mesa size,  $\alpha$  is the nanowire fill factor, and d is the length of the nanowires  $(d=1.3 \ \mu m)$ . The calculated values of the barrier height  $\Phi_B$  are also listed in Table I.

It is instructive at this point to compare the measured values of  $\Phi_B$  with the intrinsic ones in the Schottky limit. It is known that the work function,  $\Phi_m$ , of a metal depends on the deposition condition and the resulting physical and chemical nature of the metal-semiconductor interface. From published values, the value of  $\Phi_m$  for Pt is  $5.22\pm0.4~{\rm eV}.^{13}$  The values of the electron affinity,  $\chi_S$ , for InGaN were determined by linear interpolation between  $\chi_S$  (GaN)=4.16 eV (Ref. 14) and  $\chi_S$  (InN)=6.1 eV. In the Schottky limit, the intrinsic barrier height is defined by  $\Phi_{B0}=\Phi_m-\chi_S$ . The range of values of  $\Phi_{B0}$  is also listed in Table I for comparison. It is apparent that our measured values of  $\Phi_B$  are well within the range for all alloy compositions of  $In_xGa_{1-x}N$ . From C-V measurements, Jang *et al.* have reported a value of  $\Phi_B=1.43~{\rm V}$  in Pt-In<sub>0.1</sub>Ga<sub>0.9</sub>N Schottky diodes

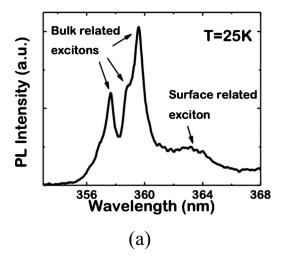

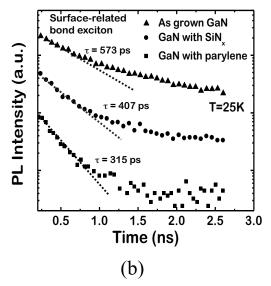

We had earlier reported on the determination of the barrier height of Au-GaN Schottky diodes from I-V measurements.<sup>17</sup> The 3.5  $\mu$ m GaN layers, with n-doping varying from  $1 \times 10^{17} - 7 \times 10^{18}$  cm<sup>-3</sup>, were grown by metalorganic chemical vapor deposition (MOCVD) directly on c-plane sapphire. The layers therefore had a fairly large dislocation density. The measured barrier heights for all the doping levels showed excellent agreement with the calculated value of 0.94 eV in the Schottky limit, taking image force lowering into account. Taken with the result of Jang et al. 16 on Pt-In<sub>0.1</sub>Ga<sub>0.9</sub>N Schottky diodes, it seems that dislocations and related defects do not play any significant role in changing the barrier height. In the nanowires characterized in this study, such defects are almost absent. It is important, however, to assess the possible role of surface recombination and surface depletion on the diode measurements. Additionally, in our experiments the nanowires are passivated with parylene. We have conducted low temperature time-resolved PL (TRPL) measurements on GaN nanowires as-grown and passivated by SiN<sub>x</sub> and parylene. The excitonic spectra at cryogenic temperature are characterized by sharp transitions corresponding to the excitons in two groups, sharp bulk related excitons and a broad surface-related defect bond exciton [Fig. 3(a)]. 18 TRPL measurements were performed at cryogenic temperatures with unpassivated and passivated nanowires at the peak emission wavelength of the various excitonic transitions. It is found that the PL decay times of the three bulk related exciton transitions are almost constant at  $\sim 220 \pm 50$  ps. We believe this time constant reflects the

FIG. 3. (a) Photoluminescence spectra of a GaN nanowire sample measured at 25 K showing three sharp bulk related excitons and a broad surface-related defect bond exciton; (b) PL decay transients obtained from TRPL measurements on as-grown and passivated GaN nanowires.

intrinsic behavior of the bulk nanowires. On the other hand, the decay time constants of the surface related exciton are 572, 407, and 315 ps for the as-grown,  $\mathrm{SiN_x}$ -passivated and parylene-passivated nanowires [Fig. 3(b)]. Due to space-charge related surface depletion, <sup>19,20</sup> electrons and holes can be spatially separated, leading to a longer recombination lifetime. With passivation, the surface state density and the extent of the depletion region will be reduced, thereby enhancing the electron-hole overlap and reducing the lifetime. It seems that with parylene passivation, as is the case in the Schottky diodes measured in this study, the carrier lifetime approaches that of the free excitons in the bulk of the nano-

wires and surface recombination is reduced to a minimum.

Finally, we have also determined  $\Phi_B$ =0.7 eV from I-V measurement on a Pt–GaN nanowire Schottky diode. It is worthwhile to comment on the difference between the barrier heights derived here from C-V measurements with the generally lower values of barrier height determined from forward-biased I-V measurements, even after including the effect of image force lowering. Our measurement on Au–GaN diodes is one of the few exceptions in this respect<sup>17</sup> since the value of  $\Phi_B$  obtained from I-V measurements is in good agreement with the ideal value after considering the effect of image force lowering. Several factors have been cited for the lower values of  $\Phi_B$  ranging from presence of damage layers to enhanced tunneling currents in nanosized contacts. These aspects need more careful study.

The work was supported by KAUST under Grant No. N012509-00.

<sup>1</sup>R. Calarco, R. J. Meijers, R. K. Debnath, T. Stoica, E. Sutter, and H. Lüth, Nano Lett. 7, 2248 (2007).

<sup>2</sup>E. Calleja, J. Ristić, S. Fernández-Garrido, L. Cerutti, M. A. Sánchez-García, J. Grandal, A. Trampert, U. Jahn, G. Sánchez, A. Griol, and B. Sánchez, Physica Status Solidi B **244**, 2816 (2007).

<sup>3</sup>C. Chèze, L. Geelhaar, O. Brandt, W. Weber, H. Riechert, S. Münch, R. Rothemund, S. Reitzenstein, A. Forchel, T. Kehagias, P. Komninou, G. Dimitrakopulos, and T. Karakostas, Nano Res. 3, 528 (2010).

<sup>4</sup>H. Sekiguchi, K. Kishino, and A. Kikuchi, Electron. Lett. 44, 151 (2008).

<sup>5</sup>W. Guo, M. Zhang, A. Banerjee, and P. Bhattacharya, Nano Lett. 10, 3355 (2010).

<sup>6</sup>J. B. Schlager, K. A. Bertness, P. T. Blanchard, L. H. Robins, A. Roshko, and N. A. Sanford, J. Appl. Phys. 103, 124309 (2008).

<sup>7</sup>L. Wang, M. I. Nathan, T. H. Lim, M. A. Khan, and Q. Chen, Appl. Phys. Lett. **68**, 1267 (1996).

<sup>8</sup>A. C. Schmitz, A. T. Ping, M. A. Khan, Q. Chen, J. W. Yang, and I. Adesida, Semicond. Sci. Technol. 11, 1464 (1996).

<sup>9</sup>C. Y. Nam, D. Tham, and J. E. Fischer, Nano Lett. 5, 2029 (2005).

<sup>10</sup>A. Motayed, A. V. Davydov, M. D. Vaudin, I. Levin, J. Melngailis, and S. N. Mohammad, J. Appl. Phys. **100**, 024306 (2006).

<sup>11</sup>P. Deb, H. Kim, Y. Qin, R. Lahiji, M. Oliver, R. Reifenberger, and T. Sands, Nano Lett. 6, 2893 (2006).

<sup>12</sup>P. T. Blanchard, K. A. Bertness, T. E. Harvey, L. M. Mansfield, A. W. Sanders, and N. A. Sanford, IEEE Trans. Nanotechnol. 7, 760 (2008).

<sup>13</sup>M. Nonnenmacher, M. P. O'Boyle, and H. K. Wickramasinghe, Appl. Phys. Lett. **58**, 2921 (1991).

<sup>14</sup>W. Fang, C. Xiong, C. Zheng, L. Wang, and F. Jiang, J. Lumin. **126**, 636 (2007).

<sup>15</sup>C. F. Shih, N. C. Chen, and C. Y. Tseng, Thin Solid Films 516, 5016 (2008).

<sup>16</sup>J.-S. Jang, D. Kim, and T.-Y. Seong, J. Appl. Phys. **99**, 073704 (2006).

<sup>17</sup>S. K. Noh and P. Bhattacharya, Appl. Phys. Lett. **78**, 3642 (2001).

<sup>18</sup>M. A. Reshchikov and H. Morkoc, J. Appl. Phys. **97**, 061301 (2005).

<sup>19</sup>R. Calarco, M. Marso, T. Richter, A. I. Aykanat, R. Meijers, A. d. Hart, T. Stoica, and H. Luth, Nano Lett. 5, 981 (2005).

<sup>20</sup>N. A. Sanford, P. T. Blanchard, K. A. Bertness, L. Mansfield, J. B. Schlager, A. W. Sanders, A. Roshko, B. B. Burton, and S. M. George, J. Appl. Phys. **107**, 034318 (2010).